# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                           |

| Number of I/O              | 39                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-TQFP                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f714-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F70x/71x

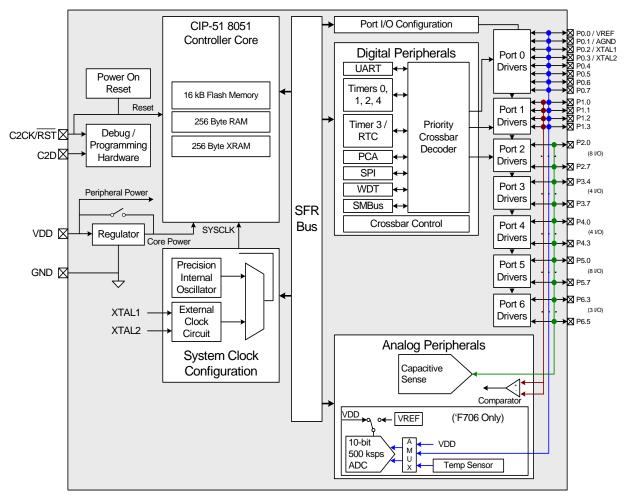

Figure 1.4. C8051F706/07 Block Diagram

# C8051F70x/71x

The Comparator response time may be configured in software via the CPT0MD register (see SFR Definition 14.2). Selecting a longer response time reduces the Comparator supply current.

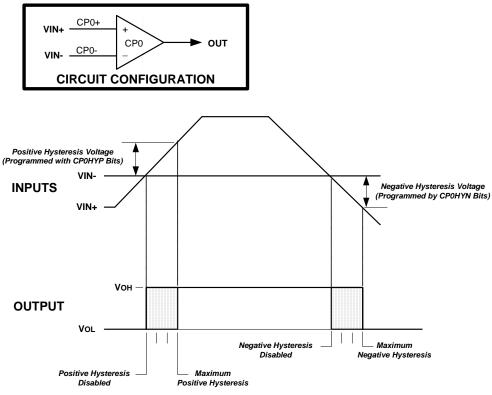

Figure 14.2. Comparator Hysteresis Plot

The Comparator hysteresis is software-programmable via its Comparator Control register CPT0CN. The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage.

The Comparator hysteresis is programmed using Bits3–0 in the Comparator Control Register CPT0CN (shown in SFR Definition 14.1). The amount of negative hysteresis voltage is determined by the settings of the CP0HYN bits. As shown in Figure 14.2, settings of 20, 10 or 5 mV of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CP0HYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see Section "21.1. MCU Interrupt Sources and Vectors" on page 138). The CP0FIF flag is set to logic 1 upon a Comparator falling-edge occurrence, and the CP0RIF flag is set to logic 1 upon the Comparator rising-edge occurrence. Once set, these bits remain set until cleared by software. The Comparator rising-edge interrupt mask is enabled by setting CP0RIE to a logic 1. The Comparator0 falling-edge interrupt mask is enabled by setting CP0FIE to a logic 1.

The output state of the Comparator can be obtained at any time by reading the CP0OUT bit. The Comparator is enabled by setting the CP0EN bit to logic 1, and is disabled by clearing this bit to logic 0.

Note that false rising edges and falling edges can be detected when the comparator is first powered on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed.

# SFR Definition 14.1. CPT0CN: Comparator0 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0HYP[1:0] |   | CP0HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/          | W |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

### SFR Address = 0x9B; SFR Page = 0

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0–.                                                    |

|     |             | 1: Voltage on CP0+ > CP0                                                      |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3:2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

## 15.5. CS0 Comparator

The CS0 comparator compares the latest capacitive sense conversion result with the value stored in CS0THH:CS0THL. If the result is less than or equal to the stored value, the CS0CMPF bit(CS0CN:0) is set to 0. If the result is greater than the stored value, CS0CMPF is set to 1.

If the CS0 conversion accumulator is configured to accumulate multiple conversions, a comparison will not be made until the last conversion has been accumulated.

An interrupt will be generated if CS0 greater-than comparator interrupts are enabled by setting the ECS-GRT bit (EIE2.1) when the comparator sets CS0CMPF to 1.

If auto-scan is running when the comparator sets the CS0CMPF bit, no further auto-scan initiated conversions will start until firmware sets CS0BUSY to 1.

A CS0 greater-than comparator event can wake a device from suspend mode. This feature is useful in systems configured to continuously sample one or more capacitive sense channels. The device will remain in the low-power suspend state until the captured value of one of the scanned channels causes a CS0 greater-than comparator event to occur. It is not necessary to have CS0 comparator interrupts enabled in order to wake a device from suspend with a greater-than event.

For a summary of behavior with different CS0 comparator, auto-scan, and auto accumulator settings, please see Table 15.2.

## SFR Definition 15.5. CS0SS: Capacitive Sense Auto-Scan Start Channel

| Bit   | 7 | 6 | 5 | 4          | 3 | 2 | 1 | 0 |  |  |

|-------|---|---|---|------------|---|---|---|---|--|--|

| Name  |   |   |   | CS0SS[5:0] |   |   |   |   |  |  |

| Туре  | R | R |   | R/W        |   |   |   |   |  |  |

| Reset | 0 | 0 | 0 | 0          | 0 | 0 | 0 | 0 |  |  |

#### SFR Address = 0x92; SFR Page = F

| Bit | Name       | Description                                                                                                                                                                                                                                                                                           |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b; Write = Don't care                                                                                                                                                                                                                                                                        |

| 5:0 | CS0SS[5:0] | Starting Channel for Auto-Scan.                                                                                                                                                                                                                                                                       |

|     |            | Sets the first CS0 channel to be selected by the mux for Capacitive Sense conver-<br>sion when auto-scan is enabled and active. All channels detailed in CS0MX SFR<br>Definition 15.12 are possible choices for this register.<br>When auto-scan is enabled, a write to CS0SS will also update CS0MX. |

## SFR Definition 15.6. CS0SE: Capacitive Sense Auto-Scan End Channel

| Bit   | 7 | 6 | 5 | 4          | 3 | 2 | 1 | 0 |  |  |

|-------|---|---|---|------------|---|---|---|---|--|--|

| Name  |   |   |   | CS0SE[5:0] |   |   |   |   |  |  |

| Туре  | R | R |   | R/W        |   |   |   |   |  |  |

| Reset | 0 | 0 | 0 | 0          | 0 | 0 | 0 | 0 |  |  |

#### SFR Address = 0x93; SFR Page = F

| Bit | Name       | Description                                                                                                                                                                                                           |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 000b; Write = Don't care                                                                                                                                                                                       |

| 5:0 | CS0SE[5:0] | Ending Channel for Auto-Scan.                                                                                                                                                                                         |

|     |            | Sets the last CS0 channel to be selected by the mux for Capacitive Sense conversion when auto-scan is enabled and active. All channels detailed in CS0MX SFR Definition 15.12 are possible choices for this register. |

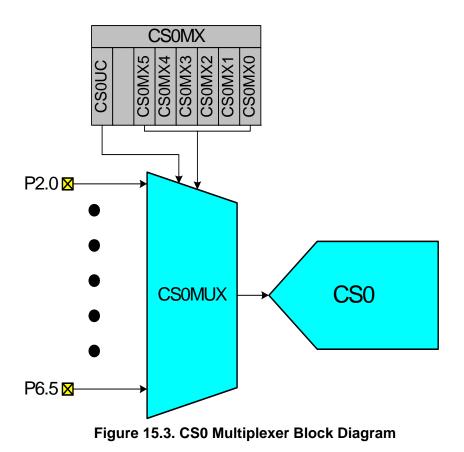

## **15.9. Capacitive Sense Multiplexer**

The input multiplexer can be controlled through two methods. The CSOMX register can be written to through firmware, or the register can be configured automatically using the modules auto-scan functionality (see "15.4. Automatic Scanning").

# SFR Definition 18.3. EMI0TC: External Memory Timing Control

| Bit                              | 7          | 6                          | 5            | 4                                                              | 3        | 2   | 1   | 0      |

|----------------------------------|------------|----------------------------|--------------|----------------------------------------------------------------|----------|-----|-----|--------|

| Nam                              | e EA       | S[1:0]                     |              | EW                                                             | R[3:0]   |     | EAH | I[1:0] |

| Туре                             | <b>,</b> F | R/W                        |              | R                                                              |          | R/W |     |        |

| Rese                             | et 1       | 1                          | 1            | 1                                                              | 1        | 1   | 1   | 1      |

| SFR Address = 0xEE; SFR Page = F |            |                            |              |                                                                |          |     |     |        |

| Bit                              | Name       |                            |              |                                                                | Function |     |     |        |

| 7:6                              | EAS[1:0]   | EMIF Addre                 | ss Setup Ti  | me Bits.                                                       |          |     |     |        |

|                                  |            | 00: Address                | setup time = | = 0 SYSCLK                                                     | cycles.  |     |     |        |

|                                  |            | 01: Address                | setup time = | = 1 SYSCLK                                                     | cycle.   |     |     |        |

|                                  |            | 10: Address                | •            |                                                                | •        |     |     |        |

|                                  |            | 11: Address                | setup time = | = 3 SYSCLK                                                     | cycles.  |     |     |        |

| 5:2                              | EWR[3:0]   | EMIF WR an                 |              |                                                                |          |     |     |        |

|                                  |            | 0000: WR ar                |              |                                                                |          |     |     |        |

|                                  |            | 0001: <u>WR</u> ar         |              |                                                                |          |     |     |        |

|                                  |            | 0010: WR ar                |              |                                                                |          |     |     |        |

|                                  |            |                            |              | ulse width = 4 SYSCLK cycles.<br>ulse width = 5 SYSCLK cycles. |          |     |     |        |

|                                  |            | 0100: WR an                |              |                                                                |          |     |     |        |

|                                  |            | 0110: WR ar                |              |                                                                | •        |     |     |        |

|                                  |            | 0111: WR an                |              |                                                                | •        |     |     |        |

|                                  |            | 1000: WR ar                |              |                                                                | •        |     |     |        |

|                                  |            | 1001: <u>WR</u> ar         |              |                                                                |          |     |     |        |

|                                  |            | 1010: WR ar                |              |                                                                | •        |     |     |        |

|                                  |            | 1011: WR ar<br>1100: WR ar |              |                                                                |          |     |     |        |

|                                  |            | 1100. WR an<br>1101: WR ar |              |                                                                |          |     |     |        |

|                                  |            | 1110: WR an                |              |                                                                |          |     |     |        |

|                                  |            | 1111: WR an                |              |                                                                |          |     |     |        |

| 1:0                              | EAH[1:0]   | EMIF Addre                 | ss Hold Tin  | ne Bits.                                                       |          |     |     |        |

|                                  |            | 00: Address                |              |                                                                | •        |     |     |        |

|                                  |            | 01: Address                |              |                                                                | •        |     |     |        |

|                                  |            | 10: Address                |              |                                                                | •        |     |     |        |

|                                  |            | 11: Address                | nola time =  | 3 SYSULK C                                                     | cycles.  |     |     |        |

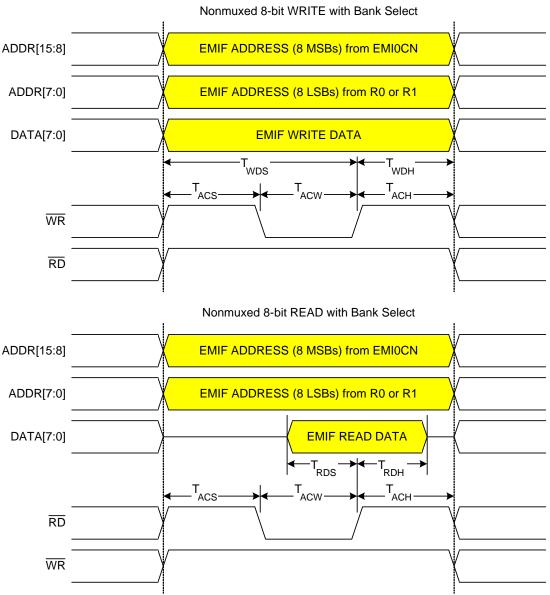

### 18.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110

Figure 18.6. Non-Multiplexed 8-Bit MOVX with Bank Select Timing

# **19. In-System Device Identification**

The C8051F70x/71x has SFRs that identify the device family and derivative. These SFRs can be read by firmware at runtime to determine the capabilities of the MCU that is executing code. This allows the same firmware image to run on MCUs with different memory sizes and peripherals, and dynamically changing functionality to suit the capabilities of that MCU.

In order for firmware to identify the MCU, it must read three SFRs. HWID describes the MCU's family, DERIVID describes the specific derivative within that device family, and REVID describes the hardware revision of the MCU.

### SFR Definition 19.1. HWID: Hardware Identification Byte

| Bit   | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------|---|---|---|---|---|---|---|

| Name  | HWID[7:0] |   |   |   |   |   |   |   |

| Туре  | R         | R | R | R | R | R | R | R |

| Reset | 0         | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

#### SFR Address = 0xC4; SFR Page = F

| Bit | Name      | Description                                                                         |

|-----|-----------|-------------------------------------------------------------------------------------|

| 7:0 | HWID[7:0] | Hardware Identification Byte.                                                       |

|     |           | Describes the MCU family.<br>0x1E: Devices covered in this document (C8051F70x/71x) |

## SFR Definition 19.2. DERIVID: Derivative Identification Byte

| Bit   | 7            | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------------|--------|--------|--------|--------|--------|--------|--------|

| Name  | DERIVID[7:0] |        |        |        |        |        |        |        |

| Туре  | R            | R      | R      | R      | R      | R      | R      | R      |

| Reset | Varies       | Varies | Varies | Varies | Varies | Varies | Varies | Varies |

SFR Address = 0xEC; SFR Page = F

| Bit | Name         | Description                                                        |

|-----|--------------|--------------------------------------------------------------------|

| 7:0 | DERIVID[7:0] | Derivative Identification Byte.                                    |

|     |              | Shows the C8051F70x/71x derivative being used.                     |

|     |              | 0xD0: C8051F700; 0xD1: C8051F701; 0xD2: C8051F702; 0xD3: C8051F703 |

|     |              | 0xD4: C8051F704; 0xD5: C8051F705; 0xD6: C8051F706; 0xD7: C8051F707 |

|     |              | 0xD8: C8051F708; 0xD9: C8051F709; 0xDA: C8051F710; 0xDB: C8051F711 |

|     |              | 0xDC: C8051F712; 0xDD: C8051F713; 0xDE: C8051F714; 0xDF: C8051F715 |

|     |              | 0xE0: C8051F716; 0xE1: C8051F717                                   |

#### 22.4.3. System Clock

- 12. If operating from an external crystal, be advised that crystal performance is susceptible to electrical interference and is sensitive to layout and to changes in temperature. If the system is operating in an electrically noisy environment, use the internal oscillator or use an external CMOS clock.

- 13. If operating from the external oscillator, switch to the internal oscillator during Flash write or erase operations. The external oscillator can continue to run, and the CPU can switch back to the external oscillator after the Flash operation has completed.

Additional Flash recommendations and example code can be found in "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories web site.

## SFR Definition 28.21. P2DRV: Port 2 Drive Strength

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | P2DRV[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xFB; SFR Page = F

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P2DRV[7:0] | Drive Strength Configuration Bits for P2.7–P2.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P2.n Output has low output drive strength.<br>1: Corresponding P2.n Output has high output drive strength. |

## SFR Definition 28.22. P3: Port 3

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | P3[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W     |   |   |   |   |   |   |   |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Address = 0xB0; SFR Page = All Pages; Bit Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P3[7:0] | <b>Port 3 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P3.n Port pin is logic<br>LOW.<br>1: P3.n Port pin is logic<br>HIGH. |

# C8051F70x/71x

## SFR Definition 28.27. P4MDIN: Port 4 Input Mode

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | P4MDIN[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Address = 0xF5; SFR Page = F

| Bit | Name        | Function                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | P4MDIN[7:0] | Analog Configuration Bits for P4.7–P4.0 (respectively).                                                     |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. |

|     |             | 0: Corresponding P4.n pin is configured for analog mode.                                                    |

|     |             | 1: Corresponding P4.n pin is not configured for analog mode.                                                |

## SFR Definition 28.28. P4MDOUT: Port 4 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | P4MDOUT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0x9A; SFR Page = F

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P4MDOUT[7:0] | Output Configuration Bits for P4.7–P4.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P4MDIN is logic 0.<br>0: Corresponding P4.n Output is open-drain.<br>1: Corresponding P4.n Output is push-pull. |

## 29.1. 16-bit CRC Algorithm

The C8051F70x/71x CRC unit calculates the 16-bit CRC MSB-first, using a poly of 0x1021. The following describes the 16-bit CRC algorithm performed by the hardware:

- 1. XOR the most-significant byte of the current CRC result with the input byte. If this is the first iteration of the CRC unit, the current CRC result will be the set initial value (0x0000 or 0xFFFF).

- 2. If the MSB of the CRC result is set, left-shift the CRC result, and then XOR the CRC result with the polynomial (0x1021).

- 3. If the MSB of the CRC result is not set, left-shift the CRC result.

- 4. Repeat at Step 2 for the number of input bits (8).

For example, the 16-bit C8051F70x/71x CRC algorithm can be described by the following code:

```

unsigned short UpdateCRC (unsigned short CRC_acc, unsigned char CRC_input) {

unsigned char i;

// loop counter

#define POLY 0x1021

// Create the CRC "dividend" for polynomial arithmetic (binary arithmetic

// with no carries)

CRC_acc = CRC_acc ^ (CRC_input << 8);</pre>

// "Divide" the poly into the dividend using CRC XOR subtraction

// CRC_acc holds the "remainder" of each divide

// Only complete this division for 8 bits since input is 1 byte

for (i = 0; i < 8; i++)

{

// Check if the MSB is set (if MSB is 1, then the POLY can "divide"

// into the "dividend")

if ((CRC_acc & 0x8000) == 0x8000)

{

// if so, shift the CRC value, and XOR "subtract" the poly

CRC_acc = CRC_acc << 1;</pre>

CRC_acc ^= POLY;

}

else

{

// if not, just shift the CRC value

CRC_acc = CRC_acc << 1;</pre>

}

}

return CRC_acc; // Return the final remainder (CRC value)

}

```

Table 29.1 lists example input values and the associated outputs using the 16-bit C8051F70x/71x CRC algorithm (an initial value of 0xFFFF is used):

| Input                        | Output |

|------------------------------|--------|

| 0x63                         | 0xBD35 |

| 0xAA, 0xBB, 0xCC             | 0x6CF6 |

| 0x00, 0x00, 0xAA, 0xBB, 0xCC | 0xB166 |

#### Table 29.1. Example 16-bit CRC Outputs

## 29.2. 32-bit CRC Algorithm

The C8051F70x/71x CRC unit calculates the 32-bit CRC using a poly of 0x04C11DB7. The CRC-32 algorithm is "reflected", meaning that all of the input bytes and the final 32-bit output are bit-reversed in the processing engine. The following is a description of a simplified CRC algorithm that produces results identical to the hardware:

- 1. XOR the least-significant byte of the current CRC result with the input byte. If this is the first iteration of the CRC unit, the current CRC result will be the set initial value (0x00000000 or 0xFFFFFFF).

- 2. Right-shift the CRC result.

- 3. If the LSB of the CRC result is set, XOR the CRC result with the reflected polynomial (0xEDB88320).

- 4. Repeat at Step 2 for the number of input bits (8).

For example, the 32-bit C8051F70x/71x CRC algorithm can be described by the following code:

```

unsigned long UpdateCRC (unsigned long CRC_acc, unsigned char CRC_input) {

unsigned char i; // loop counter

#define POLY 0xEDB88320 // bit-reversed version of the poly 0x04C11DB7

// Create the CRC "dividend" for polynomial arithmetic (binary arithmetic

// with no carries)

CRC_acc = CRC_acc ^ CRC_input;

// "Divide" the poly into the dividend using CRC XOR subtraction

// CRC_acc holds the "remainder" of each divide

// Only complete this division for 8 bits since input is 1 byte

for (i = 0; i < 8; i++)

{

// Check if the MSB is set (if MSB is 1, then the POLY can "divide" \,

// into the "dividend")

if ((CRC_acc & 0x0000001) == 0x0000001)

{

// if so, shift the CRC value, and XOR "subtract" the poly

CRC_acc = CRC_acc >> 1;

CRC_acc ^= POLY;

}

else

{

// if not, just shift the CRC value

CRC_acc = CRC_acc >> 1;

}

}

return CRC_acc; // Return the final remainder (CRC value)

```

Table 29.2 lists example input values and the associated outputs using the 32-bit C8051F70x/71x CRC algorithm (an initial value of 0xFFFFFFF is used):

#### Table 29.2. Example 32-bit CRC Outputs

| Input                        | Output     |  |  |  |

|------------------------------|------------|--|--|--|

| 0x63                         | 0xF9462090 |  |  |  |

| 0xAA, 0xBB, 0xCC             | 0x41B207B3 |  |  |  |

| 0x00, 0x00, 0xAA, 0xBB, 0xCC | 0x78D129BC |  |  |  |

## 30. SMBus

The SMBus I/O interface is a two-wire, bi-directional serial bus. The SMBus is compliant with the System Management Bus Specification, version 1.1, and compatible with the I<sup>2</sup>C serial bus. Reads and writes to the interface by the system controller are byte oriented with the SMBus interface autonomously controlling the serial transfer of the data. Data can be transferred at up to 1/20th of the system clock as a master or slave (this can be faster than allowed by the SMBus specification, depending on the system clock used). A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

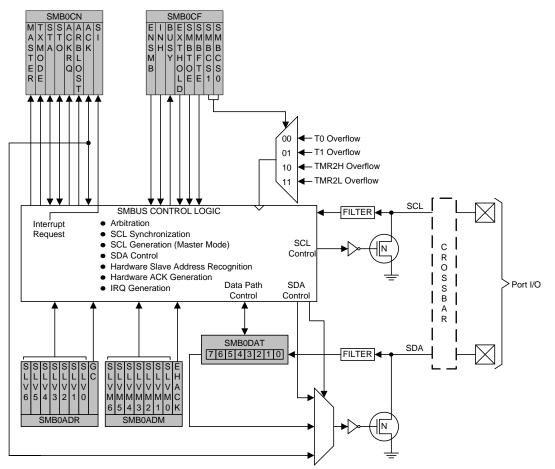

The SMBus interface may operate as a master and/or slave, and may function on a bus with multiple masters. The SMBus provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and START/STOP control and generation. The SMBus peripheral can be fully driven by software (i.e., software accepts/rejects slave addresses, and generates ACKs), or hardware slave address recognition and automatic ACK generation can be enabled to minimize software overhead. A block diagram of the SMBus peripheral and the associated SFRs is shown in Figure 30.1.

Figure 30.1. SMBus Block Diagram

| SMBCS1 | SMBCS0 | SMBus Clock Source         |  |  |  |  |

|--------|--------|----------------------------|--|--|--|--|

| 0      | 0      | Timer 0 Overflow           |  |  |  |  |

| 0      | 1      | Timer 1 Overflow           |  |  |  |  |

| 1      | 0      | Timer 2 High Byte Overflow |  |  |  |  |

| 1      | 1      | Timer 2 Low Byte Overflow  |  |  |  |  |

#### Table 30.1. SMBus Clock Source Selection

The SMBCS1–0 bits select the SMBus clock source, which is used only when operating as a master or when the Free Timeout detection is enabled. When operating as a master, overflows from the selected source determine the absolute minimum SCL low and high times as defined in Equation 30.1.The selected clock source may be shared by other peripherals so long as the timer is left running at all times. For example, Timer 1 overflows may generate the SMBus and UART baud rates simultaneously. Timer configuration is covered in Section "33. Timers" on page 262.

$$T_{HighMin} = T_{LowMin} = \frac{1}{f_{ClockSourceOverflow}}$$

### Equation 30.1. Minimum SCL High and Low Times

The selected clock source should be configured to establish the minimum SCL High and Low times as per Equation 30.1. When the interface is operating as a master (and SCL is not driven or extended by any other devices on the bus), the typical SMBus bit rate is approximated by Equation 30.2.

$$BitRate = \frac{f_{ClockSourceOverflow}}{3}$$

#### Equation 30.2. Typical SMBus Bit Rate

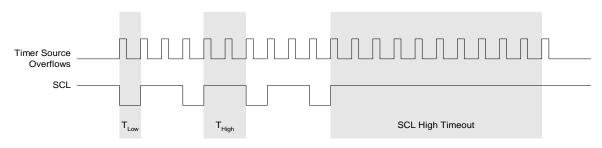

Figure 30.4 shows the typical SCL generation described by Equation 30.2. Notice that  $T_{HIGH}$  is typically twice as large as  $T_{LOW}$ . The actual SCL output may vary due to other devices on the bus (SCL may be extended low by slower slave devices, or driven low by contending master devices). The bit rate when operating as a master will never exceed the limits defined by equation Equation 30.1.

Figure 30.4. Typical SMBus SCL Generation

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 30.2 shows the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively.

# SFR Definition 30.1. SMB0CF: SMBus Clock/Configuration

| Bit   | 7     | 6   | 5    | 4       | 3      | 2      | 1          | 0 |

|-------|-------|-----|------|---------|--------|--------|------------|---|

| Name  | ENSMB | INH | BUSY | EXTHOLD | SMBTOE | SMBFTE | SMBCS[1:0] |   |

| Туре  | R/W   | R/W | R    | R/W     | R/W    | R/W    | R/W        |   |

| Reset | 0     | 0   | 0    | 0       | 0      | 0      | 0          | 0 |

## SFR Address = 0xC1; SFR Page = 0

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | ENSMB      | SMBus Enable.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     |            | This bit enables the SMBus interface when set to 1. When enabled, the interface constantly monitors the SDA and SCL pins.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 6   | INH        | SMBus Slave Inhibit.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|     |            | When this bit is set to logic 1, the SMBus does not generate an interrupt when slave events occur. This effectively removes the SMBus slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                                                                                                    |  |  |  |  |

| 5   | BUSY       | SMBus Busy Indicator.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|     |            | This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 4   | EXTHOLD    | SMBus Setup and Hold Time Extension Enable.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|     |            | This bit controls the SDA setup and hold times according to Table 30.2.                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|     |            | 0: SDA Extended Setup and Hold Times disabled.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|     |            | 1: SDA Extended Setup and Hold Times enabled.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 3   | SMBTOE     | SMBus SCL Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|     |            | This bit enables SCL low timeout detection. If set to logic 1, the SMBus forces<br>Timer 3 to reload while SCL is high and allows Timer 3 to count when SCL goes low.<br>If Timer 3 is configured to Split Mode, only the High Byte of the timer is held in reload<br>while SCL is high. Timer 3 should be programmed to generate interrupts at 25 ms,<br>and the Timer 3 interrupt service routine should reset SMBus communication. |  |  |  |  |

| 2   | SMBFTE     | SMBus Free Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|     |            | When this bit is set to logic 1, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods.                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 1:0 | SMBCS[1:0] | SMBus Clock Source Selection.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     |            | These two bits select the SMBus clock source, which is used to generate the SMBus bit rate. The selected device should be configured according to Equation 30.1.                                                                                                                                                                                                                                                                      |  |  |  |  |

|     |            | 00: Timer 0 Overflow                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|     |            | 01: Timer 1 Overflow                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|     |            | 10: Timer 2 High Byte Overflow                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|     |            | 11: Timer 2 Low Byte Overflow                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

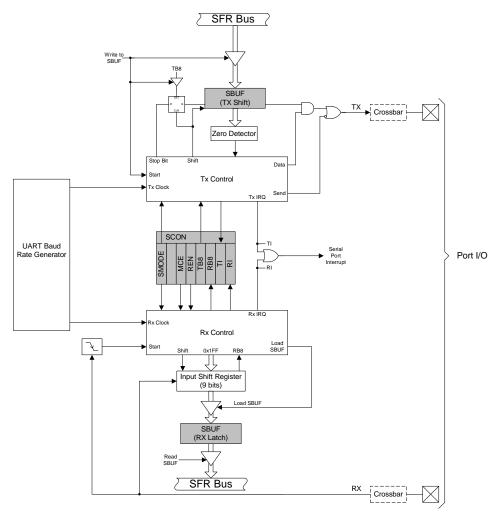

# 32. UART0

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in Section "32.1. Enhanced Baud Rate Generation" on page 255). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART0 has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Writes to SBUF0 always access the Transmit register. Reads of SBUF0 always access the buffered Receive register; it is not possible to read data from the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

Figure 32.1. UART0 Block Diagram

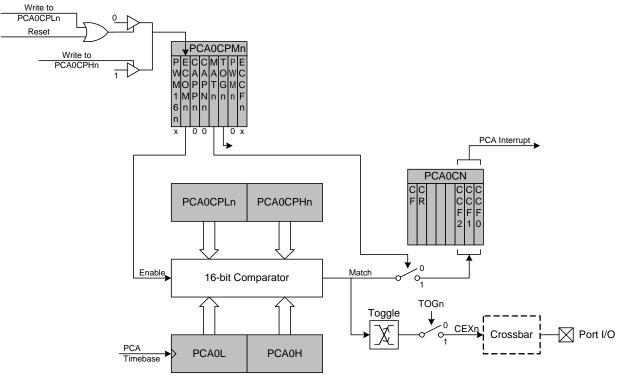

#### 34.3.3. High-Speed Output Mode

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode. If ECOMn is cleared, the associated pin will retain its state, and not toggle on the next match event.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 34.6. PCA High-Speed Output Mode Diagram

# SFR Definition 34.5. PCA0L: PCA Counter/Timer Low Byte

| Bit                              | 7         | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|----------------------------------|-----------|------------|-----|-----|-----|-----|-----|-----|

| Name                             | PCA0[7:0] |            |     |     |     |     |     |     |

| Туре                             | R/W       | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset                            | 0         | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

| SFR Address = 0xF9; SFR Page = 0 |           |            |     |     |     |     |     |     |

| Bit                              | Name      | e Function |     |     |     |     |     |     |

| Bit | Name      | Function                                                                     |

|-----|-----------|------------------------------------------------------------------------------|

| 7:0 | PCA0[7:0] | PCA Counter/Timer Low Byte.                                                  |

|     |           | The PCA0L register holds the low byte (LSB) of the 16-bit PCA Counter/Timer. |

## SFR Definition 34.6. PCA0H: PCA Counter/Timer High Byte

| Bit   | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | PCA0[15:8] |     |     |     |     |     |     |     |

| Туре  | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0xFA; SFR Page = 0

| Bit | Name       | Function                                                                                                                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | PCA0[15:8] | PCA Counter/Timer High Byte.                                                                                                                                                                                                                        |

|     |            | The PCA0H register holds the high byte (MSB) of the 16-bit PCA Counter/Timer.<br>Reads of this register will read the contents of a "snapshot" register, whose contents<br>are updated only when the contents of PCA0L are read (see Section 34.1). |