# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, WDT                                        |

| Number of I/O              | 39                                                              |

| Program Memory Size        | 8KB (8K × 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-TQFP                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f715-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

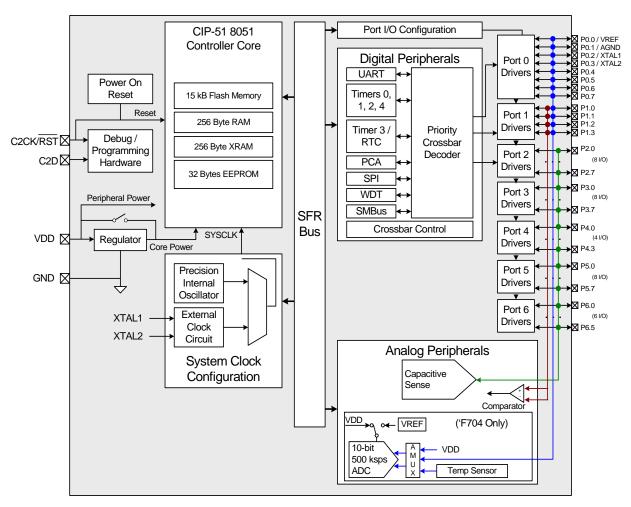

Figure 1.3. C8051F704/5 Block Diagram

## 11. Temperature Sensor

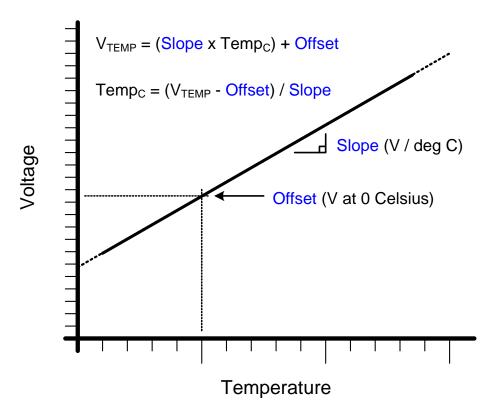

An on-chip temperature sensor is included on the C8051F700/2/4/6/8 and C8051F710/2/4/6 which can be directly accessed via the ADC multiplexer in single-ended configuration. To use the ADC to measure the temperature sensor, the ADC mux channel should be configured to connect to the temperature sensor. The temperature sensor transfer function is shown in Figure 11.1. The output voltage ( $V_{TEMP}$ ) is the positive ADC input when the ADC multiplexer is set correctly. The TEMPE bit in register REF0CN enables/disables the temperature sensor, as described in SFR Definition 12.1. While disabled, the temperature sensor defaults to a high impedance state and any ADC measurements performed on the sensor will result in meaningless data. Refer to Table 9.12 for the slope and offset parameters of the temperature sensor.

Figure 11.1. Temperature Sensor Transfer Function

#### 11.1. Calibration

The uncalibrated temperature sensor output is extremely linear and suitable for relative temperature measurements (see Table 5.1 for linearity specifications). For absolute temperature measurements, offset and/or gain calibration is recommended. Typically a 1-point (offset) calibration includes the following steps:

- 1. Control/measure the ambient temperature (this temperature must be known).

- 2. Power the device, and delay for a few seconds to allow for self-heating.

- 3. Perform an ADC conversion with the temperature sensor selected as the ADC's input.

- 4. Calculate the offset characteristics, and store this value in non-volatile memory for use with subsequent temperature sensor measurements.

Figure 5.3 shows the typical temperature sensor error assuming a 1-point calibration at 0 °C.

## SFR Definition 12.1. REF0CN: Voltage Reference Control

| Bit   | 7 | 6 | 5      | 4   | 3   | 2     | 1     | 0 |

|-------|---|---|--------|-----|-----|-------|-------|---|

| Name  |   |   | REFGND | REI | FSL | TEMPE | BIASE |   |

| Туре  | R | R | R/W    | R/W | R/W | R/W   | R/W   | R |

| Reset | 0 | 0 | 0      | 1   | 0   | 0     | 0     | 0 |

#### SFR Address = 0xD2; SFR Page = F

| Bit | Name   | Function                                                                           |

|-----|--------|------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b; Write = Don't Care.                                                    |

| 5   | REFGND | Analog Ground Reference.                                                           |

|     |        | Selects the ADC0 ground reference.                                                 |

|     |        | 0: The ADC0 ground reference is the GND pin.                                       |

|     |        | 1: The ADC0 ground reference is the P0.1/AGND pin.                                 |

| 4:3 | REFSL  | Voltage Reference Select.                                                          |

|     |        | Selects the ADC0 voltage reference.                                                |

|     |        | 00: The ADC0 voltage reference is the P0.0/VREF pin.                               |

|     |        | 01: The ADC0 voltage reference is the VDD pin.                                     |

|     |        | 10: The ADC0 voltage reference is the internal 1.8 V digital supply voltage.       |

|     |        | 11: The ADC0 voltage reference is the internal 1.6 V high-speed voltage reference. |

| 2   | TEMPE  | Temperature Sensor Enable.                                                         |

|     |        | Enables/Disables the internal temperature sensor.                                  |

|     |        | 0: Temperature Sensor Disabled.                                                    |

|     |        | 1: Temperature Sensor Enabled.                                                     |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.                                         |

|     |        | 0: Internal Bias Generator off.                                                    |

|     |        | 1: Internal Bias Generator on.                                                     |

| 0   | Unused | Read = 0b; Write = Don't Care.                                                     |

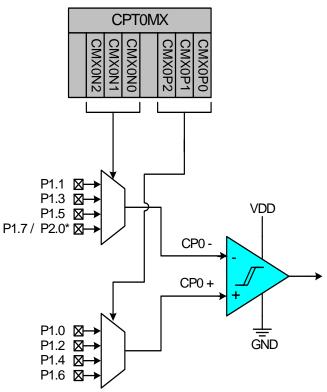

#### 14.1. Comparator Multiplexer

C8051F70x/71x devices include an analog input multiplexer to connect Port I/O pins to the comparator inputs. The Comparator0 inputs are selected in the CPT0MX register (SFR Definition 14.3). The CMX0P2–CMX0P0 bits select the Comparator0 positive input; the CMX0N2–CMX0N0 bits select the Comparator0 negative input.

**Important Note About Comparator Inputs:** The Port pins selected as comparator inputs should be configured as analog inputs in their associated Port configuration register, and configured to be skipped by the Crossbar (for details on Port configuration, see Section "28.6. Special Function Registers for Accessing and Configuring Port I/O" on page 194).

\*P1.7 on 64 and 48-pin devices, P2.0 on 32 and 24-pin devices

#### 15.6. CS0 Conversion Accumulator

CS0 can be configured to accumulate multiple conversions on an input channel. The number of samples to be accumulated is configured using the CS0ACU2:0 bits (CS0CF2:0). The accumulator can accumulate 1, 4, 8, 16, 32, or 64 samples. After the defined number of samples have been accumulated, the result is divided by either 1, 4, 8, 16, 32, or 64 (depending on the CS0ACU[2:0] setting) and copied to the CS0DH:CS0DL SFRs.

| Auto-Scan Enabled | Accumulator Enabled | CS0 Conversion<br>Complete<br>Interrupt<br>Behavior                      | CS0 Greater Than Interrupt<br>Behavior                                                                                                                       | CS0MX Behavior                                                                                                                                                                                                                    |

|-------------------|---------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N                 | Ν                   | CS0INT Interrupt<br>serviced after 1<br>conversion com-<br>pletes        | Interrupt serviced after 1 con-<br>version completes if value in<br>CS0DH:CS0DL is greater than<br>CS0THH:CS0THL                                             | CS0MX unchanged.                                                                                                                                                                                                                  |

| N                 | Y                   | CS0INT Interrupt<br>serviced after <i>M</i><br>conversions com-<br>plete | Interrupt serviced after <i>M</i> conversions complete if value in CS0DH:CS0DL (post accumulate and divide) is greater than CS0THH:CS0THL                    | CS0MX unchanged.                                                                                                                                                                                                                  |

| Y                 | Ν                   | CS0INT Interrupt<br>serviced after 1<br>conversion com-<br>pletes        | Interrupt serviced after con-<br>version completes if value in<br>CS0DH:CS0DL is greater than<br>CS0THH:CS0THL;<br>Auto-Scan stopped                         | If greater-than comparator detects conver-<br>sion value is greater than<br>CS0THH:CS0THL, CS0MX is left<br>unchanged; otherwise, CS0MX updates to<br>the next channel (CS0MX + 1) and wraps<br>back to CS0SS after passing CS0SE |

| Y                 | Y                   | CS0INT Interrupt<br>serviced after <i>M</i><br>conversions com-<br>plete | Interrupt serviced after <i>M</i> conversions complete if value in CS0DH:CS0DL (post accumulate and divide) is greater than CS0THH:CS0THL; Auto-Scan stopped | If greater-than comparator detects conver-<br>sion value is greater than<br>CS0THH:CS0THL, CS0MX is left<br>unchanged; otherwise, CS0MX updates to<br>the next channel (CS0MX + 1) and wraps<br>back to CS0SS after passing CS0SE |

|                   |                     | M =                                                                      | Accumulator setting (1x, 4x, 8                                                                                                                               | 3x, 16x, 32x, 64x)                                                                                                                                                                                                                |

Table 15.2. Operation with Auto-scan and Accumulate

#### SFR Definition 15.5. CS0SS: Capacitive Sense Auto-Scan Start Channel

| Bit   | 7 | 6 | 5 | 4           | 3  | 2 | 1 | 0 |  |  |  |

|-------|---|---|---|-------------|----|---|---|---|--|--|--|

| Name  |   |   |   | CS0SS[5:0]  |    |   |   |   |  |  |  |

| Туре  | R | R |   |             | R/ | W |   |   |  |  |  |

| Reset | 0 | 0 | 0 | 0 0 0 0 0 0 |    |   |   |   |  |  |  |

#### SFR Address = 0x92; SFR Page = F

| Bit | Name       | Description                                                                                                                                                                                                                                                                                           |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b; Write = Don't care                                                                                                                                                                                                                                                                        |

| 5:0 | CS0SS[5:0] | Starting Channel for Auto-Scan.                                                                                                                                                                                                                                                                       |

|     |            | Sets the first CS0 channel to be selected by the mux for Capacitive Sense conver-<br>sion when auto-scan is enabled and active. All channels detailed in CS0MX SFR<br>Definition 15.12 are possible choices for this register.<br>When auto-scan is enabled, a write to CS0SS will also update CS0MX. |

### SFR Definition 15.6. CS0SE: Capacitive Sense Auto-Scan End Channel

| Bit   | 7 | 6 | 5 | 4           | 3  | 2 | 1 | 0 |  |  |  |

|-------|---|---|---|-------------|----|---|---|---|--|--|--|

| Name  |   |   |   | CS0SE[5:0]  |    |   |   |   |  |  |  |

| Туре  | R | R |   |             | R/ | W |   |   |  |  |  |

| Reset | 0 | 0 | 0 | 0 0 0 0 0 0 |    |   |   |   |  |  |  |

#### SFR Address = 0x93; SFR Page = F

| Bit | Name       | Description                                                                                                                                                                                                           |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 000b; Write = Don't care                                                                                                                                                                                       |

| 5:0 | CS0SE[5:0] | Ending Channel for Auto-Scan.                                                                                                                                                                                         |

|     |            | Sets the last CS0 channel to be selected by the mux for Capacitive Sense conversion when auto-scan is enabled and active. All channels detailed in CS0MX SFR Definition 15.12 are possible choices for this register. |

## SFR Definition 15.12. CS0MX: Capacitive Sense Mux Channel Select

| Bit   | 7             | 6                                  |             | 5                     | 4      |      | 3                   | 2        | 1                     |               | 0             |

|-------|---------------|------------------------------------|-------------|-----------------------|--------|------|---------------------|----------|-----------------------|---------------|---------------|

| Nam   | e CSOUC       |                                    |             | I                     |        | I    | CS0MX               | [5:0]    |                       |               |               |

| Туре  | e R/W         | R/W                                | R/W R/W     |                       |        |      |                     |          |                       |               |               |

| Rese  | et 0          | 0                                  | 0 0 0 0 0 0 |                       |        |      |                     |          |                       | 0             |               |

| SFR A | Address = 0x9 | DC; SFR Page = 0                   |             |                       |        |      |                     |          |                       |               |               |

| Bit   | Name          |                                    | Description |                       |        |      |                     |          |                       |               |               |

| 7     | CS0UC         | CS0 Unc                            |             |                       |        |      |                     |          |                       |               |               |

|       |               | Disconne<br>0: CS0 co<br>1: CS0 di | onnecte     | d to port             | pins   | •    | dless of t          | he selec | ted chani             | nel.          |               |

| 6     | Reserved      | Write = 0                          | b           |                       |        |      |                     |          |                       |               |               |

| 5:0   | CS0MX[5:0]    | CS0 Mux                            |             |                       |        |      |                     | Correct  |                       |               |               |

|       |               | Value                              |             | •                     | 32-pin |      | Capacitive<br>Value | 64-pin   | 48-pin                | on.<br>32-pin | 24-pin        |

|       |               | 000000                             | P2.0        | <b>40-pin</b><br>P2.0 | P2.0   | P2.0 | 010011              | P4.3     | <b>46-ріп</b><br>Р4.3 | sz-pin        | 24-pm<br>P4.3 |

|       |               | 000000                             | P2.0        | P2.0                  | P2.0   | P2.0 | 010100              | P4.4     | F 4.5                 |               | P4.3          |

|       |               | 000010                             | P2.2        | P2.2                  | P2.2   | P2.2 | 010100              | P4.5     |                       |               | P4.5          |

|       |               | 000011                             | P2.3        | P2.3                  | P2.3   | P2.3 | 010110              | P4.6     | _                     |               | P4.6          |

|       |               | 000100                             | P2.4        | P2.4                  | P2.4   | P2.4 | 010111              | P4.7     | _                     | _             | P4.7          |

|       |               | 000101                             | P2.5        | P2.5                  | P2.5   | P2.5 | 011000              | P5.0     | P5.0                  | P5.0          | _             |

|       |               | 000110                             | P2.6        | P2.6                  | P2.6   | P2.6 | 011001              | P5.1     | P5.1                  | P5.1          |               |

|       |               | 000111                             | P2.7        | P2.7                  | P2.7   | P2.7 | 011010              | P5.2     | P5.2                  | P5.2          | —             |

|       |               | 001000                             | P3.0        | —                     | P3.0   | —    | 011011              | P5.3     | P5.3                  | P5.3          | _             |

|       |               | 001001                             | P3.1        |                       | P3.1   |      | 011100              | P5.4     | P5.4                  | P5.4          | —             |

|       |               | 001010                             | P3.2        |                       | P3.2   |      | 011101              | P5.5     | P5.5                  | P5.5          | —             |

|       |               | 001011                             | P3.3        | _                     | P3.3   | _    | 011110              | P5.6     | P5.6                  | P5.6          | —             |

|       |               | 001100                             | P3.4        | P3.4                  | P3.4   | —    | 011111              | P5.7     | P5.7                  | P5.7          | —             |

|       |               | 001101                             | P3.5        | P3.5                  | P3.5   |      | 100000              | P6.0     |                       | —             | —             |

|       |               | 001110                             | P3.6        | P3.6                  | P3.6   |      | 100001              | P6.1     |                       | —             | —             |

|       |               | 001111                             | P3.7        | P3.7                  | —      | —    | 100010              | P6.2     | —                     | —             | —             |

|       |               | 010000                             | P4.0        | P4.0                  | —      | P4.0 | 100011              | P6.3     | P6.3                  | P6.3          |               |

|       |               | 010001                             | P4.1        | P4.1                  | —      | P4.1 | 100100              | P6.4     | P6.4                  | P6.4          | P6.4          |

|       |               | 010010                             | P4.2        | P4.2                  | —      | P4.2 | 100101              | P6.5     | P6.5                  | P6.5          | P6.5          |

### SFR Definition 16.3. SP: Stack Pointer

| Bit    | 7           | 6               | 5           | 4  | 3                | 2 | 1 | 0 |  |  |

|--------|-------------|-----------------|-------------|----|------------------|---|---|---|--|--|

| Name   | SP[7:0]     |                 |             |    |                  |   |   |   |  |  |

| Туре   |             |                 |             | R/ | W                |   |   |   |  |  |

| Reset  | 0           | 0 0 0 0 0 1 1 1 |             |    |                  |   |   |   |  |  |

| SFR Ad | dress = 0x8 | 1; SFR Page     | = All Pages |    |                  |   |   |   |  |  |

| D:4    | Marria      |                 |             |    | <b>F</b> unction |   |   |   |  |  |

| Bit | Name    | Function                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

### SFR Definition 16.4. ACC: Accumulator

| Bit   | 7             | 7 6 5 4 3 2 1 0 |               |               |               |           |   |   |  |  |  |

|-------|---------------|-----------------|---------------|---------------|---------------|-----------|---|---|--|--|--|

| Nam   | Name ACC[7:0] |                 |               |               |               |           |   |   |  |  |  |

| Туре  | R/W           |                 |               |               |               |           |   |   |  |  |  |

| Rese  | et 0          | 0               | 0             | 0             | 0             | 0         | 0 | 0 |  |  |  |

| SFR A | Address = 0xE | E0; SFR Page    | e = All Pages | ; Bit-Addres  | sable         |           |   |   |  |  |  |

| Bit   | Name          |                 |               |               | Function      |           |   |   |  |  |  |

| 7:0   | ACC[7:0]      | Accumulator.    |               |               |               |           |   |   |  |  |  |

|       |               | This register   | is the accur  | mulator for a | rithmetic ope | erations. |   |   |  |  |  |

Rev. 1.0

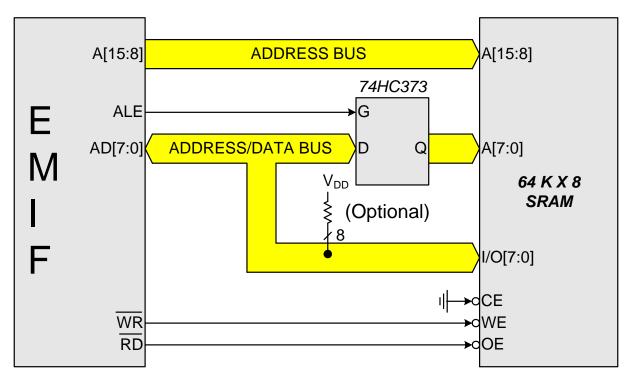

#### 18.4. Multiplexed and Non-multiplexed Selection

The External Memory Interface is capable of acting in a Multiplexed mode or a Non-multiplexed mode, depending on the state of the EMD2 (EMI0CF.4) bit.

#### 18.4.1. Multiplexed Configuration

In Multiplexed mode, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. In this mode, an external latch (74HC373 or equivalent logic gate) is used to hold the lower 8-bits of the RAM address. The external latch is controlled by the ALE (Address Latch Enable) signal, which is driven by the External Memory Interface logic. An example of a Multiplexed Configuration is shown in Figure 18.1.

In Multiplexed mode, the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the Q outputs reflect the states of the 'D' inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time RD or WR is asserted.

See Section "18.6.2. Multiplexed Mode" on page 123 for more information.

Figure 18.1. Multiplexed Configuration Example

### Table 20.2. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Page      | Description                        | Page |  |  |

|----------|---------|-----------|------------------------------------|------|--|--|

| CS0CN    | 0x9A    | 0         | CS0 Control                        | 88   |  |  |

| CS0DH    | 0xAA    | 0         | CS0 Data High                      | 90   |  |  |

| CS0DL    | 0xA9    | 0         | CS0 Data Low                       | 90   |  |  |

| CS0CF    | 0x9E    | 0         | CS0 Configuration                  | 89   |  |  |

| CS0MD1   | 0xAD    | 0         | CS0 Mode 1                         | 94   |  |  |

| CS0MD2   | 0xBE    | F         | CS0 Mode 2                         | 95   |  |  |

| CSOMX    | 0x9C    | 0         | CS0 Mux                            | 97   |  |  |

| CS0PM    | 0x9F    | F         | CS0 Pin Monitor                    | 93   |  |  |

| CS0SE    | 0x93    | F         | Auto Scan End Channel              | 91   |  |  |

| CS0SS    | 0x92    | F         | Auto Scan Start Channel            | 91   |  |  |

| CS0THH   | 0x97    | 0         | CS0 Digital Compare Threshold High | 92   |  |  |

| CS0THL   | 0x96    | 0         | CS0 Digital Compare Threshold Low  | 92   |  |  |

| DERIVID  | 0xEC    | F         | Derivative Identification          | 128  |  |  |

| DPH      | 0x83    | All Pages | Data Pointer High                  | 104  |  |  |

| DPL      | 0x82    | All Pages | Data Pointer Low                   | 104  |  |  |

| EEADDR   | 0xB6    | All Pages | EEPROM Byte Address                | 156  |  |  |

| EECNTL   | 0xC5    | F         | EEPROM Control                     | 158  |  |  |

| EEDATA   | 0xD1    | All Pages | EEPROM Byte Data                   | 157  |  |  |

| EEKEY    | 0xC6    | F         | EEPROM Protect Key                 | 159  |  |  |

| EIE1     | 0xE6    | All Pages | Extended Interrupt Enable 1        | 142  |  |  |

| EIE2     | 0xE7    | All Pages | Extended Interrupt Enable 2        | 143  |  |  |

| EIP1     | 0xCE    | F         | Extended Interrupt Priority 1      | 144  |  |  |

| EIP2     | 0xCF    | F         | Extended Interrupt Priority 2      | 145  |  |  |

| EMI0CF   | 0xC7    | F         | EMIF Configuration                 | 114  |  |  |

| EMIOCN   | 0xAA    | F         | EMIF Control                       | 113  |  |  |

| EMIOTC   | 0xEE    | F         | EMIF Timing Control                | 119  |  |  |

| FLKEY    | 0xB7    | All Pages | Flash Lock And Key                 | 154  |  |  |

| HWID     | 0xC4    | F         | Hardware Identification            | 128  |  |  |

| IE       | 0xA8    | All Pages | Interrupt Enable                   | 140  |  |  |

| IP       | 0xB8    | All Pages | Interrupt Priority                 | 141  |  |  |

| IT01CF   | 0xE4    | F         | INT0/INT1 Configuration            | 147  |  |  |

| OSCICL   | 0xBF    | F         | Internal Oscillator Calibration    | 173  |  |  |

| OSCICN   | 0xA9    | F         | Internal Oscillator Control        | 174  |  |  |

| OSCXCN   | 0xB5    | F         | External Oscillator Control        | 176  |  |  |

| P0       | 0x80    | All Pages | Port 0 Latch                       | 195  |  |  |

| P0DRV    | 0xF9    | F         | Port 0 Drive Strength              | 197  |  |  |

| POMASK   | 0xF4    | 0         | Port 0 Mask                        | 192  |  |  |

| POMAT    | 0xF3    | 0         | Port 0 Match                       | 193  |  |  |

### SFR Definition 21.6. EIP2: Extended Interrupt Priority 2

| Bit   | 7        | 6        | 5        | 4        | 3        | 2        | 1      | 0      |

|-------|----------|----------|----------|----------|----------|----------|--------|--------|

| Name  | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved | PSCGRT | PSCCPT |

| Туре  | R        | R        | R        | R        | R        | R        | R/W    | R/W    |

| Reset | 0        | 0        | 0        | 0        | 0        | 0        | 0      | 0      |

#### SFR Address = 0xCF; SFR Page = F

| Bit | Name     | Function                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:2 | Reserved | Must Write 000000b.                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 1   | PSCGRT   | apacitive Sense Greater Than Comparator Priority Control.                                                                                                                                                                                                                                            |  |  |  |  |  |

|     |          | <ul><li>This bit sets the priority of the Capacitive Sense Greater Than Comparator interrupt.</li><li>0: CS0 Greater Than Comparator interrupt set to low priority level.</li><li>1: CS0 Greater Than Comparator set to high priority level.</li></ul>                                               |  |  |  |  |  |

| 0   | PSCCPT   | <ul> <li>Capacitive Sense Conversion Complete Priority Control.</li> <li>This bit sets the priority of the Capacitive Sense Conversion Complete interrupt.</li> <li>0: CS0 Conversion Complete set to low priority level.</li> <li>1: CS0 Conversion Complete set to high priority level.</li> </ul> |  |  |  |  |  |

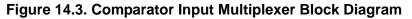

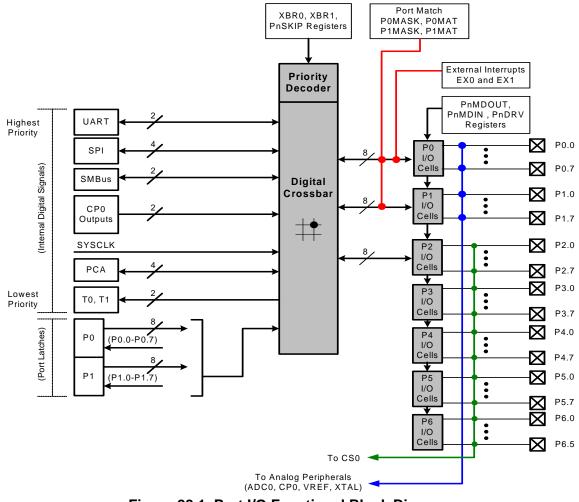

## 28. Port Input/Output

Digital and analog resources are available through 64 I/O pins. Each of the Port pins P0.0–P2.7 can be defined as general-purpose I/O (GPIO), assigned to one of the internal digital resources, or assigned to an analog function as shown in Figure 28.4. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. The state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder. The registers XBR0 and XBR1, defined in SFR Definition 28.1 and SFR Definition 28.2, are used to select internal digital functions.

All Port I/Os except P0.3 are tolerant of voltages up to 2 V above the  $V_{DD}$  supply (refer to Figure 28.2 for the Port cell circuit). The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1). Complete Electrical Specifications for Port I/O are given in Section "9. Electrical Characteristics" on page 47.

Figure 28.1. Port I/O Functional Block Diagram

overflow after 25 ms (and SMBTOE set), the Timer 3 interrupt service routine can be used to reset (disable and re-enable) the SMBus in the event of an SCL low timeout.

#### 30.3.5. SCL High (SMBus Free) Timeout

The SMBus specification stipulates that if the SCL and SDA lines remain high for more that 50  $\mu$ s, the bus is designated as free. When the SMBFTE bit in SMB0CF is set, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods (as defined by the timer configured for the SMBus clock source). If the SMBus is waiting to generate a Master START, the START will be generated following this timeout. A clock source is required for free timeout detection, even in a slave-only implementation.

#### 30.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

- Optional hardware recognition of slave address and automatic acknowledgement of address/data

SMBus interrupts are generated for each data byte or slave address that is transferred. When hardware acknowledgement is disabled, the point at which the interrupt is generated depends on whether the hardware is acting as a data transmitter or receiver. When a transmitter (i.e., sending address/data, receiving an ACK), this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data (i.e., receiving address/data, sending an ACK), this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. If hardware acknowledgement is enabled, these interrupts are always generated after the ACK cycle. See Section 30.5 for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in Section 30.4.2; Table 30.5 provides a quick SMB0CN decoding reference.

#### 30.4.1. SMBus Configuration Register

The SMBus Configuration register (SMB0CF) is used to enable the SMBus Master and/or Slave modes, select the SMBus clock source, and select the SMBus timing and timeout options. When the ENSMB bit is set, the SMBus is enabled for all master and slave events. Slave events may be disabled by setting the INH bit. With slave events inhibited, the SMBus interface will still monitor the SCL and SDA pins; however, the interface will NACK all received addresses and will not generate any slave interrupts. When the INH bit is set, all slave events will be inhibited following the next START (interrupts will continue for the duration of the current transfer).

### SFR Definition 30.2. SMB0CN: SMBus Control

| Bit   | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0   |

|-------|--------|--------|-----|-----|-------|---------|-----|-----|

| Name  | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI  |

| Туре  | R      | R      | R/W | R/W | R     | R       | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0   |

#### SFR Address = 0xC0; SFR Page = All Pages; Bit-Addressable

| Bit | Name    | Description                                                                                                                                                                                                      | Read                                                                                                                       | Write                                                                                                                                                                                |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | SMBus Master/Slave<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a master.                                                                                                     | 0: SMBus operating in<br>slave mode.<br>1: SMBus operating in<br>master mode.                                              | N/A                                                                                                                                                                                  |

| 6   | TXMODE  | SMBus Transmit Mode<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a transmitter.                                                                                               | 0: SMBus in Receiver<br>Mode.<br>1: SMBus in Transmitter<br>Mode.                                                          | N/A                                                                                                                                                                                  |

| 5   | STA     | SMBus Start Flag.                                                                                                                                                                                                | 0: No Start or repeated<br>Start detected.<br>1: Start or repeated Start<br>detected.                                      | 0: No Start generated.<br>1: When Configured as a<br>Master, initiates a START<br>or repeated START.                                                                                 |

| 4   | STO     | SMBus Stop Flag.                                                                                                                                                                                                 | 0: No Stop condition<br>detected.<br>1: Stop condition detected<br>(if in Slave Mode) or pend-<br>ing (if in Master Mode). | 0: No STOP condition is<br>transmitted.<br>1: When configured as a<br>Master, causes a STOP<br>condition to be transmit-<br>ted after the next ACK<br>cycle.<br>Cleared by Hardware. |

| 3   | ACKRQ   | SMBus Acknowledge<br>Request.                                                                                                                                                                                    | 0: No Ack requested<br>1: ACK requested                                                                                    | N/A                                                                                                                                                                                  |

| 2   | ARBLOST | SMBus Arbitration Lost<br>Indicator.                                                                                                                                                                             | 0: No arbitration error.<br>1: Arbitration Lost                                                                            | N/A                                                                                                                                                                                  |

| 1   | ACK     | SMBus Acknowledge.                                                                                                                                                                                               | 0: NACK received.<br>1: ACK received.                                                                                      | 0: Send NACK<br>1: Send ACK                                                                                                                                                          |

| 0   | SI      | <b>SMBus Interrupt Flag.</b><br>This bit is set by hardware<br>under the conditions listed in<br>Table 15.3. SI must be cleared<br>by software. While SI is set,<br>SCL is held low and the<br>SMBus is stalled. | 0: No interrupt pending<br>1: Interrupt Pending                                                                            | <ul><li>0: Clear interrupt, and initiate next state machine event.</li><li>1: Force interrupt.</li></ul>                                                                             |

| Table 30.5. SMBus Status Decoding: Hardware ACK Disabled | (EHACK = 0) | (Continued)                             |  |

|----------------------------------------------------------|-------------|-----------------------------------------|--|

|                                                          |             | ( • • • • • • • • • • • • • • • • • • • |  |

|                   | Valu                     | ies                                          | Rea                                                                                   | d                                            |                                                                                             |                                                            |     | lues<br>Vrit |      | tus<br>ected                   |

|-------------------|--------------------------|----------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------|-----|--------------|------|--------------------------------|

| Mode              | Mode<br>Status<br>Vector |                                              | ARBLOST                                                                               | ACK                                          | Current SMbus State                                                                         | Typical Response Options                                   | STA | STO          | ACK  | Next Status<br>Vector Expected |

| r                 |                          | 0                                            | 0                                                                                     | 0                                            | A slave byte was transmitted;<br>NACK received.                                             | No action required (expecting STOP condition).             | 0   | 0            | Х    | 0001                           |

| smitte            | 0100                     | 0                                            | 0                                                                                     | 1                                            | A slave byte was transmitted;<br>ACK received.                                              | Load SMB0DAT with next data byte to transmit.              | 0   | 0            | Х    | 0100                           |

| Slave Transmitter |                          | 0                                            | 1                                                                                     | х                                            | A Slave byte was transmitted; error detected.                                               | No action required (expecting Master to end transfer).     | 0   | 0            | Х    | 0001                           |

| Slav              | 0101                     | 0                                            | x                                                                                     | x                                            | An illegal STOP or bus error<br>was detected while a Slave<br>Transmission was in progress. | Clear STO.                                                 | 0   | 0            | Х    | _                              |

|                   |                          |                                              |                                                                                       |                                              |                                                                                             | If Write, Acknowledge received address                     | 0   | 0            | 1    | 0000                           |

|                   |                          | 1                                            | 0                                                                                     | Х                                            | A slave address + R/W was received; ACK requested.                                          | If Read, Load SMB0DAT with data byte; ACK received address | 0   | 0            | 1    | 0100                           |

|                   |                          |                                              |                                                                                       |                                              |                                                                                             | NACK received address.                                     | 0   | 0            | 0    | _                              |

|                   | 0010                     |                                              |                                                                                       |                                              |                                                                                             | If Write, Acknowledge received address                     | 0   | 0            | 1    | 0000                           |

| iver              |                          | 1                                            | 1                                                                                     | х                                            | Lost arbitration as master;<br>slave address + R/W received;                                | If Read, Load SMB0DAT with data byte; ACK received address | 0   | 0            | 1    | 0100                           |

| tece              |                          |                                              |                                                                                       |                                              | ACK requested.                                                                              | NACK received address.                                     | 0   | 0            | 0    |                                |

| Slave Receiver    |                          |                                              |                                                                                       |                                              |                                                                                             | Reschedule failed transfer;<br>NACK received address.      | 1   | 0            | 0    | 1110                           |

|                   | 0 0 X addressed as       |                                              | A STOP was detected while<br>addressed as a Slave Trans-<br>mitter or Slave Receiver. | Clear STO.                                   | 0                                                                                           | 0                                                          | Х   | —            |      |                                |

|                   |                          | 11XLost arbitration while attempting a STOP. |                                                                                       |                                              | No action required (transfer complete/aborted).                                             | 0                                                          | 0   | 0            | —    |                                |

|                   | 0000                     |                                              |                                                                                       | A slave byte was received;<br>ACK requested. | Acknowledge received byte;<br>Read SMB0DAT.                                                 | 0                                                          | 0   | 1            | 0000 |                                |

|                   |                          |                                              |                                                                                       |                                              |                                                                                             | NACK received byte.                                        | 0   | 0            | 0    | —                              |

## SFR Definition 33.9. TMR2RLL: Timer 2 Reload Register Low Byte

| Bit                              | 7           | 6                                             | 5        | 4 | 3 | 2 | 1 | 0 |

|----------------------------------|-------------|-----------------------------------------------|----------|---|---|---|---|---|

| Name TMR2RLL[7:0]                |             |                                               |          |   |   |   |   |   |

| Туре                             | •           | R/W                                           |          |   |   |   |   |   |

| Rese                             | et O        | 0                                             | 0        | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0xCA; SFR Page = 0 |             |                                               |          |   |   |   |   |   |

| Bit                              | Name        |                                               | Function |   |   |   |   |   |

| 7:0                              | TMR2RLL[7:0 | MR2RLL[7:0] Timer 2 Reload Register Low Byte. |          |   |   |   |   |   |

TMR2RLL holds the low byte of the reload value for Timer 2.

### SFR Definition 33.10. TMR2RLH: Timer 2 Reload Register High Byte

| Bit   | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6            | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---|---|---|---|---|---|

| Name  | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TMR2RLH[7:0] |   |   |   |   |   |   |

| Туре  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W          |   |   |   |   |   |   |

| Rese  | Reset         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td>0</td> <td>0</td> <td>0</td> |              | 0 | 0 | 0 |   |   |   |

| SFR A | SFR Address = 0xCB; SFR Page = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |   |   |   |   |   |   |

| Bit   | Name Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |   |   |   |   |   |   |

| Dit | Hamo         | i unotioni                                                   |

|-----|--------------|--------------------------------------------------------------|

| 7:0 | TMR2RLH[7:0] | Timer 2 Reload Register High Byte.                           |

|     |              | TMR2RLH holds the high byte of the reload value for Timer 2. |

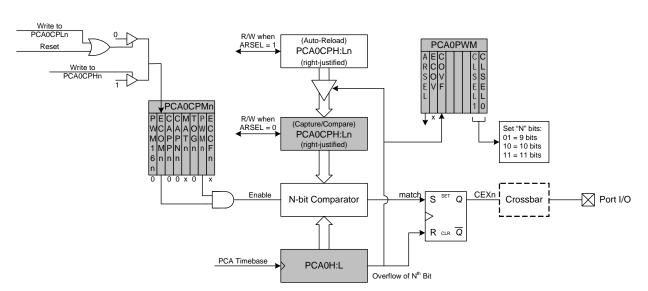

#### 34.3.5.2. 9/10/11-bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 9/10/11-bit PWM mode should be varied by writing to an "Auto-Reload" Register, which is dual-mapped into the PCA0CPHn and PCA0CPLn register locations. The data written to define the duty cycle should be right-justified in the registers. The auto-reload registers are accessed (read or written) when the bit ARSEL in PCA0PWM is set to 1. The capture/compare registers are accessed when ARSEL is set to 0.

When the least-significant N bits of the PCA0 counter match the value in the associated module's capture/compare register (PCA0CPn), the output on CEXn is asserted high. When the counter overflows from the Nth bit, CEXn is asserted low (see Figure 34.9). Upon an overflow from the Nth bit, the COVF flag is set, and the value stored in the module's auto-reload register is loaded into the capture/compare register. The value of N is determined by the CLSEL bits in register PCA0PWM.

The 9, 10 or 11-bit PWM mode is selected by setting the ECOMn and PWMn bits in the PCA0CPMn register, and setting the CLSEL bits in register PCA0PWM to the desired cycle length (other than 8-bits). If the MATn bit is set to 1, the CCFn flag for the module will be set each time a comparator match (rising edge) occurs. The COVF flag in PCA0PWM can be used to detect the overflow (falling edge), which will occur every 512 (9-bit), 1024 (10-bit) or 2048 (11-bit) PCA clock cycles. The duty cycle for 9/10/11-Bit PWM Mode is given in Equation 34.2, where N is the number of bits in the PWM cycle.

**Important Note About PCA0CPHn and PCA0CPLn Registers**: When writing a 16-bit value to the PCA0CPn registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(2^N - PCA0CPn)}{2^N}$$

Equation 34.3. 9, 10, and 11-Bit PWM Duty Cycle

A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 34.9. PCA 9, 10 and 11-Bit PWM Mode Diagram

### 34.4. Register Descriptions for PCA0

Following are detailed descriptions of the special function registers related to the operation of the PCA.

### SFR Definition 34.1. PCA0CN: PCA Control

| Bit   | 7   | 6   | 5 | 4 | 3 | 2    | 1    | 0    |

|-------|-----|-----|---|---|---|------|------|------|

| Name  | CF  | CR  |   |   |   | CCF2 | CCF1 | CCF0 |

| Туре  | R/W | R/W | R | R | R | R/W  | R/W  | R/W  |

| Reset | 0   | 0   | 0 | 0 | 0 | 0    | 0    | 0    |

SFR Address = 0xD8; SFR Page = All Pages; Bit-Addressable

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                           |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CF       | PCA Counter/Timer Overflow Flag.                                                                                                                                                                                                                                                                                   |

|     |          | Set by hardware when the PCA Counter/Timer overflows from 0xFFFF to 0x0000.<br>When the Counter/Timer Overflow (CF) interrupt is enabled, setting this bit causes the<br>CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared<br>by hardware and must be cleared by software. |

| 6   | CR       | PCA Counter/Timer Run Control.                                                                                                                                                                                                                                                                                     |

|     |          | This bit enables/disables the PCA Counter/Timer.                                                                                                                                                                                                                                                                   |

|     |          | 0: PCA Counter/Timer disabled.                                                                                                                                                                                                                                                                                     |

|     |          | 1: PCA Counter/Timer enabled.                                                                                                                                                                                                                                                                                      |

| 5:3 | Unused   | Read = 000b; Write = Don't care                                                                                                                                                                                                                                                                                    |

| 2:0 | CCF[2:0] | PCA Module n Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |

|     |          | These bits are set by hardware when a match or capture occurs in the associated PCA Module n. When the CCFn interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.               |

## C2 Register Definition 35.2. DEVICEID: C2 Device ID

| Bit   | 7             | 6                                                                          | 5          | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|---------------|----------------------------------------------------------------------------|------------|---|---|---|---|---|--|--|--|--|

| Nam   | DEVICEID[7:0] |                                                                            |            |   |   |   |   |   |  |  |  |  |

| Туре  | e             | R/W                                                                        |            |   |   |   |   |   |  |  |  |  |

| Rese  | et O          | 0                                                                          | 0          | 1 | 1 | 1 | 1 | 0 |  |  |  |  |

| C2 Ad | dress: 0x00   |                                                                            |            |   |   | L |   | L |  |  |  |  |

| Bit   | Name          |                                                                            | Function   |   |   |   |   |   |  |  |  |  |

| 7:0   | DEVICEID[7:0  | ] Device II                                                                | Device ID. |   |   |   |   |   |  |  |  |  |

|       |               | This read-only register returns the 8-bit device ID: 0x1E (C8051F70x/71x). |            |   |   |   |   |   |  |  |  |  |

### C2 Register Definition 35.3. REVID: C2 Revision ID

| Bit              | 7          | 6                                                                                      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |  |

|------------------|------------|----------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|--|--|

| Nam              | е          | REVID[7:0]                                                                             |        |        |        |        |        |        |  |  |  |  |

| Туре             | e          | R/W                                                                                    |        |        |        |        |        |        |  |  |  |  |

| Rese             | et Varies  | Varies                                                                                 | Varies | Varies | Varies | Varies | Varies | Varies |  |  |  |  |

| C2 Address: 0x01 |            |                                                                                        |        |        |        |        |        |        |  |  |  |  |

| Bit              | Name       | Function                                                                               |        |        |        |        |        |        |  |  |  |  |

| 7:0              | REVID[7:0] | <b>Revision ID</b>                                                                     |        |        |        |        |        |        |  |  |  |  |

|                  |            | This read-only register returns the 8-bit revision ID. For example: 0x00 = Revision A. |        |        |        |        |        |        |  |  |  |  |