# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Cap Sense, POR, PWM, WDT                                       |

| Number of I/O              | 20                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-WFQFN Exposed Pad                                           |

| Supplier Device Package    | 24-QFN (4x4)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f717-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## C8051F70x/71x

| SFR Definition 28.29. P4DRV: Port 4 Drive Strength               | . 206 |

|------------------------------------------------------------------|-------|

| SFR Definition 28.30. P5: Port 5                                 |       |

| SFR Definition 28.31. P5MDIN: Port 5 Input Mode                  | . 207 |

| SFR Definition 28.32. P5MDOUT: Port 5 Output Mode                | . 207 |

| SFR Definition 28.33. P5DRV: Port 5 Drive Strength               |       |

| SFR Definition 28.34. P6: Port 6                                 | . 208 |

| SFR Definition 28.35. P6MDIN: Port 6 Input Mode                  | . 209 |

| SFR Definition 28.36. P6MDOUT: Port 6 Output Mode                |       |

| SFR Definition 28.37. P6DRV: Port 6 Drive Strength               |       |

| SFR Definition 29.1. CRC0CN: CRC0 Control                        |       |

| SFR Definition 29.2. CRC0IN: CRC Data Input                      | . 216 |

| SFR Definition 29.3. CRC0DATA: CRC Data Output                   |       |

| SFR Definition 29.4. CRC0AUTO: CRC Automatic Control             |       |

| SFR Definition 29.5. CRC0CNT: CRC Automatic Flash Sector Count   |       |

| SFR Definition 29.6. CRC0FLIP: CRC Bit Flip                      |       |

| SFR Definition 30.1. SMB0CF: SMBus Clock/Configuration           | . 225 |

| SFR Definition 30.2. SMB0CN: SMBus Control                       | . 227 |

| SFR Definition 30.3. SMB0ADR: SMBus Slave Address                |       |

| SFR Definition 30.4. SMB0ADM: SMBus Slave Address Mask           |       |

| SFR Definition 30.5. SMB0DAT: SMBus Data                         |       |

| SFR Definition 31.1. SPI0CFG: SPI0 Configuration                 |       |

| SFR Definition 31.2. SPI0CN: SPI0 Control                        |       |

| SFR Definition 31.3. SPI0CKR: SPI0 Clock Rate                    |       |

| SFR Definition 31.4. SPI0DAT: SPI0 Data                          |       |

| SFR Definition 32.1. SCON0: Serial Port 0 Control                |       |

| SFR Definition 32.2. SBUF0: Serial (UART0) Port Data Buffer      |       |

| SFR Definition 33.1. CKCON: Clock Control                        |       |

| SFR Definition 33.2. TCON: Timer Control                         |       |

| SFR Definition 33.3. TMOD: Timer Mode                            |       |

| SFR Definition 33.4. TL0: Timer 0 Low Byte                       |       |

| SFR Definition 33.5. TL1: Timer 1 Low Byte                       |       |

| SFR Definition 33.6. TH0: Timer 0 High Byte                      |       |

| SFR Definition 33.7. TH1: Timer 1 High Byte                      |       |

| SFR Definition 33.8. TMR2CN: Timer 2 Control                     | 275   |

| SFR Definition 33.9. TMR2RLL: Timer 2 Reload Register Low Byte   |       |

| SFR Definition 33.10. TMR2RLH: Timer 2 Reload Register High Byte |       |

| SFR Definition 33.11. TMR2L: Timer 2 Low Byte                    |       |

| SFR Definition 33.12. TMR2H Timer 2 High Byte                    |       |

| SFR Definition 33.13. TMR3CN: Timer 3 Control                    |       |

| SFR Definition 33.14. TMR3RLL: Timer 3 Reload Register Low Byte  |       |

| SFR Definition 33.15. TMR3RLH: Timer 3 Reload Register High Byte |       |

| SFR Definition 33.16. TMR3L: Timer 3 Low Byte                    |       |

| SFR Definition 33.17. TMR3H Timer 3 High Byte                    |       |

| SFR Definition 34.1. PCA0CN: PCA Control                         |       |

| SFR Definition 34.2. PCA0MD: PCA Mode                            |       |

|                                                                  |       |

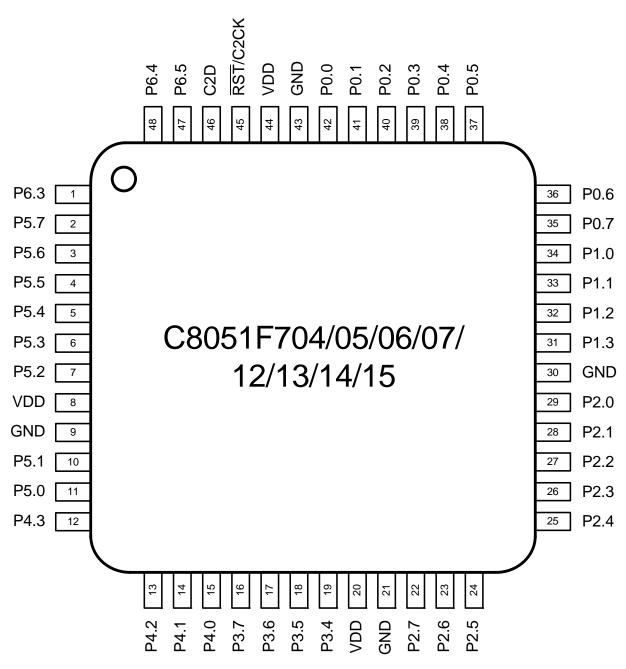

Figure 3.2. C8051F7xx-GQ QFP48 Pinout Diagram (Top View)

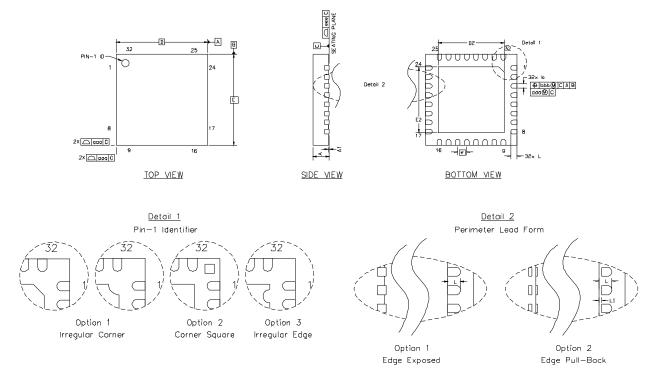

## 7. QFN-32 Package Specifications

Figure 7.1. QFN-32 Package Drawing

| Dimension | Min  | Тур       | Max  | ] | Dimension | Min  | Тур  | Мах  |

|-----------|------|-----------|------|---|-----------|------|------|------|

| A         | 0.80 | 0.90      | 1.00 | 1 | E2        | 3.50 | 3.60 | 3.70 |

| A1        | 0.00 | 0.02      | 0.05 | 1 | L         | 0.30 | 0.35 | 0.40 |

| b         | 0.18 | 0.25      | 0.30 |   | L1        | 0.00 | —    | 0.10 |

| D         |      | 5.00 BSC. |      |   | aaa       |      | 0.15 | •    |

| D2        | 3.50 | 3.60      | 3.70 |   | bbb       |      | 0.10 |      |

| е         |      | 0.50 BSC. |      |   | ddd       |      | 0.05 |      |

| E         |      | 5.00 BSC. |      | 1 | eee       |      | 0.08 |      |

## Table 7.1. QFN-32 Package Dimensions

Notes:

**1.** All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation VHHD except for custom features D2, E2, L and L1 which are toleranced per supplier designation.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## **10.4. Programmable Window Detector**

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

## SFR Definition 10.5. ADC0GTH: ADC0 Greater-Than Data High Byte

| Bit                              | 7            | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------------------|--------------|-----|---|---|---|---|---|---|

| Name                             | ADC0GTH[7:0] |     |   |   |   |   |   |   |

| Туре                             |              | R/W |   |   |   |   |   |   |

| Reset                            | 1            | 1   | 1 | 1 | 1 | 1 | 1 | 1 |

| SFR Address = 0xC4; SFR Page = 0 |              |     |   |   |   |   |   |   |

| Bit                              |              |     |   |   |   |   |   |   |

## 7:0 ADC0GTH[7:0] ADC0 Greater-Than Data Word High-Order Bits.

## SFR Definition 10.6. ADC0GTL: ADC0 Greater-Than Data Low Byte

| Bit   | 7                 | 6          | 5                                           | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-------------------|------------|---------------------------------------------|---|---|---|---|---|--|--|

| Nam   | Name ADC0GTL[7:0] |            |                                             |   |   |   |   |   |  |  |

| Туре  | R/W               |            |                                             |   |   |   |   |   |  |  |

| Rese  | et 1              | 1          |                                             |   |   |   |   |   |  |  |

| SFR A | Address = 0xC3    | ; SFR Page | e = 0                                       |   |   |   |   |   |  |  |

| Bit   | Name              |            | Function                                    |   |   |   |   |   |  |  |

| 7:0   | ADC0GTL[7:0       | ADC0 G     | ADC0 Greater-Than Data Word Low-Order Bits. |   |   |   |   |   |  |  |

## SFR Definition 13.1. REG0CN: Voltage Regulator Control

| Bit   | 7      | 6      | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------|--------|-----|-----|-----|-----|-----|-----|

| Name  | STOPCF | BYPASS |     |     |     |     |     |     |

| Туре  | R/W    | R/W    | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0   | 0   | 0   | 0   |

## SFR Address = 0xB9; SFR Page = F

| Bit | Name     | Function                                                                                                                                                                                                                                                                                |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | STOPCF   | Stop Mode Configuration.                                                                                                                                                                                                                                                                |

|     |          | This bit configures the regulator's behavior when the device enters STOP mode.<br>0: Regulator is still active in STOP mode. Any enabled reset source will reset the<br>device.<br>1: Regulator is shut down in STOP mode. Only the RST pin or power cycle can reset                    |

|     |          | the device.                                                                                                                                                                                                                                                                             |

| 6   | BYPASS   | Bypass Internal Regulator.                                                                                                                                                                                                                                                              |

|     |          | This bit places the regulator in bypass mode, allowing the core to run directly from the $V_{DD}$ supply pin.                                                                                                                                                                           |

|     |          | 0: Normal Mode—Regulator is on and regulates V <sub>DD</sub> down to the core voltage.                                                                                                                                                                                                  |

|     |          | 1: Bypass Mode—Regulator is in bypass mode, and the microcontroller core operates directly from the V <sub>DD</sub> supply voltage.                                                                                                                                                     |

|     |          | IMPORTANT: Bypass mode is for use with an external regulator as the supply voltage only. Never place the regulator in bypass mode when the $V_{DD}$ supply voltage is greater than the specifications given in Table 9.1 on page 47. Doing so may cause permanent damage to the device. |

| 5:0 | Reserved | Reserved. Must Write 000000b.                                                                                                                                                                                                                                                           |

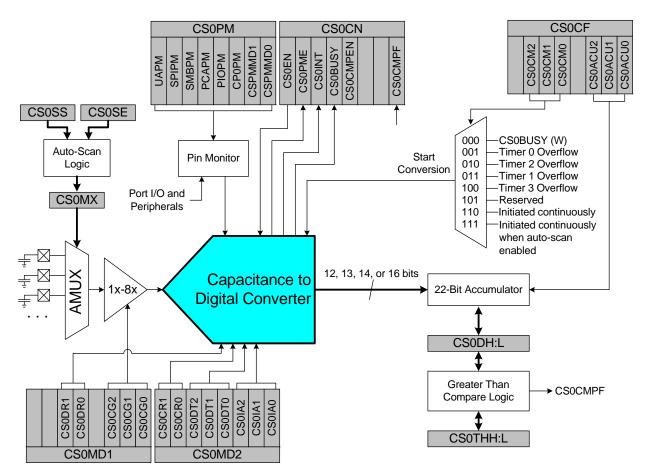

## 15. Capacitive Sense (CS0)

The Capacitive Sense subsystem uses a capacitance-to-digital circuit to determine the capacitance on a port pin. The module can take measurements from different port pins using the module's analog multiplexer. The module is enabled only when the CS0EN bit (CS0CN) is set to 1. Otherwise the module is in a low-power shutdown state. The module can be configured to take measurements on one port pin or a group of port pins, using auto-scan. A selectable gain circuit allows the designer to adjust the maximum allowable capacitance. An accumulator is also included, which can be configured to average multiple conversions on an input channel. Interrupts can be generated when CS0 completes a conversion or when the measured value crosses a threshold defined in CS0THH:L.

Figure 15.1. CS0 Block Diagram

If CS0BUSY is used to initiate conversions, and then polled to determine if the conversion is finished, at least one clock cycle must be inserted between setting CS0BUSY to 1 and polling the CS0BUSY bit.

Conversions can be configured to be initiated continuously through one of two methods. CS0 can be configured to convert at a single channel continuously or it can be configured to convert continuously with auto-scan enabled. When configured to convert continuously, conversions will begin after the CS0BUSY bit in CS0CF has been set. An interrupt will be generated if CS0 conversion complete interrupts are enabled by setting the ECSCPT bit (EIE2.0).

The CS0 module uses a method of successive approximation to determine the value of an external capacitance. The number of bits the CS0 module converts is adjustable using the CS0CR bits in register CS0MD2. Conversions are 13 bits long by default, but they can be adjusted to 12, 13, 14, or 16 bits depending on the needs of the application. Unconverted bits will be set to 0. Shorter conversion lengths produce faster conversion rates, and vice-versa. Applications can take advantage of faster conversion rates when the unconverted bits fall below the noise floor.

**Note:** CS0 conversion complete interrupt behavior depends on the settings of the CS0 accumulator. If CS0 is configured to accumulate multiple conversions on an input channel, a CS0 conversion complete interrupt will be generated only after the last conversion completes.

## 15.7. CS0 Pin Monitor

The CS0 module provides accurate conversions in all operating modes of the CPU, peripherals and I/O ports. Pin monitoring circuits are provided to improve interference immunity from high-current output pin switching. The Capacitive Sense Pin Monitor register (CS0PM, SFR Definition 15.9) controls the operation of these pin monitors.

Conversions in the CS0 module are immune to any change on digital inputs and immune to most output switching. Even high-speed serial data transmission will not affect CS0 operation as long as the output load is limited. Output changes that switch large loads such as LEDs and heavily-loaded communications lines can affect conversion accuracy. For this reason, the CS0 module includes pin monitoring circuits that will, if enabled, automatically adjust conversion timing if necessary to eliminate any effect from high-current output pin switching.

The pin monitor enable bit should be set for any output signal that is expected to drive a large load.

Example: The SMBus in a system is heavily loaded with multiple slaves and a long PCB route. Set the SMBus pin monitor enable, SMBPM = 1.

Example: Timer2 controls an LED on Port 1, pin 3 to provide variable dimming. Set the Port SFR write monitor enable, PIOPM = 1.

Example: The SPI bus is used to communicate to a nearby host. The pin monitor is not needed because the output is not heavily loaded, SPIPM remains = 0, the default reset state.

Pin monitors should not be enabled unless they are required. The pin monitor works by repeating any portion of a conversion that may have been corrupted by a change on an output pin. Setting pin monitor enables bits will slow CS0 conversions.

The frequency of CS0 retry operations can be limited by setting the CSPMMD bits. In the default (reset) state, all converter retry requests will be performed. This is the recommended setting for all applications. The number of retries per conversion can be limited to either two or four retries by changing CSPMMD. Limiting the number of retries per conversion ensures that even in circumstances where extremely frequent high-power output switching occurs, conversions will be completed, though there may be some loss of accuracy due to switching noise.

Activity of the pin monitor circuit can be detected by reading the Pin Monitor Event bit, CS0PME, in register CS0CN. This bit will be set if any CS0 converter retries have occurred. It remains set until cleared by software or a device reset.

## C8051F70x/71x

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

## 16.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

### 16.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 16.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

## 17.1. Program Memory

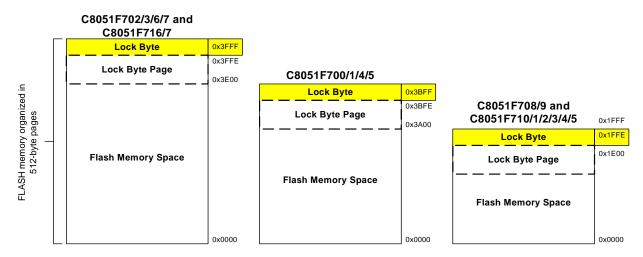

The members of the C8051F70x/71x device family contain 16 kB (C8051F702/3/6/7 and C8051F16/7), 15 kB (C8051F700/1/4/5), or 8 kB (C8051F708/9 and C8051F710/1/2/3/4/5) of re-programmable Flash memory that can be used as non-volatile program or data storage. The last byte of user code space is used as the security lock byte (0x3FFF on 16 kB devices, 0x3BFF on 15 kB devices and 0x1FFF on 8 kB devices).

Figure 17.2. Flash Program Memory Map

## 17.1.1. MOVX Instruction and Program Memory

The MOVX instruction in an 8051 device is typically used to access external data memory. On the C8051F70x/71x devices, the MOVX instruction is normally used to read and write on-chip XRAM, but can be re-configured to write and erase on-chip Flash memory space. MOVC instructions are always used to read Flash memory, while MOVX write instructions are used to erase and write Flash. This Flash access feature provides a mechanism for the C8051F70x/71x to update program code and use the program memory space for non-volatile data storage. Refer to Section "22. Flash Memory" on page 148 for further details.

## 17.2. EEPROM Memory

The C8051F700/1/4/5/8/9 and C8051F712/3 contain EEPROM emulation hardware, which uses Flash memory to emulate a 32-byte EEPROM memory space for non-volatile data storage. The EEPROM data is accessed through a RAM buffer for increased speed. More details about the EEPROM can be found in Section "23. EEPROM" on page 155.

## 17.3. Data Memory

The C8051F70x/71x device family includes 512 bytes of RAM data memory. 256 bytes of this memory is mapped into the internal RAM space of the 8051. 256 bytes of this memory is on-chip "external" memory. The data memory map is shown in Figure 17.1 for reference.

### 17.3.1. Internal RAM

There are 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight

## SFR Definition 18.3. EMI0TC: External Memory Timing Control

| Bit          | 7            | 6                          | 5                            | 4          | 3        | 2 | 1   | 0      |  |  |

|--------------|--------------|----------------------------|------------------------------|------------|----------|---|-----|--------|--|--|

| Nam          | e EA         | S[1:0]                     |                              | EW         | R[3:0]   |   | EAH | I[1:0] |  |  |

| Type R/W R/W |              |                            |                              | /W         |          | R | /W  |        |  |  |

| Rese         | et 1         | 1                          | 1                            | 1          | 1        | 1 | 1   | 1      |  |  |

| SFR A        | ddress = 0xE | EE; SFR Page               | e = F                        |            |          |   |     | II     |  |  |

| Bit          | Name         |                            |                              |            | Function |   |     |        |  |  |

| 7:6          | EAS[1:0]     | EMIF Addre                 | ss Setup Ti                  | me Bits.   |          |   |     |        |  |  |

|              |              | 00: Address                | setup time =                 | = 0 SYSCLK | cycles.  |   |     |        |  |  |

|              |              | 01: Address                | setup time =                 | = 1 SYSCLK | cycle.   |   |     |        |  |  |

|              |              | 10: Address                | •                            |            | •        |   |     |        |  |  |

|              |              | 11: Address                | setup time =                 | = 3 SYSCLK | cycles.  |   |     |        |  |  |

| 5:2          | EWR[3:0]     | EMIF WR an                 |                              |            |          |   |     |        |  |  |

|              |              | 0000: WR ar                |                              |            |          |   |     |        |  |  |

|              |              | 0001: <u>WR</u> ar         |                              |            |          |   |     |        |  |  |

|              |              | 0010: WR ar                |                              |            |          |   |     |        |  |  |

|              |              | 0011: WR ar<br>0100: WR ar |                              |            | •        |   |     |        |  |  |

|              |              | 0100: WR an                |                              |            |          |   |     |        |  |  |

|              |              | 0110: WR ar                |                              |            | •        |   |     |        |  |  |

|              |              | 0111: WR an                |                              |            | •        |   |     |        |  |  |

|              |              | 1000: WR ar                |                              |            | •        |   |     |        |  |  |

|              |              | 1001: <u>WR</u> ar         |                              |            |          |   |     |        |  |  |

|              |              | 1010: WR ar                |                              |            | •        |   |     |        |  |  |

|              |              | 1011: WR ar<br>1100: WR ar |                              |            |          |   |     |        |  |  |

|              |              | 1100. WR an<br>1101: WR ar |                              |            |          |   |     |        |  |  |

|              |              | 1110: WR an                |                              |            |          |   |     |        |  |  |

|              |              | 1111: WR an                |                              |            |          |   |     |        |  |  |

| 1:0          | EAH[1:0]     | EMIF Addre                 | EMIF Address Hold Time Bits. |            |          |   |     |        |  |  |

|              |              | 00: Address                |                              |            | •        |   |     |        |  |  |

|              |              | 01: Address                |                              |            | •        |   |     |        |  |  |

|              |              | 10: Address                |                              |            | •        |   |     |        |  |  |

|              |              | 11: Address                | nola time =                  | 3 SYSULK C | cycles.  |   |     |        |  |  |

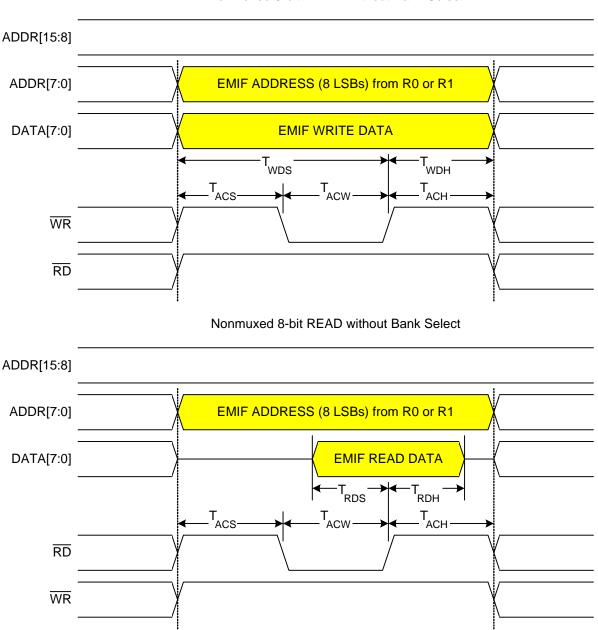

Nonmuxed 8-bit WRITE without Bank Select

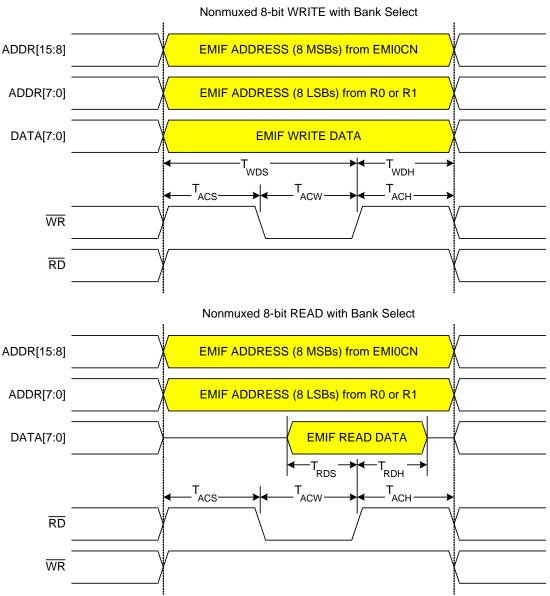

### 18.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110

Figure 18.6. Non-Multiplexed 8-Bit MOVX with Bank Select Timing

## SFR Definition 21.2. IP: Interrupt Priority

| Bit   | 7 | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---|-------|-----|-----|-----|-----|-----|-----|

| Name  |   | PSPI0 | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 |

| Туре  | R | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 1 | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Address = 0xB8; SFR Page = All Pages; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                 |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused | Read = 1b, Write = Don't Care.                                                                                                                                                                                           |

| 6   | PSPI0  | Serial Peripheral Interface (SPI0) Interrupt Priority Control.<br>This bit sets the priority of the SPI0 interrupt.<br>0: SPI0 interrupt set to low priority level.<br>1: SPI0 interrupt set to high priority level.     |

| 5   | PT2    | Timer 2 Interrupt Priority Control.This bit sets the priority of the Timer 2 interrupt.0: Timer 2 interrupt set to low priority level.1: Timer 2 interrupt set to high priority level.                                   |

| 4   | PS0    | UART0 Interrupt Priority Control.<br>This bit sets the priority of the UART0 interrupt.<br>0: UART0 interrupt set to low priority level.<br>1: UART0 interrupt set to high priority level.                               |

| 3   | PT1    | Timer 1 Interrupt Priority Control.This bit sets the priority of the Timer 1 interrupt.0: Timer 1 interrupt set to low priority level.1: Timer 1 interrupt set to high priority level.                                   |

| 2   | PX1    | External Interrupt 1 Priority Control.<br>This bit sets the priority of the External Interrupt 1 interrupt.<br>0: External Interrupt 1 set to low priority level.<br>1: External Interrupt 1 set to high priority level. |

| 1   | PT0    | Timer 0 Interrupt Priority Control.This bit sets the priority of the Timer 0 interrupt.0: Timer 0 interrupt set to low priority level.1: Timer 0 interrupt set to high priority level.                                   |

| 0   | PX0    | External Interrupt 0 Priority Control.<br>This bit sets the priority of the External Interrupt 0 interrupt.<br>0: External Interrupt 0 set to low priority level.<br>1: External Interrupt 0 set to high priority level. |

## 25.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

## 25.6. Watchdog Timer Reset

The programmable Watchdog Timer (WDT) can be used to prevent software from running out of control during a system malfunction. The WDT function can be enabled or disabled by software as described in Section "26. Watchdog Timer" on page 169. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.3) is set to 1. The state of the RST pin is unaffected by this reset.

## 25.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address above address 0x3DFF.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above address 0x3DFF.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above 0x3DFF.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "22.3. Security Options" on page 149).

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

### 25.8. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the RST pin is unaffected by this reset.

## C8051F70x/71x

overflow after 25 ms (and SMBTOE set), the Timer 3 interrupt service routine can be used to reset (disable and re-enable) the SMBus in the event of an SCL low timeout.

#### 30.3.5. SCL High (SMBus Free) Timeout

The SMBus specification stipulates that if the SCL and SDA lines remain high for more that 50  $\mu$ s, the bus is designated as free. When the SMBFTE bit in SMB0CF is set, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods (as defined by the timer configured for the SMBus clock source). If the SMBus is waiting to generate a Master START, the START will be generated following this timeout. A clock source is required for free timeout detection, even in a slave-only implementation.

### 30.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

- Optional hardware recognition of slave address and automatic acknowledgement of address/data

SMBus interrupts are generated for each data byte or slave address that is transferred. When hardware acknowledgement is disabled, the point at which the interrupt is generated depends on whether the hardware is acting as a data transmitter or receiver. When a transmitter (i.e., sending address/data, receiving an ACK), this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data (i.e., receiving address/data, sending an ACK), this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. If hardware acknowledgement is enabled, these interrupts are always generated after the ACK cycle. See Section 30.5 for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in Section 30.4.2; Table 30.5 provides a quick SMB0CN decoding reference.

#### 30.4.1. SMBus Configuration Register

The SMBus Configuration register (SMB0CF) is used to enable the SMBus Master and/or Slave modes, select the SMBus clock source, and select the SMBus timing and timeout options. When the ENSMB bit is set, the SMBus is enabled for all master and slave events. Slave events may be disabled by setting the INH bit. With slave events inhibited, the SMBus interface will still monitor the SCL and SDA pins; however, the interface will NACK all received addresses and will not generate any slave interrupts. When the INH bit is set, all slave events will be inhibited following the next START (interrupts will continue for the duration of the current transfer).

| Bit     | Set by Hardware When:                                                                                                                                                                                                                                                | Cleared by Hardware When:                                                      |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| MASTER  | A START is generated.                                                                                                                                                                                                                                                | <ul> <li>A STOP is generated.</li> </ul>                                       |

| WASTER  |                                                                                                                                                                                                                                                                      | <ul> <li>Arbitration is lost.</li> </ul>                                       |

|         | <ul> <li>START is generated.</li> </ul>                                                                                                                                                                                                                              | <ul> <li>A START is detected.</li> </ul>                                       |

| TXMODE  | <ul> <li>SMB0DAT is written before the start of an</li> </ul>                                                                                                                                                                                                        | <ul> <li>Arbitration is lost.</li> </ul>                                       |

| TAMODE  | SMBus frame.                                                                                                                                                                                                                                                         | <ul> <li>SMB0DAT is not written before the start of an SMBus frame.</li> </ul> |

| STA     | <ul> <li>A START followed by an address byte is received.</li> </ul>                                                                                                                                                                                                 | <ul> <li>Must be cleared by software.</li> </ul>                               |

| STO     | <ul> <li>A STOP is detected while addressed as a<br/>slave.</li> </ul>                                                                                                                                                                                               | A pending STOP is generated.                                                   |

|         | Arbitration is lost due to a detected STOP.                                                                                                                                                                                                                          |                                                                                |

| ACKRQ   | <ul> <li>A byte has been received and an ACK<br/>response value is needed (only when<br/>hardware ACK is not enabled).</li> </ul>                                                                                                                                    | <ul> <li>After each ACK cycle.</li> </ul>                                      |

| ARBLOST | <ul> <li>A repeated START is detected as a<br/>MASTER when STA is low (unwanted<br/>repeated START).</li> <li>SCL is sensed low while attempting to<br/>generate a STOP or repeated START<br/>condition.</li> </ul>                                                  | <ul> <li>Each time SI is cleared.</li> </ul>                                   |

|         | <ul> <li>SDA is sensed low while transmitting a 1<br/>(excluding ACK bits).</li> </ul>                                                                                                                                                                               |                                                                                |

| ACK     | <ul> <li>The incoming ACK value is low<br/>(ACKNOWLEDGE).</li> </ul>                                                                                                                                                                                                 | <ul> <li>The incoming ACK value is high<br/>(NOT ACKNOWLEDGE).</li> </ul>      |

| SI      | <ul> <li>A START has been generated.</li> <li>Lost arbitration.</li> <li>A byte has been transmitted and an ACK/NACK received.</li> <li>A byte has been received.</li> <li>A START or repeated START followed by a slave address + R/W has been received.</li> </ul> | <ul> <li>Must be cleared by software.</li> </ul>                               |

|         | <ul> <li>A STOP has been received.</li> </ul>                                                                                                                                                                                                                        |                                                                                |

Table 30.3. Sources for Hardware Changes to SMB0CN

### 30.4.3. Hardware Slave Address Recognition

The SMBus hardware has the capability to automatically recognize incoming slave addresses and send an ACK without software intervention. Automatic slave address recognition is enabled by setting the EHACK bit in register SMB0ADM to 1. This will enable both automatic slave address recognition and automatic hardware ACK generation for received bytes (as a master or slave). More detail on automatic hardware ACK generation can be found in Section 30.4.2.2.

The registers used to define which address(es) are recognized by the hardware are the SMBus Slave Address register (SFR Definition 30.3) and the SMBus Slave Address Mask register (SFR Definition 30.4). A single address or range of addresses (including the General Call Address 0x00) can be specified using these two registers. The most-significant seven bits of the two registers are used to define which addresses will be ACKed. A 1 in bit positions of the slave address mask SLVM[6:0] enable a comparison between the received slave address and the hardware's slave address SLV[6:0] for those bits. A 0 in a bit of the slave address mask means that bit will be treated as a "don't care" for comparison purposes. In this

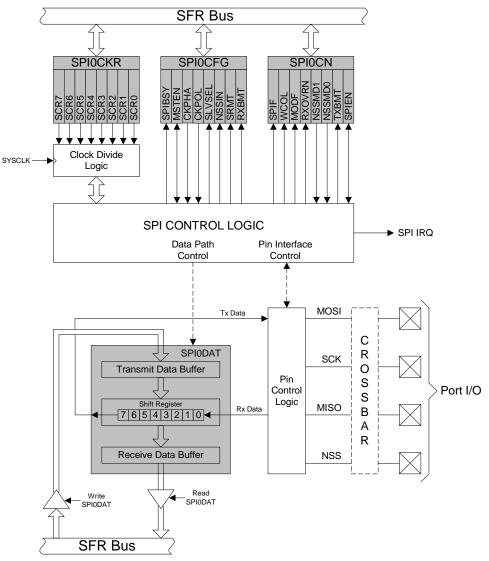

## 31. Enhanced Serial Peripheral Interface (SPI0)

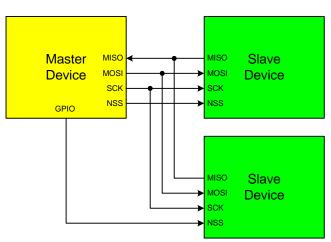

The Enhanced Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

Figure 31.4. 4-Wire Single Master Mode and Slave Mode Connection Diagram

## 31.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. The NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 31.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPI0 with the SPIEN bit. Figure 31.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

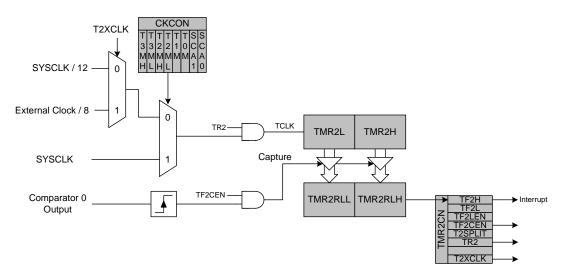

#### 33.2.3. Comparator 0 Capture Mode

The capture mode in Timer 2 allows Comparator 0 rising edges to be captured with the timer clocking from the system clock or the system clock divided by 12. Timer 2 capture mode is enabled by setting TF2CEN to 1 and T2SPLIT to 0.

When capture mode is enabled, a capture event will be generated on every Comparator 0 rising edge. When the capture event occurs, the contents of Timer 2 (TMR2H:TMR2L) are loaded into the Timer 2 reload registers (TMR2RLH:TMR2RLL) and the TF2H flag is set (triggering an interrupt if Timer 2 interrupts are enabled). By recording the difference between two successive timer capture values, the Comparator 0 period can be determined with respect to the Timer 2 clock. The Timer 2 clock should be much faster than the capture clock to achieve an accurate reading.

This mode allows software to determine the time between consecutive Comparator 0 rising edges, which can be used for detecting changes in the capacitance of a capacitive switch, or measuring the frequency of a low-level analog signal.

Figure 33.6. Timer 2 Capture Mode Block Diagram