Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, WDT                                        |

| Number of I/O              | 20                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 24-WFQFN Exposed Pad                                            |

| Supplier Device Package    | 24-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f717-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1. System Overview                                     | 17 |

|--------------------------------------------------------|----|

| 2. Ordering Information                                | 26 |

| 3. Pin Definitions                                     |    |

| 4. TQFP-64 Package Specifications                      | 37 |

| 5. TQFP-48 Package Specifications                      | 39 |

| 6. QFN-48 Package Specifications                       | 41 |

| 7. QFN-32 Package Specifications                       | 43 |

| 8. QFN-24 Package Specifications                       | 45 |

| 9. Electrical Characteristics                          | 47 |

| 9.1. Absolute Maximum Specifications                   | 47 |

| 9.2. Electrical Characteristics                        | 48 |

| 10. 10-Bit ADC (ADC0)                                  | 55 |

| 10.1. Output Code Formatting                           | 56 |

| 10.2. 8-Bit Mode                                       |    |

| 10.3. Modes of Operation                               |    |

| 10.3.1. Starting a Conversion                          | 56 |

| 10.3.2. Tracking Modes                                 | 57 |

| 10.3.3. Settling Time Requirements                     | 58 |

| 10.4. Programmable Window Detector                     | 62 |

| 10.4.1. Window Detector Example                        | 64 |

| 10.5. ADC0 Analog Multiplexer                          | 65 |

| 11. Temperature Sensor                                 | 67 |

| 11.1. Calibration                                      | 67 |

| 12. Voltage and Ground Reference Options               |    |

| 12.1. External Voltage References                      |    |

| 12.2. Internal Voltage Reference Options               |    |

| 12.3. Analog Ground Reference                          |    |

| 12.4. Temperature Sensor Enable                        |    |

| 13. Voltage Regulator (REG0)                           |    |

| 14. Comparator0                                        |    |

| 14.1. Comparator Multiplexer                           |    |

| 15. Capacitive Sense (CS0)                             |    |

| 15.1. Configuring Port Pins as Capacitive Sense Inputs |    |

| 15.2. CS0 Gain Adjustment                              | 81 |

| 15.3. Capacitive Sense Start-Of-Conversion Sources     |    |

| 15.4. Automatic Scanning                               |    |

| 15.5. CS0 Comparator                                   |    |

| 15.6. CS0 Conversion Accumulator                       |    |

| 15.7. CS0 Pin Monitor                                  |    |

| 15.8. Adjusting CS0 For Special Situations             |    |

| 15.9. Capacitive Sense Multiplexer                     |    |

| 16. CIP-51 Microcontroller                             |    |

| 16.1. Instruction Set                                  | 99 |

## 2. Ordering Information

All C8051F70x/71x devices have the following features:

- 25 MIPS (Peak)

- Calibrated Internal Oscillator

- SMBus/I<sup>2</sup>C

- UART

- Programmable counter array (3 channels)

- 4 Timers (16-bit)

- 1 Comparator

- Pb-Free (RoHS compliant) package

- 512 bytes RAM

In addition to the features listed above, each device in the C8051F70x/71x family has a set of features that vary across the product line. See Table 2.1 for a complete list of the unique feature sets for each device in the family.

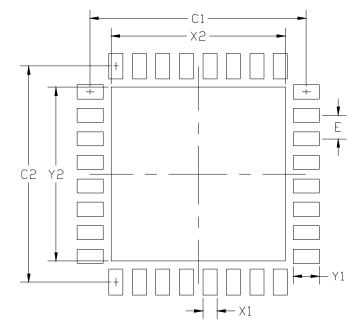

Figure 7.2. QFN-32 Recommended PCB Land Pattern

| Dimension                                                                              | Min                                                                 | Max                                                         | Dimension                                                                                                          | Min                            | Max  |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------|------|

| C1                                                                                     | 4.60                                                                |                                                             | X2                                                                                                                 | 3.60                           | 3.70 |

| C2                                                                                     | 4.                                                                  | 60                                                          | Y1                                                                                                                 | 0.45                           | 0.55 |

| E                                                                                      | 0.4                                                                 | 50                                                          | Y2                                                                                                                 | 3.60                           | 3.70 |

| X1                                                                                     | 0.20                                                                | 0.30                                                        | I                                                                                                                  |                                |      |

| <ol> <li>Dimens</li> <li>This Land</li> <li>Solder Mask D</li> <li>All meta</li> </ol> | ioning and Tolera<br>nd Pattern Desig<br>esign<br>al pads are to be | ancing is per the A<br>n is based on the<br>non-solder mask | nm) unless otherwise<br>ANSI Y14.5M-1994 sp<br>IPC-7351 guidelines<br>defined (NSMD). Cle<br>inimum, all the way a | becification.<br>arance betwee |      |

| to assur<br>6. The ste                                                                 | re good solder pa<br>ncil thickness sh<br>o of stencil apert        | aste release.<br>ould be 0.125 mm<br>ure to land pad si     | lished stencil with trap<br>n (5 mils).<br>ze should be 1:1 for a<br>5 mm pitch should be                          | all perimeter pi               | ns.  |

Table 7.2. QFN-32 PCB Land Pattern Dimensions

**10.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

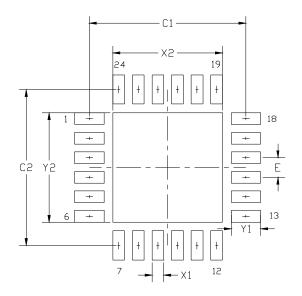

### Figure 8.2. QFN-24 Recommended PCB Land Pattern

| Table 8.2. QFN-24 PCB Land Pattern Dime | nsions |

|-----------------------------------------|--------|

|-----------------------------------------|--------|

| Dimension                                                                                    | Min  | Max  |  | Dimension | Min  | Max  |  |

|----------------------------------------------------------------------------------------------|------|------|--|-----------|------|------|--|

| C1                                                                                           | 3.90 | 4.00 |  | X2        | 2.70 | 2.80 |  |

| C2                                                                                           | 3.90 | 4.00 |  | Y1        | 0.65 | 0.75 |  |

| E                                                                                            | 0.50 | BSC  |  | Y2        | 2.70 | 2.80 |  |

| X1                                                                                           | 0.20 | 0.30 |  |           |      |      |  |

| Notes:<br>General<br>1. All dimensions shown are in millimeters (mm) unless otherwise noted. |      |      |  |           |      |      |  |

2. This Land Pattern Design is based on the IPC-7351 guidelines.

Solder Mask Design

**3.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- **6.** The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- 7. A 2x2 array of 1.10 mm x 1.10 mm openings on a 1.30 mm pitch should be used for the center pad.

Card Assembly

- 8. A No-Clean, Type-3 solder paste is recommended.

- **9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### 9. Electrical Characteristics

### 9.1. Absolute Maximum Specifications

### Table 9.1. Absolute Maximum Ratings

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                   | Conditions                                           | Min          | Тур | Max                   | Units  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------|-----|-----------------------|--------|--|--|

| Ambient temperature under bias                                                                                                                                                                                                                                                                                                                                                                              |                                                      | -55          | _   | 125                   | °C     |  |  |

| Storage Temperature                                                                                                                                                                                                                                                                                                                                                                                         |                                                      | -65          | _   | 150                   | °C     |  |  |

| Voltage on $\overline{RST}$ or any Port I/O Pin (except P0.3) with respect to GND                                                                                                                                                                                                                                                                                                                           |                                                      | -0.3         | _   | V <sub>DD</sub> + 2.0 | V      |  |  |

| Voltage on P0.3 with respect to GND                                                                                                                                                                                                                                                                                                                                                                         |                                                      | -0.3         | —   | V <sub>DD</sub> + 0.3 | V      |  |  |

| Voltage on $V_{DD}$ with respect to GND                                                                                                                                                                                                                                                                                                                                                                     | Regulator in Normal Mode<br>Regulator in Bypass Mode | -0.3<br>-0.3 | _   | 4.2<br>1.98           | V<br>V |  |  |

| Maximum Total current through V <sub>DD</sub><br>and GND                                                                                                                                                                                                                                                                                                                                                    |                                                      | —            | _   | 500                   | mA     |  |  |

| Maximum output current sunk by $\overline{RST}$ or any Port pin                                                                                                                                                                                                                                                                                                                                             |                                                      | —            | —   | 100                   | mA     |  |  |

| Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.<br>This is a stress rating only and functional operation of the devices at those or any other conditions above<br>those indicated in the operation listings of this specification is not implied. Exposure to maximum rating<br>conditions for extended periods may affect device reliability. |                                                      |              |     |                       |        |  |  |

### Table 9.11. Power Management Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified. Use factory-calibrated settings.

| Parameter                 | Conditions | Min | Тур | Max | Units   |

|---------------------------|------------|-----|-----|-----|---------|

| Idle Mode Wake-Up time    |            | 2   | -   | 3   | SYSCLKs |

| Suspend Mode Wake-Up Time |            |     | 250 |     | ns      |

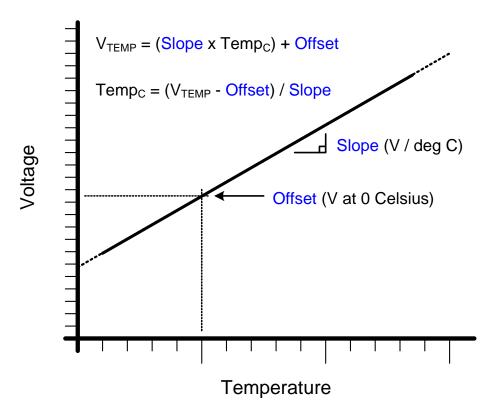

#### Table 9.12. Temperature Sensor Electrical Characteristics

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise specified.

| Parameter                                               | Conditions  | Min | Тур   | Max | Units |  |  |  |

|---------------------------------------------------------|-------------|-----|-------|-----|-------|--|--|--|

| Linearity                                               |             | _   | 1     | —   | °C    |  |  |  |

| Slope                                                   |             | —   | 3.27  | _   | mV/°C |  |  |  |

| Slope Error*                                            |             | —   | ±65   | —   | µV/°C |  |  |  |

| Offset                                                  | Temp = 0 °C | —   | 868   | —   | mV    |  |  |  |

| Offset Error*                                           | Temp = 0 °C | —   | ±15.3 | —   | mV    |  |  |  |

| *Note: Represents one standard deviation from the mean. |             |     |       |     |       |  |  |  |

### Table 9.13. Voltage Reference Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V; -40 to +85 °C unless otherwise specified.

| Parameter Conditions |                                        |          | Тур  | Max             | Units |

|----------------------|----------------------------------------|----------|------|-----------------|-------|

| lı                   | nternal High-Speed Reference (REFSL[1: | 0] = 11) |      | 1               |       |

| Output Voltage       | 25 °C ambient                          | 1.55     | 1.59 | 1.70            | V     |

| Turn-on Time         |                                        | _        | _    | 1.7             | μs    |

| Supply Current       |                                        | _        | 200  |                 | μA    |

|                      | External Reference (REF0E = 0)         |          |      |                 |       |

| Input Voltage Range  |                                        | 0        | —    | V <sub>DD</sub> |       |

| Input Current        | Sample Rate = 500 ksps; VREF = 3.0 V   |          | 7    |                 | μA    |

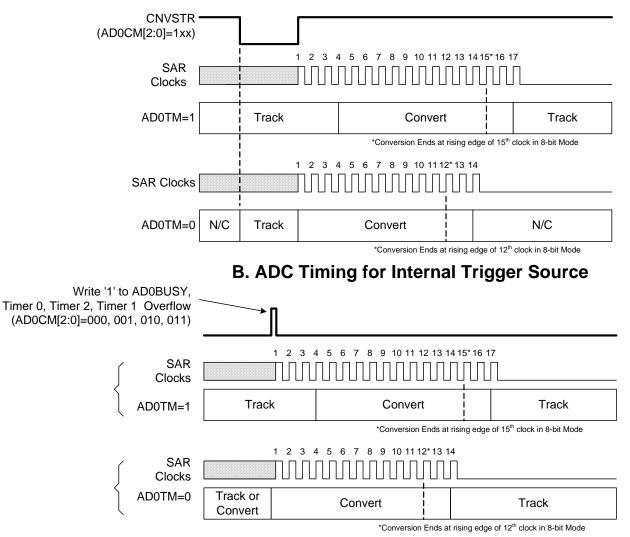

#### 10.3.2. Tracking Modes

The AD0TM bit in register ADC0CN enables "delayed conversions", and will delay the actual conversion start by three SAR clock cycles, during which time the ADC will continue to track the input. If AD0TM is left at logic 0, a conversion will begin immediately, without the extra tracking time. For internal start-of-conversion sources, the ADC will track anytime it is not performing a conversion. When the CNVSTR signal is used to initiate conversions, ADC0 will track either when AD0TM is logic 1, or when AD0TM is logic 0 and CNVSTR is held low. See Figure 10.2 for track and convert timing details. Delayed conversion mode is useful when AMUX settings are frequently changed, due to the settling time requirements described in Section "10.3.3. Settling Time Requirements" on page 58.

Figure 10.2. 10-Bit ADC Track and Conversion Example Timing

### 11. Temperature Sensor

An on-chip temperature sensor is included on the C8051F700/2/4/6/8 and C8051F710/2/4/6 which can be directly accessed via the ADC multiplexer in single-ended configuration. To use the ADC to measure the temperature sensor, the ADC mux channel should be configured to connect to the temperature sensor. The temperature sensor transfer function is shown in Figure 11.1. The output voltage ( $V_{TEMP}$ ) is the positive ADC input when the ADC multiplexer is set correctly. The TEMPE bit in register REF0CN enables/disables the temperature sensor, as described in SFR Definition 12.1. While disabled, the temperature sensor defaults to a high impedance state and any ADC measurements performed on the sensor will result in meaningless data. Refer to Table 9.12 for the slope and offset parameters of the temperature sensor.

Figure 11.1. Temperature Sensor Transfer Function

### 11.1. Calibration

The uncalibrated temperature sensor output is extremely linear and suitable for relative temperature measurements (see Table 5.1 for linearity specifications). For absolute temperature measurements, offset and/or gain calibration is recommended. Typically a 1-point (offset) calibration includes the following steps:

- 1. Control/measure the ambient temperature (this temperature must be known).

- 2. Power the device, and delay for a few seconds to allow for self-heating.

- 3. Perform an ADC conversion with the temperature sensor selected as the ADC's input.

- 4. Calculate the offset characteristics, and store this value in non-volatile memory for use with subsequent temperature sensor measurements.

Figure 5.3 shows the typical temperature sensor error assuming a 1-point calibration at 0 °C.

## 13. Voltage Regulator (REG0)

C8051F70x/71x devices include an internal voltage regulator (REG0) to regulate the internal core supply to 1.8 V from a  $V_{DD}$  supply of 1.8 to 3.6 V. Two power-saving modes are built into the regulator to help reduce current consumption in low-power applications. These modes are accessed through the REG0CN register (SFR Definition 13.1). Electrical characteristics for the on-chip regulator are specified in Table 9.5 on page 50

If an external regulator is used to power the device, the internal regulator may be put into bypass mode using the BYPASS bit. The internal regulator should never be placed in bypass mode unless an external 1.8 V regulator is used to supply  $V_{DD}$ . Doing so could cause permanent damage to the device.

Under default conditions, when the device enters STOP mode the internal regulator will remain on. This allows any enabled reset source to generate a reset for the device and bring the device out of STOP mode. For additional power savings, the STOPCF bit can be used to shut down the regulator and the internal power network of the device when the part enters STOP mode. When STOPCF is set to 1, the RST pin or a full power cycle of the device are the only methods of generating a reset.

### SFR Definition 15.1. CS0CN: Capacitive Sense Control

| Bit   | 7     | 6      | 5      | 4       | 3        | 2 | 1 | 0       |

|-------|-------|--------|--------|---------|----------|---|---|---------|

| Name  | CS0EN | CS0PME | CS0INT | CS0BUSY | CS0CMPEN |   |   | CS0CMPF |

| Туре  | R/W   | R/W    | R/W    | R/W     | R/W      | R | R | R       |

| Reset | 0     | 0      | 0      | 0       | 0        | 0 | 0 | 0       |

### SFR Address = 0x9A; SFR Page = 0

| Bit | Name     | Description                                                                                                                                                                                            |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CS0EN    | CS0 Enable.                                                                                                                                                                                            |

|     |          | 0: CS0 disabled and in low-power mode.                                                                                                                                                                 |

|     |          | 1: CS0 enabled and ready to convert.                                                                                                                                                                   |

| 6   | CS0PME   | CS0 Pin Monitor Event.                                                                                                                                                                                 |

|     |          | Set if any converter re-try requests have occurred due to a pin monitor event. This bit remains set until cleared by firmware.                                                                         |

| 5   | CS0INT   | CS0 Interrupt Flag.                                                                                                                                                                                    |

|     |          | 0: CS0 has not completed a data conversion since the last time CS0INT was cleared.                                                                                                                     |

|     |          | 1: CS0 has completed a data conversion.                                                                                                                                                                |

|     |          | This bit is not automatically cleared by hardware.                                                                                                                                                     |

| 4   | CS0BUSY  | CS0 Busy.                                                                                                                                                                                              |

|     |          | Read:                                                                                                                                                                                                  |

|     |          | 0: CS0 conversion is complete or a conversion is not currently in progress.                                                                                                                            |

|     |          | 1: CS0 conversion is in progress.<br>Write:                                                                                                                                                            |

|     |          | 0: No effect.                                                                                                                                                                                          |

|     |          | 1: Initiates CS0 conversion if CS0CM[2:0] = 000b, 110b, or 111b.                                                                                                                                       |

| 3   | CS0CMPEN | CS0 Digital Comparator Enable Bit.                                                                                                                                                                     |

|     |          | Enables the digital comparator, which compares accumulated CS0 conversion<br>output to the value stored in CS0THH:CS0THL.<br>0: CS0 digital comparator disabled.<br>1: CS0 digital comparator enabled. |

| 2:1 | Unused   | Read = 00b; Write = Don't care                                                                                                                                                                         |

| 0   | CS0CMPF  | CS0 Digital Comparator Interrupt Flag.                                                                                                                                                                 |

|     |          | 0: CS0 result is smaller than the value set by CS0THH and CS0THL since the last time CS0CMPF was cleared.                                                                                              |

|     |          | 1: CS0 result is greater than the value set by CS0THH and CS0THL since the last time CS0CMPF was cleared.                                                                                              |

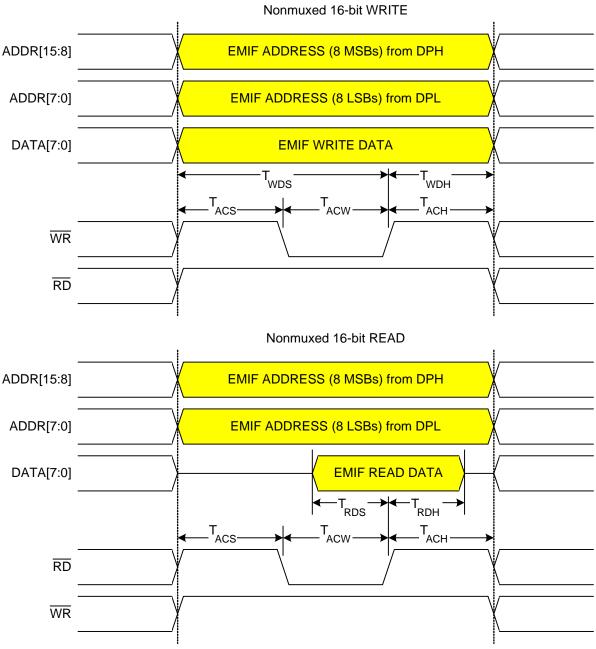

### **18.2.** Configuring the External Memory Interface

Configuring the External Memory Interface consists of five steps:

- 1. Configure the Output Modes of the associated port pins as either push-pull or open-drain (push-pull is most common).

- 2. Configure Port latches to "park" the EMIF pins in a dormant state (usually by setting them to logic 1).

- 3. Select Multiplexed mode or Non-multiplexed mode.

- 4. Select the memory mode (on-chip only, split mode without bank select, split mode with bank select, or off-chip only).

- 5. Set up timing to interface with off-chip memory or peripherals.

Each of these five steps is explained in detail in the following sections. The Port selection, Multiplexed mode selection, and Mode bits are located in the EMI0CF register shown in SFR Definition .

### 18.3. Port Configuration

The EMIF pinout is shown in Figure 18.2 on Page 127

The External Memory Interface claims the associated Port pins for memory operations ONLY during the execution of an off-chip MOVX instruction. Once the MOVX instruction has completed, control of the Port pins reverts to the Port latches for those pins. See Section "28. Port Input/Output" on page 180 for more information about Port operation and configuration. The Port latches should be explicitly configured to "park" the External Memory Interface pins in a dormant state, most commonly by setting them to a logic 1.

During the execution of the MOVX instruction, the External Memory Interface will explicitly disable the drivers on all Port pins that are acting as Inputs (Data[7:0] during a READ operation, for example). The Output mode of the Port pins (whether the pin is configured as Open-Drain or Push-Pull) is unaffected by the External Memory Interface operation, and remains controlled by the PnMDOUT registers. In most cases, the output modes of all EMIF pins should be configured for push-pull mode.

### 18.6.1. Non-Multiplexed Mode

18.6.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111

120

### **20. Special Function Registers**

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the C8051F70x/71x's resources and peripherals. The CIP-51 controller core duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the sub-systems unique to the C8051F70x/71x. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 20.1 lists the SFRs implemented in the C8051F70x/71x device family.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g., P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the data sheet, as indicated in Table 20.2, for a detailed description of each register.

### 22. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system through the C2 interface or by software using the MOVX write instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operations is not required. Code execution is stalled during Flash write/erase operations. Refer to Table 9.6 for complete Flash memory electrical characteristics.

### 22.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Laboratories or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "35. C2 Interface" on page 301.

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before programming Flash memory using MOVX, Flash programming operations must be enabled by: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software.

**Note:** A minimum SYSCLK frequency is required for writing or erasing Flash memory, as detailed in Section "Table 9.6. Flash Electrical Characteristics" on page 50.

For detailed guidelines on programming Flash from firmware, please see Section "22.4. Flash Write and Erase Guidelines" on page 150.

To ensure the integrity of the Flash contents, the on-chip VDD Monitor must be enabled and enabled as a reset source in any system that includes code that writes and/or erases Flash memory from software. Furthermore, there should be no delay between enabling the  $V_{DD}$  Monitor and enabling the  $V_{DD}$  Monitor as a reset source. Any attempt to write or erase Flash memory while the  $V_{DD}$  Monitor is disabled, or not enabled as a reset source, will cause a Flash Error device reset.

#### 22.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 22.2.

#### 22.1.2. Flash Erase Procedure

The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire 512-byte page, perform the following steps:

- 1. Save current interrupt state and disable interrupts.

- 2. Set the PSEE bit (register PSCTL).

- 3. Set the PSWE bit (register PSCTL).

- 4. Write the first key code to FLKEY: 0xA5.

- 5. Write the second key code to FLKEY: 0xF1.

unlocked pages, and user firmware executing on locked pages. Table 22.1 summarizes the Flash security features of the C8051F70x/71x devices.

| Action                                                                        | C2 Debug      | User Firmware executing from: |               |  |  |

|-------------------------------------------------------------------------------|---------------|-------------------------------|---------------|--|--|

|                                                                               | Interface     | an unlocked page              | a locked page |  |  |

| Read, Write or Erase unlocked pages<br>(except page with Lock Byte)           | Permitted     | Permitted                     | Permitted     |  |  |

| Read, Write or Erase locked pages<br>(except page with Lock Byte)             | Not Permitted | FEDR                          | Permitted     |  |  |

| Read or Write page containing Lock Byte<br>(if no pages are locked)           | Permitted     | Permitted                     | Permitted     |  |  |

| Read or Write page containing Lock Byte<br>(if any page is locked)            | Not Permitted | FEDR                          | Permitted     |  |  |

| Read contents of Lock Byte<br>(if no pages are locked)                        | Permitted     | Permitted                     | Permitted     |  |  |

| Read contents of Lock Byte<br>(if any page is locked)                         | Not Permitted | FEDR                          | Permitted     |  |  |

| Erase page containing Lock Byte<br>(if no pages are locked)                   | Permitted     | FEDR                          | FEDR          |  |  |

| Erase page containing Lock Byte - Unlock all pages<br>(if any page is locked) | Only by C2DE  | FEDR                          | FEDR          |  |  |

| Lock additional pages<br>(change '1's to '0's in the Lock Byte)               | Not Permitted | FEDR                          | FEDR          |  |  |

| Unlock individual pages<br>(change '0's to '1's in the Lock Byte)             | Not Permitted | FEDR                          | FEDR          |  |  |

| Read, Write or Erase Reserved Area                                            | Not Permitted | FEDR                          | FEDR          |  |  |

Table 22.1. Flash Security Summary

C2DE - C2 Device Erase (Erases all Flash pages including the page containing the Lock Byte) FEDR - Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is '1' after reset)

All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

Locking any Flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

### 22.4. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of VDD, system clock frequency, or temperature. This accidental execution of Flash modifying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

To help prevent the accidental modification of Flash by firmware, the VDD Monitor must be enabled and enabled as a reset source on C8051F70x/71x devices for the Flash to be successfully modified. If either the VDD Monitor or the VDD Monitor reset source is not enabled, a Flash Error Device Reset will be generated when the firmware attempts to modify the Flash.

### SFR Definition 26.1. WDTCN: Watchdog Timer Control

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----------|---|---|---|---|---|---|---|

| Name  | WDT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W      |   |   |   |   |   |   |   |

| Reset | 0        | 0 | 0 | 1 | 0 | 1 | 1 | 1 |

SFR Address = 0xE3; SFR Page = All Pages

| Bit | Name       | Description                        | Write                                                                                                                                                                                  | Read                                   |

|-----|------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 7:0 | WDT[7:0]   | WDT Control.                       | Writing 0xA5 both<br>enables and reloads the<br>WDT.<br>Writing 0xDE followed<br>within 4 system clocks by<br>0xAD disables the WDT.<br>Writing 0xFF locks out<br>the disable feature. |                                        |

| 4   | WDTSTATUS  | Watchdog Status Bit.               |                                                                                                                                                                                        | 0: WDT is inactive<br>1: WDT is active |

| 2:0 | WDTTIMEOUT | Watchdog Timeout Interval<br>Bits. | WDTCN[2:0] bits set the<br>Watchdog Timeout Inter-<br>val. When writing these<br>bits, WDTCN[7] must be<br>set to 0.                                                                   |                                        |

#### 28.2.2. Assigning Port I/O Pins to Digital Functions

Any Port pins not assigned to analog functions may be assigned to digital functions or used as GPIO. Most digital functions rely on the Crossbar for pin assignment; however, some digital functions bypass the Crossbar in a manner similar to the analog functions listed above. **Port pins used by these digital func-tions and any Port pins selected for use as GPIO should have their corresponding bit in PnSKIP set to 1.** Table 28.2 shows all available digital functions and the potential mapping of Port I/O to each digital function.

| Digital Function                                                              | Potentially Assignable Port Pins                                                                                                                                                                                | SFR(s) used for<br>Assignment |  |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|

| UART0, SPI0, SMBus, CP0,<br>CP0A, SYSCLK, PCA0<br>(CEX0-2 and ECI), T0 or T1. | Any Port pin available for assignment by the<br>Crossbar. This includes P0.0–P2.7 pins which<br>have their PnSKIP bit set to 0.<br><b>Note:</b> The Crossbar will always assign UART0<br>pins to P0.4 and P0.5. | XBR0, XBR1                    |  |

| Any pin used for GPIO                                                         | P0.0–P6.5                                                                                                                                                                                                       | P0SKIP, P1SKIP,<br>P2SKIP     |  |

| External Memory Interface                                                     | P3.0–P6.2                                                                                                                                                                                                       | EMI0CF                        |  |

### Table 28.2. Port I/O Assignment for Digital Functions

#### 28.2.3. Assigning Port I/O Pins to External Event Trigger Functions

External event trigger functions can be used to trigger an interrupt or wake the device from a low power mode when a transition occurs on a digital I/O pin. The event trigger functions do not require dedicated pins and will function on both GPIO pins (PnSKIP = 1) and pins in use by the Crossbar (PnSKIP = 0). External event trigger functions cannot be used on pins configured for analog I/O. Table 28.3 shows all available external event trigger functions.

| Table 28.3. I | Port I/O Assiq | nment for E | xternal Event | Trigger Functions |

|---------------|----------------|-------------|---------------|-------------------|

|               |                |             |               |                   |

| Event Trigger Function | Potentially Assignable Port Pins | SFR(s) used for<br>Assignment  |

|------------------------|----------------------------------|--------------------------------|

| External Interrupt 0   | P0.0–P0.7                        | IT01CF                         |

| External Interrupt 1   | P0.0–P0.7                        | IT01CF                         |

| Port Match             | P0.0–P1.7                        | POMASK, POMAT<br>P1MASK, P1MAT |

### SFR Definition 28.15. P1SKIP: Port 1 Skip

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | P1SKIP[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xD5; SFR Page = F

| Bit | Name        | Function                                                                                                                                                                                                                                                                              |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1SKIP[7:0] | Port 1 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                     |

|     |             | These bits select Port 1 pins to be skipped by the Crossbar Decoder. Port pins<br>used for analog, special functions or GPIO should be skipped by the Crossbar.<br>0: Corresponding P1.n pin is not skipped by the Crossbar.<br>1: Corresponding P1.n pin is skipped by the Crossbar. |

### SFR Definition 28.16. P1DRV: Port 1 Drive Strength

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | P1DRV[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xFA; SFR Page = F

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1DRV[7:0] | Drive Strength Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P1.n Output has low output drive strength.<br>1: Corresponding P1.n Output has high output drive strength. |

### 32.2. Operational Modes

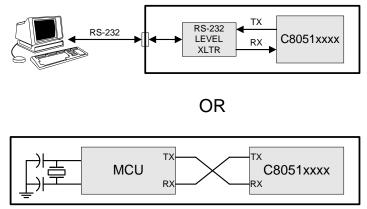

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown in Figure 32.3.

Figure 32.3. UART Interconnect Diagram

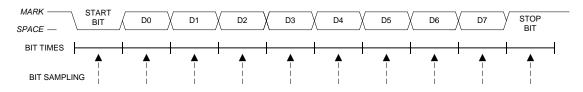

### 32.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 32.4. 8-Bit UART Timing Diagram

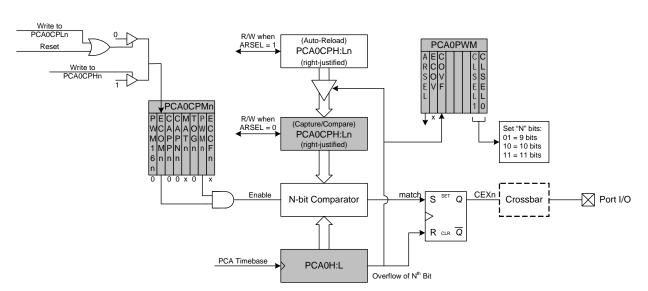

### 34.3.5.2. 9/10/11-bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 9/10/11-bit PWM mode should be varied by writing to an "Auto-Reload" Register, which is dual-mapped into the PCA0CPHn and PCA0CPLn register locations. The data written to define the duty cycle should be right-justified in the registers. The auto-reload registers are accessed (read or written) when the bit ARSEL in PCA0PWM is set to 1. The capture/compare registers are accessed when ARSEL is set to 0.

When the least-significant N bits of the PCA0 counter match the value in the associated module's capture/compare register (PCA0CPn), the output on CEXn is asserted high. When the counter overflows from the Nth bit, CEXn is asserted low (see Figure 34.9). Upon an overflow from the Nth bit, the COVF flag is set, and the value stored in the module's auto-reload register is loaded into the capture/compare register. The value of N is determined by the CLSEL bits in register PCA0PWM.

The 9, 10 or 11-bit PWM mode is selected by setting the ECOMn and PWMn bits in the PCA0CPMn register, and setting the CLSEL bits in register PCA0PWM to the desired cycle length (other than 8-bits). If the MATn bit is set to 1, the CCFn flag for the module will be set each time a comparator match (rising edge) occurs. The COVF flag in PCA0PWM can be used to detect the overflow (falling edge), which will occur every 512 (9-bit), 1024 (10-bit) or 2048 (11-bit) PCA clock cycles. The duty cycle for 9/10/11-Bit PWM Mode is given in Equation 34.2, where N is the number of bits in the PWM cycle.

**Important Note About PCA0CPHn and PCA0CPLn Registers**: When writing a 16-bit value to the PCA0CPn registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(2^N - PCA0CPn)}{2^N}$$

Equation 34.3. 9, 10, and 11-Bit PWM Duty Cycle

A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 34.9. PCA 9, 10 and 11-Bit PWM Mode Diagram