Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | CPU32                                                                 |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 16MHz                                                                 |

| Connectivity               | EBI/EMI, SCI, SPI, UART/USART                                         |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 15                                                                    |

| Program Memory Size        | -                                                                     |

| Program Memory Type        | ROMIess                                                               |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 144-LQFP                                                              |

| Supplier Device Package    | 144-LQFP (20x20)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68332acpv16 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Table 1 Ordering Information**

| Package Type | TPU Type               | Temperature    | Frequency<br>(MHz) | Package<br>Order<br>Quantity | Order Number    |  |  |        |           |

|--------------|------------------------|----------------|--------------------|------------------------------|-----------------|--|--|--------|-----------|

| 132-Pin PQFP | Motion Control         | -40 to +85 °C  | 16 MHz             | 2 pc tray                    | SPAKMC332GCFC16 |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332GCFC16   |  |  |        |           |

|              |                        |                | 20 MHz             | 2 pc tray                    | SPAKMC332GCFC20 |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332GCFC20   |  |  |        |           |

|              |                        | -40 to +105 °C | 16 MHz             | 2 pc tray                    | SPAKMC332GVFC16 |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332GVFC16   |  |  |        |           |

|              |                        |                | 20 MHz             | 2 pc tray                    | SPAKMC332GVFC20 |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332GVFC20   |  |  |        |           |

|              |                        | -40 to +125 °C | 16 MHz             | 2 pc tray                    | SPAKMC332GMFC16 |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332GMFC16   |  |  |        |           |

|              |                        |                | 20 MHz             | 2 pc tray                    | SPAKMC332GMFC20 |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332GMFC20   |  |  |        |           |

|              | Standard               | −40 to +85 °C  | 16 MHz             | 2 pc tray                    | SPAKMC332CFC16  |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332CFC16    |  |  |        |           |

|              |                        |                | 20 MHz             | 2 pc tray                    | SPAKMC332CFC20  |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332CFC20    |  |  |        |           |

|              |                        | -40 to +105 °C | +105 °C 16 MHz     | 2 pc tray                    | SPAKMC332VFC16  |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332VFC16    |  |  |        |           |

|              |                        |                |                    | 2 pc tray                    | SPAKMC332VFC20  |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332VFC20    |  |  |        |           |

|              |                        | -40 to +125 °C | 16 MHz             | 2 pc tray                    | SPAKMC332MFC16  |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332MFC16    |  |  |        |           |

|              |                        |                |                    |                              |                 |  |  | 20 MHz | 2 pc tray |

|              |                        |                |                    | 36 pc tray                   | MC68332MFC20    |  |  |        |           |

|              | Std w/enhanced<br>PPWA | -40 to +85 °C  | 16 MHz             | 2 pc tray                    | SPAKMC332ACFC16 |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332ACFC16   |  |  |        |           |

|              |                        |                | 20 MHz             | 2 pc tray                    | SPAKMC332ACFC20 |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332ACFC20   |  |  |        |           |

|              |                        | -40 to +105 °C | 16 MHz             | 2 pc tray                    | SPAKMC332AVFC16 |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332AVFC16   |  |  |        |           |

|              |                        |                | 20 MHz             | 2 pc tray                    | SPAKMC332AVFC20 |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332AVFC20   |  |  |        |           |

|              |                        | -40 to +125 °C | 16 MHz             | 2 pc tray                    | SPAKMC332AMFC16 |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332AMFC16   |  |  |        |           |

|              |                        |                | 20 MHz             | 2 pc tray                    | SPAKMC332AMFC20 |  |  |        |           |

|              |                        |                |                    | 36 pc tray                   | MC68332AMFC20   |  |  |        |           |

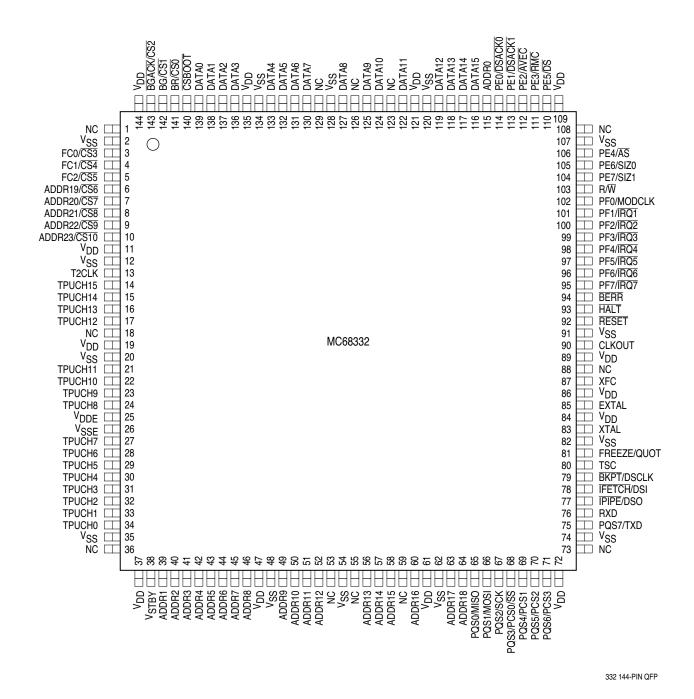

#### 1.3 Pin Assignments

Figure 2 MC68332 132-Pin QFP Pin Assignments

Figure 3 MC68332 144-Pin QFP Pin Assignments

### **Table 2 MCU Pin Characteristic (Continued)**

| Pin<br>Mnemonic   | Output<br>Driver | Input<br>Synchronized | Input<br>Hysteresis | Discrete<br>I/O | Port<br>Designation |

|-------------------|------------------|-----------------------|---------------------|-----------------|---------------------|

| T2CLK             | _                | Y                     | Y                   | _               | _                   |

| TPUCH[15:0]       | А                | Y                     | Y                   | _               | _                   |

| TSC               | _                | Y                     | Y                   | _               | _                   |

| TXD               | Во               | Y                     | Y                   | I/O             | PQS7                |

| XFC <sup>2</sup>  | _                | _                     | _                   | Special         | _                   |

| XTAL <sup>2</sup> | _                | _                     | _                   | Special         | _                   |

#### NOTES:

- 1. DATA[15:0] are synchronized during reset only. MODCLK is synchronized only when used as an input port pin.

- 2. EXTAL, XFC, and XTAL are clock reference connections.

### 2.2 MCU Power Connections

### **Table 3 MCU Power Connections**

| V <sub>STBY</sub>                  | Standby RAM Power/Clock Synthesizer Power   |

|------------------------------------|---------------------------------------------|

| V <sub>DDSYN</sub>                 | Clock Synthesizer Power                     |

| V <sub>SSE</sub> /V <sub>DDE</sub> | External Periphery Power (Source and Drain) |

| $V_{SSI}/V_{DDI}$                  | Internal Module Power (Source and Drain)    |

# 2.3 MCU Driver Types

### **Table 4 MCU Driver Types**

| Туре | I/O | Description                                                                                                                                                                                                                                  |

|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А    | 0   | Output-only signals that are always driven; no external pull-up required                                                                                                                                                                     |

| Aw   | 0   | Type A output with weak P-channel pull-up during reset                                                                                                                                                                                       |

| В    | 0   | Three-state output that includes circuitry to pull up output before high impedance is established, to ensure rapid rise time. An external holding resistor is required to maintain logic level while the pin is in the high-impedance state. |

| Во   | 0   | Type B output that can be operated in an open-drain mode                                                                                                                                                                                     |

# **Table 5 MCU Signal Characteristics (Continued)**

| Signal Name | MCU Module | Signal Type | Active State |

|-------------|------------|-------------|--------------|

| TSC         | SIM        | Input       | _            |

| TXD         | QSM        | Output      | _            |

| XFC         | SIM        | Input       | _            |

| XTAL        | SIM        | Output      | _            |

# 2.5 Signal Function

# **Table 6 MCU Signal Function**

| Signal Name                          | Mnemonic           | Function                                                                                                                                                                     |

|--------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Bus                          | ADDR[23:0]         | 24-bit address bus                                                                                                                                                           |

| Address Strobe                       | ĀS                 | Indicates that a valid address is on the address bus                                                                                                                         |

| Autovector                           | AVEC               | Requests an automatic vector during interrupt acknowledge                                                                                                                    |

| Bus Error                            | BERR               | Indicates that a bus error has occurred                                                                                                                                      |

| Bus Grant                            | BG                 | Indicates that the MCU has relinquished the bus                                                                                                                              |

| Bus Grant Acknowledge                | BGACK              | Indicates that an external device has assumed bus mastership                                                                                                                 |

| Breakpoint                           | BKPT               | Signals a hardware breakpoint to the CPU                                                                                                                                     |

| Bus Request                          | BR                 | Indicates that an external device requires bus mastership                                                                                                                    |

| System Clockout                      | CLKOUT             | System clock output                                                                                                                                                          |

| Chip Selects                         | CS[10:0]           | Select external devices at programmed addresses                                                                                                                              |

| Boot Chip Select                     | CSBOOT             | Chip select for external boot start-up ROM                                                                                                                                   |

| Data Bus                             | DATA[15:0]         | 16-bit data bus                                                                                                                                                              |

| Data Strobe                          | DS                 | During a read cycle, indicates when it is possible for an external device to place data on the data bus. During a write cycle, indicates that valid data is on the data bus. |

| Data and Size Acknowledge            | DSACK[1:0]         | Provide asynchronous data transfers and dynamic bus sizing                                                                                                                   |

| Development Serial In, Out,<br>Clock | DSI, DSO,<br>DSCLK | Serial I/O and clock for background debugging mode                                                                                                                           |

| Crystal Oscillator                   | EXTAL, XTAL        | Connections for clock synthesizer circuit reference; a crystal or an external oscillator can be used                                                                         |

| Function Codes                       | FC[2:0]            | Identify processor state and current address space                                                                                                                           |

| Freeze                               | FREEZE             | Indicates that the CPU has entered background mode                                                                                                                           |

| Halt                                 | HALT               | Suspend external bus activity                                                                                                                                                |

| Instruction Pipeline                 | IFETCH<br>IPIPE    | Indicate instruction pipeline activity                                                                                                                                       |

| Interrupt Request Level              | ĪRQ[7:1]           | Provides an interrupt priority level to the CPU                                                                                                                              |

| Master In Slave Out                  | MISO               | Serial input to QSPI in master mode;<br>serial output from QSPI in slave mode                                                                                                |

| Clock Mode Select                    | MODCLK             | Selects the source and type of system clock                                                                                                                                  |

| Master Out Slave In                  | MOSI               | Serial output from QSPI in master mode;<br>serial input to QSPI in slave mode                                                                                                |

| Port C                               | PC[6:0]            | SIM digital output port signals                                                                                                                                              |

| Peripheral Chip Select               | PCS[3:0]           | QSPI peripheral chip selects                                                                                                                                                 |

| Port E                               | PE[7:0]            | SIM digital I/O port signals                                                                                                                                                 |

| Port F                               | PF[7:0]            | SIM digital I/O port signals                                                                                                                                                 |

| Port QS                              | PQS[7:0]           | QSM digital I/O port signals                                                                                                                                                 |

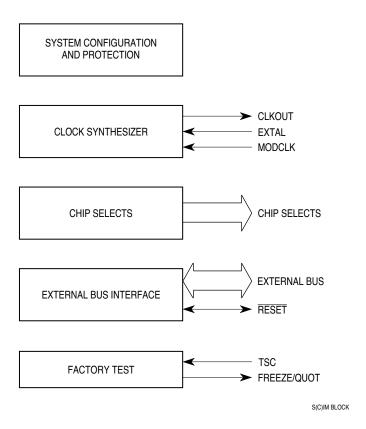

## 3 System Integration Module

The MCU system integration module (SIM) consists of five functional blocks that control system startup, initialization, configuration, and external bus.

Figure 5 SIM Block Diagram

#### 3.1 Overview

The system configuration and protection block controls MCU configuration and operating mode. The block also provides bus and software watchdog monitors.

The system clock generates clock signals used by the SIM, other IMB modules, and external devices. In addition, a periodic interrupt generator supports execution of time-critical control routines.

The external bus interface handles the transfer of information between IMB modules and external address space.

The chip-select block provides eleven general-purpose chip-select signals and a boot ROM chip select signal. Both general-purpose and boot ROM chip-select signals have associated base address registers and option registers.

The system test block incorporates hardware necessary for testing the MCU. It is used to perform factory tests, and its use in normal applications is not supported.

The SIM control register address map occupies 128 bytes. Unused registers within the 128-byte address space return zeros when read. The "Access" column in the SIM address map below indicates which registers are accessible only at the supervisor privilege level and which can be assigned to either the supervisor or user privilege level, according to the value of the SUPV bit in the SIMCR.

#### 3.2.3 Bus Monitor

The internal bus monitor checks for excessively long  $\overline{DSACK}$  response times during normal bus cycles and for excessively long  $\overline{DSACK}$  or  $\overline{AVEC}$  response times during interrupt acknowledge cycles. The monitor asserts  $\overline{BERR}$  if response time is excessive.

DSACK and AVEC response times are measured in clock cycles. The maximum allowable response time can be selected by setting the BMT field.

The monitor does not check DSACK response on the external bus unless the CPU initiates the bus cycle. The BME bit in the SYPCR enables the internal bus monitor for internal to external bus cycles. If a system contains external bus masters, an external bus monitor must be implemented and the internal to external bus monitor option must be disabled.

#### 3.2.4 Halt Monitor

The halt monitor responds to an assertion of  $\overline{HALT}$  on the internal bus. A flag in the reset status register (RSR) indicates that the last reset was caused by the halt monitor. The halt monitor reset can be inhibited by the HME bit in the SYPCR.

### 3.2.5 Spurious Interrupt Monitor

The spurious interrupt monitor issues  $\overline{\text{BERR}}$  if no interrupt arbitration occurs during an interrupt-acknowledge cycle.

### 3.2.6 Software Watchdog

The software watchdog is controlled by SWE in the SYPCR. Once enabled, the watchdog requires that a service sequence be written to SWSR on a periodic basis. If servicing does not take place, the watchdog times out and issues a reset. This register can be written at any time, but returns zeros when read.

| <b>SWSR</b> —Software Service Register |   |   |   |   |   |   |   | \$YF | FFA27 |

|----------------------------------------|---|---|---|---|---|---|---|------|-------|

| 15                                     | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0     |

| NOT USED                               |   | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0     |

| RESET:                                 |   |   |   |   |   |   |   |      |       |

|                                        |   | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0     |

Register shown with read value

Perform a software watchdog service sequence as follows:

- a. Write \$55 to SWSR.

- b. Write \$AA to SWSR.

Both writes must occur before time-out in the order listed, but any number of instructions can be executed between the two writes.

The watchdog clock rate is affected by SWP and SWT in SYPCR. When SWT[1:0] are modified, a watchdog service sequence must be performed before the new time-out period takes effect.

The reset value of SWP is affected by the state of the MODCLK pin on the rising edge of reset, as shown in the following table.

| MODCLK | SWP |

|--------|-----|

| 0      | 1   |

| 1      | 0   |

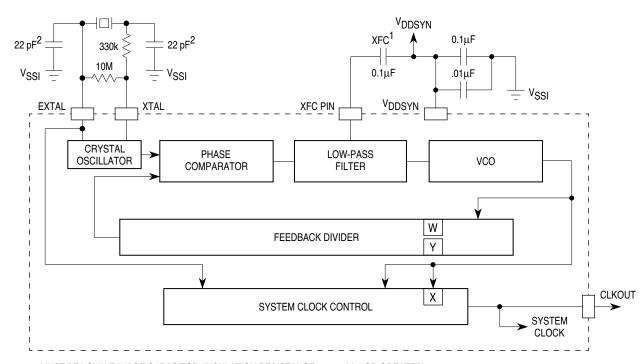

#### 3.3 System Clock

The system clock in the SIM provides timing signals for the IMB modules and for an external peripheral bus. Because MCU operation is fully static, register and memory contents are not affected when the clock rate changes. System hardware and software support changes in the clock rate during operation.

The system clock signal can be generated in three ways. An internal phase-locked loop can synthesize the clock from an internal or external frequency source, or the clock signal can be input from an external source.

Following is a block diagram of the clock submodule.

- 1. MUST BE LOW-LEAKAGE CAPACITOR (INSULATION RESISTANCE 30,000 M $\Omega$  OR GREATER)

- 2. RESISTANCE AND CAPACITANCE BASED ON A TEST CIRCUIT CONSTRUCTED WITH A DAISHINKU DMX-38 32.768-kHz CRYSTAL. SPECIFIC COMPONENTS MUST BE BASED ON CRYSTAL TYPE. CONTACT CRYSTAL VENDOR FOR EXACT CIRCUIT.

SYS CLOCK

Figure 7 System Clock Block Diagram

### 3.3.1 Clock Sources

The state of the clock mode (MODCLK) pin during reset determines the clock source. When MODCLK is held high during reset, the clock synthesizer generates a clock signal from either a crystal oscillator or an external reference input. Clock synthesizer control register SYNCR determines operating frequency and various modes of operation. When MODCLK is held low during reset, the clock synthesizer is disabled, and an external system clock signal must be applied. When the synthesizer is disabled, SYNCR control bits have no effect.

A reference crystal must be connected between the EXTAL and XTAL pins to use the internal oscillator. Use of a 32.768-kHz crystal is recommended. These crystals are inexpensive and readily available. If an external reference signal or an external system clock signal is applied through the EXTAL pin, the XTAL pin must be left floating. External reference signal frequency must be less than or equal to maximum specified reference frequency. External system clock signal frequency must be less than or equal to maximum specified system clock frequency.

When an external system clock signal is applied (i.e., the PLL is not used), duty cycle of the input is critical, especially at near maximum operating frequencies. The relationship between clock signal duty cycle and clock signal period is expressed:

Minimum external clock period =

minimum external clock high/low time 50% — percentage variation of external clock input duty cycle

#### 3.3.2 Clock Synthesizer Operation

A voltage controlled oscillator (VCO) generates the system clock signal. A portion of the clock signal is fed back to a divider/counter. The divider controls the frequency of one input to a phase comparator. The other phase comparator input is a reference signal, either from the internal oscillator or from an external source. The comparator generates a control signal proportional to the difference in phase between its two inputs. The signal is low-pass filtered and used to correct VCO output frequency.

The synthesizer locks when VCO frequency is identical to reference frequency. Lock time is affected by the filter time constant and by the amount of difference between the two comparator inputs. Whenever comparator input changes, the synthesizer must re-lock. Lock status is shown by the SLOCK bit in SYN-CR.

The MCU does not come out of reset state until the synthesizer locks. Crystal type, characteristic frequency, and layout of external oscillator circuitry affect lock time.

The low-pass filter requires an external low-leakage capacitor, typically 0.1  $\mu$ F, connected between the XFC and  $V_{DDSYN}$  pins.

$V_{DDSYN}$  is used to power the clock circuits. A separate power source increases MCU noise immunity and can be used to run the clock when the MCU is powered down. Use a quiet power supply as the  $V_{DDSYN}$  source, since PLL stability depends on the VCO, which uses this supply. Place adequate external bypass capacitors as close as possible to the  $V_{DDSYN}$  pin to ensure stable operating frequency.

When the clock synthesizer is used, control register SYNCR determines operating frequency and various modes of operation. SYNCR can be read only when the processor is operating at the supervisor privilege level.

The SYNCR X bit controls a divide by two prescaler that is not in the synthesizer feedback loop. Setting X doubles clock speed without changing VCO speed. There is no VCO relock delay. The SYNCR W bit controls a 3-bit prescaler in the feedback divider. Setting W increases VCO speed by a factor of four. The SYNCR Y field determines the count modulus for a modulo 64 down counter, causing it to divide by a value of Y + 1. When either W or Y value changes, there is a VCO relock delay.

Clock frequency is determined by SYNCR bit settings as follows:

$$F_{\text{SYSTEM}} = F_{\text{REFERENCE}} [4(Y + 1)(2^{2W + X})]$$

In order for the device to perform correctly, the clock frequency selected by the W, X, and Y bits must be within the limits specified for the MCU.

The VCO frequency is twice the system clock frequency if X = 1 or four times the system clock frequency if X = 0.

The reset state of SYNCR (\$3F00) produces a modulus-64 count.

#### 3.4.8 Data Transfer Mechanism

The MCU architecture supports byte, word, and long-word operands, allowing access to 8- and 16-bit data ports through the use of asynchronous cycles controlled by the data transfer and size acknowledge inputs (DSACK1 and DSACK0).

### 3.4.9 Dynamic Bus Sizing

The MCU dynamically interprets the port size of the addressed device during each bus cycle, allowing operand transfers to or from 8- and 16-bit ports. During an operand transfer cycle, the slave device signals its port size and indicates completion of the bus cycle to the MCU through the use of the DSACKO and DSACKI inputs, as shown in the following table.

Table 10 Effect of DSACK Signals

| DSACK1 | DSACK0 | Result                                        |

|--------|--------|-----------------------------------------------|

| 1      | 1      | Insert Wait States in Current Bus Cycle       |

| 1      | 0      | Complete Cycle —Data Bus Port Size is 8 Bits  |

| 0      | 1      | Complete Cycle —Data Bus Port Size is 16 Bits |

| 0      | 0      | Reserved                                      |

For example, if the MCU is executing an instruction that reads a long-word operand from a 16-bit port, the MCU latches the 16 bits of valid data and then runs another bus cycle to obtain the other 16 bits. The operation for an 8-bit port is similar, but requires four read cycles. The addressed device uses the  $\overline{DSACK0}$  and  $\overline{DSACK1}$  signals to indicate the port width. For instance, a 16-bit device always returns  $\overline{DSACK0} = 1$  and  $\overline{DSACK1} = 0$  for a 16-bit port, regardless of whether the bus cycle is a byte or word operation.

Dynamic bus sizing requires that the portion of the data bus used for a transfer to or from a particular port size be fixed. A 16-bit port must reside on data bus bits [15:0] and an 8-bit port must reside on data bus bits [15:8]. This minimizes the number of bus cycles needed to transfer data and ensures that the MCU transfers valid data.

The MCU always attempts to transfer the maximum amount of data on all bus cycles. For a word operation, it is assumed that the port is 16 bits wide when the bus cycle begins. Operand bytes are designated as shown in the following figure. OP0 is the most significant byte of a long-word operand, and OP3 is the least significant byte. The two bytes of a word-length operand are OP0 (most significant) and OP1. The single byte of a byte-length operand is OP0.

| Operand    | Byte Order |    |     |    |     |    |     |    |

|------------|------------|----|-----|----|-----|----|-----|----|

|            | 31         | 24 | 23  | 16 | 15  | 8  | 7   | 0  |

| Long Word  | OP0        |    | OP1 |    | OP2 |    | OP3 |    |

| Three Byte |            |    | OP0 |    | OP1 |    | OP2 |    |

| Word       |            |    | ,   |    | OF  | 90 | OI  | P1 |

| Byte       |            |    |     |    |     |    | OI  | P0 |

Figure 8 Operand Byte Order

### 3.4.10 Operand Alignment

The data multiplexer establishes the necessary connections for different combinations of address and data sizes. The multiplexer takes the two bytes of the 16-bit bus and routes them to their required positions. Positioning of bytes is determined by the size and address outputs. SIZ1 and SIZ0 indicate the remaining number of bytes to be transferred during the current bus cycle. The number of bytes transferred is equal to or less than the size indicated by SIZ1 and SIZ0, depending on port width.

**Table 18 Reset Mode Selection**

| DATA0                               | CSBOOT 16-Bit                                    | CSBOOT 8-Bit                                                                |

|-------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------|

| DATA1                               | CS0<br>CS1<br>CS2                                | BR<br>BG<br>BGACK                                                           |

| DATA2                               | CS3<br>CS4<br>CS5                                | FC0<br>FC1<br>FC2                                                           |

| DATA3 DATA4 DATA5 DATA6 DATA7 DATA8 | CS6<br>CS[7:6]<br>CS[8:6]<br>CS[9:6]<br>CS[10:6] | ADDR19<br>ADDR[20:19]<br>ADDR[21:19]<br>ADDR[22:19]<br>ADDR[23:19]<br>PORTE |

| DATA9                               | AVEC, DS, AS,<br>SIZ[1:0]<br>IRQ[7:1]<br>MODCLK  | PORTF                                                                       |

| DATA11                              | Test Mode Disabled                               | Test Mode Enabled                                                           |

| MODCLK                              | VCO = System Clock                               | EXTAL = System Clock                                                        |

| BKPT                                | Background Mode Disabled                         | Background Mode Enabled                                                     |

### 3.7.2 Functions of Pins for Other Modules During Reset

Generally, pins associated with modules other than the SIM default to port functions, and input/output ports are set to input state. This is accomplished by disabling pin functions in the appropriate control registers, and by clearing the appropriate port data direction registers. Refer to individual module sections in this manual for more information. The following table is a summary of module pin function out of reset.

**Table 19 Module Pin Functions**

| Module | Pin Mnemonic      | Function        |

|--------|-------------------|-----------------|

| CPU32  | DSI/IFETCH        | DSI/IFETCH      |

|        | DSO/IPIPE         | DSO/IPIPE       |

|        | BKPT/DSCLK        | BKPT/DSCLK      |

| GPT    | PGP7/IC4/OC5      | Discrete Input  |

|        | PGP[6:3]/OC[4:1]  | Discrete Input  |

|        | PGP[2:0]/IC[3:1]  | Discrete Input  |

|        | PAI               | Discrete Input  |

|        | PCLK              | Discrete Input  |

|        | PWMA, PWMB        | Discrete Output |

| QSM    | PQS7/TXD          | Discrete Input  |

|        | PQS[6:4]/PCS[3:1] | Discrete Input  |

|        | PQS3/PCS0/SS      | Discrete Input  |

|        | PQS2/SCK          | Discrete Input  |

|        | PQS1/MOSI         | Discrete Input  |

|        | PQS0/MISO         | Discrete Input  |

|        | RXD               | RXD             |

# 4.6 Instruction Set Summary

**Table 20 Instruction Set Summary**

|                          | 1                                            | ne 20 man action             |                                                                                                                                                                                 |

|--------------------------|----------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction              | Syntax                                       | Operand Size                 | Operation                                                                                                                                                                       |

| ABCD                     | Dn, Dn<br>– (An), – (An)                     | 8<br>8                       | $Source_{10} + Destination_{10} + X \Rightarrow Destination$                                                                                                                    |

| ADD                      | Dn, <ea> <ea>, Dn</ea></ea>                  | 8, 16, 32<br>8, 16, 32       | Source + Destination ⇒ Destination                                                                                                                                              |

| ADDA                     | <ea>, An</ea>                                | 16, 32                       | Source + Destination ⇒ Destination                                                                                                                                              |

| ADDI                     | # <data>, <ea></ea></data>                   | 8, 16, 32                    | Immediate data + Destination ⇒ Destination                                                                                                                                      |

| ADDQ                     | # <data>, <ea></ea></data>                   | 8, 16, 32                    | Immediate data + Destination ⇒ Destination                                                                                                                                      |

| ADDX                     | Dn, Dn<br>– (An), – (An)                     | 8, 16, 32<br>8, 16, 32       | Source + Destination + X ⇒ Destination                                                                                                                                          |

| AND                      | <ea>, Dn<br/>Dn, <ea></ea></ea>              | 8, 16, 32<br>8, 16, 32       | Source • Destination ⇒ Destination                                                                                                                                              |

| ANDI                     | # <data>, <ea></ea></data>                   | 8, 16, 32                    | Data • Destination ⇒ Destination                                                                                                                                                |

| ANDI to CCR              | # <data>, CCR</data>                         | 8                            | Source • CCR ⇒ CCR                                                                                                                                                              |

| ANDI to SR1 <sup>1</sup> | # <data>, SR</data>                          | 16                           | Source • SR $\Rightarrow$ SR                                                                                                                                                    |

| ASL                      | Dn, Dn<br># <data>, Dn<br/>Í</data>          | 8, 16, 32<br>8, 16, 32<br>16 | X/C <b>← ←</b> 0                                                                                                                                                                |

| ASR                      | Dn, Dn<br># <data>, Dn<br/>Í</data>          | 8, 16, 32<br>8, 16, 32<br>16 | X/C                                                                                                                                                                             |

| Bcc                      | label                                        | 8, 16, 32                    | If condition true, then $PC + d \Rightarrow PC$                                                                                                                                 |

| BCHG                     | Dn, <ea><br/># <data>, <ea></ea></data></ea> | 8, 32<br>8, 32               | $\overline{\text{bit number}} \land \text{of destination}) \Rightarrow Z \Rightarrow \text{bit of destination}$                                                                 |

| BCLR                     | Dn, <ea><br/># <data>, <ea></ea></data></ea> | 8, 32<br>8, 32               | (⟨bit number⟩of destination)  0 ⇒ bit of destination                                                                                                                            |

| BGND                     | none                                         | none                         | If background mode enabled, then enter background mode, else format/vector $\Rightarrow$ – (SSP); PC $\Rightarrow$ – (SSP); SR $\Rightarrow$ – (SSP); (vector) $\Rightarrow$ PC |

| BKPT                     | # <data></data>                              | none                         | If breakpoint cycle acknowledged, then execute returned operation word, else trap as illegal instruction                                                                        |

| BRA                      | label                                        | 8, 16, 32                    | $PC + d \Rightarrow PC$                                                                                                                                                         |

| BSET                     | Dn, <ea><br/># <data>, <ea></ea></data></ea> | 8, 32<br>8, 32               | (⟨bit number⟩of destination) ⇒ Z;<br>1 ⇒ bit of destination                                                                                                                     |

| BSR                      | label                                        | 8, 16, 32                    | $SP - 4 \Rightarrow SP$ ; $PC \Rightarrow (SP)$ ; $PC + d \Rightarrow PC$                                                                                                       |

| BTST                     | Dn, <ea><br/># <data>, <ea></ea></data></ea> | 8, 32<br>8, 32               | (⟨bit number⟩of destination) ⇒ Z                                                                                                                                                |

| CHK                      | <ea>, Dn</ea>                                | 16, 32                       | If Dn < 0 or Dn > (ea), then CHK exception                                                                                                                                      |

| CHK2                     | <ea>, Rn</ea>                                | 8, 16, 32                    | If Rn < lower bound or Rn > upper bound, then CHK exception                                                                                                                     |

| CLR                      | ĺ                                            | 8, 16, 32                    | 0 ⇒ Destination                                                                                                                                                                 |

| CMP                      | <ea>, Dn</ea>                                | 8, 16, 32                    | (Destination – Source), CCR shows results                                                                                                                                       |

| CMPA                     | <ea>, An</ea>                                | 16, 32                       | (Destination – Source), CCR shows results                                                                                                                                       |

| CMPI                     | # <data>, <ea></ea></data>                   | 8, 16, 32                    | (Destination – Data), CCR shows results                                                                                                                                         |

| CMPM                     | (An) +, (An) +                               | 8, 16, 32                    | (Destination – Source), CCR shows results                                                                                                                                       |

| CMP2                     | <ea>, Rn</ea>                                | 8, 16, 32                    | Lower bound $\leq Rn \leq Upper bound$ , CCR shows result                                                                                                                       |

#### 5.2.3 Queued Output Match (QOM)

QOM can generate single or multiple output match events from a table of offsets in parameter RAM. Loop modes allow complex pulse trains to be generated once, a specified number of times, or continuously. The function can be triggered by a link from another TPU channel. In addition, the reference time for the sequence of matches can be obtained from another channel. QOM can generate pulse-width modulated waveforms, including waveforms with high times of 0% or 100%. QOM also allows a TPU channel to be used as a discrete output pin.

### 5.2.4 Programmable Time Accumulator (PTA)

PTA accumulates a 32-bit sum of the total high time, low time, or period of an input signal over a programmable number of periods or pulses. The accumulation can start on a rising or falling edge. After the specified number of periods or pulses, the PTA generates an interrupt request and optionally generates links to other channels.

From 1 to 255 period measurements can be made and summed with the previous measurement(s) before the TPU interrupts the CPU, providing instantaneous or average frequency measurement capability, and the latest complete accumulation (over the programmed number of periods).

### 5.2.5 Multichannel Pulse Width Modulation (MCPWM)

MCPWM generates pulse-width modulated outputs with full 0% to 100% duty cycle range independent of other TPU activity. This capability requires two TPU channels plus an external gate for one PWM channel. (A simple one-channel PWM capability is supported by the QOM function.)

Multiple PWMs generated by MCPWM have two types of high time alignment: edge aligned and center aligned. Edge aligned mode uses n+1 TPU channels for n PWMs; center aligned mode uses 2n+1 channels. Center aligned mode allows a user defined 'dead time' to be specified so that two PWMs can be used to drive an H-bridge without destructive current spikes. This feature is important for motor control applications.

#### 5.2.6 Fast Quadrature Decode (FQD)

FQD is a position feedback function for motor control. It decodes the two signals from a slotted encoder to provide the CPU with a 16-bit free running position counter. FQD incorporates a "speed switch" which disables one of the channels at high speed, allowing faster signals to be decoded. A time stamp is provided on every counter update to allow position interpolation and better velocity determination at low speed or when low resolution encoders are used. The third index channel provided by some encoders is handled by the ICTC function.

### 5.2.7 Universal Asynchronous Receiver/Transmitter (UART)

The UART function uses one or two TPU channels to provide asynchronous communications. Data word length is programmable from 1 to 14 bits. The function supports detection or generation of even, odd, and no parity. Baud rate is freely programmable and can be higher than 100 Kbaud. Eight bidirectional UART channels running in excess of 9600 baud could be implemented on the TPU.

### 5.2.8 Brushless Motor Commutation (COMM)

This function generates the phase commutation signals for a variety of brushless motors, including three-phase brushless direct current. It derives the commutation state directly from the position decoded in FQD, thus eliminating the need for hall effect sensors.

The state sequence is implemented as a user-configurable state machine, thus providing a flexible approach with other general applications. A CPU offset parameter is provided to allow all the switching angles to be advanced or retarded on the fly by the CPU. This feature is useful for torque maintenance at high speeds.

#### 5.4 Parameter RAM

Parameter RAM occupies 256 bytes at the top of the TPU module address map. Channel parameters are organized as 128 16-bit words. However, only 100 words are actually implemented. The parameter RAM address map shows how parameter words are organized in memory.

**Table 23 TPU Parameter RAM Address Map**

| Channel | Base      |    |    | Par | amete | r Addr | ess |    |    |

|---------|-----------|----|----|-----|-------|--------|-----|----|----|

| Number  | Address   | 0  | 1  | 2   | 3     | 4      | 5   | 6  | 7  |

| 0       | \$YFFFF## | 00 | 02 | 04  | 06    | 08     | 0A  | _  | _  |

| 1       | \$YFFFF## | 10 | 12 | 14  | 16    | 18     | 1A  | _  | _  |

| 2       | \$YFFFF## | 20 | 22 | 24  | 26    | 28     | 2A  | _  | _  |

| 3       | \$YFFFF## | 30 | 32 | 34  | 36    | 38     | 3A  | _  | _  |

| 4       | \$YFFFF## | 40 | 42 | 44  | 46    | 48     | 4A  | _  | _  |

| 5       | \$YFFFF## | 50 | 52 | 54  | 56    | 58     | 5A  | _  | _  |

| 6       | \$YFFFF## | 60 | 62 | 64  | 66    | 68     | 6A  | _  | _  |

| 7       | \$YFFFF## | 70 | 72 | 74  | 76    | 78     | 7A  | _  | _  |

| 8       | \$YFFFF## | 80 | 82 | 84  | 86    | 88     | 8A  | _  | _  |

| 9       | \$YFFFF## | 90 | 92 | 94  | 96    | 98     | 9A  | _  | _  |

| 10      | \$YFFFF## | A0 | A2 | A4  | A6    | A8     | AA  | _  | _  |

| 11      | \$YFFFF## | B0 | B2 | B4  | В6    | B8     | ВА  | _  | _  |

| 12      | \$YFFFF## | C0 | C2 | C4  | C6    | C8     | CA  | _  | _  |

| 13      | \$YFFFF## | D0 | D2 | D4  | D6    | D8     | DA  | _  | _  |

| 14      | \$YFFFF## | E0 | E2 | E4  | E6    | E8     | EA  | EC | EE |

| 15      | \$YFFFF## | F0 | F2 | F4  | F6    | F8     | FA  | FC | FE |

<sup>--</sup> Not Implemented

### 5.5 TPU Registers

The TPU memory map contains three groups of registers:

System Configuration Registers

Channel Control and Status Registers

Development Support and Test Verification Registers

### 5.5.1 System Configuration Registers

# **TPUMCR** — TPU Module Configuration Register

\$YFFE00

| 15     | 14  | 13  | 12  | 11  | 10  | 9    | 8   | 7    | 6    | 5 | 4 | 3 |     |    | 0 |

|--------|-----|-----|-----|-----|-----|------|-----|------|------|---|---|---|-----|----|---|

| STOP   | TCF | R1P | TCF | R2P | EMU | T2CG | STF | SUPV | PSCK | 0 | 0 |   | IAF | RB |   |

| RESET: |     |     |     |     |     |      |     |      |      |   |   |   |     |    |   |

| 0      | 0   | 0   | 0   | 0   | 0   | 0    | 0   | 1    | 0    | 0 | 0 | 0 | 0   | 0  | 0 |

STOP — Stop Bit

0 = TPU operating normally

1 = Internal clocks shut down

Y = M111, where M represents the logic state of the MM bit in the SIMCR.

| HSQR0  | — Но | st Seq | uence | Regist | er 0 |    |      |    |     |    |      |    |     | \$Y        | FFE14 |

|--------|------|--------|-------|--------|------|----|------|----|-----|----|------|----|-----|------------|-------|

| 15     | 14   | 13     | 12    | 11     | 10   | 9  | 8    | 7  | 6   | 5  | 4    | 3  | 2   | 1          | 0     |

| CH     | 15   | CH     | l 14  | CH     | l 13 | CH | l 12 | CH | 111 | CH | l 10 | Cl | H 9 | Cl         | 4 8   |

| RESET: |      |        |       | •      |      | •  |      | •  |     | •  |      |    |     | •          |       |

| 0      | 0    | 0      | 0     | 0      | 0    | 0  | 0    | 0  | 0   | 0  | 0    | 0  | 0   | 0          | 0     |

| HSQR1  | — Но | st Seq | uence | Regist | er 1 |    |      |    |     |    |      |    |     | <b>\$Y</b> | FFE16 |

| 15     | 14   | 13     | 12    | 11     | 10   | 9  | 8    | 7  | 6   | 5  | 4    | 3  | 2   | 1          | 0     |

| СН     | 7    | Cl     | H 6   | Cl     | H 5  | CI | H 4  | С  | H 3 | CI | H 2  | CI | H 1 | CI         | 1 0   |

| RESET: |      | •      |       | •      |      | •  |      |    |     | •  |      | •  |     | •          |       |

| 0      | 0    | 0      | 0     | 0      | 0    | 0  | 0    | 0  | 0   | 0  | 0    | 0  | 0   | 0          | 0     |

#### CH[15:0] — Encoded Host Sequence

The host sequence field selects the mode of operation for the time function selected on a given channel. The meaning of the host sequence bits depends on the time function specified.

| HSRR0  | — Но | st Serv | ice Re         | quest | Registe        | er O |    |    |      |    |     |    |                | \$YI | FFE18 |

|--------|------|---------|----------------|-------|----------------|------|----|----|------|----|-----|----|----------------|------|-------|

| 15     | 14   | 13      | 12             | 11    | 10             | 9    | 8  | 7  | 6    | 5  | 4   | 3  | 2              | 1    | 0     |

| СН     | 15   | CH      | l 14           | CH    | l 13           | CH   | 12 | CH | l 11 | CH | 110 | CI | <del>1</del> 9 | CH   | 4 8   |

| RESET: |      | •       |                | •     |                |      |    | •  |      | •  |     | •  |                | •    |       |

| 0      | 0    | 0       | 0              | 0     | 0              | 0    | 0  | 0  | 0    | 0  | 0   | 0  | 0              | 0    | 0     |

| HSRR1  | — Но | st Serv | ice Re         | quest | Registe        | er 1 |    |    |      |    |     |    |                | \$YF | FE1A  |

| 15     | 14   | 13      | 12             | 11    | 10             | 9    | 8  | 7  | 6    | 5  | 4   | 3  | 2              | 1    | 0     |

| СН     | 7    | Cl      | <del>1</del> 6 | CI    | <del>1</del> 5 | Cl   | 14 | CI | 13   | CH | 12  | CI | 11             | Cl   | H 0   |

| RESET: |      | •       |                | •     |                |      |    | •  |      | •  |     | •  |                | •    |       |

| 0      |      |         | 0              |       |                | 0    |    |    |      |    |     |    |                |      |       |

### CH[15:0] — Encoded Type of Host Service

The host service request field selects the type of host service request for the time function selected on a given channel. The meaning of the host service request bits depends on the time function specified. A host service request field cleared to %00 signals the host that service is completed by the microengine on that channel. The host can request service on a channel by writing the corresponding host service request field to one of three nonzero states. The CPU should monitor the host service request register until the TPU clears the service request to %00 before the CPU changes any parameters or issues a new service request to the channel.

| CPR0 - | – Char | nnel Pr | iority F | Registe | r 0            |    |                |    |     |    |      |    |     | \$YF | FE1C |

|--------|--------|---------|----------|---------|----------------|----|----------------|----|-----|----|------|----|-----|------|------|

| 15     | 14     | 13      | 12       | 11      | 10             | 9  | 8              | 7  | 6   | 5  | 4    | 3  | 2   | 1    | 0    |

| CH     | 15     | CH      | l 14     | CH      | 113            | CH | l 12           | CH | 111 | CH | l 10 | CI | H 9 | CI   | 18   |

| RESET: |        | •       |          | •       |                | •  |                |    |     |    |      |    |     |      |      |

| 0      | 0      | 0       | 0        | 0       | 0              | 0  | 0              | 0  | 0   | 0  | 0    | 0  | 0   | 0    | 0    |

| CPR1 - | – Char | nnel Pr | iority F | Registe | r 1            |    |                |    |     |    |      |    |     | \$YF | FE1E |

| 15     | 14     | 13      | 12       | 11      | 10             | 9  | 8              | 7  | 6   | 5  | 4    | 3  | 2   | 1    | 0    |

| СН     | 7      | CH      | 16       | CH      | <del>1</del> 5 | Cl | <del> </del> 4 | CI | H 3 | CI | H 2  | CI | H 1 | Cl   | 10   |

| RESET: |        |         |          |         |                | •  |                |    |     | •  |      |    |     | •    |      |

| 0      | 0      | 0       | 0        | 0       | 0              | 0  | 0              | 0  | 0   | 0  | 0    | 0  | 0   | 0    | 0    |

CH[15:0] — Encoded One of Three Channel Priority Levels

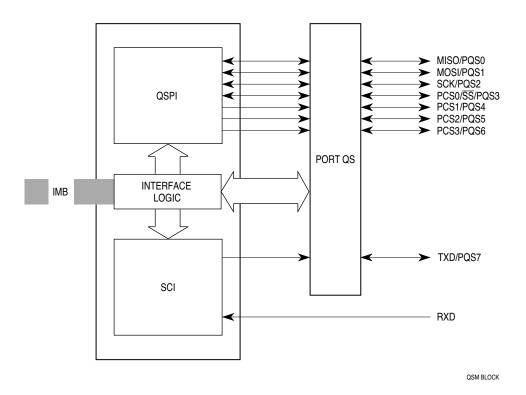

#### 6 Queued Serial Module

The QSM contains two serial interfaces, the queued serial peripheral interface (QSPI) and the serial communication interface (SCI).

Figure 13 QSM Block Diagram

#### 6.1 Overview

The QSPI provides easy peripheral expansion or interprocessor communication through a full-duplex, synchronous, three-line bus: data in, data out, and a serial clock. Four programmable peripheral chipselect pins provide addressability for up to 16 peripheral devices. A self-contained RAM queue allows up to 16 serial transfers of 8 to 16 bits each, or transmission of a 256-bit data stream without CPU intervention. A special wraparound mode supports continuous sampling of a serial peripheral, with automatic QSPI RAM updating, which makes the interface to A/D converters more efficient.

The SCI provides a standard nonreturn to zero (NRZ) mark/space format. It operates in either full- or half-duplex mode. There are separate transmitter and receiver enable bits and dual data buffers. A modulus-type baud rate generator provides rates from 64 to 524 kbaud with a 16.78-MHz system clock, or 110 to 655 kbaud with a 20.97-MHz system clock. Word length of either 8 or 9 bits is software selectable. Optional parity generation and detection provide either even or odd parity check capability. Advanced error detection circuitry catches glitches of up to 1/16 of a bit time in duration. Wakeup functions allow the CPU to run uninterrupted until meaningful data is available.

An address map of the QSM is shown below.

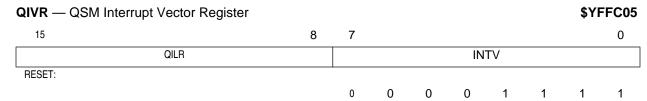

At reset, QIVR is initialized to \$0F, which corresponds to the uninitialized interrupt vector in the exception table. This vector is selected until QIVR is written. A user-defined vector (\$40–\$FF) should be written to QIVR during QSM initialization.

After initialization, QIVR determines which two vectors in the exception vector table are to be used for QSM interrupts. The QSPI and SCI submodules have separate interrupt vectors adjacent to each other. Both submodules use the same interrupt vector with the least significant bit (LSB) determined by the submodule causing the interrupt.

The value of INTV0 used during an interrupt-acknowledge cycle is supplied by the QSM. During an interrupt-acknowledge cycle, INTV[7:1] are driven on DATA[7:1] IMB lines. DATA0 is negated for an SCI interrupt and asserted for a QSPI interrupt. Writes to INTV0 have no meaning or effect. Reads of INTV0 return a value of one.

#### 6.4.2 Pin Control Registers

The QSM uses nine pins, eight of which form a parallel port (PORTQS) on the MCU. Although these pins are used by the serial subsystems, any pin can alternately be assigned as general-purpose I/O on a pin-by-pin basis.

Pins used for general-purpose I/O must not be assigned to the QSPI by register PQSPAR. To avoid driving incorrect data, the first byte to be output must be written before DDRQS is configured. DDRQS must then be written to determine the direction of data flow and to output the value contained in register PORTQS. Subsequent data for output is written to PORTQS.

#### **PORTQS** — Port QS Data Register

\$YFFC14

| 15       | 8 | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------|---|------|------|------|------|------|------|------|------|

| NOT USED |   | PQS7 | PQS6 | PQS5 | PQS4 | PQS3 | PQS2 | PQS1 | PQS0 |

|          |   | RES  | SET: |      | •    |      |      |      |      |

|          |   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

PORTQS latches I/O data. Writes drive pins defined as outputs. Reads return data present on the pins. To avoid driving undefined data, first write a byte to PORTQS, then configure DDRQS.

PQSPAR — PORT QS Pin Assignment Register

DDRQS — PORT QS Data Direction Register

\$YFFC16 \$YFFC17

| 15     | 14     | 13     | 12     | 11     | 10 | 9      | 8      | /     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|--------|--------|--------|--------|----|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0      | PQSPA6 | PQSPA5 | PQSPA4 | PQSPA3 | 0  | PQSPA1 | PQSPA0 | DDQS7 | DDQS6 | DDQS5 | DDQS4 | DDQS3 | DDQS2 | DDQS1 | DDQS0 |

| RESET: |        |        |        |        |    |        |        |       |       |       |       |       |       |       |       |

| •      | •      | •      | •      | ^      | ^  | ^      | •      | •     | ^     | ^     | •     | •     | •     | •     | •     |

Clearing a bit in the PQSPAR assigns the corresponding pin to general-purpose I/O; setting a bit assigns the pin to the QSPI. The PQSPAR does not affect operation of the SCI.

### Table 26 Effect of DDRQS on QSM Pin Function

| QSM Pin          | Mode     | DDRQS<br>Bit | Bit<br>State | Pin Function                 |

|------------------|----------|--------------|--------------|------------------------------|

| MISO             | Master   | DDQ0         | 0            | Serial Data Input to QSPI    |

|                  |          |              | 1            | Disables Data Input          |

|                  | Slave    | ]            | 0            | Disables Data Output         |

|                  |          |              | 1            | Serial Data Output from QSPI |

| MOSI             | Master   | DDQ1         | 0            | Disables Data Output         |

|                  |          |              | 1            | Serial Data Output from QSPI |

|                  | Slave    |              | 0            | Serial Data Input to QSPI    |

|                  |          |              | 1            | Disables Data Input          |

| SCK <sup>1</sup> | Master   | DDQ2         | 0            | Disables Clock Output        |

|                  |          |              | 1            | Clock Output from QSPI       |

|                  | Slave    | 1            | 0            | Clock Input to QSPI          |

|                  |          |              | 1            | Disables Clock Input         |

| PCS0/SS          | Master   | DDQ3         | 0            | Assertion Causes Mode Fault  |

|                  |          |              | 1            | Chip-Select Output           |

|                  | Slave    |              | 0            | QSPI Slave Select Input      |

|                  |          |              | 1            | Disables Select Input        |

| PCS[3:1]         | Master   | DDQ[4:6]     | 0            | Disables Chip-Select Output  |

|                  |          |              | 1            | Chip-Select Output           |

|                  | Slave    |              | 0            | Inactive                     |

|                  |          |              | 1            | Inactive                     |

| TXD <sup>2</sup> | Transmit | DDQ7         | Х            | Serial Data Output from SCI  |

| RXD              | Receive  | None         | NA           | Serial Data Input to SCI     |

#### NOTES:

- 1. PQS2 is a digital I/O pin unless the SPI is enabled (SPE in SPCR1 set), in which case it becomes SPI serial clock SCK.

- 2. PQS7 is a digital I/O pin unless the SCI transmitter is enabled (TE in SCCR1 = 1), in which case it becomes SCI serial output TXD.

DDRQS determines the direction of the TXD pin only when the SCI transmitter is disabled. When the SCI transmitter is enabled, the TXD pin is an output.

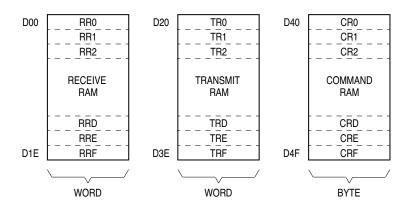

QSPI RAM MAP

Figure 15 QSPI RAM

Once the CPU has set up the queue of QSPI commands and enabled the QSPI, the QSPI can operate independently of the CPU. The QSPI executes all of the commands in its queue, sets a flag indicating that it is finished, and then either interrupts the CPU or waits for CPU intervention. It is possible to execute a queue of commands repeatedly without CPU intervention.

### RR[0:F] — Receive Data RAM

\$YFFD00

Data received by the QSPI is stored in this segment. The CPU reads this segment to retrieve data from the QSPI. Data stored in receive RAM is right-justified. Unused bits in a receive queue entry are set to zero by the QSPI upon completion of the individual queue entry. The CPU can access the data using byte, word, or long-word addressing.

The CPTQP value in SPSR shows which queue entries have been executed. The CPU uses this information to determine which locations in receive RAM contain valid data before reading them.

#### TR[0:F] — Transmit Data RAM

\$YFFD20

Data that is to be transmitted by the QSPI is stored in this segment. The CPU usually writes one word of data into this segment for each queue command to be executed.

Information to be transmitted must be written to transmit data RAM in a right-justified format. The QSPI cannot modify information in the transmit data RAM. The QSPI copies the information to its data serializer for transmission. Information remains in transmit RAM until overwritten.

### CR[0:F] — Command RAM

\$YFFD40

| 7    | 6     | 5  | 4    | 3    | 2    | 1    | 0     |

|------|-------|----|------|------|------|------|-------|

| CONT | BITSE | DT | DSCK | PCS3 | PCS2 | PCS1 | PCS0* |

|      |       |    |      |      |      |      |       |

| _    | _     | -  | -    | _    | _    | -    | _     |

|      |       |    |      |      |      |      |       |

| CONT | BITSE | DT | DSCK | PCS3 | PCS2 | PCS1 | PCS0* |

COMMAND CONTROL

PERIPHERAL CHIP SELECT

<sup>\*</sup>The PCS0 bit represents the dual-function PCS0/SS.

Writing a value of zero to SCBR disables the baud rate generator.

The following table lists the SCBR settings for standard and maximum baud rates using 16.78-MHz and 20.97-MHz system clocks.

#### **Table 27 SCI Baud Rates**

| N | ominal Baud Rate |

|---|------------------|

|   | 64*              |

|   | 110              |

|   | 300              |

|   | 600              |

|   | 1200             |

|   | 2400             |

|   | 4800             |

|   | 9600             |

|   | 19200            |

|   | 38400            |

|   | 76800            |

|   | Maximum Rate     |

| Actual Rate with 16.78-MHz Clock | SCBR Value |  |  |  |  |  |

|----------------------------------|------------|--|--|--|--|--|

| 64.0                             | \$1FFF     |  |  |  |  |  |

| 110.0                            | \$129E     |  |  |  |  |  |

| 299.9                            | \$06D4     |  |  |  |  |  |

| 599.9                            | \$036A     |  |  |  |  |  |

| 1199.7                           | \$0165     |  |  |  |  |  |

| 2405.0                           | \$00DA     |  |  |  |  |  |

| 4810.0                           | \$006D     |  |  |  |  |  |

| 9532.5                           | \$0037     |  |  |  |  |  |

| 19418.1                          | \$0016     |  |  |  |  |  |

| 37449.1                          | \$000E     |  |  |  |  |  |

| 74898.3                          | \$0007     |  |  |  |  |  |

| 524288.0                         | \$0001     |  |  |  |  |  |

| Actual Rate with 20.97-MHz Clock | SCBR Value |  |  |  |  |  |

|----------------------------------|------------|--|--|--|--|--|

| _                                | _          |  |  |  |  |  |

| 110.0                            | \$1745     |  |  |  |  |  |

| 300.1                            | \$0888     |  |  |  |  |  |

| 600.1                            | \$0444     |  |  |  |  |  |

| 1200.3                           | \$0222     |  |  |  |  |  |

| 2400.6                           | \$0111     |  |  |  |  |  |

| 4783.6                           | \$0089     |  |  |  |  |  |

| 9637.6                           | \$0044     |  |  |  |  |  |

| 19275.3                          | \$0022     |  |  |  |  |  |

| 38550.6                          | \$0011     |  |  |  |  |  |

| 72817.8                          | \$0009     |  |  |  |  |  |

| 655360.0                         | \$0001     |  |  |  |  |  |

|                                  |            |  |  |  |  |  |

#### **SCCR1** — SCI Control Register 1

\$YFFC0A

|   | 15     | 14    | 13   | 12  | 11 | 10 | 9 | 8    | 7   | 6    | 5   | 4    | 3  | 2  | 1   | 0   |

|---|--------|-------|------|-----|----|----|---|------|-----|------|-----|------|----|----|-----|-----|

|   | 0      | LOOPS | WOMS | ILT | PT | PE | М | WAKE | TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

| • | RESET: |       |      |     | •  |    |   |      | •   | •    |     |      |    |    |     |     |

|   | •      | •     | •    | •   | •  | •  | • | •    | •   | •    | •   | •    | •  | •  | •   | •   |

SCCR1 contains SCI configuration parameters. The CPU can read and write this register at any time. The SCI can modify RWU in some circumstances. In general, interrupts enabled by these control bits are cleared by reading SCSR, then reading (receiver status bits) or writing (transmitter status bits) SCDR.

#### Bit 15 — Not Implemented

### LOOPS — Loop Mode

- 0 = Normal SCI operation, no looping, feedback path disabled

- 1 = Test SCI operation, looping, feedback path enabled

LOOPS controls a feedback path on the data serial shifter. When loop mode is enabled, SCI transmitter output is fed back into the receive serial shifter. TXD is asserted (idle line). Both transmitter and receiver must be enabled before entering loop mode.

### WOMS — Wired-OR Mode for SCI Pins

- 0 = If configured as an output, TXD is a normal CMOS output.

- 1 = If configured as an output, TXD is an open-drain output.

WOMS determines whether the TXD pin is an open-drain output or a normal CMOS output. This bit is used only when TXD is an output. If TXD is used as a general-purpose input pin, WOMS has no effect.

### ILT — Idle-Line Detect Type

- 0 = Short idle-line detect (start count on first one)

- 1 = Long idle-line detect (start count on first one after stop bit(s))

#### PT — Parity Type

- 0 = Even parity

- 1 = Odd parity

When parity is enabled, PT determines whether parity is even or odd for both the receiver and the transmitter.