TUTUTI

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | CPU32                                                                 |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 25MHz                                                                 |

| Connectivity               | EBI/EMI, SCI, SPI, UART/USART                                         |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 15                                                                    |

| Program Memory Size        | -                                                                     |

| Program Memory Type        | ROMIess                                                               |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 144-LQFP                                                              |

| Supplier Device Package    | 144-LQFP (20x20)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68332acpv25 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Package Type | ТРU Туре       | Temperature    | Frequency<br>(MHz) | Package<br>Order<br>Quantity | Order Number    |                 |                 |

|--------------|----------------|----------------|--------------------|------------------------------|-----------------|-----------------|-----------------|

| 132-Pin PQFP | Motion Control | -40 to +85 °C  | 16 MHz             | 2 pc tray                    | SPAKMC332GCFC16 |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332GCFC16   |                 |                 |

|              | 20 MHz         |                | 2 pc tray          | SPAKMC332GCFC20              |                 |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332GCFC20   |                 |                 |

|              |                | –40 to +105 °C | 16 MHz             | 2 pc tray                    | SPAKMC332GVFC16 |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332GVFC16   |                 |                 |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332GVFC20 |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332GVFC20   |                 |                 |

|              |                | –40 to +125 °C | 16 MHz             | 2 pc tray                    | SPAKMC332GMFC16 |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332GMFC16   |                 |                 |

|              |                |                |                    | 20 MHz                       | 2 pc tray       | SPAKMC332GMFC20 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332GMFC20   |                 |                 |

|              | Standard       | –40 to +85 °C  | 16 MHz             | 2 pc tray                    | SPAKMC332CFC16  |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332CFC16    |                 |                 |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332CFC20  |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332CFC20    |                 |                 |

|              |                | –40 to +105 °C | 16 MHz             | 2 pc tray                    | SPAKMC332VFC16  |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332VFC16    |                 |                 |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332VFC20  |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332VFC20    |                 |                 |

|              |                | –40 to +125 °C | 16 MHz             | 2 pc tray                    | SPAKMC332MFC16  |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332MFC16    |                 |                 |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332MFC20  |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332MFC20    |                 |                 |

|              | Std w/enhanced | –40 to +85 °C  | 16 MHz             | 2 pc tray                    | SPAKMC332ACFC16 |                 |                 |

|              | PPWA           |                |                    | 36 pc tray                   | MC68332ACFC16   |                 |                 |

|              |                |                |                    |                              | 20 MHz          | 2 pc tray       | SPAKMC332ACFC20 |

|              |                |                |                    | 36 pc tray                   | MC68332ACFC20   |                 |                 |

|              |                | –40 to +105 °C | 16 MHz             | 2 pc tray                    | SPAKMC332AVFC16 |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332AVFC16   |                 |                 |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332AVFC20 |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332AVFC20   |                 |                 |

|              |                | –40 to +125 °C | 16 MHz             | 2 pc tray                    | SPAKMC332AMFC16 |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332AMFC16   |                 |                 |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332AMFC20 |                 |                 |

|              |                |                |                    | 36 pc tray                   | MC68332AMFC20   |                 |                 |

### **Table 1 Ordering Information**

| Package Type | TPU Type       | Temperature    | Frequency<br>(MHz) | Package<br>Order<br>Quantity | Order Number    |                |

|--------------|----------------|----------------|--------------------|------------------------------|-----------------|----------------|

| 144-Pin QFP  | Motion Control | –40 to +85 °C  | 16 MHz             | 2 pc tray                    | SPAKMC332GCFV16 |                |

|              |                |                |                    | 44 pc tray                   | MC68332GCFVV16  |                |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332GCFV20 |                |

|              |                |                |                    | 44 pc tray                   | MC68332GCFV20   |                |

|              |                | -40 to +105 °C | 16 MHz             | 2 pc tray                    | SPAKMC332GVFV16 |                |

|              |                |                |                    | 44 pc tray                   | MC68332GVFV16   |                |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332GVFV20 |                |

|              |                |                |                    | 44 pc tray                   | MC68332GVFV20   |                |

|              |                | -40 to +125 °C | 16 MHz             | 2 pc tray                    | SPAKMC332GMFV16 |                |

|              |                |                |                    | 44 pc tray                   | MC68332GMFV16   |                |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332GMFV20 |                |

|              |                |                |                    | 44 pc tray                   | MC68332GMFVV20  |                |

|              | Standard       | –40 to +85 °C  | 16 MHz             | 2 pc tray                    | SPAKMC332CFV16  |                |

|              |                |                |                    | 44 pc tray                   | MC68332CFV16    |                |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332CFVV20 |                |

|              |                |                |                    | 44 pc tray                   | MC68332CFV20    |                |

|              |                | -40 to +105 °C | 16 MHz             | 2 pc tray                    | SPAKMC332VFV16  |                |

|              |                |                |                    | 44 pc tray                   | MC68332VFV16    |                |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332VFV20  |                |

|              |                |                |                    | 44 pc tray                   | MC68332VFV20    |                |

|              |                | -40 to +125 °C | -40 to +125 °C     | 16 MHz                       | 2 pc tray       | SPAKMC332MFV16 |

|              |                |                |                    | 44 pc tray                   | MC68332MFV16    |                |

|              |                | 20 MHz         | 2 pc tray          | SPAKMC332MFV20               |                 |                |

|              |                |                |                    | 44 pc tray                   | MC68332MFV20    |                |

|              | Std w/enhanced | –40 to +85 °C  | 16 MHz             | 2 pc tray                    | SPAKMC332ACFV16 |                |

|              | PPWA           |                |                    | 44 pc tray                   | MC68332ACFV16   |                |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332ACFV20 |                |

|              |                |                |                    | 44 pc tray                   | MC68332ACFV20   |                |

|              |                | –40 to +105 °C | 16 MHz             | 2 pc tray                    | SPAKMC332AVFV16 |                |

|              |                |                |                    | 44 pc tray                   | MC68332AVFV16   |                |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332AVFC20 |                |

|              |                |                |                    | 44 pc tray                   | MC68332AVFV20   |                |

|              |                | –40 to +125 °C | 16 MHz             | 2 pc tray                    | SPAKMC332AMFV16 |                |

|              |                |                |                    | 44 pc tray                   | MC68332AMFV16   |                |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332AMFV20 |                |

| ŀ            |                |                |                    | 44 pc tray                   | MC68332AMFV20   |                |

#### Table 1 Ordering Information (Continued)

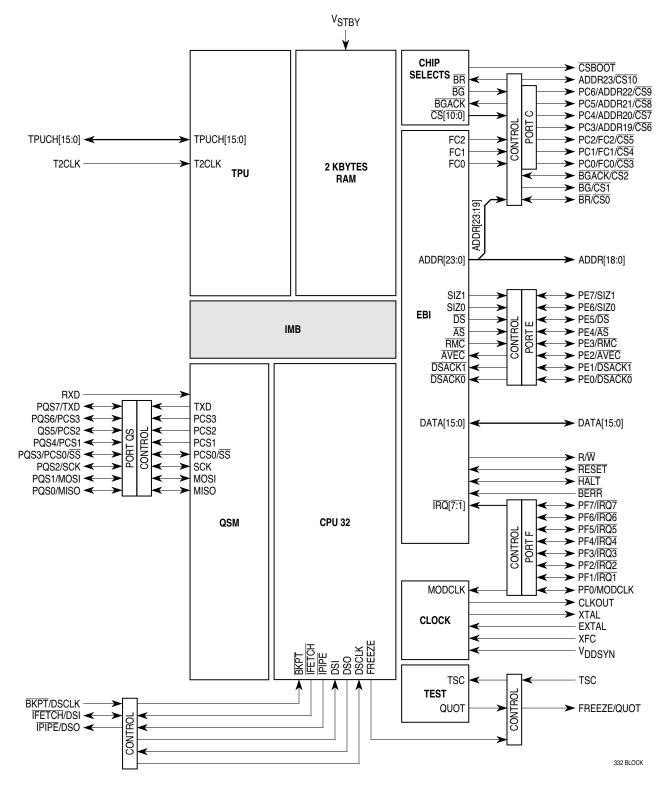

1.2 Block Diagram

Figure 1 MCU Block Diagram

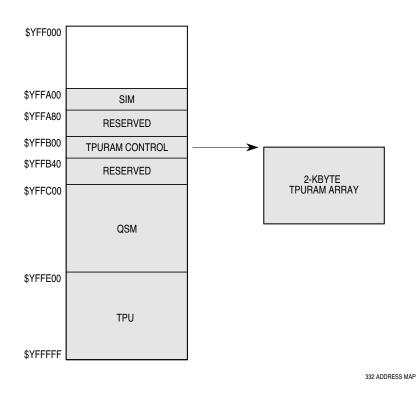

#### 1.4 Address Map

The following figure is a map of the MCU internal addresses. The RAM array is positioned by the base address registers in the associated RAM control block. Unimplemented blocks are mapped externally.

Figure 4 MCU Address Map

#### 1.5 Intermodule Bus

The intermodule bus (IMB) is a standardized bus developed to facilitate both design and operation of modular microcontrollers. It contains circuitry to support exception processing, address space partitioning, multiple interrupt levels, and vectored interrupts. The standardized modules in the MCU communicate with one another and with external components through the IMB. The IMB in the MCU uses 24 address and 16 data lines.

### **2 Signal Descriptions**

#### 2.1 Pin Characteristics

The following table shows MCU pins and their characteristics. All inputs detect CMOS logic levels. All inputs can be put in a high-impedance state, but the method of doing this differs depending upon pin function. Refer to the table, MCU Driver Types, for a description of output drivers. An entry in the discrete I/O column of the MCU Pin Characteristics table indicates that a pin has an alternate I/O function. The port designation is given when it applies. Refer to the MCU Block Diagram for information about port organization.

| Pin<br>Mnemonic         | Output<br>Driver | Input<br>Synchronized | Input<br>Hysteresis | Discrete<br>I/O | Port<br>Designation |

|-------------------------|------------------|-----------------------|---------------------|-----------------|---------------------|

| ADDR23/CS10/ECLK        | A                | Y                     | N                   | 0               | —                   |

| ADDR[22:19]/CS[9:6]     | A                | Y                     | N                   | 0               | PC[6:3]             |

| ADDR[18:0]              | A                | Y                     | N                   | —               | —                   |

| ĀS                      | В                | Y                     | N                   | I/O             | PE5                 |

| AVEC                    | В                | Y                     | N                   | I/O             | PE2                 |

| BERR                    | В                | Y                     | N                   | _               |                     |

| BG/CS1                  | В                | _                     | —                   | _               |                     |

| BGACK/CS2               | В                | Y                     | N                   | _               |                     |

| BKPT/DSCLK              |                  | Y                     | Y                   | _               |                     |

| BR/CS0                  | В                | Y                     | N                   | —               |                     |

| CLKOUT                  | A                | _                     | —                   | _               |                     |

| CSBOOT                  | В                |                       | _                   | —               |                     |

| DATA[15:0] <sup>1</sup> | Aw               | Y                     | N                   | —               |                     |

| DS                      | В                | Y                     | N                   | I/O             | PE4                 |

| DSACK1                  | В                | Y                     | N                   | I/O             | PE1                 |

| DSACK0                  | В                | Y                     | N                   | I/O             | PE0                 |

| DSI/IFETCH              | A                | Y                     | Y                   | —               |                     |

| DSO/IPIPE               | A                |                       | —                   | —               | _                   |

| EXTAL <sup>2</sup>      | —                |                       | Special             | —               |                     |

| FC[2:0]/CS[5:3]         | A                | Y                     | N                   | 0               | PC[2:0]             |

| FREEZE/QUOT             | A                |                       | _                   | —               |                     |

| HALT                    | Bo               | Y                     | N                   | —               |                     |

| IRQ[7:1]                | В                | Y                     | Y                   | I/O             | PF[7:1]             |

| MISO                    | Bo               | Y                     | Y                   | I/O             | PQS0                |

| MODCLK <sup>1</sup>     | В                | Y                     | N                   | I/O             | PF0                 |

| MOSI                    | Во               | Y                     | Y                   | I/O             | PQS1                |

| PCS0/SS                 | Во               | Y                     | Y                   | I/O             | PQS3                |

| PCS[3:1]                | Во               | Y                     | Y                   | I/O             | PQS[6:4]            |

| R/W                     | A                | Y                     | N                   | _               |                     |

| RESET                   | Во               | Y                     | Y                   | —               | —                   |

| RMC                     | В                | Y                     | N                   | I/O             | PE3                 |

| RXD                     | —                | Ν                     | N                   | —               | —                   |

| SCK                     | Bo               | Y                     | Y                   | I/O             | PQS2                |

| SIZ[1:0]                | В                | Y                     | N                   | I/O             | PE[7:6]             |

#### Table 2 MCU Pin Characteristic

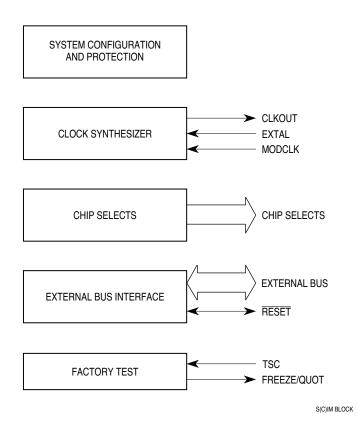

#### **3 System Integration Module**

The MCU system integration module (SIM) consists of five functional blocks that control system startup, initialization, configuration, and external bus.

#### 3.1 Overview

The system configuration and protection block controls MCU configuration and operating mode. The block also provides bus and software watchdog monitors.

The system clock generates clock signals used by the SIM, other IMB modules, and external devices. In addition, a periodic interrupt generator supports execution of time-critical control routines.

The external bus interface handles the transfer of information between IMB modules and external address space.

The chip-select block provides eleven general-purpose chip-select signals and a boot ROM chip select signal. Both general-purpose and boot ROM chip-select signals have associated base address registers and option registers.

The system test block incorporates hardware necessary for testing the MCU. It is used to perform factory tests, and its use in normal applications is not supported.

The SIM control register address map occupies 128 bytes. Unused registers within the 128-byte address space return zeros when read. The "Access" column in the SIM address map below indicates which registers are accessible only at the supervisor privilege level and which can be assigned to either the supervisor or user privilege level, according to the value of the SUPV bit in the SIMCR.

- EXOFF External Clock Off

- 0 = The CLKOUT pin is driven from an internal clock source.

- 1 = The CLKOUT pin is placed in a high-impedance state.

#### FRZSW — Freeze Software Enable

- 0 = When FREEZE is asserted, the software watchdog and periodic interrupt timer counters continue to run.

- 1 = When FREEZE is asserted, the software watchdog and periodic interrupt timer counters are disabled, preventing interrupts during software debug.

- FRZBM Freeze Bus Monitor Enable

- 0 = When FREEZE is asserted, the bus monitor continues to operate.

- 1 = When FREEZE is asserted, the bus monitor is disabled.

#### SLVEN — Factory Test Mode Enabled

This bit is a read-only status bit that reflects the state of DATA11 during reset.

- 0 = IMB is not available to an external master.

- 1 = An external bus master has direct access to the IMB.

#### SHEN[1:0] — Show Cycle Enable

This field determines what the EBI does with the external bus during internal transfer operations. A show cycle allows internal transfers to be externally monitored. The table below shows whether show cycle data is driven externally, and whether external bus arbitration can occur. To prevent bus conflict, external peripherals must not be enabled during show cycles.

| SHEN | Action                                                                                        |

|------|-----------------------------------------------------------------------------------------------|

| 00   | Show cycles disabled, external arbitration enabled                                            |

| 01   | Show cycles enabled, external arbitration disabled                                            |

| 10   | Show cycles enabled, external arbitration enabled                                             |

| 11   | Show cycles enabled, external arbitration enabled, internal activity is halted by a bus grant |

#### SUPV — Supervisor/Unrestricted Data Space

The SUPV bit places the SIM global registers in either supervisor or user data space.

- 0 = Registers with access controlled by the SUPV bit are accessible from either the user or supervisor privilege level.

- 1 = Registers with access controlled by the SUPV bit are restricted to supervisor access only.

#### MM — Module Mapping

- 0 = Internal modules are addressed from \$7FF000 -\$7FFFFF.

- 1 = Internal modules are addressed from \$FFF000 \$FFFFFF.

#### IARB[3:0] — Interrupt Arbitration Field

Each module that can generate interrupt requests has an interrupt arbitration (IARB) field. Arbitration between interrupt requests of the same priority is performed by serial contention between IARB field bit values. Contention must take place whenever an interrupt request is acknowledged, even when there is only a single pending request. An IARB field must have a non-zero value for contention to take place. If an interrupt request from a module with an IARB field value of %0000 is recognized, the CPU processes a spurious interrupt exception. Because the SIM routes external interrupt requests to the CPU, the SIM IARB field value is used for arbitration between internal and external interrupts of the same priority. The reset value of IARB for the SIM is %1111, and the reset IARB value for all other modules is %0000, which prevents SIM interrupts from being discarded during initialization.

#### AVEC — Autovector Enable

0 = External interrupt vector enabled

1 = Autovector enabled

This field selects one of two methods of acquiring the interrupt vector during the interrupt acknowledge cycle. It is not usually used in conjunction with a chip-select pin.

If the chip select is configured to trigger on an interrupt acknowledge cycle (SPACE = 00) and the  $\overline{AVEC}$  field is set to one, the chip select automatically generates an  $\overline{AVEC}$  in response to the interrupt cycle. Otherwise, the vector must be supplied by the requesting device.

The AVEC bit must not be used in synchronous mode, as autovector response timing can vary because of ECLK synchronization.

#### 3.5.5 Port C Data Register

Bit values in port C determine the state of chip-select pins used for discrete output. When a pin is assigned as a discrete output, the value in this register appears at the output. This is a read/write register. Bit 7 is not used. Writing to this bit has no effect, and it always returns zero when read.

| <b>PORTC</b> — Port C Data Register |   |   |     |     |     |     |     | \$YF | FFA41 |

|-------------------------------------|---|---|-----|-----|-----|-----|-----|------|-------|

| 15                                  | 8 | 7 | 6   | 5   | 4   | 3   | 2   | 1    | 0     |

| NOT USED                            |   | 0 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1  | PC0   |

| RESET:                              |   |   |     |     |     |     |     |      |       |

|                                     |   | 0 | 1   | 1   | 1   | 1   | 1   | 1    | 1     |

#### 3.6 General-Purpose Input/Output

SIM pins can be configured as two general-purpose I/O ports, E and F. The following paragraphs describe registers that control the ports.

| PORTE0, PORTE1 — Port E Data Register |   |     |     |     |     | \$  | YFFA1 | 1, \$YF | FA13 |

|---------------------------------------|---|-----|-----|-----|-----|-----|-------|---------|------|

| 15                                    | 8 | 7   | 6   | 5   | 4   | 3   | 2     | 1       | 0    |

| NOT USED                              |   | PE7 | PE6 | PE5 | PE4 | PE3 | PE2   | PE1     | PE0  |

| RESET:                                |   |     |     |     |     |     |       |         |      |

|                                       |   | U   | U   | U   | U   | U   | U     | U       | U    |

A write to the port E data register is stored in the internal data latch and, if any port E pin is configured as an output, the value stored for that bit is driven on the pin. A read of the port E data register returns the value at the pin only if the pin is configured as a discrete input. Otherwise, the value read is the value stored in the register.

The port E data register is a single register that can be accessed in two locations. When accessed at \$YFFA11, the register is referred to as PORTE0; when accessed at \$YFFA13, the register is referred to as PORTE1. The register can be read or written at any time. It is unaffected by reset.

| DDRE — Port E Data Direction Register |   |      |      |      |      |      |      | \$YF | FFA15 |

|---------------------------------------|---|------|------|------|------|------|------|------|-------|

| 15                                    | 8 | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0     |

| NOT USED                              |   | DDE7 | DDE6 | DDE5 | DDE4 | DDE3 | DDE2 | DDE1 | DDE0  |

| RESET:                                |   |      |      |      |      |      |      |      |       |

|                                       |   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     |

The bits in this register control the direction of the pin drivers when the pins are configured as I/O. Any bit in this register set to one configures the corresponding pin as an output. Any bit in this register cleared to zero configures the corresponding pin as an input. This register can be read or written at any time.

| <b>PFPAR</b> — Port F Pin Assignment Register |   |       |       |       |       |       |       | \$YF  | FA1F  |

|-----------------------------------------------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 15                                            | 8 | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| NOT USED                                      |   | PFPA7 | PFPA6 | PFPA5 | PFPA4 | PFPA3 | PFPA2 | PFPA1 | PFPA0 |

| DEOET                                         |   |       | •     |       |       |       |       |       |       |

RESET:

DATA9 DATA9 DATA9 DATA9 DATA9 DATA9 DATA9 DATA9

The bits in this register control the function of each port F pin. Any bit cleared to zero defines the corresponding pin to be an I/O pin. Any bit set to one defines the corresponding pin to be an interrupt request signal or MODCLK. The MODCLK signal has no function after reset.

#### Table 17 Port F Pin Assignments

| PFPAR Field | Port F Signal | Alternate Signal |

|-------------|---------------|------------------|

| PFPA7       | PF7           | IRQ7             |

| PFPA6       | PF6           | IRQ6             |

| PFPA5       | PF5           | IRQ5             |

| PFPA4       | PF4           | IRQ4             |

| PFPA3       | PF3           | IRQ3             |

| PFPA2       | PF2           | IRQ2             |

| PFPA1       | PF1           | IRQ1             |

| PFPA0       | PF0           | MODCLK           |

Data bus pin 9 controls the state of this register following reset. If DATA9 is set to one during reset, the register is set to \$FF, which defines all port F pins as interrupt request inputs. If DATA9 is cleared to zero during reset, this register is set to \$00, defining all port F pins as I/O pins.

#### 3.7 Resets

Reset procedures handle system initialization and recovery from catastrophic failure. The MCU performs resets with a combination of hardware and software. The system integration module determines whether a reset is valid, asserts control signals, performs basic system configuration based on hardware mode-select inputs, then passes control to the CPU.

Reset occurs when an active low logic level on the RESET pin is clocked into the SIM. Resets are gated by the CLKOUT signal. Asynchronous resets are assumed to be catastrophic. An asynchronous reset can occur on any clock edge. Synchronous resets are timed to occur at the end of bus cycles. If there is no clock when RESET is asserted, reset does not occur until the clock starts. Resets are clocked in order to allow completion of write cycles in progress at the time RESET is asserted.

Reset is the highest-priority CPU32 exception. Any processing in progress is aborted by the reset exception, and cannot be restarted. Only essential tasks are performed during reset exception processing. Other initialization tasks must be accomplished by the exception handler routine.

#### 3.7.1 SIM Reset Mode Selection

The logic states of certain data bus pins during reset determine SIM operating configuration. In addition, the state of the MODCLK pin determines system clock source and the state of the BKPT pin determines what happens during subsequent breakpoint assertions. The following table is a summary of reset mode selection options.

#### Table 18 Reset Mode Selection

| Mode Select Pin | Default Function   | Alternate Function |

|-----------------|--------------------|--------------------|

|                 | (Pin Left High)    | (Pin Pulled Low)   |

|                 | (· ··· =•·····g··) | (                  |

| DATA0                                     | CSBOOT 16-Bit                                                                | CSBOOT 8-Bit                                                       |

|-------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------|

| DATA1                                     | CS0           CS1           CS2                                              | BR<br>BG<br>BGACK                                                  |

| DATA2                                     | CS3<br>CS4<br>CS5                                                            | FC0<br>FC1<br>FC2                                                  |

| DATA3<br>DATA4<br>DATA5<br>DATA6<br>DATA7 | CS6           CS[7:6]           CS[8:6]           CS[9:6]           CS[10:6] | ADDR19<br>ADDR[20:19]<br>ADDR[21:19]<br>ADDR[22:19]<br>ADDR[23:19] |

| DATA8                                     | DSACKO, DSACK1,<br>AVEC, DS, AS,<br>SIZ[1:0]                                 | PORTE                                                              |

| DATA9                                     | IRQ[7:1]<br>MODCLK                                                           | PORTF                                                              |

| DATA11                                    | Test Mode Disabled                                                           | Test Mode Enabled                                                  |

| MODCLK                                    | VCO = System Clock                                                           | EXTAL = System Clock                                               |

| BKPT                                      | Background Mode Disabled                                                     | Background Mode Enabled                                            |

#### Table 18 Reset Mode Selection

#### 3.7.2 Functions of Pins for Other Modules During Reset

Generally, pins associated with modules other than the SIM default to port functions, and input/output ports are set to input state. This is accomplished by disabling pin functions in the appropriate control registers, and by clearing the appropriate port data direction registers. Refer to individual module sections in this manual for more information. The following table is a summary of module pin function out of reset.

| Module | Pin Mnemonic      | Function        |

|--------|-------------------|-----------------|

| CPU32  | DSI/IFETCH        | DSI/IFETCH      |

|        | DSO/IPIPE         | DSO/IPIPE       |

|        | BKPT/DSCLK        | BKPT/DSCLK      |

| GPT    | PGP7/IC4/OC5      | Discrete Input  |

|        | PGP[6:3]/OC[4:1]  | Discrete Input  |

|        | PGP[2:0]/IC[3:1]  | Discrete Input  |

|        | PAI               | Discrete Input  |

|        | PCLK              | Discrete Input  |

|        | PWMA, PWMB        | Discrete Output |

| QSM    | PQS7/TXD          | Discrete Input  |

|        | PQS[6:4]/PCS[3:1] | Discrete Input  |

|        | PQS3/PCS0/SS      | Discrete Input  |

|        | PQS2/SCK          | Discrete Input  |

|        | PQS1/MOSI         | Discrete Input  |

|        | PQS0/MISO         | Discrete Input  |

|        | RXD               | RXD             |

#### **Table 19 Module Pin Functions**

**Freescale Semiconductor, Inc.**

#### 4.6 Instruction Set Summary

|                          |                                              | bie 20 instruction           |                                                                                                                                                                                    |

|--------------------------|----------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction              | Syntax                                       | Operand Size                 | Operation                                                                                                                                                                          |

| ABCD                     | Dn, Dn<br>– (An), – (An)                     | 8<br>8                       | Source <sub>10</sub> + Destination <sub>10</sub> + X $\Rightarrow$ Destination                                                                                                     |

| ADD                      | Dn, <ea><br/><ea>, Dn</ea></ea>              | 8, 16, 32<br>8, 16, 32       | Source + Destination $\Rightarrow$ Destination                                                                                                                                     |

| ADDA                     | <ea>, An</ea>                                | 16, 32                       | Source + Destination $\Rightarrow$ Destination                                                                                                                                     |

| ADDI                     | # <data>, <ea></ea></data>                   | 8, 16, 32                    | Immediate data + Destination $\Rightarrow$ Destination                                                                                                                             |

| ADDQ                     | # <data>, <ea></ea></data>                   | 8, 16, 32                    | Immediate data + Destination $\Rightarrow$ Destination                                                                                                                             |

| ADDX                     | Dn, Dn<br>– (An), – (An)                     | 8, 16, 32<br>8, 16, 32       | Source + Destination + $X \Rightarrow$ Destination                                                                                                                                 |

| AND                      | <ea>, Dn<br/>Dn, <ea></ea></ea>              | 8, 16, 32<br>8, 16, 32       | Source • Destination $\Rightarrow$ Destination                                                                                                                                     |

| ANDI                     | # <data>, <ea></ea></data>                   | 8, 16, 32                    | Data • Destination $\Rightarrow$ Destination                                                                                                                                       |

| ANDI to CCR              | # <data>, CCR</data>                         | 8                            | Source • CCR $\Rightarrow$ CCR                                                                                                                                                     |

| ANDI to SR1 <sup>1</sup> | # <data>, SR</data>                          | 16                           | Source • SR $\Rightarrow$ SR                                                                                                                                                       |

| ASL                      | Dn, Dn<br># <data>, Dn<br/>Í</data>          | 8, 16, 32<br>8, 16, 32<br>16 | X/C - 0                                                                                                                                                                            |

| ASR                      | Dn, Dn<br># <data>, Dn<br/>Í</data>          | 8, 16, 32<br>8, 16, 32<br>16 |                                                                                                                                                                                    |

| Bcc                      | label                                        | 8, 16, 32                    | If condition true, then $PC + d \Rightarrow PC$                                                                                                                                    |

| BCHG                     | Dn, <ea><br/># <data>, <ea></ea></data></ea> | 8, 32<br>8, 32               | $\overline{\text{bit number}}$ of destination) $\Rightarrow$ Z $\Rightarrow$ bit of destination                                                                                    |

| BCLR                     | Dn, <ea><br/># <data>, <ea></ea></data></ea> | 8, 32<br>8, 32               | $\overline{(\langle \text{bit number} \rangle \text{ of destination})}$<br>0 $\Rightarrow \overline{\text{bit of destination}}$                                                    |

| BGND                     | none                                         | none                         | If background mode enabled, then enter background mode, else format/vector $\Rightarrow$ – (SSP);<br>PC $\Rightarrow$ – (SSP); SR $\Rightarrow$ – (SSP); (vector) $\Rightarrow$ PC |

| BKPT                     | # <data></data>                              | none                         | If breakpoint cycle acknowledged, then execute returned operation word, else trap as illegal instruction                                                                           |

| BRA                      | label                                        | 8, 16, 32                    | $PC + d \Rightarrow PC$                                                                                                                                                            |

| BSET                     | Dn, <ea><br/># <data>, <ea></ea></data></ea> | 8, 32<br>8, 32               | $\overline{(\langle \text{bit number} \rangle \text{ of destination})} \Rightarrow Z;$<br>1 $\Rightarrow$ bit of destination                                                       |

| BSR                      | label                                        | 8, 16, 32                    | $SP - 4 \Rightarrow SP; PC \Rightarrow (SP); PC + d \Rightarrow PC$                                                                                                                |

| BTST                     | Dn, <ea><br/># <data>, <ea></ea></data></ea> | 8, 32<br>8, 32               | $\overline{(\langle \text{bit number} \rangle \text{of destination})} \Rightarrow Z$                                                                                               |

| СНК                      | <ea>, Dn</ea>                                | 16, 32                       | If Dn < 0 or Dn > (ea), then CHK exception                                                                                                                                         |

| CHK2                     | <ea>, Rn</ea>                                | 8, 16, 32                    | If Rn < lower bound or Rn > upper bound, then<br>CHK exception                                                                                                                     |

| CLR                      | Í                                            | 8, 16, 32                    | $0 \Rightarrow \text{Destination}$                                                                                                                                                 |

| CMP                      | <ea>, Dn</ea>                                | 8, 16, 32                    | (Destination – Source), CCR shows results                                                                                                                                          |

| CMPA                     | <ea>, An</ea>                                | 16, 32                       | (Destination – Source), CCR shows results                                                                                                                                          |

| CMPI                     | # <data>, <ea></ea></data>                   | 8, 16, 32                    | (Destination – Data), CCR shows results                                                                                                                                            |

| CMPM                     | (An) +, (An) +                               | 8, 16, 32                    | (Destination – Source), CCR shows results                                                                                                                                          |

| CMP2                     | <ea>, Rn</ea>                                | 8, 16, 32                    | Lower bound $\leq$ Rn $\leq$ Upper bound, CCR shows result                                                                                                                         |

#### **Table 20 Instruction Set Summary**

#### **5 Time Processor Unit**

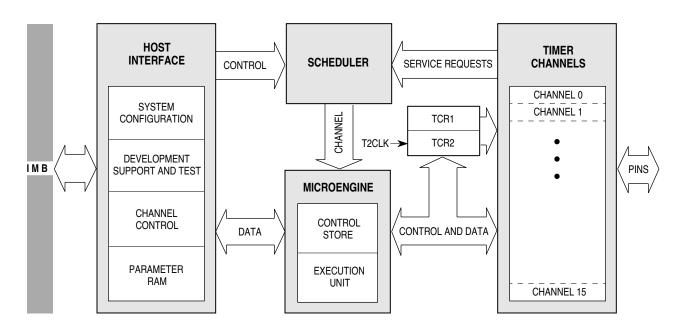

The time processor unit (TPU) provides optimum performance in controlling time-related activity. The TPU contains a dedicated execution unit, a tri-level prioritized scheduler, data storage RAM, dual-time bases, and microcode ROM. The TPU controls 16 independent, orthogonal channels, each with an associated I/O pin, and is capable of performing any microcoded time function. Each channel contains dedicated hardware that allows input or output events to occur simultaneously on all channels.

TPU BLOCK

Figure 12 TPU Block Diagram

#### 5.1 MC68332 and MC68332A Time Functions

The following paragraphs describe factory-programmed time functions implemented in standard and enhanced standard TPU microcode ROM. A complete description of the functions is beyond the scope of this summary. Refer to *Using the TPU Function Library and TPU Emulation Mode* (TPUPN00/D) as well as other TPU programming notes for more information about specific functions.

#### 5.1.1 Discrete Input/Output (DIO)

When a pin is used as a discrete input, a parameter indicates the current input level and the previous 15 levels of a pin. Bit 15, the most significant bit of the parameter, indicates the most recent state. Bit 14 indicates the next most recent state, and so on. The programmer can choose one of the three following conditions to update the parameter: 1) when a transition occurs, 2) when the CPU makes a request, or 3) when a rate specified in another parameter is matched. When a pin is used as a discrete output, it is set high or low only upon request by the CPU.

For More Information On This Product, Go to: www.freescale.com

#### 5.1.2 Input Capture/Input Transition Counter (ITC)

Any channel of the TPU can capture the value of a specified TCR upon the occurrence of each transition or specified number of transitions, and then generate an interrupt request to notify the CPU. A channel can perform input captures continually, or a channel can detect a single transition or specified number of transitions, then cease channel activity until reinitialization. After each transition or specified number of transitions, the channel can generate a link to a sequential block of up to eight channels. The user specifies a starting channel of the block and the number of channels within the block. The generation of links depends on the mode of operation. In addition, after each transition or specified number of transitions, one byte of the parameter RAM (at an address specified by channel parameter) can be incremented and used as a flag to notify another channel of a transition.

#### 5.1.3 Output Compare (OC)

The output compare function generates a rising edge, falling edge, or a toggle of the previous edge in one of three ways:

- 1. Immediately upon CPU initiation, thereby generating a pulse with a length equal to a programmable delay time.

- 2. At a programmable delay time from a user-specified time.

- 3. Continuously. Upon receiving a link from a channel, OC references, without CPU interaction, a specifiable period and calculates an offset:

Offset = Period \* Ratio

where Ratio is a parameter supplied by the user.

This algorithm generates a 50% duty-cycle continuous square wave with each high/low time equal to the calculated OFFSET. Due to offset calculation, there is an initial link time before continuous pulse generation begins.

#### 5.1.4 Pulse-Width Modulation (PWM)

The TPU can generate a pulse-width modulation waveform with any duty cycle from zero to 100% (within the resolution and latency capability of the TPU). To define the PWM, the CPU provides one parameter that indicates the period and another parameter that indicates the high time. Updates to one or both of these parameters can direct the waveform change to take effect immediately, or coherently beginning at the next low-to-high transition of the pin.

#### 5.1.5 Synchronized Pulse-Width Modulation (SPWM)

The TPU generates a PWM waveform in which the CPU can change the period and/or high time at any time. When synchronized to a time function on a second channel, the synchronized PWM low-to-high transitions have a time relationship to transitions on the second channel.

#### 5.1.6 Period Measurement with Additional Transition Detect (PMA)

This function and the following function are used primarily in toothed-wheel speed-sensing applications, such as monitoring rotational speed of an engine. The period measurement with additional transition detect function allows for a special-purpose 23-bit period measurement. It can detect the occurrence of an additional transition (caused by an extra tooth on the sensed wheel) indicated by a period measurement that is less than a programmable ratio of the previous period measurement.

Once detected, this condition can be counted and compared to a programmable number of additional transitions detected before TCR2 is reset to \$FFFF. Alternatively, a byte at an address specified by a channel parameter can be read and used as a flag. A nonzero value of the flag indicates that TCR2 is to be reset to \$FFFF once the next additional transition is detected.

#### 5.1.7 Period Measurement with Missing Transition Detect (PMM)

Period measurement with missing transition detect allows a special-purpose 23-bit period measurement. It detects the occurrence of a missing transition (caused by a missing tooth on the sensed wheel), indicated by a period measurement that is greater than a programmable ratio of the previous period measurement. Once detected, this condition can be counted and compared to a programmable number of additional transitions detected before TCR2 is reset to \$FFFF. In addition, one byte at an address specified by a channel parameter can be read and used as a flag. A nonzero value of the flag indicates that TCR2 is to be reset to \$FFFF once the next missing transition is detected.

#### 5.1.8 Position-Synchronized Pulse Generator (PSP)

Any channel of the TPU can generate an output transition or pulse, which is a projection in time based on a reference period previously calculated on another channel. Both TCRs are used in this algorithm: TCR1 is internally clocked, and TCR2 is clocked by a position indicator in the user's device. An example of a TCR2 clock source is a sensor that detects special teeth on the flywheel of an automobile using PMA or PMM. The teeth are placed at known degrees of engine rotation; hence, TCR2 is a coarse representation of engine degrees, i.e., each count represents some number of degrees.

Up to 15 position-synchronized pulse generator function channels can operate with a single input reference channel executing a PMA or PMM input function. The input channel measures and stores the time period between the flywheel teeth and resets TCR2 when the engine reaches a reference position. The output channel uses the period calculated by the input channel to project output transitions at specific engine degrees. Because the flywheel teeth might be 30 or more degrees apart, a fractional multiplication operation resolves down to the desired degrees. Two modes of operation allow pulse length to be determined either by angular position or by time.

#### 5.1.9 Stepper Motor (SM)

The stepper motor control algorithm provides for linear acceleration and deceleration control of a stepper motor with a programmable number of step rates of up to 14. Any group of channels, up to eight, can be programmed to generate the control logic necessary to drive a stepper motor.

The time period between steps (P) is defined as:

$$P(r) = K1 - K2 * r$$

where r is the current step rate (1-14), and K1 and K2 are supplied as parameters.

After providing the desired step position in a 16-bit parameter, the CPU issues a step request. Next, the TPU steps the motor to the desired position through an acceleration/deceleration profile defined by parameters. The parameter indicating the desired position can be changed by the CPU while the TPU is stepping the motor. This algorithm changes the control state every time a new step command is received.

A 16-bit parameter initialized by the CPU for each channel defines the output state of the associated pin. The bit pattern written by the CPU defines the method of stepping, such as full stepping or half stepping. With each transition, the 16-bit parameter rotates one bit. The period of each transition is defined by the programmed step rate.

#### 5.1.10 Period/Pulse-Width Accumulator (PPWA)

The period/pulse-width accumulator algorithm accumulates a 16-bit or 24-bit sum of either the period or the pulse width of an input signal over a programmable number of periods or pulses (from 1 to 255). After an accumulation period, the algorithm can generate a link to a sequential block of up to eight channels. The user specifies a starting channel of the block and number of channels within the block. Generation of links depends on the mode of operation. Any channel can be used to measure an accumulated number of periods of an input signal. A maximum of 24 bits can be used for the accumu-

| HSQR0              | — Ho       | st Sequ       | Jence       | Regist  | er 0       |       |          |       |          |       |         |      |          | \$YI             | FFE14              |

|--------------------|------------|---------------|-------------|---------|------------|-------|----------|-------|----------|-------|---------|------|----------|------------------|--------------------|

| 15                 | 14         | 13            | 12          | 11      | 10         | 9     | 8        | 7     | 6        | 5     | 4       | 3    | 2        | 1                | 0                  |

| CH 15              |            | CH 14         |             | CH 13   |            | CH 12 |          | CH 11 |          | CH 10 |         | CH 9 |          | CH 8             |                    |

| RESET:             |            |               |             |         |            |       |          |       |          |       |         |      |          |                  |                    |

| 0                  | 0          | 0             | 0           | 0       | 0          | 0     | 0        | 0     | 0        | 0     | 0       | 0    | 0        | 0                | 0                  |

|                    |            |               |             |         |            |       |          |       |          |       |         |      |          |                  |                    |

| HSQR1              | — Ho       | st Sequ       | uence       | Regist  | er 1       |       |          |       |          |       |         |      |          | \$YI             | FFE16              |

| <b>HSQR1</b><br>15 | — Ho<br>14 | st Sequ<br>13 | uence<br>12 | Registe | er 1<br>10 | 9     | 8        | 7     | 6        | 5     | 4       | 3    | 2        | <b>\$YI</b><br>1 | F <b>FE16</b><br>0 |

|                    | 14         | 13            |             | 11      |            | -     | 8<br>H 4 |       | 6<br>H 3 | -     | 4<br>12 | -    | 2<br>H 1 | 1                |                    |

| 15                 | 14         | 13            | 12          | 11      | 10         | -     | -        |       | -        | -     |         | -    |          | 1                | 0                  |

#### CH[15:0] — Encoded Host Sequence

The host sequence field selects the mode of operation for the time function selected on a given channel. The meaning of the host sequence bits depends on the time function specified.

| HOKKU | — H08 | st Serv | ice Re | quest | Registe | eru |   |   |

|-------|-------|---------|--------|-------|---------|-----|---|---|

| 15    | 14    | 13      | 12     | 11    | 10      | 9   | 8 | 7 |

#### CH 15 CH 14 CH 12 CH 11 CH 10 CH 9 CH 8 CH 13 RESET: **\$YFFE1A** HSRR1 — Host Service Request Register 1 CH 7 CH 6 CH 5 CH 4 CH 3 CH 2 CH 1 CH 0 RESET:

#### CH[15:0] — Encoded Type of Host Service

. . .

• •

The host service request field selects the type of host service request for the time function selected on a given channel. The meaning of the host service request bits depends on the time function specified. A host service request field cleared to %00 signals the host that service is completed by the microengine on that channel. The host can request service on a channel by writing the corresponding host service request field to one of three nonzero states. The CPU should monitor the host service request register until the TPU clears the service request to %00 before the CPU changes any parameters or issues a new service request to the channel.

| C      | CPR0 —       | - Char       | nnel Pri       | ority R | egiste | r 0              |       |   |       |          |       |   |      |          | \$YF             | FE1C               |

|--------|--------------|--------------|----------------|---------|--------|------------------|-------|---|-------|----------|-------|---|------|----------|------------------|--------------------|

|        | 15           | 14           | 13             | 12      | 11     | 10               | 9     | 8 | 7     | 6        | 5     | 4 | 3    | 2        | 1                | 0                  |

| CH 15  |              | CH 14        |                | CH13    |        | СН               | CH 12 |   | CH 11 |          | CH 10 |   | CH 9 |          | 18               |                    |

| RESET: |              |              |                |         |        |                  |       |   |       |          |       |   |      |          |                  |                    |

|        | 0            | 0            | 0              | 0       | 0      | 0                | 0     | 0 | 0     | 0        | 0     | 0 | 0    | 0        | 0                | 0                  |

|        |              |              |                |         |        |                  |       |   |       |          |       |   |      |          |                  |                    |

| C      | CPR1 —       | - Char       | nnel Pri       | ority R | egiste | r 1              |       |   |       |          |       |   |      |          | \$YF             | FE1E               |

| C      | <b>PR1</b> — | - Char<br>14 | nnel Pri<br>13 | ority R | egiste | r <b>1</b><br>10 | 9     | 8 | 7     | 6        | 5     | 4 | 3    | 2        | <b>\$YF</b><br>1 | • <b>FE1E</b><br>0 |

|        |              | 14           |                | 12      | -      | 10               |       | 8 |       | 6<br>H 3 | -     | 4 | -    | 2<br>H 1 | 1                |                    |

|        | 15           | 14           | 13             | 12      | 11     | 10               |       |   |       |          | -     |   | -    |          | 1                | 0                  |

|        | 15<br>CH 7   | 14           | 13             | 12      | 11     | 10               |       |   |       |          | -     |   | -    |          | 1                | 0                  |

CH[15:0] — Encoded One of Three Channel Priority Levels

**\$YFFE18**

| CHX[1:0] | Service  | Guaranteed Time Slots |

|----------|----------|-----------------------|

| 00       | Disabled |                       |

| 01       | Low      | 4 out of 7            |

| 10       | Middle   | 2 out of 7            |

| 11       | High     | 1 out of 7            |

#### 5.5.3 Development Support and Test Registers

These registers are used for custom microcode development or for factory test. Describing the use of the registers is beyond the scope of this technical summary. Register names and addresses are given for reference only. Please refer to the *TPU Reference Manual* (TPURM/AD) for more information.

| DSCR — Development Support Control Register                                              | \$YFFE04 |

|------------------------------------------------------------------------------------------|----------|

| DSSR — Development Support Status Register                                               | \$YFFE06 |

| LR — Link Register                                                                       | \$YFFE22 |

| SGLR — Service Grant Latch Register                                                      | \$YFFE24 |

| DCNR — Decoded Channel Number Register                                                   | \$YFFE26 |

| <b>TCR</b> — Test Configuration Register<br>The TCR is used for factory test of the MCU. | \$YFFE02 |

#### 6.3 Pin Function

The following table is a summary of the functions of the QSM pins when they are not configured for general-purpose I/O. The QSM data direction register (DDRQS) designates each pin except RXD as an input or output.

|           | Pin      | Mode     | Pin Function                                                      |

|-----------|----------|----------|-------------------------------------------------------------------|

|           | MISO     | Master   | Serial Data Input to QSPI                                         |

| QSPI Pins |          | Slave    | Serial Data Output from QSPI                                      |

|           | MOSI     | Master   | Serial Data Output from QSPI                                      |

|           |          | Slave    | Serial Data Input to QSPI                                         |

|           | SCK      | Master   | Clock Output from QSPI                                            |

|           |          | Slave    | Clock Input to QSPI                                               |

|           | PCS0/SS  | Master   | Input: Assertion Causes Mode Fault<br>Output: Selects Peripherals |

|           |          | Slave    | Input: Selects the QSPI                                           |

|           | PCS[3:1] | Master   | Output: Selects Peripherals                                       |

|           |          | Slave    | None                                                              |

| SCI Pins  | TXD      | Transmit | Serial Data Output from SCI                                       |

|           | RXD      | Receive  | Serial Data Input to SCI                                          |

#### 6.4 QSM Registers

QSM registers are divided into four categories: QSM global registers, QSM pin control registers, QSPI submodule registers, and SCI submodule registers. The QSPI and SCI registers are defined in separate sections below. Writes to unimplemented register bits have no meaning or effect, and reads from unimplemented bits always return a logic zero value.

The module mapping bit of the SIM configuration register (SIMCR) defines the most significant bit (ADDR23) of the address, shown in each register figure as Y (Y = 7 or F). This bit, concatenated with the rest of the address given, forms the absolute address of each register. Refer to the SIM section of this technical summary for more information about how the state of MM affects the system.

#### 6.4.1 Global Registers

The QSM global registers contain system parameters used by both the QSPI and the SCI submodules. These registers contain the bits and fields used to configure the QSM.

| ( | QSMCR — QSM Configuration Register |      |      |    |    |    |   |   |      |   |   |   | \$YF | FC00 |    |   |

|---|------------------------------------|------|------|----|----|----|---|---|------|---|---|---|------|------|----|---|

|   | 15                                 | 14   | 13   | 12 | 11 | 10 | 9 | 8 | 7    | 6 | 5 | 4 | 3    |      |    | 0 |

|   | STOP                               | FRZ1 | FRZ0 | 0  | 0  | 0  | 0 | 0 | SUPV | 0 | 0 | 0 |      | IAF  | RB |   |

|   | RESET:                             |      |      |    |    |    |   |   |      |   |   |   |      |      |    |   |

|   | 0                                  | 0    | 0    | 0  | 0  | 0  | 0 | 0 | 1    | 0 | 0 | 0 | 0    | 0    | 0  | 0 |

The QSMCR contains parameters for the QSM/CPU/intermodule bus (IMB) interface.

#### STOP — Stop Enable

0 = Normal QSM clock operation

1 = QSM clock operation stopped

STOP places the QSM in a low-power state by disabling the system clock in most parts of the module. The QSMCR is the only register guaranteed to be readable while STOP is asserted. The QSPI RAM is not readable. However, writes to RAM or any register are guaranteed to be valid while STOP is asserted. STOP can be negated by the CPU and by reset.

| Pin Names                              | Mnemonics  | Mode                      | Function                                                             |

|----------------------------------------|------------|---------------------------|----------------------------------------------------------------------|

| Master In Slave Out                    | MISO       | Master<br>Slave           | Serial Data Input to QSPI<br>Serial Data Output from QSPI            |

| Master Out Slave In                    | MOSI       | Master<br>Slave           | Serial Data Output from QSPI<br>Serial Data Input to QSPI            |

| Serial Clock                           | SCK        | Master<br>Slave           | Clock Output from QSPI<br>Clock Input to QSPI                        |

| Peripheral Chip Selects                | PCS[3:1]   | Master                    | Select Peripherals                                                   |

| Peripheral Chip Select<br>Slave Select | PCS0<br>SS | Master<br>Master<br>Slave | Selects Peripheral<br>Causes Mode Fault<br>Initiates Serial Transfer |

#### 6.5.2 QSPI Registers

The programmer's model for the QSPI submodule consists of the QSM global and pin control registers, four QSPI control registers, one status register, and the 80-byte QSPI RAM.

The CPU can read and write to registers and RAM. The four control registers must be initialized before the QSPI is enabled to ensure defined operation. SPCR1 should be written last because it contains QSPI enable bit SPE. Asserting this bit starts the QSPI. The QSPI control registers are reset to a defined state and can then be changed by the CPU. Reset values are shown below each register.

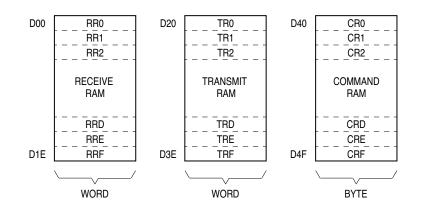

Refer to the following memory map of the QSPI.

| Address  | Name  | Usage                          |

|----------|-------|--------------------------------|

| \$YFFC18 | SPCR0 | QSPI Control Register 0        |

| \$YFFC1A | SPCR1 | QSPI Control Register 1        |

| \$YFFC1C | SPCR2 | QSPI Control Register 2        |

| \$YFFC1E | SPCR3 | QSPI Control Register 3        |

| \$YFFC1F | SPSR  | QSPI Status Register           |

| \$YFFD00 | RAM   | QSPI Receive Data (16 Words)   |

| \$YFFD20 | RAM   | QSPI Transmit Data (16 Words)  |

| \$YFFD40 | RAM   | QSPI Command Control (8 Words) |

Writing a different value into any control register except SPCR2 while the QSPI is enabled disrupts operation. SPCR2 is buffered to prevent disruption of the current serial transfer. After completion of the current serial transfer, the new SPCR2 values become effective.

Writing the same value into any control register except SPCR2 while the QSPI is enabled has no effect on QSPI operation. Rewriting NEWQP in SPCR2 causes execution to restart at the designated location.

| SPCR0  | — QSF | PI Con | trol Re | egister | 0  |      |      |   |   |   |    |    |   | \$YF | FC18 |  |

|--------|-------|--------|---------|---------|----|------|------|---|---|---|----|----|---|------|------|--|

| 15     | 14    | 13     |         |         | 10 | 9    | 8    | 7 |   |   |    |    |   |      | 0    |  |

| MSTR   | WOMQ  |        | Bľ      | TS      |    | CPOL | CPHA |   |   |   | SP | BR |   |      |      |  |

| RESET: |       |        |         |         |    |      |      |   |   |   |    |    |   |      |      |  |

| 0      | 0     | 0      | 0       | 0       | 0  | 0    | 1    | 0 | 0 | 0 | 0  | 0  | 1 | 0    | 0    |  |

SPCR0 contains parameters for configuring the QSPI before it is enabled. The CPU can read and write this register. The QSM has read-only access.

QSPI RAM MAP

#### Figure 15 QSPI RAM

Once the CPU has set up the queue of QSPI commands and enabled the QSPI, the QSPI can operate independently of the CPU. The QSPI executes all of the commands in its queue, sets a flag indicating that it is finished, and then either interrupts the CPU or waits for CPU intervention. It is possible to execute a queue of commands repeatedly without CPU intervention.

#### RR[0:F] — Receive Data RAM

Data received by the QSPI is stored in this segment. The CPU reads this segment to retrieve data from the QSPI. Data stored in receive RAM is right-justified. Unused bits in a receive queue entry are set to zero by the QSPI upon completion of the individual queue entry. The CPU can access the data using byte, word, or long-word addressing.

The CPTQP value in SPSR shows which queue entries have been executed. The CPU uses this information to determine which locations in receive RAM contain valid data before reading them.

#### TR[0:F] — Transmit Data RAM

Data that is to be transmitted by the QSPI is stored in this segment. The CPU usually writes one word of data into this segment for each queue command to be executed.

Information to be transmitted must be written to transmit data RAM in a right-justified format. The QSPI cannot modify information in the transmit data RAM. The QSPI copies the information to its data serializer for transmission. Information remains in transmit RAM until overwritten.

#### CR[0:F] — Command RAM 7 6 5 4 3 2 1 0 CONT DT PCS3 PCS2 PCS1 BITSE DSCK PCS0\* CONT BITSE DT DSCK PCS3 PCS2 PCS1 PCS0\*

COMMAND CONTROL

#### PERIPHERAL CHIP SELECT

\*The PCS0 bit represents the dual-function PCS0/SS.

\$YFFD00

\$YFFD20

\$YFFD40