Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | CPU32                                                                 |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 20MHz                                                                 |

| Connectivity               | EBI/EMI, SCI, SPI, UART/USART                                         |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 15                                                                    |

| Program Memory Size        | -                                                                     |

| Program Memory Type        | ROMIess                                                               |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 132-BQFP Bumpered                                                     |

| Supplier Device Package    | 132-PQFP (24.13x24.13)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68332gmeh20 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Package Type | TPU Type       | Temperature    | Frequency<br>(MHz) | Package<br>Order<br>Quantity | Order Number    |

|--------------|----------------|----------------|--------------------|------------------------------|-----------------|

| 144-Pin QFP  | Motion Control | –40 to +85 °C  | 16 MHz             | 2 pc tray                    | SPAKMC332GCFV16 |

|              |                |                |                    | 44 pc tray                   | MC68332GCFVV16  |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332GCFV20 |

|              |                |                |                    | 44 pc tray                   | MC68332GCFV20   |

|              |                | -40 to +105 °C | 16 MHz             | 2 pc tray                    | SPAKMC332GVFV16 |

|              |                |                |                    | 44 pc tray                   | MC68332GVFV16   |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332GVFV20 |

|              |                |                |                    | 44 pc tray                   | MC68332GVFV20   |

|              |                | -40 to +125 °C | 16 MHz             | 2 pc tray                    | SPAKMC332GMFV16 |

|              |                |                |                    | 44 pc tray                   | MC68332GMFV16   |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332GMFV20 |

|              |                |                |                    | 44 pc tray                   | MC68332GMFVV20  |

|              | Standard       | –40 to +85 °C  | 16 MHz             | 2 pc tray                    | SPAKMC332CFV16  |

|              |                |                |                    | 44 pc tray                   | MC68332CFV16    |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332CFVV20 |

|              |                |                |                    | 44 pc tray                   | MC68332CFV20    |

|              |                | _40 to +105 °C | 16 MHz             | 2 pc tray                    | SPAKMC332VFV16  |

|              |                |                |                    | 44 pc tray                   | MC68332VFV16    |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332VFV20  |

|              |                |                |                    | 44 pc tray                   | MC68332VFV20    |

|              |                | –40 to +125 °C | 16 MHz             | 2 pc tray                    | SPAKMC332MFV16  |

|              |                |                |                    | 44 pc tray                   | MC68332MFV16    |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332MFV20  |

|              |                |                |                    | 44 pc tray                   | MC68332MFV20    |

|              | Std w/enhanced | –40 to +85 °C  | 16 MHz             | 2 pc tray                    | SPAKMC332ACFV16 |

|              | PPWA           |                |                    | 44 pc tray                   | MC68332ACFV16   |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332ACFV20 |

|              |                |                |                    | 44 pc tray                   | MC68332ACFV20   |

|              |                | –40 to +105 °C | 16 MHz             | 2 pc tray                    | SPAKMC332AVFV16 |

|              |                |                |                    | 44 pc tray                   | MC68332AVFV16   |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332AVFC20 |

|              |                |                |                    | 44 pc tray                   | MC68332AVFV20   |

|              |                | –40 to +125 °C | 16 MHz             | 2 pc tray                    | SPAKMC332AMFV16 |

|              |                |                |                    | 44 pc tray                   | MC68332AMFV16   |

|              |                |                | 20 MHz             | 2 pc tray                    | SPAKMC332AMFV20 |

| ŀ            |                |                |                    | 44 pc tray                   | MC68332AMFV20   |

# Table 1 Ordering Information (Continued)

| Signal Name               | Mnemonic    | Function                                                                                |

|---------------------------|-------------|-----------------------------------------------------------------------------------------|

| Quotient Out              | QUOT        | Provides the quotient bit of the polynomial divider                                     |

| Reset                     | RESET       | System reset                                                                            |

| Read-Modify-Write Cycle   | RMC         | Indicates an indivisible read-modify-write instruction                                  |

| Read/Write                | R/W         | Indicates the direction of data transfer on the bus                                     |

| SCI Receive Data          | RXD         | Serial input to the SCI                                                                 |

| QSPI Serial Clock         | SCK         | Clock output from QSPI in master mode;<br>clock input to QSPI in slave mode             |

| Size                      | SIZ[1:0]    | Indicates the number of bytes to be transferred during a bus cycle                      |

| Slave Select              | SS          | Causes serial transmission when QSPI is in slave mode; causes mode fault in master mode |

| TCR2 Clock                | T2CLK       | External clock source for TCR2 counter                                                  |

| TPU Channel Pins          | TPUCH[15:0] | Bidirectional pins associated with TPU channels                                         |

| Three-State Control       | TSC         | Places all output drivers in a high-impedance state                                     |

| SCI Transmit Data         | TXD         | Serial output from the SCI                                                              |

| External Filter Capacitor | XFC         | Connection for external phase-locked loop filter capacitor                              |

# Table 6 MCU Signal Function (Continued)

### Table 7 SIM Address Map

| Access | Address  | 15 8                              | 7                                    |  |  |  |  |  |  |

|--------|----------|-----------------------------------|--------------------------------------|--|--|--|--|--|--|

| S      | \$YFFA00 | SIM CONFIGUE                      | ATION (SIMCR)                        |  |  |  |  |  |  |

| S      | \$YFFA02 | FACTORY TEST (SIMTR)              |                                      |  |  |  |  |  |  |

| S      | \$YFFA04 | CLOCK SYNTHESIZER CONTROL (SYNCR) |                                      |  |  |  |  |  |  |

| S      | \$YFFA06 | NOT USED                          | RESET STATUS REGISTER (RSR)          |  |  |  |  |  |  |

| S      | \$YFFA08 | MODULE TES                        | T E (SIMTRE)                         |  |  |  |  |  |  |

| S      | \$YFFA0A | NOT USED                          | NOT USED                             |  |  |  |  |  |  |

| S      | \$YFFA0C | NOT USED                          | NOT USED                             |  |  |  |  |  |  |

| S      | \$YFFA0E | NOT USED                          | NOT USED                             |  |  |  |  |  |  |

| S/U    | \$YFFA10 | NOT USED                          | PORT E DATA (PORTE0)                 |  |  |  |  |  |  |

| S/U    | \$YFFA12 | NOT USED                          | PORT E DATA (PORTE1)                 |  |  |  |  |  |  |

| S/U    | \$YFFA14 | NOT USED                          | PORT E DATA DIRECTION (DDRE          |  |  |  |  |  |  |

| S      | \$YFFA16 | NOT USED                          | PORT E PIN ASSIGNMENT (PEPAF         |  |  |  |  |  |  |

| S/U    | \$YFFA18 | NOT USED                          | PORT F DATA (PORTF0)                 |  |  |  |  |  |  |

| S/U    | \$YFFA1A | NOT USED                          | PORT F DATA (PORTF1)                 |  |  |  |  |  |  |

| S/U    | \$YFFA1C | NOT USED                          | PORT F DATA DIRECTION (DDRF          |  |  |  |  |  |  |

| S      | \$YFFA1E | NOT USED                          | PORT F PIN ASSIGNMENT (PFPAF         |  |  |  |  |  |  |

| S      | \$YFFA20 | NOT USED                          | SYSTEM PROTECTION CONTROL<br>(SYPCR) |  |  |  |  |  |  |

| S      | \$YFFA22 | PERIODIC INTERRU                  | PT CONTROL (PICR)                    |  |  |  |  |  |  |

| S      | \$YFFA24 | PERIODIC INTERR                   | UPT TIMING (PITR)                    |  |  |  |  |  |  |

| S      | \$YFFA26 | NOT USED                          | SOFTWARE SERVICE (SWSR)              |  |  |  |  |  |  |

| S      | \$YFFA28 | NOT USED                          | NOT USED                             |  |  |  |  |  |  |

| S      | \$YFFA2A | NOT USED                          | NOT USED                             |  |  |  |  |  |  |

| S      | \$YFFA2C | NOT USED                          | NOT USED                             |  |  |  |  |  |  |

| S      | \$YFFA2E | NOT USED                          | NOT USED                             |  |  |  |  |  |  |

| S      | \$YFFA30 | TEST MODULE MASTE                 | R SHIFT A (TSTMSRA)                  |  |  |  |  |  |  |

| S      | \$YFFA32 | TEST MODULE MASTE                 | ER SHIFT B (TSTMSRB)                 |  |  |  |  |  |  |

| S      | \$YFFA34 | TEST MODULE SHI                   | FT COUNT (TSTSC)                     |  |  |  |  |  |  |

| S      | \$YFFA36 | TEST MODULE REPETI                | TION COUNTER (TSTRC)                 |  |  |  |  |  |  |

| S      | \$YFFA38 | TEST MODULE C                     | CONTROL (CREG)                       |  |  |  |  |  |  |

| S/U    | \$YFFA3A |                                   | UTED REGISTER (DREG)                 |  |  |  |  |  |  |

|        | \$YFFA3C | NOT USED                          | NOT USED                             |  |  |  |  |  |  |

|        | \$YFFA3E | NOT USED                          | NOT USED                             |  |  |  |  |  |  |

| S/U    | \$YFFA40 | NOT USED                          | PORT C DATA (PORTC)                  |  |  |  |  |  |  |

|        | \$YFFA42 | NOT USED                          | NOT USED                             |  |  |  |  |  |  |

| S      | \$YFFA44 | CHIP-SELECT PIN AS                | SIGNMENT (CSPAR0)                    |  |  |  |  |  |  |

| S      | \$YFFA46 |                                   | SIGNMENT (CSPAR1)                    |  |  |  |  |  |  |

| S      | \$YFFA48 |                                   | E BOOT (CSBARBT)                     |  |  |  |  |  |  |

| S      | \$YFFA4A | CHIP-SELECT OPTION BOOT (CSORBT)  |                                      |  |  |  |  |  |  |

| S      | \$YFFA4C |                                   | ASE 0 (CSBAR0)                       |  |  |  |  |  |  |

| S      | \$YFFA4E |                                   | PTION 0 (CSOR0)                      |  |  |  |  |  |  |

| S      | \$YFFA50 |                                   | ASE 1 (CSBAR1)                       |  |  |  |  |  |  |

| S      | \$YFFA52 |                                   | PTION 1 (CSOR1)                      |  |  |  |  |  |  |

| S      | \$YFFA54 |                                   | ASE 2 (CSBAR2)                       |  |  |  |  |  |  |

| Access | Address  | 15 8                           | 7 0                           |  |  |  |  |  |

|--------|----------|--------------------------------|-------------------------------|--|--|--|--|--|

| S      | \$YFFA56 | CHIP-SELECT OF                 | PTION 2 (CSOR2)               |  |  |  |  |  |

| S      | \$YFFA58 | CHIP-SELECT B                  | ASE 3 (CSBAR3)                |  |  |  |  |  |

| S      | \$YFFA5A | CHIP-SELECT OF                 | PTION 3 (CSOR3)               |  |  |  |  |  |

| S      | \$YFFA5C | CHIP-SELECT B                  | ASE 4 (CSBAR4)                |  |  |  |  |  |

| S      | \$YFFA5E | CHIP-SELECT OF                 | PTION 4 (CSOR4)               |  |  |  |  |  |

| S      | \$YFFA60 | CHIP-SELECT B                  | ASE 5 (CSBAR5)                |  |  |  |  |  |

| S      | \$YFFA62 | CHIP-SELECT OF                 | PTION 5 (CSOR5)               |  |  |  |  |  |

| S      | \$YFFA64 | CHIP-SELECT B                  | ASE 6 (CSBAR6)                |  |  |  |  |  |

| S      | \$YFFA66 | CHIP-SELECT OF                 | PTION 6 (CSOR6)               |  |  |  |  |  |

| S      | \$YFFA68 | CHIP-SELECT B                  | ASE 7 (CSBAR7)                |  |  |  |  |  |

| S      | \$YFFA6A | CHIP-SELECT OF                 | PTION 7 (CSOR7)               |  |  |  |  |  |

| S      | \$YFFA6C | CHIP-SELECT B                  | ASE 8 (CSBAR8)                |  |  |  |  |  |

| S      | \$YFFA6E | CHIP-SELECT OF                 | PTION 8 (CSOR8)               |  |  |  |  |  |

| S      | \$YFFA70 | CHIP-SELECT B                  | ASE 9 (CSBAR9)                |  |  |  |  |  |

| S      | \$YFFA72 | CHIP-SELECT OF                 | PTION 9 (CSOR9)               |  |  |  |  |  |

| S      | \$YFFA74 | CHIP-SELECT BA                 | CHIP-SELECT BASE 10 (CSBAR10) |  |  |  |  |  |

| S      | \$YFFA76 | CHIP-SELECT OPTION 10 (CSOR10) |                               |  |  |  |  |  |

|        | \$YFFA78 | NOT USED NOT USED              |                               |  |  |  |  |  |

|        | \$YFFA7A | NOT USED NOT USED              |                               |  |  |  |  |  |

|        | \$YFFA7C | NOT USED                       | NOT USED                      |  |  |  |  |  |

|        | \$YFFA7E | NOT USED                       | NOT USED                      |  |  |  |  |  |

### Table 7 SIM Address Map (Continued)

Y = M111, where M is the logic state of the module mapping (MM) bit in the SIMCR.

# **3.2 System Configuration and Protection**

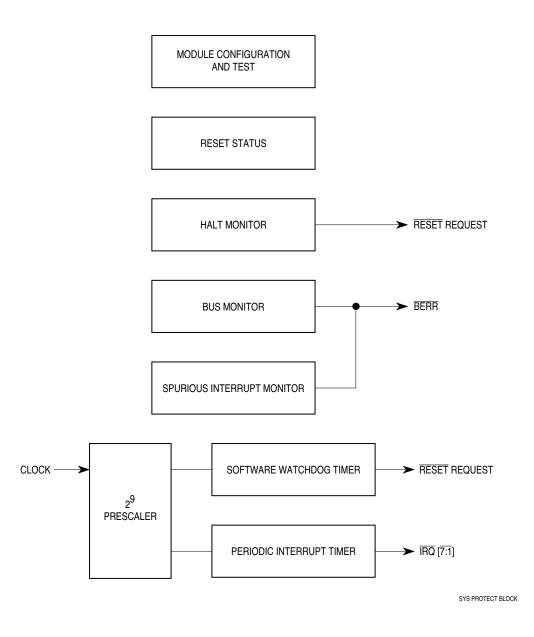

This functional block provides configuration control for the entire MCU. It also performs interrupt arbitration, bus monitoring, and system test functions. MCU system protection includes a bus monitor, a HALT monitor, a spurious interrupt monitor, and a software watchdog timer. These functions have been made integral to the microcontroller to reduce the number of external components in a complete control system.

# Figure 6 System Configuration and Protection Block

# 3.2.1 System Configuration

The SIM controls MCU configuration during normal operation and during internal testing.

|   | SIMCR —SIM Configuration Register |       |       |    |        |    |    |    |      | \$YF | FA00 |   |   |     |    |   |

|---|-----------------------------------|-------|-------|----|--------|----|----|----|------|------|------|---|---|-----|----|---|

|   | 15                                | 14    | 13    | 12 | 11     | 10 | 9  | 8  | 7    | 6    | 5    | 4 | 3 |     |    | 0 |

| ſ | EXOFF                             | FRZSW | FRZBM | 0  | SLVEN  | 0  | SH | EN | SUPV | MM   | 0    | 0 |   | IAI | RB |   |

|   | RESET:                            |       |       |    |        |    |    |    |      |      |      |   |   |     |    |   |

|   | 0                                 | 0     | 0     | 0  | DATA11 | 0  | 0  | 0  | 1    | 1    | 0    | 0 | 1 | 1   | 1  | 1 |

The SIM configuration register controls system configuration. It can be read or written at any time, except for the module mapping (MM) bit, which can be written only once.

### 3.2.2 System Protection Control Register

The system protection control register controls system monitor functions, software watchdog clock prescaling, and bus monitor timing. This register can be written only once following power-on or reset, but can be read at any time.

| SYPCR — System Protection Control Register |   |     |        |    |    |     |     | \$YFF | A21 |

|--------------------------------------------|---|-----|--------|----|----|-----|-----|-------|-----|

| 15                                         | 8 | 7   | 6      | 5  | 4  | 3   | 2   | 1     | 0   |

| NOT USED                                   |   | SWE | SWP    | SW | /T | HME | BME | BI    | ЛТ  |

| RESET:                                     |   |     |        |    |    |     |     |       |     |

|                                            |   | 1   | MODCLK | 0  | 0  | 0   | 0   | 0     | 0   |

SWE — Software Watchdog Enable

0 = Software watchdog disabled

1 = Software watchdog enabled

### SWP — Software Watchdog Prescale

This bit controls the value of the software watchdog prescaler.

- 0 = Software watchdog clock not prescaled

- 1 = Software watchdog clock prescaled by 512

# SWT[1:0] — Software Watchdog Timing

This field selects the divide ratio used to establish software watchdog time-out period. The following table gives the ratio for each combination of SWP and SWT bits.

| SWP | SWT | Ratio           |

|-----|-----|-----------------|

| 0   | 00  | 2 <sup>9</sup>  |

| 0   | 01  | 2 <sup>11</sup> |

| 0   | 10  | 2 <sup>13</sup> |

| 0   | 11  | 2 <sup>15</sup> |

| 1   | 00  | 2 <sup>18</sup> |

| 1   | 01  | 2 <sup>20</sup> |

| 1   | 10  | 2 <sup>22</sup> |

| 1   | 11  | 2 <sup>24</sup> |

### HME — Halt Monitor Enable

0 = Disable halt monitor function

1 = Enable halt monitor function

BME — Bus Monitor External Enable

- 0 = Disable bus monitor function for an internal to external bus cycle.

- 1 = Enable bus monitor function for an internal to external bus cycle.

### BMT[1:0] — Bus Monitor Timing

This field selects a bus monitor time-out period as shown in the following table.

| BMT | Bus Monitor Time-out Period |  |  |  |  |  |  |

|-----|-----------------------------|--|--|--|--|--|--|

| 00  | 64 System Clocks            |  |  |  |  |  |  |

| 01  | 32 System Clocks            |  |  |  |  |  |  |

| 10  | 16 System Clocks            |  |  |  |  |  |  |

| 11  | 8 System Clocks             |  |  |  |  |  |  |

#### 3.4.8 Data Transfer Mechanism

The MCU architecture supports byte, word, and long-word operands, allowing access to 8- and 16-bit data ports through the use of asynchronous cycles controlled by the data transfer and size acknowledge inputs (DSACK1 and DSACK0).

#### 3.4.9 Dynamic Bus Sizing

The MCU dynamically interprets the port size of the addressed device during each bus cycle, allowing operand transfers to or from 8- and 16-bit ports. During an operand transfer cycle, the slave device signals its port size and indicates completion of the bus cycle to the MCU through the use of the DSACK0 and DSACK1 inputs, as shown in the following table.

| DSACK1 | DSACK0 | Result                                         |

|--------|--------|------------------------------------------------|

| 1      | 1      | Insert Wait States in Current Bus Cycle        |

| 1      | 0      | Complete Cycle — Data Bus Port Size is 8 Bits  |

| 0      | 1      | Complete Cycle — Data Bus Port Size is 16 Bits |

| 0      | 0      | Reserved                                       |

#### Table 10 Effect of DSACK Signals

For example, if the MCU is executing an instruction that reads a long-word operand from a 16-bit port, the MCU latches the 16 bits of valid data and then runs another bus cycle to obtain the other 16 bits. The operation for an 8-bit port is similar, but requires four read cycles. The addressed device uses the  $\overline{DSACK0}$  and  $\overline{DSACK1}$  signals to indicate the port width. For instance, a 16-bit device always returns  $\overline{DSACK0} = 1$  and  $\overline{DSACK1} = 0$  for a 16-bit port, regardless of whether the bus cycle is a byte or word operation.

Dynamic bus sizing requires that the portion of the data bus used for a transfer to or from a particular port size be fixed. A 16-bit port must reside on data bus bits [15:0] and an 8-bit port must reside on data bus bits [15:8]. This minimizes the number of bus cycles needed to transfer data and ensures that the MCU transfers valid data.

The MCU always attempts to transfer the maximum amount of data on all bus cycles. For a word operation, it is assumed that the port is 16 bits wide when the bus cycle begins. Operand bytes are designated as shown in the following figure. OP0 is the most significant byte of a long-word operand, and OP3 is the least significant byte. The two bytes of a word-length operand are OP0 (most significant) and OP1. The single byte of a byte-length operand is OP0.

| Operand    | Byte Order |    |     |               |       |   |     |    |

|------------|------------|----|-----|---------------|-------|---|-----|----|

|            | 31         | 24 | 23  | 16            | 15    | 8 | 7   | 0  |

| Long Word  | OP0        |    | OP1 |               | OP2   |   | OP3 |    |

| Three Byte |            |    | O   | <b>&gt;</b> 0 | 0 OP1 |   | 0   | P2 |

| Word       |            |    | (   |               | OP0   |   | OP1 |    |

| Byte       |            |    |     |               |       |   | 0   | P0 |

### Figure 8 Operand Byte Order

### 3.4.10 Operand Alignment

The data multiplexer establishes the necessary connections for different combinations of address and data sizes. The multiplexer takes the two bytes of the 16-bit bus and routes them to their required positions. Positioning of bytes is determined by the size and address outputs. SIZ1 and SIZ0 indicate the remaining number of bytes to be transferred during the current bus cycle. The number of bytes transferred is equal to or less than the size indicated by SIZ1 and SIZ0, depending on port width.

#### 3.5.1 Chip-Select Registers

Pin assignment registers CSPAR0 and CSPAR1 determine functions of chip-select pins. These registers also determine port size (8- or 16-bit) for dynamic bus allocation.

A pin data register (PORTC) latches discrete output data.

Blocks of addresses are assigned to each chip-select function. Block sizes of 2 Kbytes to 1 Mbyte can be selected by writing values to the appropriate base address register (CSBAR). Address blocks for separate chip-select functions can overlap.

Chip-select option registers (CSORBT and CSOR[10:0]) determine timing of and conditions for assertion of chip-select signals. Eight parameters, including operating mode, access size, synchronization, and wait state insertion can be specified.

Initialization code often resides in a peripheral memory device controlled by the chip-select circuits. A set of special chip-select functions and registers (CSORBT, CSBARBT) is provided to support bootstrap operation.

### 3.5.2 Pin Assignment Registers

The pin assignment registers (CSPAR0 and CSPAR1) contain pairs of bits that determine the function of chip-select pins. The pin assignment encodings used in these registers are shown below.

| Bit Field | Description               |

|-----------|---------------------------|

| 00        | Discrete Output           |

| 01        | Alternate Function        |

| 10        | Chip Select (8-Bit Port)  |

| 11        | Chip Select (16-Bit Port) |

#### **Table 12 Pin Assignment Encodings**

### **CSPAR0**—Chip Select Pin Assignment Register 0

#### \$YFFA44

| 15     | 14 | 13  | 12    | 11  | 10    | 9   | 8     | 7   | 6     | 5   | 4     | 3   | 2     | 1   | 0   |

|--------|----|-----|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|-----|

| 0      | 0  | CSP | A0[6] | CSP | A0[5] | CSP | A0[4] | CSP | A0[3] | CSP | A0[2] | CSP | A0[1] | CSB | ООТ |

| RESET: |    |     |       |     |       |     |       |     |       |     |       |     |       |     |     |

0 0 DATA2 1 DATA2 1 DATA2 1 DATA1 1 DATA1 1 DATA1 1 1 DATA0

CSPAR0 contains seven 2-bit fields that determine the functions of corresponding chip-select pins. CSPAR0[15:14] are not used. These bits always read zero; writes have no effect. CSPAR0 bit 1 always reads one; writes to CSPAR0 bit 1 have no effect.

#### Table 13 CSPAR0 Pin Assignments

| CSPAR0 Field | Chip Select Signal | Alternate Signal | Discrete Output |

|--------------|--------------------|------------------|-----------------|

| CSPA0[6]     | CS5                | FC2              | PC2             |

| CSPA0[5]     | CS4                | FC1              | PC1             |

| CSPA0[4]     | CS3                | FC0              | PC0             |

| CSPA0[3]     | CS2                | BGACK            | _               |

| CSPA0[2]     | CS1                | BG               | —               |

| CSPA0[1]     | CSO                | BR               | _               |

| CSBOOT       | CSBOOT             | _                | _               |

| <b>PFPAR</b> — Port F Pin Assignment Register |   |       |       |       |       |       |       | \$YF  | FA1F  |

|-----------------------------------------------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 15                                            | 8 | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| NOT USED                                      |   | PFPA7 | PFPA6 | PFPA5 | PFPA4 | PFPA3 | PFPA2 | PFPA1 | PFPA0 |

| DEOET                                         |   |       | •     |       |       |       |       |       |       |

RESET:

DATA9 DATA9 DATA9 DATA9 DATA9 DATA9 DATA9 DATA9

The bits in this register control the function of each port F pin. Any bit cleared to zero defines the corresponding pin to be an I/O pin. Any bit set to one defines the corresponding pin to be an interrupt request signal or MODCLK. The MODCLK signal has no function after reset.

### Table 17 Port F Pin Assignments

| PFPAR Field | Port F Signal | Alternate Signal |

|-------------|---------------|------------------|

| PFPA7       | PF7           | IRQ7             |

| PFPA6       | PF6           | IRQ6             |

| PFPA5       | PF5           | IRQ5             |

| PFPA4       | PF4           | IRQ4             |

| PFPA3       | PF3           | IRQ3             |

| PFPA2       | PF2           | IRQ2             |

| PFPA1       | PF1           | IRQ1             |

| PFPA0       | PF0           | MODCLK           |

Data bus pin 9 controls the state of this register following reset. If DATA9 is set to one during reset, the register is set to \$FF, which defines all port F pins as interrupt request inputs. If DATA9 is cleared to zero during reset, this register is set to \$00, defining all port F pins as I/O pins.

### 3.7 Resets

Reset procedures handle system initialization and recovery from catastrophic failure. The MCU performs resets with a combination of hardware and software. The system integration module determines whether a reset is valid, asserts control signals, performs basic system configuration based on hardware mode-select inputs, then passes control to the CPU.

Reset occurs when an active low logic level on the RESET pin is clocked into the SIM. Resets are gated by the CLKOUT signal. Asynchronous resets are assumed to be catastrophic. An asynchronous reset can occur on any clock edge. Synchronous resets are timed to occur at the end of bus cycles. If there is no clock when RESET is asserted, reset does not occur until the clock starts. Resets are clocked in order to allow completion of write cycles in progress at the time RESET is asserted.

Reset is the highest-priority CPU32 exception. Any processing in progress is aborted by the reset exception, and cannot be restarted. Only essential tasks are performed during reset exception processing. Other initialization tasks must be accomplished by the exception handler routine.

# 3.7.1 SIM Reset Mode Selection

The logic states of certain data bus pins during reset determine SIM operating configuration. In addition, the state of the MODCLK pin determines system clock source and the state of the BKPT pin determines what happens during subsequent breakpoint assertions. The following table is a summary of reset mode selection options.

### Table 18 Reset Mode Selection

| Mode Select Pin | Default Function   | Alternate Function |

|-----------------|--------------------|--------------------|

|                 | (Pin Left High)    | (Pin Pulled Low)   |

|                 | (· ··· =•·····g··) | (                  |

mask lower-priority interrupts during exception processing, and it is decoded by modules that have requested interrupt service to determine whether the current interrupt acknowledge cycle pertains to them.

Modules that have requested interrupt service decode the IP value placed on the address bus at the beginning of the interrupt acknowledge cycle, and if their requests are at the specified IP level, respond to the cycle. Arbitration between simultaneous requests of the same priority is performed by means of serial contention between module interrupt arbitration (IARB) field bit values.

Each module that can make an interrupt service request, including the SIM, has an IARB field in its configuration register. An IARB field can be assigned a value from %0001 (lowest priority) to %1111 (highest priority). A value of %0000 in an IARB field causes the CPU to process a spurious interrupt exception when an interrupt from that module is recognized.

Because the EBI manages external interrupt requests, the SIM IARB value is used for arbitration between internal and external interrupt requests. The reset value of IARB for the SIM is %1111, and the reset IARB value for all other modules is %0000. Initialization software must assign different IARB values in order to implement an arbitration scheme.

Each module must have a unique IARB value. When two or more IARB fields have the same nonzero value, the CPU interprets multiple vector numbers simultaneously, with unpredictable consequences.

Arbitration must always take place, even when a single source requests service. This point is important for two reasons: the CPU interrupt acknowledge cycle is not driven on the external bus unless the SIM wins contention, and failure to contend causes an interrupt acknowledge bus cycle to be terminated by a bus error, which causes a spurious interrupt exception to be taken.

When arbitration is complete, the dominant module must place an interrupt vector number on the data bus and terminate the bus cycle. In the case of an external interrupt request, because the interrupt acknowledge cycle is transferred to the external bus, an external device must decode the mask value and respond with a vector number, then generate bus cycle termination signals. If the device does not respond in time, a spurious interrupt exception is taken.

The periodic interrupt timer (PIT) in the SIM can generate internal interrupt requests of specific priority at predetermined intervals. By hardware convention, PIT interrupts are serviced before external interrupt service requests of the same priority. Refer to 3.2.7 Periodic Interrupt Timer for more information.

# 3.8.2 Interrupt Processing Summary

A summary of the interrupt processing sequence follows. When the sequence begins, a valid interrupt service request has been detected and is pending.

- A. The CPU finishes higher priority exception processing or reaches an instruction boundary.

- B. Processor state is stacked. The contents of the status register and program counter are saved.

- C. The interrupt acknowledge cycle begins:

- 1. FC[2:0] are driven to %111 (CPU space) encoding.

- 2. The address bus is driven as follows. ADDR[23:20] = %1111; ADDR[19:16] = %1111, which indicates that the cycle is an interrupt acknowledge CPU space cycle; ADDR[15:4] = %111111111111; ADDR[3:1] = the level of the interrupt request being acknowledged; and ADDR0 = %1.

- 3. Request priority level is latched into the IP field in the status register from the address bus.

- D. Modules or external peripherals that have requested interrupt service decode the request level in ADDR[3:1]. If the request level of at least one interrupting module or device is the same as the value in ADDR[3:1], interrupt arbitration contention takes place. When there is no contention, the spurious interrupt monitor asserts BERR, and a spurious interrupt exception is processed.

- E. After arbitration, the interrupt acknowledge cycle can be completed in one of three ways:

**Freescale Semiconductor, Inc.**

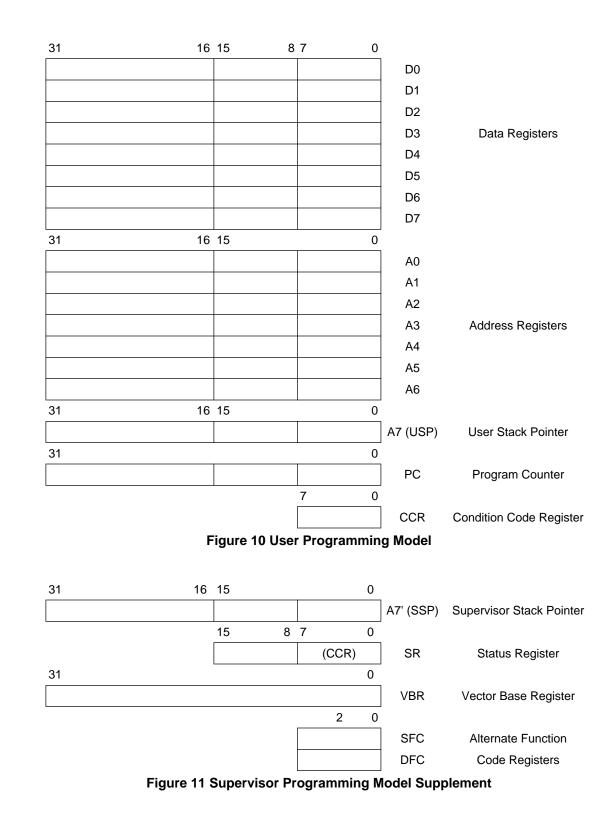

### 4.3 Status Register

The status register contains the condition codes that reflect the results of a previous operation and can be used for conditional instruction execution in a program. The lower byte containing the condition codes is the only portion of the register available at the user privilege level; it is referenced as the condition code register (CCR) in user programs. At the supervisor privilege level, software can access the full status register, including the interrupt priority mask and additional control bits.

#### SR — Status Register

| 15     | 14 | 13 | 12 | 11 | 10 |    | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|

| T1     | Т0 | S  | 0  | 0  |    | IP |   | 0 | 0 | 0 | Х | N | Z | V | C |

| RESET: |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |

| 0      | 0  | 1  | 0  | 0  | 1  | 1  | 1 | 0 | 0 | 0 | U | U | U | U | U |

### System Byte

T[1:0] —Trace Enable S —Supervisor/User State Bits [12:11] —Unimplemented IP[2:0] —Interrupt Priority Mask

User Byte (Condition Code Register)

Bits [7:5] — Unimplemented

- X Extend

- N Negative

- Z Zero

- V Overflow

- C Carry

# 4.4 Data Types

Six basic data types are supported:

- Bits

- Packed Binary Coded Decimal Digits

- Byte Integers (8 bits)

- Word Integers (16 bits)

- Long-Word Integers (32 bits)

- Quad-Word Integers (64 bits)

# 4.5 Addressing Modes

Addressing in the CPU32 is register-oriented. Most instructions allow the results of the specified operation to be placed either in a register or directly in memory. This flexibility eliminates the need for extra instructions to store register contents in memory. The CPU32 supports seven basic addressing modes:

- Register direct

- Register indirect

- Register indirect with index

- · Program counter indirect with displacement

- Program counter indirect with index

- Absolute

- Immediate

Included in the register indirect addressing modes are the capabilities to post-increment, predecrement, and offset. The program counter relative mode also has index and offset capabilities. In addition to these addressing modes, many instructions implicitly specify the use of the status register, stack pointer, or program counter.

# 4.6 Instruction Set Summary

|                          |                                              | ble 20 Instruction           |                                                                                                                                                                                    |  |  |

|--------------------------|----------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Instruction              | Syntax                                       | Operand Size                 | Operation                                                                                                                                                                          |  |  |

| ABCD                     | Dn, Dn<br>– (An), – (An)                     | 8<br>8                       | Source <sub>10</sub> + Destination <sub>10</sub> + X $\Rightarrow$ Destination                                                                                                     |  |  |

| ADD                      | Dn, <ea><br/><ea>, Dn</ea></ea>              | 8, 16, 32<br>8, 16, 32       | Source + Destination $\Rightarrow$ Destination                                                                                                                                     |  |  |

| ADDA                     | <ea>, An</ea>                                | 16, 32                       | Source + Destination $\Rightarrow$ Destination                                                                                                                                     |  |  |

| ADDI                     | # <data>, <ea></ea></data>                   | 8, 16, 32                    | Immediate data + Destination $\Rightarrow$ Destination                                                                                                                             |  |  |

| ADDQ                     | # <data>, <ea></ea></data>                   | 8, 16, 32                    | Immediate data + Destination $\Rightarrow$ Destination                                                                                                                             |  |  |

| ADDX                     | Dn, Dn<br>– (An), – (An)                     | 8, 16, 32<br>8, 16, 32       | Source + Destination + $X \Rightarrow$ Destination                                                                                                                                 |  |  |

| AND                      | <ea>, Dn<br/>Dn, <ea></ea></ea>              | 8, 16, 32<br>8, 16, 32       | Source • Destination $\Rightarrow$ Destination                                                                                                                                     |  |  |

| ANDI                     | # <data>, <ea></ea></data>                   | 8, 16, 32                    | Data • Destination $\Rightarrow$ Destination                                                                                                                                       |  |  |

| ANDI to CCR              | # <data>, CCR</data>                         | 8                            | Source • CCR $\Rightarrow$ CCR                                                                                                                                                     |  |  |

| ANDI to SR1 <sup>1</sup> | # <data>, SR</data>                          | 16                           | Source • SR $\Rightarrow$ SR                                                                                                                                                       |  |  |

| ASL                      | Dn, Dn<br># <data>, Dn<br/>Í</data>          | 8, 16, 32<br>8, 16, 32<br>16 | X/C - 0                                                                                                                                                                            |  |  |

| ASR                      | Dn, Dn<br># <data>, Dn<br/>Í</data>          | 8, 16, 32<br>8, 16, 32<br>16 |                                                                                                                                                                                    |  |  |

| Bcc                      | label                                        | 8, 16, 32                    | If condition true, then $PC + d \Rightarrow PC$                                                                                                                                    |  |  |

| BCHG                     | Dn, <ea><br/># <data>, <ea></ea></data></ea> | 8, 32<br>8, 32               | bit number of destination) $\Rightarrow$ Z $\Rightarrow$ bit of destination                                                                                                        |  |  |

| BCLR                     | Dn, <ea><br/># <data>, <ea></ea></data></ea> | 8, 32<br>8, 32               | $\overline{(\langle \text{bit number} \rangle \text{ of destination})}$<br>0 $\Rightarrow \overline{\text{bit of destination}}$                                                    |  |  |

| BGND                     | none                                         | none                         | If background mode enabled, then enter background mode, else format/vector $\Rightarrow$ – (SSP);<br>PC $\Rightarrow$ – (SSP); SR $\Rightarrow$ – (SSP); (vector) $\Rightarrow$ PC |  |  |

| BKPT                     | # <data></data>                              | none                         | If breakpoint cycle acknowledged, then execute returned operation word, else trap as illegal instruction                                                                           |  |  |

| BRA                      | label                                        | 8, 16, 32                    | $PC + d \Rightarrow PC$                                                                                                                                                            |  |  |

| BSET                     | Dn, <ea><br/># <data>, <ea></ea></data></ea> | 8, 32<br>8, 32               | $\overline{(\langle \text{bit number} \rangle \text{ of destination})} \Rightarrow Z;$<br>1 $\Rightarrow$ bit of destination                                                       |  |  |

| BSR                      | label                                        | 8, 16, 32                    | $SP - 4 \Rightarrow SP; PC \Rightarrow (SP); PC + d \Rightarrow PC$                                                                                                                |  |  |

| BTST                     | Dn, <ea><br/># <data>, <ea></ea></data></ea> | 8, 32<br>8, 32               | $\overline{(\langle \text{bit number} \rangle \text{of destination})} \Rightarrow Z$                                                                                               |  |  |

| СНК                      | <ea>, Dn</ea>                                | 16, 32                       | If Dn < 0 or Dn > (ea), then CHK exception                                                                                                                                         |  |  |

| CHK2                     | <ea>, Rn</ea>                                | 8, 16, 32                    | If Rn < lower bound or Rn > upper bound, then<br>CHK exception                                                                                                                     |  |  |

| CLR                      | Í                                            | 8, 16, 32                    | $0 \Rightarrow \text{Destination}$                                                                                                                                                 |  |  |

| CMP                      | <ea>, Dn</ea>                                | 8, 16, 32                    | (Destination – Source), CCR shows results                                                                                                                                          |  |  |

| CMPA                     | <ea>, An</ea>                                | 16, 32                       | (Destination – Source), CCR shows results                                                                                                                                          |  |  |

| CMPI                     | # <data>, <ea></ea></data>                   | 8, 16, 32                    | (Destination – Data), CCR shows results                                                                                                                                            |  |  |

| CMPM                     | (An) +, (An) +                               | 8, 16, 32                    | (Destination – Source), CCR shows results                                                                                                                                          |  |  |

| CMP2                     | <ea>, Rn</ea>                                | 8, 16, 32                    | Lower bound $\leq$ Rn $\leq$ Upper bound, CCR shows result                                                                                                                         |  |  |

### **Table 20 Instruction Set Summary**

| Instruction            | Syntax                                                 | Operand Size                                                               | Operation                                                                                                                           |  |

|------------------------|--------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| MOVES <sup>1</sup>     | Rn, <ea><br/><ea>, Rn</ea></ea>                        | 8, 16, 32                                                                  | $Rn \Rightarrow Destination using DFC$<br>Source using SFC $\Rightarrow Rn$                                                         |  |

| MULS/MULU              | <ea>, Dn<br/><ea>, Dl<br/><ea>, Dh : Dl</ea></ea></ea> | $16 * 16 \Rightarrow 32$ $32 * 32 \Rightarrow 32$ $32 * 32 \Rightarrow 64$ | Source $*$ Destination $\Rightarrow$ Destination (signed or unsigned)                                                               |  |

| NBCD                   | Í                                                      | 8 8                                                                        | $0 - \text{Destination}_{10} - X \Rightarrow \text{Destination}$                                                                    |  |

| NEG                    | Í                                                      | 8, 16, 32                                                                  | $0 - Destination \Rightarrow Destination$                                                                                           |  |

| NEGX                   | Í                                                      | 8, 16, 32                                                                  | $0 - Destination - X \Rightarrow Destination$                                                                                       |  |

| NOP                    | none                                                   | none                                                                       | $PC + 2 \Rightarrow PC$                                                                                                             |  |

| NOT                    | Í                                                      | 8, 16, 32                                                                  | $\overline{\text{Destination}} \Rightarrow \text{Destination}$                                                                      |  |

| OR                     | <ea>, Dn<br/>Dn, <ea></ea></ea>                        | 8, 16, 32<br>8, 16, 32                                                     | Source + Destination $\Rightarrow$ Destination                                                                                      |  |

| ORI                    | # <data>, <ea></ea></data>                             | 8, 16, 32                                                                  | Data + Destination $\Rightarrow$ Destination                                                                                        |  |

| ORI to CCR             | # <data>, CCR</data>                                   | 16                                                                         | Source + CCR $\Rightarrow$ SR                                                                                                       |  |

| ORI to SR <sup>1</sup> | # <data>, SR</data>                                    | 16                                                                         | Source ; SR $\Rightarrow$ SR                                                                                                        |  |

| PEA                    | Í                                                      | 32                                                                         | $SP - 4 \Rightarrow SP; \langle ea \rangle \Rightarrow SP$                                                                          |  |

| RESET <sup>1</sup>     | none                                                   | none                                                                       | Assert RESET line                                                                                                                   |  |

| ROL                    | Dn, Dn<br># <data>, Dn<br/>Í</data>                    | 8, 16, 32<br>8, 16, 32<br>16                                               |                                                                                                                                     |  |

| ROR                    | Dn, Dn<br># <data>, Dn<br/>Í</data>                    | 8, 16, 32<br>8, 16, 32<br>16                                               |                                                                                                                                     |  |

| ROXL                   | Dn, Dn<br>#⊲data>, Dn<br>Í                             | 8, 16, 32<br>8, 16, 32<br>16                                               |                                                                                                                                     |  |

| ROXR                   | Dn, Dn<br># <data>, Dn<br/>Í</data>                    | 8, 16, 32<br>8, 16, 32<br>16                                               |                                                                                                                                     |  |

| RTD                    | #d                                                     | 16                                                                         | $(SP) \Rightarrow PC; SP + 4 + d \Rightarrow SP$                                                                                    |  |

| RTE <sup>1</sup>       | none                                                   | none                                                                       | $(SP) \Rightarrow SR; SP + 2 \Rightarrow SP; (SP) \Rightarrow PC;$<br>SP + 4 $\Rightarrow$ SP;<br>Restore stack according to format |  |

| RTR                    | none                                                   | none                                                                       | $(SP) \Rightarrow CCR; SP + 2 \Rightarrow SP; (SP) \Rightarrow PC;$<br>SP + 4 $\Rightarrow$ SP                                      |  |

| RTS                    | none                                                   | none                                                                       | $(SP) \Rightarrow PC;  SP + 4 \Rightarrow SP$                                                                                       |  |

| SBCD                   | Dn, Dn<br>– (An), – (An)                               | 8<br>8                                                                     | Destination10 – Source10 – $X \Rightarrow$ Destination                                                                              |  |

| Scc                    | Í                                                      | 8                                                                          | If condition true, then destination bits are set to 1; else, destination bits are cleared to 0                                      |  |

| STOP <sup>1</sup>      | # <data></data>                                        | 16                                                                         | Data $\Rightarrow$ SR; STOP                                                                                                         |  |

| SUB                    | <ea>, Dn<br/>Dn, <ea></ea></ea>                        | 8, 16, 32                                                                  | Destination – Source $\Rightarrow$ Destination                                                                                      |  |

| SUBA                   | <ea>, An</ea>                                          | 16, 32                                                                     | Destination – Source $\Rightarrow$ Destination                                                                                      |  |

| SUBI                   | # <data>, <ea></ea></data>                             | 8, 16, 32                                                                  | Destination – Data $\Rightarrow$ Destination                                                                                        |  |

| SUBQ                   | # <data>, <ea></ea></data>                             | 8, 16, 32                                                                  | Destination – Data $\Rightarrow$ Destination                                                                                        |  |

| SUBX                   | Dn, Dn<br>– (An), – (An)                               | 8, 16, 32<br>8, 16, 32                                                     | Destination – Source – $X \Rightarrow$ Destination                                                                                  |  |

### Table 20 Instruction Set Summary(Continued)

### 5.1.7 Period Measurement with Missing Transition Detect (PMM)

Period measurement with missing transition detect allows a special-purpose 23-bit period measurement. It detects the occurrence of a missing transition (caused by a missing tooth on the sensed wheel), indicated by a period measurement that is greater than a programmable ratio of the previous period measurement. Once detected, this condition can be counted and compared to a programmable number of additional transitions detected before TCR2 is reset to \$FFFF. In addition, one byte at an address specified by a channel parameter can be read and used as a flag. A nonzero value of the flag indicates that TCR2 is to be reset to \$FFFF once the next missing transition is detected.

### 5.1.8 Position-Synchronized Pulse Generator (PSP)

Any channel of the TPU can generate an output transition or pulse, which is a projection in time based on a reference period previously calculated on another channel. Both TCRs are used in this algorithm: TCR1 is internally clocked, and TCR2 is clocked by a position indicator in the user's device. An example of a TCR2 clock source is a sensor that detects special teeth on the flywheel of an automobile using PMA or PMM. The teeth are placed at known degrees of engine rotation; hence, TCR2 is a coarse representation of engine degrees, i.e., each count represents some number of degrees.

Up to 15 position-synchronized pulse generator function channels can operate with a single input reference channel executing a PMA or PMM input function. The input channel measures and stores the time period between the flywheel teeth and resets TCR2 when the engine reaches a reference position. The output channel uses the period calculated by the input channel to project output transitions at specific engine degrees. Because the flywheel teeth might be 30 or more degrees apart, a fractional multiplication operation resolves down to the desired degrees. Two modes of operation allow pulse length to be determined either by angular position or by time.

### 5.1.9 Stepper Motor (SM)

The stepper motor control algorithm provides for linear acceleration and deceleration control of a stepper motor with a programmable number of step rates of up to 14. Any group of channels, up to eight, can be programmed to generate the control logic necessary to drive a stepper motor.

The time period between steps (P) is defined as:

$$P(r) = K1 - K2 * r$$

where r is the current step rate (1-14), and K1 and K2 are supplied as parameters.

After providing the desired step position in a 16-bit parameter, the CPU issues a step request. Next, the TPU steps the motor to the desired position through an acceleration/deceleration profile defined by parameters. The parameter indicating the desired position can be changed by the CPU while the TPU is stepping the motor. This algorithm changes the control state every time a new step command is received.

A 16-bit parameter initialized by the CPU for each channel defines the output state of the associated pin. The bit pattern written by the CPU defines the method of stepping, such as full stepping or half stepping. With each transition, the 16-bit parameter rotates one bit. The period of each transition is defined by the programmed step rate.

# 5.1.10 Period/Pulse-Width Accumulator (PPWA)

The period/pulse-width accumulator algorithm accumulates a 16-bit or 24-bit sum of either the period or the pulse width of an input signal over a programmable number of periods or pulses (from 1 to 255). After an accumulation period, the algorithm can generate a link to a sequential block of up to eight channels. The user specifies a starting channel of the block and number of channels within the block. Generation of links depends on the mode of operation. Any channel can be used to measure an accumulated number of periods of an input signal. A maximum of 24 bits can be used for the accumu-

lation parameter. From 1 to 255 period measurements can be made and summed with the previous measurement(s) before the TPU interrupts the CPU, allowing instantaneous or average frequency measurement, and the latest complete accumulation (over the programmed number of periods).

The pulse width (high-time portion) of an input signal can be measured (up to 24 bits) and added to a previous measurement over a programmable number of periods (1 to 255). This provides an instantaneous or average pulse-width measurement capability, allowing the latest complete accumulation (over the specified number of periods) to always be available in a parameter. By using the output compare function in conjunction with PPWA, an output signal can be generated that is proportional to a specified input signal. The ratio of the input and output frequency is programmable. One or more output signals with different frequencies, yet proportional and synchronized to a single input signal, can be generated on separate channels.

### 5.1.11 Quadrature Decode (QDEC)

The quadrature decode function uses two channels to decode a pair of out-of-phase signals in order to present the CPU with directional information and a position value. It is particularly suitable for use with slotted encoders employed in motor control. The function derives full resolution from the encoder signals and provides a 16-bit position counter with rollover/under indication via an interrupt.

The counter in parameter RAM is updated when a valid transition is detected on either one of the two inputs. The counter is incremented or decremented depending on the lead/lag relationship of the two signals at the time of servicing the transition. The user can read or write the counter at any time. The counter is free running, overflowing to \$0000 or underflowing to \$FFFF depending on direction. The QDEC function also provides a time stamp referenced to TCR1 for every valid signal edge and the ability for the host CPU to obtain the latest TCR1 value. This feature allows position interpolation by the host CPU between counts at very slow count rates.

### 5.2 MC68332G Time Functions

The following paragraphs describe factory-programmed time functions implemented in the motion-control microcode ROM. A complete description of the functions is beyond the scope of this summary. Refer to *Using the TPU Function Library and TPU Emulation Mode* (TPUPN00/D) for more information about specific functions.

# 5.2.1 Table Stepper Motor (TSM)

The TSM function provides for acceleration and deceleration control of a stepper motor with a programmable number of step rates up to 58. TSM uses a table in PRAM, rather than an algorithm, to define the stepper motor acceleration profile, allowing the user to fully define the profile. In addition, a slew rate parameter allows fine control of the terminal running speed of the motor independent of the acceleration table. The CPU need only write a desired position, and the TPU accelerates, slews, and decelerates the motor to the required position. Full and half step support is provided for two-phase motors. In addition, a slew rate parameter allows fine control of the terminal running speed of the motor independent of the acceleration table.

# 5.2.2 New Input Capture/Transition Counter (NITC)

Any channel of the TPU can capture the value of a specified TCR or any specified location in parameter RAM upon the occurrence of each transition or specified number of transitions, and then generate an interrupt request to notify the bus master. The times of the most recent two transitions are maintained in parameter RAM. A channel can perform input captures continually, or a channel can detect a single transition or specified number of transitions, the channel activity until reinitialization. After each transition or specified number of transitions, the channel can generate a link to other channels.

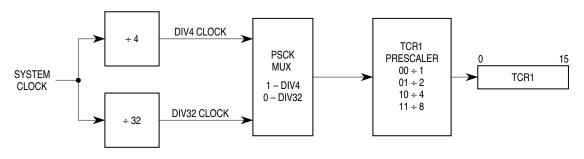

### TCR1P — Timer Count Register 1 Prescaler Control

TCR1 is clocked from the output of a prescaler. The prescaler's input is the internal TPU system clock divided by either 4 or 32, depending on the value of the PSCK bit. The prescaler divides this input by 1, 2, 4, or 8. Channels using TCR1 have the capability to resolve down to the TPU system clock divided by 4.

PRESCALER CTL BLOCK 1

|                |              | PSC                 | K = 0             | PSCK = 1            |                   |  |

|----------------|--------------|---------------------|-------------------|---------------------|-------------------|--|

| TCR1 Prescaler | Divide<br>By | Number of<br>Clocks | Rate at<br>16 MHz | Number of<br>Clocks | Rate at<br>16 MHz |  |

| 00             | 1            | 32                  | 2 ms              | 4                   | 250 ns            |  |

| 01             | 2            | 64                  | 4 ms              | 8                   | 500 ns            |  |

| 10             | 4            | 128                 | 8 ms              | 16                  | 1 ms              |  |

| 11             | 8            | 256                 | 16 ms             | 32                  | 2 ms              |  |

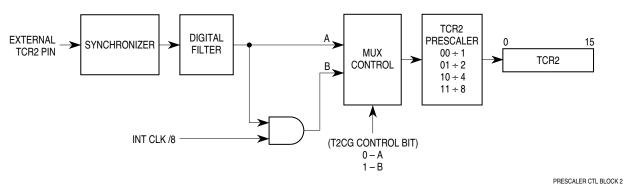

# TCR2P — Timer Count Register 2 Prescaler Control

TCR2 is clocked from the output of a prescaler. If T2CG = 0, the input to the TCR2 prescaler is the external TCR2 clock source. If T2CG = 1, the input is the TPU system clock divided by eight. The TCR2P field specifies the value of the prescaler: 1, 2, 4, or 8. Channels using TCR2 have the capability to resolve down to the TPU system clock divided by 8. The following table is a summary of prescaler output.

| TCR2 Prescaler | Divide By | Internal Clock Divided<br>By | External Clock Divided<br>By |

|----------------|-----------|------------------------------|------------------------------|

| 00             | 1         | 8                            | 1                            |

| 01             | 2         | 16                           | 2                            |

| 10             | 4         | 32                           | 4                            |

| 11             | 8         | 64                           | 8                            |

| Pin Names                              | Mnemonics  | Mode                      | Function                                                             |

|----------------------------------------|------------|---------------------------|----------------------------------------------------------------------|

| Master In Slave Out                    | MISO       | Master<br>Slave           | Serial Data Input to QSPI<br>Serial Data Output from QSPI            |

| Master Out Slave In                    | MOSI       | Master<br>Slave           | Serial Data Output from QSPI<br>Serial Data Input to QSPI            |

| Serial Clock                           | SCK        | Master<br>Slave           | Clock Output from QSPI<br>Clock Input to QSPI                        |

| Peripheral Chip Selects                | PCS[3:1]   | Master                    | Select Peripherals                                                   |

| Peripheral Chip Select<br>Slave Select | PCS0<br>SS | Master<br>Master<br>Slave | Selects Peripheral<br>Causes Mode Fault<br>Initiates Serial Transfer |

# 6.5.2 QSPI Registers

The programmer's model for the QSPI submodule consists of the QSM global and pin control registers, four QSPI control registers, one status register, and the 80-byte QSPI RAM.

The CPU can read and write to registers and RAM. The four control registers must be initialized before the QSPI is enabled to ensure defined operation. SPCR1 should be written last because it contains QSPI enable bit SPE. Asserting this bit starts the QSPI. The QSPI control registers are reset to a defined state and can then be changed by the CPU. Reset values are shown below each register.

Refer to the following memory map of the QSPI.

| Address  | Name  | Usage                          |

|----------|-------|--------------------------------|

| \$YFFC18 | SPCR0 | QSPI Control Register 0        |

| \$YFFC1A | SPCR1 | QSPI Control Register 1        |

| \$YFFC1C | SPCR2 | QSPI Control Register 2        |

| \$YFFC1E | SPCR3 | QSPI Control Register 3        |

| \$YFFC1F | SPSR  | QSPI Status Register           |

| \$YFFD00 | RAM   | QSPI Receive Data (16 Words)   |

| \$YFFD20 | RAM   | QSPI Transmit Data (16 Words)  |

| \$YFFD40 | RAM   | QSPI Command Control (8 Words) |

Writing a different value into any control register except SPCR2 while the QSPI is enabled disrupts operation. SPCR2 is buffered to prevent disruption of the current serial transfer. After completion of the current serial transfer, the new SPCR2 values become effective.

Writing the same value into any control register except SPCR2 while the QSPI is enabled has no effect on QSPI operation. Rewriting NEWQP in SPCR2 causes execution to restart at the designated location.

| SPCR0 — QSPI Control Register 0 \$YFI |        |      |      |   |   |    |      |      |      |   |   |   |   | FC18 |   |   |  |

|---------------------------------------|--------|------|------|---|---|----|------|------|------|---|---|---|---|------|---|---|--|

|                                       | 15     | 14   | 13   |   |   | 10 | 9    | 8    | 7    |   |   |   |   |      |   | 0 |  |

|                                       | MSTR   | WOMQ | BITS |   |   |    | CPOL | CPHA | SPBR |   |   |   |   |      |   |   |  |

|                                       | RESET: |      |      |   |   |    |      |      |      |   |   |   |   |      |   |   |  |

|                                       | 0      | 0    | 0    | 0 | 0 | 0  | 0    | 1    | 0    | 0 | 0 | 0 | 0 | 1    | 0 | 0 |  |

SPCR0 contains parameters for configuring the QSPI before it is enabled. The CPU can read and write this register. The QSM has read-only access.

# 7 Standby RAM with TPU Emulation RAM

The TPURAM module contains a 2-Kbyte array of fast (two bus cycle) static RAM, which is especially useful for system stacks and variable storage. Alternately, it can be used by the TPU as emulation RAM for new timer algorithms.

### 7.1 Overview

The TPURAM can be mapped to any 4-Kbyte boundary in the address map, but must not overlap the module control registers. (Overlap makes the registers inaccessible.) Data can be read or written in bytes, word, or long words. TPURAM responds to both program and data space accesses. Data can be read or written in bytes, words, or long words. The TPURAM is powered by  $V_{DD}$  in normal operation. During power-down, the TPURAM contents are maintained by power on standby voltage pin  $V_{STBY}$ . Power switching between sources is automatic.

Access to the TPURAM array is controlled by the RASP field in TRAMMCR. This field can be encoded so that TPURAM responds to both program and data space accesses. This allows code to be executed from TPURAM, and permits the use of program counter relative addressing mode for operand fetches from the array.

An address map of the TPURAM control registers follows. All TPURAM control registers are located in supervisor data space.

| Access | Address                                         | 15 8 7                                          | 0 |  |  |  |  |

|--------|-------------------------------------------------|-------------------------------------------------|---|--|--|--|--|

| S      | \$YFFB00                                        | TPURAM MODULE CONFIGURATION REGISTER (TRAMMCR)  |   |  |  |  |  |

| S      | \$YFFB02                                        | \$YFFB02         TPURAM TEST REGISTER (TRAMTST) |   |  |  |  |  |

| S      | \$YFFB04 TPURAM BASE ADDRESS REGISTER (TRAMBAR) |                                                 |   |  |  |  |  |

|        | \$YFFB06–<br>\$YFFB3F                           | NOT USED                                        |   |  |  |  |  |

#### Table 28 TPURAM Control Register Address Map

Y = M111, where M is the logic state of the MM bit in the SIMCR.

### 7.2 TPURAM Register Block

There are three TPURAM control registers: the RAM module configuration register (TRAMMCR), the RAM test register (TRAMTST), and the RAM array base address registers (TRAMBAR).

There is an 8-byte minimum register block size for the module. Unimplemented register addresses are read as zeros, and writes have no effect.

# 7.3 TPURAM Registers

| TRAMM  | ICR — | TPUR | AM Mo | odule C | configu |   | \$YFFB00 |   |          |   |

|--------|-------|------|-------|---------|---------|---|----------|---|----------|---|

| 15     | 14    | 13   | 12    | 11      | 10      | 9 | 8        | 7 |          | 0 |

| STOP   | 0     | 0    | 0     | 0       | 0       | 0 | RASP     |   | NOT USED |   |

| RESET: |       |      |       | •       |         |   |          |   |          |   |

| 0      | 0     | 0    | 0     | ٥       | 0       | 0 | 1        |   |          |   |

TSTOP —Stop Control

0 = RAM array operates normally.

1 = RAM array enters low-power stop mode.

This bit controls whether the RAM array is in stop mode or normal operation. Reset state is zero, for normal operation. In stop mode, the array retains its contents, but cannot be read or written by the CPU.

Home Page: www.freescale.com email: support@freescale.com USA/Europe or Locations Not Listed: Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH **Technical Information Center** Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com Japan: Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com Asia/Pacific: Freescale Semiconductor Hong Kong Ltd. **Technical Information Center** 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

RoHS-compliant and/or Pb- free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb- free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale.s Environmental Products program, go to http://www.freescale.com/epp.