Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000                       |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Active                                                     |

| Core Processor             | CPU32                                                      |

| Core Size                  | 32-Bit Single-Core                                         |

| Speed                      | 25MHz                                                      |

| Connectivity               | EBI/EMI, SCI, SPI, UART/USART                              |

| Peripherals                | POR, PWM, WDT                                              |

| Number of I/O              | 15                                                         |

| Program Memory Size        |                                                            |

| Program Memory Type        | ROMIess                                                    |

| EEPROM Size                | -                                                          |

| RAM Size                   | 2K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                |

| Data Converters            |                                                            |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 132-BQFP Bumpered                                          |

| Supplier Device Package    | 132-PQFP (24.13x24.13)                                     |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68332gveh25 |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

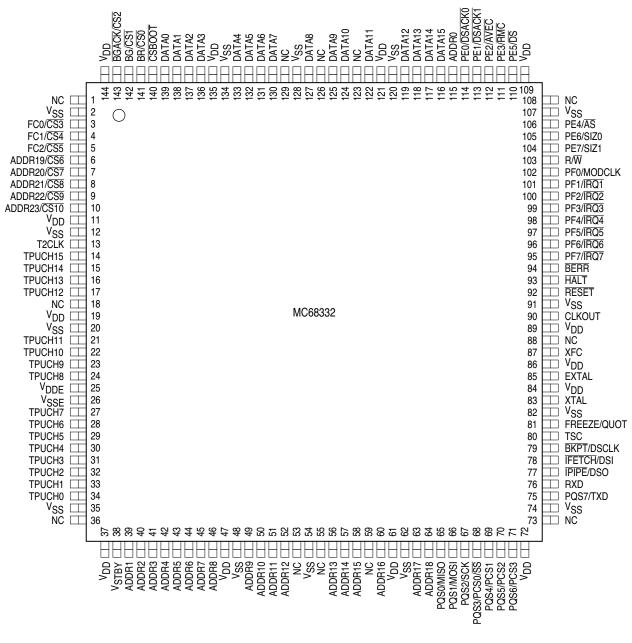

332 144-PIN QFP

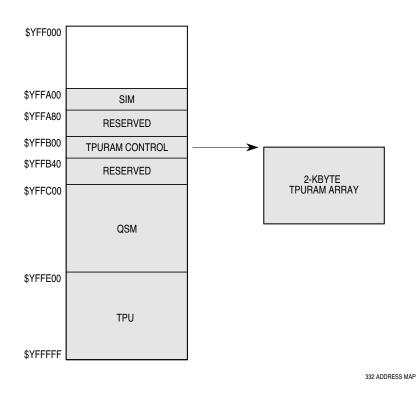

### 1.4 Address Map

The following figure is a map of the MCU internal addresses. The RAM array is positioned by the base address registers in the associated RAM control block. Unimplemented blocks are mapped externally.

Figure 4 MCU Address Map

### 1.5 Intermodule Bus

The intermodule bus (IMB) is a standardized bus developed to facilitate both design and operation of modular microcontrollers. It contains circuitry to support exception processing, address space partitioning, multiple interrupt levels, and vectored interrupts. The standardized modules in the MCU communicate with one another and with external components through the IMB. The IMB in the MCU uses 24 address and 16 data lines.

## **2 Signal Descriptions**

## 2.1 Pin Characteristics

The following table shows MCU pins and their characteristics. All inputs detect CMOS logic levels. All inputs can be put in a high-impedance state, but the method of doing this differs depending upon pin function. Refer to the table, MCU Driver Types, for a description of output drivers. An entry in the discrete I/O column of the MCU Pin Characteristics table indicates that a pin has an alternate I/O function. The port designation is given when it applies. Refer to the MCU Block Diagram for information about port organization.

| Pin<br>Mnemonic         | Output<br>Driver | Input<br>Synchronized | Input<br>Hysteresis | Discrete<br>I/O | Port<br>Designation |

|-------------------------|------------------|-----------------------|---------------------|-----------------|---------------------|

| ADDR23/CS10/ECLK        | A                | Y                     | N                   | 0               | —                   |

| ADDR[22:19]/CS[9:6]     | A                | Y                     | N                   | 0               | PC[6:3]             |

| ADDR[18:0]              | A                | Y                     | N                   | —               | —                   |

| ĀS                      | В                | Y                     | N                   | I/O             | PE5                 |

| AVEC                    | В                | Y                     | N                   | I/O             | PE2                 |

| BERR                    | В                | Y                     | N                   | _               |                     |

| BG/CS1                  | В                | _                     | —                   | _               |                     |

| BGACK/CS2               | В                | Y                     | N                   | _               |                     |

| BKPT/DSCLK              |                  | Y                     | Y                   | _               |                     |

| BR/CS0                  | В                | Y                     | N                   | —               |                     |

| CLKOUT                  | A                | _                     | —                   | _               |                     |

| CSBOOT                  | В                |                       | _                   | —               |                     |

| DATA[15:0] <sup>1</sup> | Aw               | Y                     | N                   | —               |                     |

| DS                      | В                | Y                     | N                   | I/O             | PE4                 |

| DSACK1                  | В                | Y                     | N                   | I/O             | PE1                 |

| DSACK0                  | В                | Y                     | N                   | I/O             | PE0                 |

| DSI/IFETCH              | A                | Y                     | Y                   | —               |                     |

| DSO/IPIPE               | A                |                       | —                   | —               | _                   |

| EXTAL <sup>2</sup>      | —                |                       | Special             | —               |                     |

| FC[2:0]/CS[5:3]         | A                | Y                     | N                   | 0               | PC[2:0]             |

| FREEZE/QUOT             | A                |                       | _                   | —               |                     |

| HALT                    | Bo               | Y                     | N                   | —               |                     |

| IRQ[7:1]                | В                | Y                     | Y                   | I/O             | PF[7:1]             |

| MISO                    | Bo               | Y                     | Y                   | I/O             | PQS0                |

| MODCLK <sup>1</sup>     | В                | Y                     | N                   | I/O             | PF0                 |

| MOSI                    | Bo               | Y                     | Y                   | I/O             | PQS1                |

| PCS0/SS                 | Во               | Y                     | Y                   | I/O             | PQS3                |

| PCS[3:1]                | Во               | Y                     | Y                   | I/O             | PQS[6:4]            |

| R/W                     | A                | Y                     | N                   | _               |                     |

| RESET                   | Во               | Y                     | Y                   | -               | —                   |

| RMC                     | В                | Y                     | N                   | I/O             | PE3                 |

| RXD                     | —                | Ν                     | N                   | —               | —                   |

| SCK                     | Bo               | Y                     | Y                   | I/O             | PQS2                |

| SIZ[1:0]                | В                | Y                     | N                   | I/O             | PE[7:6]             |

### Table 2 MCU Pin Characteristic

### 3.2.3 Bus Monitor

The internal bus monitor checks for excessively long DSACK response times during normal bus cycles and for excessively long DSACK or AVEC response times during interrupt acknowledge cycles. The monitor asserts BERR if response time is excessive.

DSACK and AVEC response times are measured in clock cycles. The maximum allowable response time can be selected by setting the BMT field.

The monitor does not check DSACK response on the external bus unless the CPU initiates the bus cycle. The BME bit in the SYPCR enables the internal bus monitor for internal to external bus cycles. If a system contains external bus masters, an external bus monitor must be implemented and the internal to external bus monitor option must be disabled.

### 3.2.4 Halt Monitor

The halt monitor responds to an assertion of  $\overline{HALT}$  on the internal bus. A flag in the reset status register (RSR) indicates that the last reset was caused by the halt monitor. The halt monitor reset can be inhibited by the HME bit in the SYPCR.

### 3.2.5 Spurious Interrupt Monitor

The spurious interrupt monitor issues **BERR** if no interrupt arbitration occurs during an interrupt-acknowledge cycle.

### 3.2.6 Software Watchdog

The software watchdog is controlled by SWE in the SYPCR. Once enabled, the watchdog requires that a service sequence be written to SWSR on a periodic basis. If servicing does not take place, the watchdog times out and issues a reset. This register can be written at any time, but returns zeros when read.

| SWSR —Software Service Re | gister |   |   |   |   |   |   | \$YI | FFA27 |

|---------------------------|--------|---|---|---|---|---|---|------|-------|

| 15                        | 8      | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0     |

| NOT USED                  | )      | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0     |

| RESET:                    |        |   |   |   |   |   |   |      |       |

|                           |        | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0     |

Register shown with read value

Perform a software watchdog service sequence as follows:

- a. Write \$55 to SWSR.

- b. Write \$AA to SWSR.

Both writes must occur before time-out in the order listed, but any number of instructions can be executed between the two writes.

The watchdog clock rate is affected by SWP and SWT in SYPCR. When SWT[1:0] are modified, a watchdog service sequence must be performed before the new time-out period takes effect.

The reset value of SWP is affected by the state of the MODCLK pin on the rising edge of reset, as shown in the following table.

| MODCLK | SWP |

|--------|-----|

| 0      | 1   |

| 1      | 0   |

### 3.2.7 Periodic Interrupt Timer

The periodic interrupt timer (PIT) generates interrupts of specified priorities at specified intervals. Timing for the PIT is provided by a programmable prescaler driven by the system clock.

| F | PICR — Periodic Interrupt Control Register |    |    |    |    |    |       |   |   |   |   |   |   | \$YF | FFA22 |   |

|---|--------------------------------------------|----|----|----|----|----|-------|---|---|---|---|---|---|------|-------|---|

|   | 15                                         | 14 | 13 | 12 | 11 | 10 |       | 8 | 7 |   |   |   |   |      |       | 0 |

| Γ | 0                                          | 0  | 0  | 0  | 0  |    | PIRQL |   |   |   |   | P | V |      |       |   |

|   | RESET:                                     |    |    |    |    |    |       |   |   |   |   |   |   |      |       |   |

|   | 0                                          | 0  | 0  | 0  | 0  | 0  | 0     | 0 | 0 | 0 | 0 | 0 | 1 | 1    | 1     | 1 |

This register contains information concerning periodic interrupt priority and vectoring. Bits [10:0] can be read or written at any time. Bits [15:11] are unimplemented and always return zero.

### PIRQL[2:0] — Periodic Interrupt Request Level

The following table shows what interrupt request level is asserted when a periodic interrupt is generated. If a PIT interrupt and an external IRQ signal of the same priority occur simultaneously, the PIT interrupt is serviced first. The periodic timer continues to run when the interrupt is disabled.

| PIRQL | Interrupt Request Level     |

|-------|-----------------------------|

| 000   | Periodic Interrupt Disabled |

| 001   | Interrupt Request Level 1   |

| 010   | Interrupt Request Level 2   |

| 011   | Interrupt Request Level 3   |

| 100   | Interrupt Request Level 4   |

| 101   | Interrupt Request Level 5   |

| 110   | Interrupt Request Level 6   |

| 111   | Interrupt Request Level 7   |

### PIV[7:0] — Periodic Interrupt Vector

The bits of this field contain the vector generated in response to an interrupt from the periodic timer. When the SIM responds, the periodic interrupt vector is placed on the bus.

#### PITR — Periodic Interrupt Timer Register

| 15     | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7 |   |   |    |    |   |   | 0 |

|--------|----|----|----|----|----|---|-----|---|---|---|----|----|---|---|---|

| 0      | 0  | 0  | 0  | 0  | 0  | 0 | PTP |   |   |   | Pľ | TM |   |   |   |

| RESET: |    |    |    |    |    |   |     |   |   |   |    |    |   |   |   |

| 0      | 0  | 0  | 0  | 0  | 0  | 0 |     | 0 | 0 | 0 | 0  | 0  | 0 | 0 | 0 |

The PITR contains the count value for the periodic timer. A zero value turns off the periodic timer. This register can be read or written at any time.

### PTP — Periodic Timer Prescaler Control

0 = Periodic timer clock not prescaled

1 = Periodic timer clock prescaled by a value of 512

The reset state of PTP is the complement of the state of the MODCLK signal during reset.

#### PITM[7:0] — Periodic Interrupt Timing Modulus Field

This is an 8-bit timing modulus. The period of the timer can be calculated as follows:

PIT Period = [(PITM)(Prescaler)(4)]/EXTAL

where

PIT Period = Periodic interrupt timer period PITM = Periodic interrupt timer register modulus (PITR[7:0]) EXTAL Frequency = Crystal frequency Prescale = 512 or 1 depending on the state of the PTP bit in the PITR **\$YFFA24**

### 3.5.1 Chip-Select Registers

Pin assignment registers CSPAR0 and CSPAR1 determine functions of chip-select pins. These registers also determine port size (8- or 16-bit) for dynamic bus allocation.

A pin data register (PORTC) latches discrete output data.

Blocks of addresses are assigned to each chip-select function. Block sizes of 2 Kbytes to 1 Mbyte can be selected by writing values to the appropriate base address register (CSBAR). Address blocks for separate chip-select functions can overlap.

Chip-select option registers (CSORBT and CSOR[10:0]) determine timing of and conditions for assertion of chip-select signals. Eight parameters, including operating mode, access size, synchronization, and wait state insertion can be specified.

Initialization code often resides in a peripheral memory device controlled by the chip-select circuits. A set of special chip-select functions and registers (CSORBT, CSBARBT) is provided to support bootstrap operation.

### 3.5.2 Pin Assignment Registers

The pin assignment registers (CSPAR0 and CSPAR1) contain pairs of bits that determine the function of chip-select pins. The pin assignment encodings used in these registers are shown below.

| Bit Field | Description               |

|-----------|---------------------------|

| 00        | Discrete Output           |

| 01        | Alternate Function        |

| 10        | Chip Select (8-Bit Port)  |

| 11        | Chip Select (16-Bit Port) |

### **Table 12 Pin Assignment Encodings**

### **CSPAR0**—Chip Select Pin Assignment Register 0

#### \$YFFA44

| 15     | 14 | 13  | 12    | 11  | 10    | 9   | 8     | 7   | 6     | 5   | 4     | 3   | 2     | 1   | 0   |

|--------|----|-----|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|-----|

| 0      | 0  | CSP | A0[6] | CSP | A0[5] | CSP | A0[4] | CSP | A0[3] | CSP | A0[2] | CSP | A0[1] | CSB | ООТ |

| RESET: |    |     |       |     |       |     |       |     |       |     |       |     |       |     |     |

0 0 DATA2 1 DATA2 1 DATA2 1 DATA1 1 DATA1 1 DATA1 1 1 DATA0

CSPAR0 contains seven 2-bit fields that determine the functions of corresponding chip-select pins. CSPAR0[15:14] are not used. These bits always read zero; writes have no effect. CSPAR0 bit 1 always reads one; writes to CSPAR0 bit 1 have no effect.

#### Table 13 CSPAR0 Pin Assignments

| CSPAR0 Field | Chip Select Signal | Alternate Signal | Discrete Output |

|--------------|--------------------|------------------|-----------------|

| CSPA0[6]     | CS5                | FC2              | PC2             |

| CSPA0[5]     | CS4                | FC1              | PC1             |

| CSPA0[4]     | CS3                | FC0              | PC0             |

| CSPA0[3]     | CS2                | BGACK            | _               |

| CSPA0[2]     | CS1                | BG               | —               |

| CSPA0[1]     | CSO                | BR               | _               |

| CSBOOT       | CSBOOT             | _                | _               |

| ( | CSPAR  | <b>1</b> —Ch | nip Sele | ect Pin | Assig | nment | Registe | er 1 |               |      |               |      |               |       | \$YF          | FA46 |

|---|--------|--------------|----------|---------|-------|-------|---------|------|---------------|------|---------------|------|---------------|-------|---------------|------|

|   | 15     | 14           | 13       | 12      | 11    | 10    | 9       | 8    | 7             | 6    | 5             | 4    | 3             | 2     | 1             | 0    |

| Γ | 0      | 0            | 0        | 0       | 0     | 0     | CSPA    | 1[4] | CSPA          | 1[3] | CSPA          | 1[2] | CSPA          | .1[1] | CSPA          | 1[0] |

|   | RESET: |              |          |         |       |       |         |      |               |      | •             |      |               |       | •             |      |

|   | 0      | 0            | 0        | 0       | 0     | 0     | DATA7   | 1    | DATA<br>[7:6] | 1    | DATA<br>[7:5] | 1    | DATA<br>[7:4] | 1     | DATA<br>[7:3] | 1    |

CSPAR1 contains five 2-bit fields that determine the functions of corresponding chip-select pins. CSPAR1[15:10] are not used. These bits always read zero; writes have no effect.

| CSPAR0 Field | Chip Select Signal | Alternate Signal | Discrete Output |

|--------------|--------------------|------------------|-----------------|

| CSPA1[4]     | CS10               | ADDR23           | ECLK            |

| CSPA1[3]     | CS9                | ADDR22           | PC6             |

| CSPA1[2]     | CS8                | ADDR21           | PC5             |

| CSPA1[1]     | CS7                | ADDR20           | PC4             |

| CSPA1[0]     | CS6                | ADDR19           | PC3             |

#### Table 14 CSPAR1 Pin Assignments

At reset, either the alternate function (01) or chip-select function (11) can be encoded. DATA pins are driven to logic level one by a weak interval pull-up during reset. Encoding is for chip-select function unless a data line is held low during reset. Note that bus loading can overcome the weak pull-up and hold pins low during reset. The following table shows the hierarchical selection method that determines the reset functions of pins controlled by CSPAR1.

|       | Data B | us Pins at | Reset |       | Chip-Select/Address Bus Pin Function |                |                |                |                |  |  |

|-------|--------|------------|-------|-------|--------------------------------------|----------------|----------------|----------------|----------------|--|--|

| DATA7 | DATA6  | DATA5      | DATA4 | DATA3 | CS10/<br>ADDR23                      | CS9/<br>ADDR22 | CS8/<br>ADDR21 | CS7/<br>ADDR20 | CS6/<br>ADDR19 |  |  |

| 1     | 1      | 1          | 1     | 1     | CS10                                 | CS9            | CS8            | CS7            | CS6            |  |  |

| 1     | 1      | 1          | 1     | 0     | CS10                                 | CS9            | CS8            | CS7            | ADDR19         |  |  |

| 1     | 1      | 1          | 0     | Х     | CS10                                 | CS9            | CS8            | ADDR20         | ADDR19         |  |  |

| 1     | 1      | 0          | Х     | Х     | CS10                                 | CS9            | ADDR21         | ADDR20         | ADDR19         |  |  |

| 1     | 0      | Х          | Х     | Х     | CS10                                 | ADDR22         | ADDR21         | ADDR20         | ADDR19         |  |  |

| 0     | Х      | Х          | Х     | Х     | ADDR23                               | ADDR22         | ADDR21         | ADDR20         | ADDR19         |  |  |

### Table 15 Reset Pin Function of CS[10:6]

A pin programmed as a discrete output drives an external signal to the value specified in the port C pin data register (PORTC), with the following exceptions:

- 1. No discrete output function is available on pins BR, BG, or BGACK.

- 2. ADDR23 provides E-clock output rather than a discrete output signal.

When a pin is programmed for discrete output or alternate function, internal chip-select logic still functions and can be used to generate DSACK or AVEC internally on an address match.

Port size is determined when a pin is assigned as a chip select. When a pin is assigned to an 8-bit port, the chip select is asserted at all addresses within the block range. If a pin is assigned to a 16-bit port, the upper/lower byte field of the option register selects the byte with which the chip select is associated.

### 3.5.3 Base Address Registers

A base address is the starting address for the block enabled by a given chip select. Block size determines the extent of the block above the base address. Each chip select has an associated base register so that an efficient address map can be constructed for each application. If a chip-select base address register is programmed with the same address as a microcontroller module or memory array, an access to that address goes to the module or array and the chip-select signal is not asserted.

| CSBAR       | BT —                  | Chip-S      | Select E   | Base A     | ddress        | Regis        | ter Bo                  | ot RON     | Л               |                 |                 |                   |        | \$YF    | FA48             |

|-------------|-----------------------|-------------|------------|------------|---------------|--------------|-------------------------|------------|-----------------|-----------------|-----------------|-------------------|--------|---------|------------------|

| 15          | 14                    | 13          | 12         | 11         | 10            | 9            | 8                       | 7          | 6               | 5               | 4               | 3                 | 2      |         | 0                |

| ADDR<br>23  | ADDR<br>22            | ADDR<br>21  | ADDR<br>20 | ADDR<br>19 | ADDR<br>18    | ADDR<br>17   | ADDR<br>16              | ADDR<br>15 | ADDR<br>14      | ADDR<br>13      | ADDR<br>12      | ADDR<br>11        |        | BLKSZ   |                  |

| RESET:      |                       |             |            |            |               |              |                         |            |                 |                 |                 |                   |        |         |                  |

| 0           | 0                     | 0           | 0          | 0          | 0             | 0            | 0                       | 0          | 0               | 0               | 0               | 0                 | 1      | 1       | 1                |

|             |                       |             |            |            |               |              |                         |            |                 |                 |                 | \$YFFA4C-\$YFFA74 |        |         |                  |

| CSBAR       | [10:0]                | —Chip       | o-Selec    | t Base     | Addre         | ess Re       | gisters                 |            |                 |                 |                 | \$`               | /FFA4  | 4C–\$YF | FA74             |

| CSBAR<br>15 | [ <b>10:0</b> ]<br>14 | —Chip<br>13 | -Selec     | t Base     | e Addre<br>10 | ess Reg<br>9 | gisters<br><sup>8</sup> | 7          | 6               | 5               | 4               | <b>\$`</b><br>3   | 2 PFFA | 4C–\$YF | <b>FA74</b><br>0 |

|             |                       | •           |            |            |               |              | •                       |            | 6<br>ADDR<br>14 | 5<br>ADDR<br>13 | 4<br>ADDR<br>12 |                   |        | 4C-\$YF |                  |

| 15<br>ADDR  | 14<br>ADDR            | 13<br>ADDR  | 12<br>ADDR | 11<br>ADDR | 10<br>ADDR    | 9<br>ADDR    | 8<br>ADDR               | 7<br>ADDR  | ADDR            | ADDR            | ADDR            | 3<br>ADDR         |        |         |                  |

### ADDR[23:11] - Base Address Field

This field sets the starting address of a particular address space. The address compare logic uses only the most significant bits to match an address within a block. The value of the base address must be a multiple of block size. Base address register diagrams show how base register bits correspond to address lines.

### BLKSZ — Block Size Field

This field determines the size of the block that must be enabled by the chip select. The following table shows bit encoding for the base address registers block size field.

| Block Size Field | Block Size | Address Lines Compared |

|------------------|------------|------------------------|

| 000              | 2 K        | ADDR[23:11]            |

| 001              | 8 K        | ADDR[23:13]            |

| 010              | 16 K       | ADDR[23:14]            |

| 011              | 64 K       | ADDR[23:16]            |

| 100              | 128 K      | ADDR[23:17]            |

| 101              | 256 K      | ADDR[23:18]            |

| 110              | 512 K      | ADDR[23:19]            |

| 111              | 1 M        | ADDR[23:20]            |

### 3.5.4 Option Registers

The option registers contain eight fields that determine timing of and conditions for assertion of chipselect signals. For a chip-select signal to be asserted, all bits in the base address register must match the corresponding internal upper address lines, and all conditions specified in the option register must be satisfied. These conditions also apply to providing DSACK or autovector support.

| PEPAR — Port E Pin Assignment Register |   |       |       |       |       |       |       | \$YF  | FA17  |

|----------------------------------------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 15                                     | 8 | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| NOT USED                               |   | PEPA7 | PEPA6 | PEPA5 | PEPA4 | PEPA3 | PEPA2 | PEPA1 | PEPA0 |

| RESET:                                 |   |       |       |       |       |       |       |       |       |

DATA8 DATA8 DATA8 DATA8 DATA8 DATA8 DATA8 DATA8

The bits in this register control the function of each port E pin. Any bit set to one configures the corresponding pin as a bus control signal, with the function shown in the following table. Any bit cleared to zero defines the corresponding pin to be an I/O pin, controlled by PORTE and DDRE.

Data bus bit 8 controls the state of this register following reset. If DATA8 is set to one during reset, the register is set to \$FF, which defines all port E pins as bus control signals. If DATA8 is cleared to zero during reset, this register is set to \$00, configuring all port E pins as I/O pins.

Any bit cleared to zero defines the corresponding pin to be an I/O pin. Any bit set to one defines the corresponding pin to be a bus control signal.

| PEPAR Bit | Port E Signal | Bus Control Signal |

|-----------|---------------|--------------------|

| PEPA7     | PE7           | SIZ1               |

| PEPA6     | PE6           | SIZO               |

| PEPA5     | PE5           | ĀS                 |

| PEPA4     | PE4           | DS                 |

| PEPA3     | PE3           | RMC                |

| PEPA2     | PE2           | AVEC               |

| PEPA1     | PE1           | DSACK1             |

| PEPA0     | PE0           | DSACK0             |

### Table 16 Port E Pin Assignments

| PORTF0, PORTF1 — Port F Data Register |   |     |     |     | \$YFFA19, \$YFFA1B |     |     |     |     |

|---------------------------------------|---|-----|-----|-----|--------------------|-----|-----|-----|-----|

| 15                                    | 8 | 7   | 6   | 5   | 4                  | 3   | 2   | 1   | 0   |

| NOT USED                              |   | PF7 | PF6 | PF5 | PF4                | PF3 | PF2 | PF1 | PF0 |

| RESET:                                |   |     |     |     |                    |     |     |     |     |

|                                       |   | U   | U   | U   | U                  | U   | U   | U   | U   |

The write to the port F data register is stored in the internal data latch, and if any port F pin is configured as an output, the value stored for that bit is driven onto the pin. A read of the port F data register returns the value at the pin only if the pin is configured as a discrete input. Otherwise, the value read is the value stored in the register.

The port F data register is a single register that can be accessed in two locations. When accessed at \$YFFA19, the register is referred to as PORTF0; when accessed at \$YFFA1B, the register is referred to as PORTF1. The register can be read or written at any time. It is unaffected by reset.

| DDRF — Port F Data Direction Register |   |      |      |      |      |      |      | \$YF | FA1D |

|---------------------------------------|---|------|------|------|------|------|------|------|------|

| 15                                    | 8 | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| NOT USED                              |   | DDF7 | DDF6 | DDF5 | DDF4 | DDF3 | DDF2 | DDF1 | DDF0 |

| RESET:                                |   |      |      |      |      |      |      |      |      |

|                                       |   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

The bits in this register control the direction of the pin drivers when the pins are configured for I/O. Any bit in this register set to one configures the corresponding pin as an output. Any bit in this register cleared to zero configures the corresponding pin as an input.

| <b>PFPAR</b> — Port F Pin Assignment Register |   |       |       |       |       |       |       | \$YF  | FA1F  |

|-----------------------------------------------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 15                                            | 8 | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| NOT USED                                      |   | PFPA7 | PFPA6 | PFPA5 | PFPA4 | PFPA3 | PFPA2 | PFPA1 | PFPA0 |

| DEOET                                         |   |       | •     |       |       |       |       |       |       |

RESET:

DATA9 DATA9 DATA9 DATA9 DATA9 DATA9 DATA9 DATA9

The bits in this register control the function of each port F pin. Any bit cleared to zero defines the corresponding pin to be an I/O pin. Any bit set to one defines the corresponding pin to be an interrupt request signal or MODCLK. The MODCLK signal has no function after reset.

### Table 17 Port F Pin Assignments

| PFPAR Field | Port F Signal | Alternate Signal |

|-------------|---------------|------------------|

| PFPA7       | PF7           | IRQ7             |

| PFPA6       | PF6           | IRQ6             |

| PFPA5       | PF5           | IRQ5             |

| PFPA4       | PF4           | IRQ4             |

| PFPA3       | PF3           | IRQ3             |

| PFPA2       | PF2           | IRQ2             |

| PFPA1       | PF1           | IRQ1             |

| PFPA0       | PF0           | MODCLK           |

Data bus pin 9 controls the state of this register following reset. If DATA9 is set to one during reset, the register is set to \$FF, which defines all port F pins as interrupt request inputs. If DATA9 is cleared to zero during reset, this register is set to \$00, defining all port F pins as I/O pins.

### 3.7 Resets

Reset procedures handle system initialization and recovery from catastrophic failure. The MCU performs resets with a combination of hardware and software. The system integration module determines whether a reset is valid, asserts control signals, performs basic system configuration based on hardware mode-select inputs, then passes control to the CPU.

Reset occurs when an active low logic level on the RESET pin is clocked into the SIM. Resets are gated by the CLKOUT signal. Asynchronous resets are assumed to be catastrophic. An asynchronous reset can occur on any clock edge. Synchronous resets are timed to occur at the end of bus cycles. If there is no clock when RESET is asserted, reset does not occur until the clock starts. Resets are clocked in order to allow completion of write cycles in progress at the time RESET is asserted.

Reset is the highest-priority CPU32 exception. Any processing in progress is aborted by the reset exception, and cannot be restarted. Only essential tasks are performed during reset exception processing. Other initialization tasks must be accomplished by the exception handler routine.

### 3.7.1 SIM Reset Mode Selection

The logic states of certain data bus pins during reset determine SIM operating configuration. In addition, the state of the MODCLK pin determines system clock source and the state of the BKPT pin determines what happens during subsequent breakpoint assertions. The following table is a summary of reset mode selection options.

### Table 18 Reset Mode Selection

| Mode Select Pin | Default Function   | Alternate Function |

|-----------------|--------------------|--------------------|

|                 | (Pin Left High)    | (Pin Pulled Low)   |

|                 | (· ··· =•·····g··) | (                  |

| Instruction               | Syntax                                                      | Operand Size                                                                                            | Operation                                                                                                                                                                                                                                        |

|---------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBcc                      | Dn, label                                                   | 16                                                                                                      | If condition false, then $Dn - 1 \Rightarrow PC$ ;<br>if $Dn \neq (-1)$ , then $PC + d \Rightarrow PC$                                                                                                                                           |

| DIVS/DIVU                 | <ea>, Dn</ea>                                               | 32/16 ⇒ 16 : 16                                                                                         | Destination / Source $\Rightarrow$ Destination (signed or unsigned)                                                                                                                                                                              |

| DIVSL/DIVUL               | <ea>, Dr : Dq<br/><ea>, Dq<br/><ea>, Dr : Dq</ea></ea></ea> | $\begin{array}{c} 64/32 \Rightarrow 32:32\\ 32/32 \Rightarrow 32\\ 32/32 \Rightarrow 32:32 \end{array}$ | Destination / Source $\Rightarrow$ Destination (signed or unsigned)                                                                                                                                                                              |

| EOR                       | Dn, <ea></ea>                                               | 8, 16, 32                                                                                               | Source $\oplus$ Destination $\Rightarrow$ Destination                                                                                                                                                                                            |

| EORI                      | # <data>, <ea></ea></data>                                  | 8, 16, 32                                                                                               | Data $\oplus$ Destination $\Rightarrow$ Destination                                                                                                                                                                                              |

| EORI to CCR               | # <data>, CCR</data>                                        | 8                                                                                                       | Source $\oplus$ CCR $\Rightarrow$ CCR                                                                                                                                                                                                            |

| EORI to SR <sup>1</sup>   | # <data>, SR</data>                                         | 16                                                                                                      | Source $\oplus$ SR $\Rightarrow$ SR                                                                                                                                                                                                              |

| EXG                       | Rn, Rn                                                      | 32                                                                                                      | $Rn \Rightarrow Rn$                                                                                                                                                                                                                              |

| EXT                       | Dn<br>Dn                                                    | $\begin{array}{c} 8 \Rightarrow 16 \\ 16 \Rightarrow 32 \end{array}$                                    | Sign extended Destination $\Rightarrow$ Destination                                                                                                                                                                                              |

| EXTB                      | Dn                                                          | $8 \Rightarrow 32$                                                                                      | Sign extended Destination $\Rightarrow$ Destination                                                                                                                                                                                              |

| ILLEGAL                   | none                                                        | none                                                                                                    | $\begin{array}{l} SSP-2 \Rightarrow SSP; \text{ vector offset} \Rightarrow (SSP);\\ SSP-4 \Rightarrow SSP; PC \Rightarrow (SSP);\\ SSP-2 \Rightarrow SSP; SR \Rightarrow (SSP);\\ Illegal instruction vector address \Rightarrow PC \end{array}$ |

| JMP                       | Í                                                           | none                                                                                                    | Destination $\Rightarrow$ PC                                                                                                                                                                                                                     |

| JSR                       | Í                                                           | none                                                                                                    | SP – 4 $\Rightarrow$ SP; PC $\Rightarrow$ (SP); destination $\Rightarrow$ PC                                                                                                                                                                     |

| LEA                       | <ea>, An</ea>                                               | 32                                                                                                      | $\langle ea \rangle \Rightarrow An$                                                                                                                                                                                                              |

| LINK                      | An, # d                                                     | 16, 32                                                                                                  | $SP - 4 \Rightarrow SP$ , $An \Rightarrow (SP)$ ; $SP \Rightarrow An$ , $SP + d \Rightarrow SP$                                                                                                                                                  |

| LPSTOP <sup>1</sup>       | # <data></data>                                             | 16                                                                                                      | $Data \Rightarrow SR; interrupt \; mask \Rightarrow EBI;  STOP$                                                                                                                                                                                  |

| LSL                       | Dn, Dn<br># <data>, Dn<br/>ĺ</data>                         | 8, 16, 32<br>8, 16, 32<br>16                                                                            | X/C - 0                                                                                                                                                                                                                                          |

| LSR                       | Dn, Dn<br># <data>, Dn<br/>Í</data>                         | 8, 16, 32<br>8, 16, 32<br>16                                                                            | 0                                                                                                                                                                                                                                                |

| MOVE                      | <ea>, <ea></ea></ea>                                        | 8, 16, 32                                                                                               | Source $\Rightarrow$ Destination                                                                                                                                                                                                                 |

| MOVEA                     | <ea>, An</ea>                                               | 16, $32 \Rightarrow 32$                                                                                 | Source $\Rightarrow$ Destination                                                                                                                                                                                                                 |

| MOVEA <sup>1</sup>        | USP, An<br>An, USP                                          | 32<br>32                                                                                                | $\begin{array}{l} USP \Rightarrow An \\ An \Rightarrow USP \end{array}$                                                                                                                                                                          |

| MOVE from CCR             | CCR, <ea></ea>                                              | 16                                                                                                      | $CCR \Rightarrow Destination$                                                                                                                                                                                                                    |

| MOVE to CCR               | <ea>, CCR</ea>                                              | 16                                                                                                      | Source $\Rightarrow$ CCR                                                                                                                                                                                                                         |

| MOVE from SR <sup>1</sup> | SR, <ea></ea>                                               | 16                                                                                                      | $SR \Rightarrow Destination$                                                                                                                                                                                                                     |

| MOVE to SR <sup>1</sup>   | <ea>, SR</ea>                                               | 16                                                                                                      | Source $\Rightarrow$ SR                                                                                                                                                                                                                          |

| MOVE USP <sup>1</sup>     | USP, An<br>An, USP                                          | 32<br>32                                                                                                | $\begin{array}{l} USP \Rightarrow An \\ An \Rightarrow USP \end{array}$                                                                                                                                                                          |

| MOVEC <sup>1</sup>        | Rc, Rn<br>Rn, Rc                                            | 32<br>32                                                                                                | $ \begin{array}{l} Rc \Rightarrow Rn \\ Rn \Rightarrow Rc \end{array} $                                                                                                                                                                          |

| MOVEM                     | list, <ea><br/><ea>, list</ea></ea>                         | 16, 32<br>16, 32 ⇒ 32                                                                                   | Listed registers $\Rightarrow$ Destination<br>Source $\Rightarrow$ Listed registers                                                                                                                                                              |

| MOVEP                     | Dn, (d16, An)                                               | 16, 32                                                                                                  | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                           |

|                           | (d16, An), Dn                                               |                                                                                                         | $\begin{array}{l} (An+d) \Rightarrow Dn \ [31:24]; \ (An+d+2) \Rightarrow Dn \ [23:16]; \\ (An+d+4) \Rightarrow Dn \ [15:8]; \ (An+d+6) \Rightarrow Dn \ [7:0] \end{array}$                                                                      |

| MOVEQ                     | # <data>, Dn</data>                                         | $8 \Rightarrow 32$                                                                                      | Immediate data $\Rightarrow$ Destination                                                                                                                                                                                                         |

### Table 20 Instruction Set Summary(Continued)

### 4.7 Background Debugging Mode

The background debugger on the CPU32 is implemented in CPU microcode. The background debugging commands are summarized below.

| <b>0</b>              | Marana      | Description                                                                                                                                                                                                                                        |

|-----------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command               | Mnemonic    | Description                                                                                                                                                                                                                                        |

| Read D/A Register     | RDREG/RAREG | Read the selected address or data register and return the results through the serial interface.                                                                                                                                                    |

| Write D/A Register    | WDREG/WAREG | The data operand is written to the specified address or data register.                                                                                                                                                                             |

| Read System Register  | RSREG       | The specified system control register is read. All registers that can be read in supervisor mode can be read in background mode.                                                                                                                   |

| Write System Register | WSREG       | The operand data is written into the specified system control register.                                                                                                                                                                            |

| Read Memory Location  | READ        | Read the sized data at the memory location specified by the long-word address. The source function code register (SFC) determines the address space accessed.                                                                                      |

| Write Memory Location | WRITE       | Write the operand data to the memory location specified by the long-word address. The destination function code (DFC) register determines the address space accessed.                                                                              |

| Dump Memory Block     | DUMP        | Used in conjunction with the READ command to dump large<br>blocks of memory. An initial READ is executed to set up the<br>starting address of the block and retrieve the first result.<br>Subsequent operands are retrieved with the DUMP command. |

| Fill Memory Block     | FILL        | Used in conjunction with the WRITE command to fill large<br>blocks of memory. Initially, a WRITE is executed to set up the<br>starting address of the block and supply the first operand. The<br>FILL command writes subsequent operands.          |

| Resume Execution      | GO          | The pipe is flushed and refilled before resuming instruction execution at the current PC.                                                                                                                                                          |

| Patch User Code       | CALL        | Current program counter is stacked at the location of the current stack pointer. Instruction execution begins at user patch code.                                                                                                                  |

| Reset Peripherals     | RST         | Asserts RESET for 512 clock cycles. The CPU is not reset by this command. Synonymous with the CPU RESET instruction.                                                                                                                               |

| No Operation          | NOP         | NOP performs no operation and can be used as a null command.                                                                                                                                                                                       |

### Table 21 Background Debuggung Mode

### 5.1.2 Input Capture/Input Transition Counter (ITC)

Any channel of the TPU can capture the value of a specified TCR upon the occurrence of each transition or specified number of transitions, and then generate an interrupt request to notify the CPU. A channel can perform input captures continually, or a channel can detect a single transition or specified number of transitions, then cease channel activity until reinitialization. After each transition or specified number of transitions, the channel can generate a link to a sequential block of up to eight channels. The user specifies a starting channel of the block and the number of channels within the block. The generation of links depends on the mode of operation. In addition, after each transition or specified number of transitions, one byte of the parameter RAM (at an address specified by channel parameter) can be incremented and used as a flag to notify another channel of a transition.

## 5.1.3 Output Compare (OC)

The output compare function generates a rising edge, falling edge, or a toggle of the previous edge in one of three ways:

- 1. Immediately upon CPU initiation, thereby generating a pulse with a length equal to a programmable delay time.

- 2. At a programmable delay time from a user-specified time.

- 3. Continuously. Upon receiving a link from a channel, OC references, without CPU interaction, a specifiable period and calculates an offset:

Offset = Period \* Ratio

where Ratio is a parameter supplied by the user.

This algorithm generates a 50% duty-cycle continuous square wave with each high/low time equal to the calculated OFFSET. Due to offset calculation, there is an initial link time before continuous pulse generation begins.

### 5.1.4 Pulse-Width Modulation (PWM)

The TPU can generate a pulse-width modulation waveform with any duty cycle from zero to 100% (within the resolution and latency capability of the TPU). To define the PWM, the CPU provides one parameter that indicates the period and another parameter that indicates the high time. Updates to one or both of these parameters can direct the waveform change to take effect immediately, or coherently beginning at the next low-to-high transition of the pin.

### 5.1.5 Synchronized Pulse-Width Modulation (SPWM)

The TPU generates a PWM waveform in which the CPU can change the period and/or high time at any time. When synchronized to a time function on a second channel, the synchronized PWM low-to-high transitions have a time relationship to transitions on the second channel.

### 5.1.6 Period Measurement with Additional Transition Detect (PMA)

This function and the following function are used primarily in toothed-wheel speed-sensing applications, such as monitoring rotational speed of an engine. The period measurement with additional transition detect function allows for a special-purpose 23-bit period measurement. It can detect the occurrence of an additional transition (caused by an extra tooth on the sensed wheel) indicated by a period measurement that is less than a programmable ratio of the previous period measurement.

Once detected, this condition can be counted and compared to a programmable number of additional transitions detected before TCR2 is reset to \$FFFF. Alternatively, a byte at an address specified by a channel parameter can be read and used as a flag. A nonzero value of the flag indicates that TCR2 is to be reset to \$FFFF once the next additional transition is detected.

### 5.2.9 Frequency Measurement (FQM)

FQM counts the number of input pulses to a TPU channel during a user-defined window period. The function has single shot and continuous modes. No pulses are lost between sample windows in continuous mode. The user selects whether to detect pulses on the rising or falling edge. This function is intended for high speed measurement; measurement of slow pulses with noise rejection can be made with PTA.

### 5.2.10 Hall Effect Decode (HALLD)

This function decodes the sensor signals from a brushless motor, along with a direction input from the CPU, into a state number. The function supports two- or three-sensor decoding. The decoded state number is written into a COMM channel, which outputs the required commutation drive signals. In addition to brushless motor applications, the function can have more general applications, such as decoding "option" switches.

### 5.3 Programmer's Model

The TPU control register address map occupies 512 bytes. The "Access" column in the TPU address map below indicates which registers are accessible only at the supervisor privilege level and which can be assigned to either the supervisor or user privilege level, according to the value of the SUPV bit in the TPUMCR.

| Access | Address  | 15 8 7                                        | 0 |

|--------|----------|-----------------------------------------------|---|

| S      | \$YFFE00 | TPU MODULE CONFIGURATION REGISTER (TPUMCR)    |   |

| S      | \$YFFE02 | TEST CONFIGURATION REGISTER (TCR)             |   |

| S      | \$YFFE04 | DEVELOPMENT SUPPORT CONTROL REGISTER (DSCR)   |   |

| S      | \$YFFE06 | DEVELOPMENT SUPPORT STATUS REGISTER (DSSR)    |   |

| S      | \$YFFE08 | TPU INTERRUPT CONFIGURATION REGISTER (TICR)   |   |

| S      | \$YFFE0A | CHANNEL INTERRUPT ENABLE REGISTER (CIER)      |   |

| S      | \$YFFE0C | CHANNEL FUNCTION SELECTION REGISTER 0 (CFSR0) |   |

| S      | \$YFFE0E | CHANNEL FUNCTION SELECTION REGISTER 1 (CFSR1) |   |

| S      | \$YFFE10 | CHANNEL FUNCTION SELECTION REGISTER 2 (CFSR2) |   |

| S      | \$YFFE12 | CHANNEL FUNCTION SELECTION REGISTER 3 (CFSR3) |   |

| S/U    | \$YFFE14 | HOST SEQUENCE REGISTER 0 (HSQR0)              |   |

| S/U    | \$YFFE16 | HOST SEQUENCE REGISTER 1 (HSQR1)              |   |

| S/U    | \$YFFE18 | HOST SERVICE REQUEST REGISTER 0 (HSRR0)       |   |

| S/U    | \$YFFE1A | HOST SERVICE REQUEST REGISTER 1 (HSRR1)       |   |

| S      | \$YFFE1C | CHANNEL PRIORITY REGISTER 0 (CPR0)            |   |

| S      | \$YFFE1E | CHANNEL PRIORITY REGISTER 1 (CPR1)            |   |

| S      | \$YFFE20 | CHANNEL INTERRUPT STATUS REGISTER (CISR)      |   |

| S      | \$YFFE22 | LINK REGISTER (LR)                            |   |

| S      | \$YFFE24 | SERVICE GRANT LATCH REGISTER (SGLR)           |   |

| S      | \$YFFE26 | DECODED CHANNEL NUMBER REGISTER (DCNR)        |   |

#### Table 22 TPU Address Map

Y = M111, where M represents the logic state of the module mapping (MM) bit in the SIMCR.

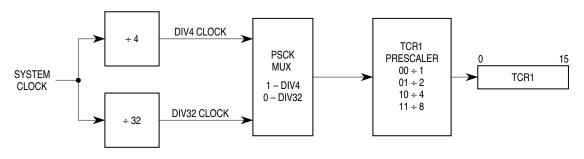

### TCR1P — Timer Count Register 1 Prescaler Control

TCR1 is clocked from the output of a prescaler. The prescaler's input is the internal TPU system clock divided by either 4 or 32, depending on the value of the PSCK bit. The prescaler divides this input by 1, 2, 4, or 8. Channels using TCR1 have the capability to resolve down to the TPU system clock divided by 4.

PRESCALER CTL BLOCK 1

|                |              | PSC                 | K = 0             | PSCK = 1            |                   |  |  |

|----------------|--------------|---------------------|-------------------|---------------------|-------------------|--|--|

| TCR1 Prescaler | Divide<br>By | Number of<br>Clocks | Rate at<br>16 MHz | Number of<br>Clocks | Rate at<br>16 MHz |  |  |

| 00             | 1            | 32                  | 2 ms              | 4                   | 250 ns            |  |  |

| 01             | 2            | 64                  | 4 ms              | 8                   | 500 ns            |  |  |

| 10             | 4            | 128                 | 8 ms              | 16                  | 1 ms              |  |  |

| 11             | 8            | 256                 | 16 ms             | 32                  | 2 ms              |  |  |

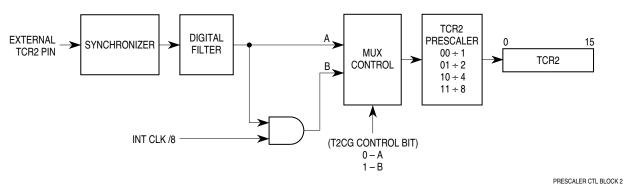

### TCR2P — Timer Count Register 2 Prescaler Control

TCR2 is clocked from the output of a prescaler. If T2CG = 0, the input to the TCR2 prescaler is the external TCR2 clock source. If T2CG = 1, the input is the TPU system clock divided by eight. The TCR2P field specifies the value of the prescaler: 1, 2, 4, or 8. Channels using TCR2 have the capability to resolve down to the TPU system clock divided by 8. The following table is a summary of prescaler output.

| TCR2 Prescaler | Divide By | Internal Clock Divided<br>By | External Clock Divided<br>By |

|----------------|-----------|------------------------------|------------------------------|

| 00             | 1         | 8                            | 1                            |

| 01             | 2         | 16                           | 2                            |

| 10             | 4         | 32                           | 4                            |

| 11             | 8         | 64                           | 8                            |

| Pin Names                              | Mnemonics  | Mode                      | Function                                                             |

|----------------------------------------|------------|---------------------------|----------------------------------------------------------------------|

| Master In Slave Out                    | MISO       | Master<br>Slave           | Serial Data Input to QSPI<br>Serial Data Output from QSPI            |

| Master Out Slave In                    | MOSI       | Master<br>Slave           | Serial Data Output from QSPI<br>Serial Data Input to QSPI            |

| Serial Clock                           | SCK        | Master<br>Slave           | Clock Output from QSPI<br>Clock Input to QSPI                        |

| Peripheral Chip Selects                | PCS[3:1]   | Master                    | Select Peripherals                                                   |

| Peripheral Chip Select<br>Slave Select | PCS0<br>SS | Master<br>Master<br>Slave | Selects Peripheral<br>Causes Mode Fault<br>Initiates Serial Transfer |

## 6.5.2 QSPI Registers

The programmer's model for the QSPI submodule consists of the QSM global and pin control registers, four QSPI control registers, one status register, and the 80-byte QSPI RAM.

The CPU can read and write to registers and RAM. The four control registers must be initialized before the QSPI is enabled to ensure defined operation. SPCR1 should be written last because it contains QSPI enable bit SPE. Asserting this bit starts the QSPI. The QSPI control registers are reset to a defined state and can then be changed by the CPU. Reset values are shown below each register.

Refer to the following memory map of the QSPI.

| Address  | Name  | Usage                          |

|----------|-------|--------------------------------|

| \$YFFC18 | SPCR0 | QSPI Control Register 0        |

| \$YFFC1A | SPCR1 | QSPI Control Register 1        |

| \$YFFC1C | SPCR2 | QSPI Control Register 2        |

| \$YFFC1E | SPCR3 | QSPI Control Register 3        |

| \$YFFC1F | SPSR  | QSPI Status Register           |

| \$YFFD00 | RAM   | QSPI Receive Data (16 Words)   |

| \$YFFD20 | RAM   | QSPI Transmit Data (16 Words)  |

| \$YFFD40 | RAM   | QSPI Command Control (8 Words) |

Writing a different value into any control register except SPCR2 while the QSPI is enabled disrupts operation. SPCR2 is buffered to prevent disruption of the current serial transfer. After completion of the current serial transfer, the new SPCR2 values become effective.

Writing the same value into any control register except SPCR2 while the QSPI is enabled has no effect on QSPI operation. Rewriting NEWQP in SPCR2 causes execution to restart at the designated location.

| SPCR0  | — QSF | PI Con | trol Re | egister | 0  |      |      |   |   |   |    |    |   | \$YF | FC18 |  |

|--------|-------|--------|---------|---------|----|------|------|---|---|---|----|----|---|------|------|--|

| 15     | 14    | 13     |         |         | 10 | 9    | 8    | 7 |   |   |    |    |   |      | 0    |  |

| MSTR   | WOMQ  |        | Bľ      | TS      |    | CPOL | CPHA |   |   |   | SP | BR |   |      |      |  |

| RESET: |       |        |         |         |    |      |      |   |   |   |    |    |   |      |      |  |

| 0      | 0     | 0      | 0       | 0       | 0  | 0    | 1    | 0 | 0 | 0 | 0  | 0  | 1 | 0    | 0    |  |

SPCR0 contains parameters for configuring the QSPI before it is enabled. The CPU can read and write this register. The QSM has read-only access.

SCK baud rate:

SCK Baud Rate = System Clock/(2SPBR)

or

SPBR = System Clock/(2SCK)(Baud Rate Desired)

where SPBR equals {2, 3, 4,..., 255}

Giving SPBR a value of zero or one disables the baud rate generator. SCK is disabled and assumes its inactive state value. No serial transfers occur. At reset, baud rate is initialized to one eighth of the system clock frequency.

|        | QU | 11001 |   | gister | • |   |   |   |   |   |   |    |   | ΨΠ |   |  |

|--------|----|-------|---|--------|---|---|---|---|---|---|---|----|---|----|---|--|

| 15     | 14 |       |   |        |   |   | 8 | 7 |   |   |   |    |   |    | 0 |  |

| SPE    |    |       |   | DSCKL  |   |   |   |   |   |   | D | TL |   |    |   |  |

| RESET: |    |       |   |        |   |   |   |   |   |   |   |    |   |    |   |  |

| 0      | 0  | 0     | 0 | 0      | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 1 | 0  | 0 |  |

SPCR1 contains parameters for configuring the QSPI before it is enabled. The CPU can read and write this register, but the QSM has read access only, except for SPE, which is automatically cleared by the QSPI after completing all serial transfers, or when a mode fault occurs.

## SPE — QSPI Enable

0 = QSPI is disabled. QSPI pins can be used for general-purpose I/O.

1 = QSPI is enabled. Pins allocated by PQSPAR are controlled by the QSPI.

### DSCKL — Delay before SCK

When the DSCK bit in command RAM is set, this field determines the length of delay from PCS valid to SCK transition. PCS can be any of the four peripheral chip-select pins. The following equation determines the actual delay before SCK:

PCS to SCK Delay = [DSCKL/System Clock]

where DSCKL equals {1, 2, 3,..., 127}.

When the DSCK value of a queue entry equals zero, then DSCKL is not used. Instead, the PCS valid-to-SCK transition is one-half SCK period.

### DTL — Length of Delay after Transfer

When the DT bit in command RAM is set, this field determines the length of delay after serial transfer. The following equation is used to calculate the delay:

Delay after Transfer = [(32DTL)/System Clock]

where DTL equals {1, 2, 3,..., 255}.

A zero value for DTL causes a delay-after-transfer value of 8192/System Clock.

If DT equals zero, a standard delay is inserted.

Standard Delay after Transfer = [17/System Clock]

Delay after transfer can be used to provide a peripheral deselect interval. A delay can also be inserted between consecutive transfers to allow serial A/D converters to complete conversion.

\$YFFC1A

#### 6.6 SCI Submodule

The SCI submodule is used to communicate with external devices through an asynchronous serial bus. The SCI is fully compatible with the SCI systems found on other Motorola MCUs, such as the M68HC11 and M68HC05 Families.

### 6.6.1 SCI Pins

There are two unidirectional pins associated with the SCI. The SCI controls the transmit data (TXD) pin when enabled, whereas the receive data (RXD) pin remains a dedicated input pin to the SCI. TXD is available as a general-purpose I/O pin when the SCI transmitter is disabled. When used for I/O, TXD can be configured either as input or output, as determined by QSM register DDRQS.

The following table shows SCI pins and their functions.

| Pin Names     | Mnemonics | Mode                                        | Function                                           |

|---------------|-----------|---------------------------------------------|----------------------------------------------------|

| Receive Data  | RXD       | Receiver Disabled<br>Receiver Enabled       | Not Used<br>Serial Data Input to SCI               |

| Transmit Data | TXD       | Transmitter Disabled<br>Transmitter Enabled | General-Purpose I/O<br>Serial Data Output from SCI |

#### 6.6.2 SCI Registers

The SCI programming model includes QSM global and pin control registers, and four SCI registers. There are two SCI control registers, one status register, and one data register. All registers can be read or written at any time by the CPU.

Changing the value of SCI control bits during a transfer operation may disrupt operation. Before changing register values, allow the transmitter to complete the current transfer, then disable the receiver and transmitter. Status flags in the SCSR may be cleared at any time.

|            | SCCR0  | — SC | I Contr | ol Reg | ister 0 | ) |   |   |   |   |   |   |   |   | \$YF | FC08 |

|------------|--------|------|---------|--------|---------|---|---|---|---|---|---|---|---|---|------|------|

|            | 15     | 14   | 13      | 12     |         |   |   |   |   |   |   |   |   |   |      | 0    |

| 0 0 0 SCBR |        |      |         |        |         |   |   |   |   |   |   |   |   |   |      |      |

|            | RESET: |      |         |        |         |   |   |   |   |   |   |   |   |   |      |      |

|            | 0      | 0    | 0       | 0      | 0       | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0    | 0    |

|            |        | _    |         |        |         |   |   |   |   |   |   |   |   |   |      |      |

SCCR0 contains a baud rate selection parameter. Baud rate must be set before the SCI is enabled. The CPU can read and write this register at any time.

#### Bits [15:13] - Not Implemented

#### SCBR — Baud Rate

SCI baud rate is programmed by writing a 13-bit value to BR. The baud rate is derived from the MCU system clock by a modulus counter.

The SCI receiver operates asynchronously. An internal clock is necessary to synchronize with an incoming data stream. The SCI baud rate generator produces a receiver sampling clock with a frequency 16 times that of the expected baud rate of the incoming data. The SCI determines the position of bit boundaries from transitions within the received waveform, and adjusts sampling points to the proper positions within the bit period. Receiver sampling rate is always 16 times the frequency of the SCI baud rate, which is calculated as follows:

SCI Baud Rate = System Clock/(32SCBR)

or

SCBR = System Clock(32SCK)(Baud Rate desired)

where SCBR is in the range {1, 2, 3, ..., 8191}

For More Information On This Product, Go to: www.freescale.com

Writing a value of zero to SCBR disables the baud rate generator.

The following table lists the SCBR settings for standard and maximum baud rates using 16.78-MHz and 20.97-MHz system clocks.

| Nominal Baud Rate | Actual Rate with<br>16.78-MHz Clock | SCBR Value | Actual Rate with 20.97-MHz Clock | SCBR Value |

|-------------------|-------------------------------------|------------|----------------------------------|------------|

| 64*               | 64.0                                | \$1FFF     | _                                | —          |

| 110               | 110.0                               | \$129E     | 110.0                            | \$1745     |

| 300               | 299.9                               | \$06D4     | 300.1                            | \$0888     |

| 600               | 599.9                               | \$036A     | 600.1                            | \$0444     |

| 1200              | 1199.7                              | \$0165     | 1200.3                           | \$0222     |

| 2400              | 2405.0                              | \$00DA     | 2400.6                           | \$0111     |

| 4800              | 4810.0                              | \$006D     | 4783.6                           | \$0089     |

| 9600              | 9532.5                              | \$0037     | 9637.6                           | \$0044     |

| 19200             | 19418.1                             | \$0016     | 19275.3                          | \$0022     |

| 38400             | 37449.1                             | \$000E     | 38550.6                          | \$0011     |

| 76800             | 74898.3                             | \$0007     | 72817.8                          | \$0009     |

| Maximum Rate      | 524288.0                            | \$0001     | 655360.0                         | \$0001     |

### Table 27 SCI Baud Rates

### SCCR1 — SCI Control Register 1

|        |       |      | •   |    |    |   |      |     |      |     |      |    |    |     |     |

|--------|-------|------|-----|----|----|---|------|-----|------|-----|------|----|----|-----|-----|

| 15     | 14    | 13   | 12  | 11 | 10 | 9 | 8    | 7   | 6    | 5   | 4    | 3  | 2  | 1   | 0   |

| 0      | LOOPS | WOMS | ILT | PT | PE | М | WAKE | TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

| RESET: |       |      |     |    |    |   |      |     |      |     |      |    |    |     |     |

| 0      | 0     | 0    | 0   | 0  | 0  | 0 | 0    | 0   | 0    | 0   | 0    | 0  | 0  | 0   | 0   |

SCCR1 contains SCI configuration parameters. The CPU can read and write this register at any time. The SCI can modify RWU in some circumstances. In general, interrupts enabled by these control bits are cleared by reading SCSR, then reading (receiver status bits) or writing (transmitter status bits) SCDR.

### Bit 15 — Not Implemented

### LOOPS - Loop Mode

- 0 = Normal SCI operation, no looping, feedback path disabled

- 1 = Test SCI operation, looping, feedback path enabled

LOOPS controls a feedback path on the data serial shifter. When loop mode is enabled, SCI transmitter output is fed back into the receive serial shifter. TXD is asserted (idle line). Both transmitter and receiver must be enabled before entering loop mode.

### WOMS — Wired-OR Mode for SCI Pins

- 0 = If configured as an output, TXD is a normal CMOS output.

- 1 = If configured as an output, TXD is an open-drain output.

WOMS determines whether the TXD pin is an open-drain output or a normal CMOS output. This bit is used only when TXD is an output. If TXD is used as a general-purpose input pin, WOMS has no effect.

### ILT — Idle-Line Detect Type

- 0 = Short idle-line detect (start count on first one)

- 1 = Long idle-line detect (start count on first one after stop bit(s))

PT — Parity Type

- 0 = Even parity

- 1 = Odd parity

When parity is enabled, PT determines whether parity is even or odd for both the receiver and the transmitter.

**\$YFFC0A**

SBK — Send Break

0 = Normal operation

1 = Break frame(s) transmitted after completion of current frame