# E·XFL

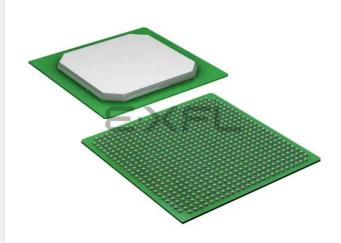

### Intel - EP4CGX110DF27C8N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | 6839                                                        |

| Number of Logic Elements/Cells | 109424                                                      |

| Total RAM Bits                 | 5621760                                                     |

| Number of I/O                  | 393                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.16V ~ 1.24V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 672-BGA                                                     |

| Supplier Device Package        | 672-FBGA (27x27)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4cgx110df27c8n |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Recommended Operating Conditions**

This section lists the functional operation limits for AC and DC parameters for Cyclone IV devices. Table 1–3and Table 1–4list the steady-state voltage and current values expected from Cyclone IV E and Cyclone IV GX devices. All supplies must be strictly monotonic without plateaus.

Table 1–3. Recommended Operating Conditions for Cyclone IV E Dévices(Part 1 of 2)

| Symbol                                | Parameter                                            | Conditions                                   | Min   | Тур | Ma    | x Un |

|---------------------------------------|------------------------------------------------------|----------------------------------------------|-------|-----|-------|------|

| V (3)                                 | Supply voltage for internal logic, 1.2-V operation   | —                                            | 1.15  | 1.2 | 1.25  | V    |

| V <sub>CCINT</sub> <sup>(3)</sup>     | Supply voltage for internal logic, 1.0-V operation   | —                                            | 0.97  | 1.0 | 1.03  | V    |

|                                       | Supply voltage for output buffers 3.3-V operation    | ·,                                           | 3.135 | 3.3 | 3.465 | V    |

|                                       | Supply voltage for output buffers 3.0-V operation    | ·,                                           | 2.85  | 3   | 3.15  | V    |

| V <sub>CCIO</sub> <sup>(3), (4)</sup> | Supply voltage for output buffers<br>2.5-V operation | ·,                                           | 2.375 | 2.5 | 2.625 | V    |

| VCCIO <sup>V</sup>                    | Supply voltage for output buffers<br>1.8-V operation | ·,                                           | 1.71  | 1.8 | 1.89  | V    |

|                                       | Supply voltage for output buffers<br>1.5-V operation | ·,                                           | 1.425 | 1.5 | 1.575 | V    |

|                                       | Supply voltage for output buffers<br>1.2-V operation | ·,                                           | 1.14  | 1.2 | 1.26  | V    |

| V <sub>CCA</sub> <sup>(3)</sup>       | Supply (analog) voltage for PLL regulator            | —                                            | 2.375 | 2.5 | 2.625 | V    |

| V <sub>CCD_PLL</sub> <sup>(3)</sup>   | Supply (digital) voltage for PLL, 1.2-V operation    | —                                            | 1.15  | 1.2 | 1.25  | V    |

|                                       | Supply (digital) voltage for PLL, 1.0-V operation    | —                                            | 0.97  | 1.0 | 1.03  | V    |

| VI                                    | Input voltage                                        | —                                            | -0.5  | _   | 3.6   | V    |

| Vo                                    | Output voltage                                       | —                                            | 0     |     | ckio  | V    |

|                                       |                                                      | For commercial use                           | 0     |     | 85    | °C   |

| TJ                                    | Operating junction temperature                       | For industrial use                           | -40   | _   | 100   | °C   |

|                                       |                                                      | For extended temperature                     | -40   | ) _ | - 12  | 5 °( |

|                                       |                                                      | For automotive use                           | -40   | _   | 125   | °C   |

| t <sub>RAMP</sub>                     | Power supply ramp time                               | Standard power-on reset (POR) <sup>(5)</sup> | 50 µs | _   | 50 ms | _    |

|                                       |                                                      | Fast POR <sup>6)</sup>                       | 50 µs | _   | 3 ms  |      |

| Symbol               | Parameter                                                      | Conditions                                    | Min   | Тур | ) Ma  | x Uni |

|----------------------|----------------------------------------------------------------|-----------------------------------------------|-------|-----|-------|-------|

| V <sub>CCA_GXB</sub> | Transceiver PMA and auxiliary power supply                     | —                                             | 2.375 | 2.5 | 2.625 | V     |

| V <sub>CCL_GXB</sub> | Transceiver PMA and auxiliary power supply                     | _                                             | 1.16  | 1.2 | 1.24  | V     |

| VI                   | DC input voltage                                               | —                                             | -0.5  | _   | 3.6   | V     |

| Vo                   | DC output voltage                                              | —                                             | 0     | _   | င၆၊၀  | V     |

| Tj                   | Operating junction tomocrature                                 | For commercial use                            | 0     | —   | 85    | °C    |

|                      | Operating junction temperature                                 | For industrial use                            | -40   | _   | 100   | °C    |

| t <sub>RAMP</sub>    | Power supply ramp time                                         | Standard poweon reset<br>(POR) <sup>(7)</sup> | 50 µs | _   | 50 ms | —     |

|                      |                                                                | Fast POR <sup>8)</sup>                        | 50 µs | —   | 3 ms  | —     |

| I <sub>Diode</sub>   | Magnitude of DC current across<br>PCI-clamp diode when enabled | _                                             | —     | _   | 10    | mA    |

Table 1-4. Recommended Operating Conditions for Cyclone IV GX Devices (Part 2 of 2)

Notes toTable 1-4

- (1) All VCCApins must be powered to 2.5 V (even when PLLs are no) taused bust be powered up approximate down at the same time.

- (2) You must connect VD PLL VCCINT through a decoupling capitor and ferrite bead.

- (3) Power supplies must rise monotonically.

- (4) V<sub>CCIO</sub> for all I/O banks must be powered up during device operation. Configurations pins are powered up full Banks 3, 8, and 9 where I/O Banks 3 and 9 only support for 1.5, 1.8, 2.5, 3.0, and 3.3 V. For pressive parallel (FPP)ndinguration mode, the VIO Bank 8 must be powered up to 1.5, 1.8, 2.5, 3.0, and 3.3 V.

- (5) You must set  $\partial_{C_{CLKIN}}$  0 2.5 V if you us@LKIN as a high-speed serial interface (HSBSU) or as aDIFFCLK input.

- (6) TheCLKIN pins in I/O Banks 3B and 8B can suppingle-ended I/O standard when the pinguaged to clock left PLIs in non-transceiver applications.

- (7) The POR time for Standard POR ranges between 50 and  $200_{IM}$  (Cloof I/O Banks 3, 8, and 9 must reach the recommended operating range within 50 ms.

- (8) The POR time for Fast POR ranges between 3 and & maxV& and CLO f I/O Banks 3, 8, and 9 must reach the recommended operating range within 3 ms.

### **ESD** Performance

This section lists the electrostatic discharge (ESD) voltages using the human body model (HBM) and charged device model (CDM) for Cyclone IV devices general purpose I/Os (GPIOs) and high-speed serial interface (HSSI) I/Os. Table 1–5lists the ESD for Cyclone IV devices GPIOs and HSSI I/Os.

| Table 1-5. | ESD for Cyclone IV Devices GPIOs and HSSI I/Os |

|------------|------------------------------------------------|

|------------|------------------------------------------------|

| Symbol              | Parameter                         | Passing Voltage | Unit |

|---------------------|-----------------------------------|-----------------|------|

| V <sub>ESDHBM</sub> | ESD voltage using the HBM (GPIØs) | ± 2000          | V    |

|                     | ESD using the HBM (HSSI I/0%)     | ± 1000          | V    |

| V <sub>ESDCDM</sub> | ESD using the CDM (GPIOs)         | ± 500           | V    |

|                     | ESD using the CDM (HSSI I/0%)     | ± 250           | V    |

### Notes toTable 1-5

(1) The passing voltage for EP4CGX30 row I/Os is ±1000V.

(2) This value is applicable yoth Cyclone IV GX devices.

The OCT resistance may vary with the variation of temperature and voltage after calibration at device power-up. Use Table 1–10and Equation 1–1 to determine the final OCT resistance considering the variations after calibration at device power-up. Table 1–10lists the change percentage of the OCT resistance with voltage and temperature.

| Nominal Voltage | dR/dT (%/°C) | dR/dV (%/mV) |

|-----------------|--------------|--------------|

| 3.0             | 0.262        | -0.026       |

| 2.5             | 0.234        | -0.039       |

| 1.8             | 0.219        | -0.086       |

| 1.5             | 0.199        | -0.136       |

| 1.2             | 0.161        | -0.288       |

Equation 1–1. Final OCT Resistante<sup>(2), (3), (4), (5), (6)</sup>

$$\label{eq:RV} \begin{split} & ^{\prime}R_V = (V_2 - V_1) \times 1000 \times dR/dV - --- \frac{(7)}{2} \\ & ^{\prime}R_T = (T_2 - T_1) \times dR/dT - --- \frac{(8)}{2} \\ & For ~^{\prime}R_x < 0; ~ MF_x = 1/~(|^{\prime}R_x|/100 + 1) - --- \frac{(9)}{2} \\ & For ~^{\prime}R_x > 0; ~ MF_x = ~^{\prime}R_x/100 + 1 - --- \frac{(10)}{2} \\ & MF = MF_7 \times MF_7 - --- \frac{(11)}{2} \\ & R_{final} = R_{nitial} \times MF - --- \frac{(12)}{2} \end{split}$$

Notes toEquation 1-1

- (1)  $T_2$  is the final temperature.

- (2)  $T_1$  is the initial temperature.

- (3) MF is multiplication factor.

- (4) R<sub>final</sub> is final resistance.

- (5) R<sub>initial</sub> is initial resistance.

- (6) Subscript refers to both and T.

- (7)  $'R_V$  is a variation of resistance with voltage.

- (8)  $'R_T$  is a variation of resistance with temperature.

- (9) dR/dT is the change percentage of resistantbetemperature after calibration at device power

- (10) dR/dV is the change percentage of rescience taken to voltage after ideal attain at device power.

(11) V<sub>2</sub> is final voltage.

(12)  $V_1$  is the initial voltage.

### Schmitt Trigger Input

Cyclone IV devices support Schmitt trigger input on the TDI, TMS TCK, nSTATUS nCONFIG, nCE, CONF\_DONE and DCLKpins. A Schmitt trigger feature introduces hysteresis to the input signal for improved noise immunity, especially for signals with slow edge rate. Table 1–14lists the hysteresis specifications across the supported V<sub>CCIO</sub> range for Schmitt trigger inputs in Cyclone IV devices.

Table 1–14. Hysteresis Specifications for Schmitt Trigger Input in Cyclone IV Devices

| Symbol   | Parameter                      | Conditions (V           | ) Minimum | Unit |

|----------|--------------------------------|-------------------------|-----------|------|

| Vschmitt |                                | V <sub>CCIO</sub> = 3.3 | 200       | mV   |

|          | Hysteresis for Schmitt trigger | V <sub>CCIO</sub> = 2.5 | 200       | mV   |

|          | input                          | V <sub>CCIO</sub> = 1.8 | 140       | mV   |

|          |                                | V <sub>CCIO</sub> = 1.5 | 110       | mV   |

## I/O Standard Specifications

The following tables list input voltage sensitivities (V  $_{IH}$  and V $_{IL}$ ), output voltage (V  $_{OH}$  and V $_{OL}$ ), and current drive characteristics (I $_{OH}$  and I $_{OL}$ ), for various I/O standards supported by Cyclone IV devices. Table 1–15through Table 1–20provide the I/O standard specifications for Cyclone IV devices.

| I/O Standard                | V <sub>ccid</sub> (V) |     | $V_{L}(V)$ |       | Y <sub>H</sub> (V)                         |                             | V <sub>6L</sub> (V)               | ν <sub>6L</sub> (V)         | bL                          | I <sub>OH</sub> |      |

|-----------------------------|-----------------------|-----|------------|-------|--------------------------------------------|-----------------------------|-----------------------------------|-----------------------------|-----------------------------|-----------------|------|

| I/O Standard                | Min Typ               | Max | Min        | Max   | Min                                        | Max                         | Max                               | Min                         | (mA)<br>(4)                 | ) (mA)<br>(4)   |      |

| 3.3-V LVTTL <sup>(3)</sup>  | 3.135                 | 3.3 | 3.465      | —     | 0.8                                        | 1.7                         | 3.6                               | 0.45                        | 2.4                         | 4               |      |

| 3.3-V LVCMO\$ <sup>3)</sup> | 3.135                 | 3.3 | 3.465      | —     | 0.8                                        | 1.7                         | 3.6                               | 0.2                         | c∂⁄o− 0.2                   | 2               | -2   |

| 3.0-V LVTTL <sup>(3)</sup>  | 2.85                  | 3.0 | 3.15       | -0.3  | 0.8                                        | 1.7                         | c∛₀+ 0.3                          | 0.45                        | 2.4                         | 4               | -4   |

| 3.0-V LVCMO\$ <sup>3)</sup> | 2.85                  | 3.0 | 3.15       | -0.3  | 0.8                                        | 1.7                         | c∛₀+ 0.3                          | 0.2                         | V <sub>CIO</sub> − 0.2      | 0.1             | -0.1 |

| 2.5 V <sup>(3)</sup>        | 2.375                 | 2.5 | 2.625      | -0.3  | 0.7                                        | 1.7                         | <sub>c</sub> ∦ <sub>O</sub> + 0.3 | 0.4                         | 2.0                         | 1               | -1   |

| 1.8 V                       | 1.71                  | 1.8 | 1.89       | -0.3  | 3 <mark>0.35 х</mark><br>V <sub>CCIO</sub> | 0.65 x<br>V <sub>CCIO</sub> | 2.25                              | 0.45                        | V <sub>CCIO</sub> -<br>0.45 | 2               | -2   |

| 1.5 V                       | 1.425                 | 1.5 | 1.575      | 5 —0. | 3 <sup>0.35 х</sup><br>V <sub>CCIO</sub>   | 0.65 x<br>V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3           | 0.25 x<br>V <sub>CCIO</sub> | 0.75 x<br>V <sub>CCIO</sub> | 2               | -2   |

| 1.2 V                       | 1.14                  | 1.2 | 1.26       | -0.3  | 3 <mark>0.35 х</mark><br>V <sub>CCIO</sub> | 0.65 x<br>V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3           | 0.25 x<br>V <sub>CCIO</sub> | 0.75 x<br>V <sub>CCIO</sub> | 2               | -2   |

| 3.0-V PCI                   | 2.85                  | 3.0 | 3.15       | 5 —   | 0.3 x<br>V <sub>CCIO</sub>                 | 0.5 x<br>V <sub>CCIO</sub>  | V <sub>CCIO</sub> + 0.3           | 0.1 x ∛ <sub>CIO</sub>      | 0.9 х У <sub>сю</sub>       | 1.5             | -0.5 |

| 3.0-V PCI-X                 | 2.85                  | 3.0 | 3.15       | 5 —   | 0.35 x<br>V <sub>CCIO</sub>                | 0.5 x<br>V <sub>CCIO</sub>  | V <sub>CCIO</sub> + 0.3           | 0.1 x ∛ <sub>CIO</sub>      | 0.9 x У <sub>сю</sub>       | 1.5             | -0.5 |

Table 1-15. SingleEnded I/O Standard Specifications for Cyclone IV Devide

Notes toTable 1–15

(1) For voltagereferenced receiver input waveformed explanation of terms used Tarble 1-15 refer to "Glossary" on page 1-37

(2) AC load CL = 10 pF

(3) For more information about interfageCyclone IV devices th 3.3/3.0/2.5/ LVTTL/LVCMOS I/O standards, refeNte47: Interfacing Cyclone III and Cyclone IV Devices with 3.3/3.0/2.5-V LVTTL/LVCMOS I/O Systems

(4) To meet theoLand bHspecifications, you must set thearrent strength settings according. For example, to meet theoLand bHspecifications, you must set thearrent strength settings according. For example, to meet theoLand bHspecifications in the handbook.