Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 3118                                                       |

| Number of Logic Elements/Cells | 49888                                                      |

| Total RAM Bits                 | 2562048                                                    |

| Number of I/O                  | 290                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.16V ~ 1.24V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 484-BGA                                                    |

| Supplier Device Package        | 484-FBGA (23x23)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4cgx50cf23c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

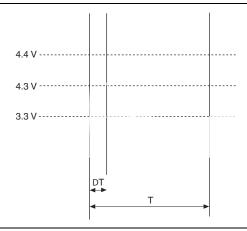

A DC signal is equivalent to 100% duty cycle. For example, a signal that overshoots to 4.3 V can only be at 4.3 V for 65% over the lifetime of the device; for a device lifetime of 10 years, this amounts to 65/10ths of a year.

Table 1–2. Maximum Allowed Overshoot During Transitions over a 10-Year Time Frame for Cyclone IV Devices

| Symbol         | Parameter           | Condition (V)         | Overshoot Duration as % of High Time | Unit |

|----------------|---------------------|-----------------------|--------------------------------------|------|

|                |                     | V <sub>I</sub> = 4.20 | 100                                  | %    |

|                |                     | V <sub>I</sub> = 4.25 | 98                                   | %    |

|                |                     | V <sub>I</sub> = 4.30 | 65                                   | %    |

|                | 40 1                | V <sub>I</sub> = 4.35 | 43                                   | %    |

| V <sub>i</sub> | AC Input<br>Voltage | V <sub>I</sub> = 4.40 | 29                                   | %    |

|                | l                   | V <sub>I</sub> = 4.45 | 20                                   | %    |

|                |                     | V <sub>I</sub> = 4.50 | 13                                   | %    |

|                |                     | V <sub>I</sub> = 4.55 | 9                                    | %    |

|                |                     | V <sub>I</sub> = 4.60 | 6                                    | %    |

Figure 1–1 shows the methodology to determine the overshoot duration. The overshoot voltage is shown in red and is present on the input pin of the Cyclone IV device at over 4.3 V but below 4.4 V. From Table 1–2, for an overshoot of 4.3 V, the percentage of high time for the overshoot can be as high as 65% over a 10-year period. Percentage of high time is calculated as ([delta T]/T)  $\times$  100. This 10-year period assumes that the device is always turned on with 100% I/O toggle rate and 50% duty cycle signal. For lower I/O toggle rates and situations in which the device is in an idle state, lifetimes are increased.

Figure 1-1. Cyclone IV Devices Overshoot Duration

# **Recommended Operating Conditions**

This section lists the functional operation limits for AC and DC parameters for Cyclone IV devices. Table 1–3 and Table 1–4 list the steady-state voltage and current values expected from Cyclone IV E and Cyclone IV GX devices. All supplies must be strictly monotonic without plateaus.

Table 1–3. Recommended Operating Conditions for Cyclone IV E Devices (1), (2) (Part 1 of 2)

| Symbol                     | Parameter                                             | Conditions                        | Min   | Тур | Max                                                                                                                               | Unit |

|----------------------------|-------------------------------------------------------|-----------------------------------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------|------|

| V <sub>CCINT</sub> (3)     | Supply voltage for internal logic,<br>1.2-V operation | _                                 | 1.15  | 1.2 | 1.25                                                                                                                              | V    |

| VCCINT 19                  | Supply voltage for internal logic,<br>1.0-V operation | _                                 | 0.97  | 1.0 | 2 1.25 0 1.03 3 3.465 3 3.15 5 2.625 8 1.89 5 1.575 2 1.26 5 2.625 2 1.25 0 1.03 - 3.6 - V <sub>CCIO</sub> - 85 - 100 - 125 - 125 | V    |

|                            | Supply voltage for output buffers, 3.3-V operation    | _                                 | 3.135 | 3.3 | 3.465                                                                                                                             | V    |

|                            | Supply voltage for output buffers, 3.0-V operation    | _                                 | 2.85  | 3   | 3.15                                                                                                                              | V    |

| V <sub>CCIO</sub> (3), (4) | Supply voltage for output buffers, 2.5-V operation    | _                                 | 2.375 | 2.5 | 2.625                                                                                                                             | V    |

| VCCIO (5% (5)              | Supply voltage for output buffers, 1.8-V operation    | _                                 | 1.71  | 1.8 | 1.89                                                                                                                              | V    |

|                            | Supply voltage for output buffers, 1.5-V operation    | _                                 | 1.425 | 1.5 | 1.575                                                                                                                             | V    |

|                            | Supply voltage for output buffers, 1.2-V operation    | _                                 | 1.14  | 1.2 | 1.26                                                                                                                              | V    |

| V <sub>CCA</sub> (3)       | Supply (analog) voltage for PLL regulator             | _                                 | 2.375 | 2.5 | 2.625                                                                                                                             | V    |

| V (3)                      | Supply (digital) voltage for PLL, 1.2-V operation     | _                                 | 1.15  | 1.2 | 1.25                                                                                                                              | V    |

| V <sub>CCD_PLL</sub> (3)   | Supply (digital) voltage for PLL, 1.0-V operation     | _                                 | 0.97  | 1.0 | 1.03                                                                                                                              | V    |

| V <sub>I</sub>             | Input voltage                                         | _                                 | -0.5  | _   | 3.6                                                                                                                               | V    |

| $V_0$                      | Output voltage                                        | _                                 | 0     | _   | V <sub>CCIO</sub>                                                                                                                 | V    |

|                            |                                                       | For commercial use                | 0     | _   |                                                                                                                                   | °C   |

| т                          | Operating junction temperature                        | For industrial use                | -40   | _   | 100                                                                                                                               | °C   |

| $T_J$                      | Operating junction temperature                        | For extended temperature          | -40   | _   | 125                                                                                                                               | °C   |

|                            |                                                       | For automotive use                | -40   | _   | 125                                                                                                                               | °C   |

| t <sub>RAMP</sub>          | Power supply ramp time                                | Standard power-on reset (POR) (5) | 50 μs | _   | 50 ms                                                                                                                             | _    |

|                            |                                                       | Fast POR (6)                      | 50 μs | _   | 3 ms                                                                                                                              | _    |

Table 1–3. Recommended Operating Conditions for Cyclone IV E Devices (1), (2) (Part 2 of 2)

| Symbol             | Parameter                                                     | Conditions | Min | Тур | Max | Unit |

|--------------------|---------------------------------------------------------------|------------|-----|-----|-----|------|

| I <sub>Diode</sub> | Magnitude of DC current across<br>PCI-clamp diode when enable | _          | _   | _   | 10  | mA   |

## Notes to Table 1-3:

- (1) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades.

- (2) V<sub>CCIO</sub> for all I/O banks must be powered up during device operation. All VCCA pins must be powered to 2.5 V (even when PLLs are not used) and must be powered up and powered down at the same time.

- (3) V<sub>CC</sub> must rise monotonically.

- (4)  $V_{CCIO}$  powers all input buffers.

- (5) The POR time for Standard POR ranges between 50 and 200 ms. Each individual power supply must reach the recommended operating range within 50 ms.

- (6) The POR time for Fast POR ranges between 3 and 9 ms. Each individual power supply must reach the recommended operating range within 3 ms.

Table 1-4. Recommended Operating Conditions for Cyclone IV GX Devices (Part 1 of 2)

| Symbol                     | Parameter                                                          | Conditions | Min   | Тур | Max   | Unit |

|----------------------------|--------------------------------------------------------------------|------------|-------|-----|-------|------|

| V <sub>CCINT</sub> (3)     | Core voltage, PCIe hard IP block, and transceiver PCS power supply | _          | 1.16  | 1.2 | 1.24  | V    |

| V <sub>CCA</sub> (1), (3)  | PLL analog power supply                                            | _          | 2.375 | 2.5 | 2.625 | V    |

| V <sub>CCD_PLL</sub> (2)   | PLL digital power supply                                           | _          | 1.16  | 1.2 | 1.24  | V    |

|                            | I/O banks power supply for 3.3-V operation                         | _          | 3.135 | 3.3 | 3.465 | V    |

|                            | I/O banks power supply for 3.0-V operation                         | _          | 2.85  | 3   | 3.15  | V    |

| V <sub>CCIO</sub> (3), (4) | I/O banks power supply for 2.5-V operation                         | _          | 2.375 | 2.5 | 2.625 | V    |

| vccio (2)                  | I/O banks power supply for 1.8-V operation                         | _          | 1.71  | 1.8 | 1.89  | V    |

|                            | I/O banks power supply for 1.5-V operation                         | _          | 1.425 | 1.5 | 1.575 | V    |

|                            | I/O banks power supply for 1.2-V operation                         | _          | 1.14  | 1.2 | 1.26  | V    |

|                            | Differential clock input pins power supply for 3.3-V operation     | _          | 3.135 | 3.3 | 3.465 | V    |

|                            | Differential clock input pins power supply for 3.0-V operation     | _          | 2.85  | 3   | 3.15  | V    |

| V <sub>CC_CLKIN</sub>      | Differential clock input pins power supply for 2.5-V operation     | _          | 2.375 | 2.5 | 2.625 | V    |

| (3), (5), (6)              | Differential clock input pins power supply for 1.8-V operation     | _          | 1.71  | 1.8 | 1.89  | V    |

|                            | Differential clock input pins power supply for 1.5-V operation     | _          | 1.425 | 1.5 | 1.575 | V    |

|                            | Differential clock input pins power supply for 1.2-V operation     | _          | 1.14  | 1.2 | 1.26  | V    |

| $V_{\text{CCH\_GXB}}$      | Transceiver output buffer power supply                             | _          | 2.375 | 2.5 | 2.625 | V    |

The OCT resistance may vary with the variation of temperature and voltage after calibration at device power-up. Use Table 1–10 and Equation 1–1 to determine the final OCT resistance considering the variations after calibration at device power-up. Table 1–10 lists the change percentage of the OCT resistance with voltage and temperature.

Table 1–10. OCT Variation After Calibration at Device Power-Up for Cyclone IV Devices

| Nominal Voltage | dR/dT (%/°C) | dR/dV (%/mV) |

|-----------------|--------------|--------------|

| 3.0             | 0.262        | -0.026       |

| 2.5             | 0.234        | -0.039       |

| 1.8             | 0.219        | -0.086       |

| 1.5             | 0.199        | -0.136       |

| 1.2             | 0.161        | -0.288       |

# Equation 1-1. Final OCT Resistance (1), (2), (3), (4), (5), (6)

#### Notes to Equation 1-1:

- (1)  $T_2$  is the final temperature.

- (2)  $T_1$  is the initial temperature.

- (3) MF is multiplication factor.

- (4) R<sub>final</sub> is final resistance.

- (5) R<sub>initial</sub> is initial resistance.

- (6) Subscript  $_{\rm X}$  refers to both  $_{\rm V}$  and  $_{\rm T}$ .

- (7)  $\Delta R_V$  is a variation of resistance with voltage.

- (8)  $\Delta R_T$  is a variation of resistance with temperature.

- (9) dR/dT is the change percentage of resistance with temperature after calibration at device power-up.

- (10) dR/dV is the change percentage of resistance with voltage after calibration at device power-up.

- (11) V2 is final voltage.

- (12)  $V_1$  is the initial voltage.

For more information about receiver input and transmitter output waveforms, and for other differential I/O standards, refer to the I/O Features in Cyclone IV Devices chapter.

Table 1–18. Differential SSTL I/O Standard Specifications for Cyclone IV Devices (1)

| I/O Standard           | V     | <sub>CC10</sub> (V | <b>'</b> ) | V <sub>Swing</sub> | <sub>J(DC)</sub> (V) | V <sub>X(AC)</sub> (V)       |     |                                 | V <sub>Swi</sub> | ng(AC)<br><b>/)</b> | V <sub>ox</sub>                 | <sub>(AC)</sub> (V) |                                 |

|------------------------|-------|--------------------|------------|--------------------|----------------------|------------------------------|-----|---------------------------------|------------------|---------------------|---------------------------------|---------------------|---------------------------------|

|                        | Min   | Тур                | Max        | Min                | Max                  | Min                          | Тур | Max                             | Min              | Max                 | Min                             | Тур                 | Max                             |

| SSTL-2<br>Class I, II  | 2.375 | 2.5                | 2.625      | 0.36               | V <sub>CCIO</sub>    | V <sub>CCIO</sub> /2 - 0.2   | _   | V <sub>CCIO</sub> /2<br>+ 0.2   | 0.7              | V <sub>CCI</sub>    | V <sub>CCIO</sub> /2 -<br>0.125 | _                   | V <sub>CCIO</sub> /2<br>+ 0.125 |

| SSTL-18<br>Class I, II | 1.7   | 1.8                | 1.90       | 0.25               | V <sub>CCIO</sub>    | V <sub>CCIO</sub> /2 - 0.175 | _   | V <sub>CCIO</sub> /2<br>+ 0.175 | 0.5              | V <sub>CCI</sub>    | V <sub>CCIO</sub> /2 - 0.125    | _                   | V <sub>CCIO</sub> /2<br>+ 0.125 |

#### Note to Table 1-18:

Table 1–19. Differential HSTL I/O Standard Specifications for Cyclone IV Devices (1)

|                        | V <sub>CCIO</sub> (V) |     |       | V <sub>DIF(DC)</sub> (V) |                   | V <sub>X(AC)</sub> (V)   |     |                             | V <sub>CM(DC)</sub> (V)     |     |                             |         | V <sub>DIF(AC)</sub> (V)    |  |

|------------------------|-----------------------|-----|-------|--------------------------|-------------------|--------------------------|-----|-----------------------------|-----------------------------|-----|-----------------------------|---------|-----------------------------|--|

| I/O Standard           | Min                   | Тур | Max   | Min                      | Max               | Min                      | Тур | Max                         | Min                         | Тур | Max                         | Mi<br>n | Max                         |  |

| HSTL-18<br>Class I, II | 1.71                  | 1.8 | 1.89  | 0.2                      | _                 | 0.85                     |     | 0.95                        | 0.85                        | _   | 0.95                        | 0.4     | _                           |  |

| HSTL-15<br>Class I, II | 1.425                 | 1.5 | 1.575 | 0.2                      | _                 | 0.71                     |     | 0.79                        | 0.71                        | _   | 0.79                        | 0.4     | _                           |  |

| HSTL-12<br>Class I, II | 1.14                  | 1.2 | 1.26  | 0.16                     | V <sub>CCIO</sub> | 0.48 x V <sub>CCIO</sub> |     | 0.52 x<br>V <sub>CCIO</sub> | 0.48 x<br>V <sub>CCIO</sub> |     | 0.52 x<br>V <sub>CCIO</sub> | 0.3     | 0.48 x<br>V <sub>CCIO</sub> |  |

#### Note to Table 1-19:

Table 1–20. Differential I/O Standard Specifications for Cyclone IV Devices (1) (Part 1 of 2)

| I/O Standard                   |       | V <sub>CCIO</sub> (V) |       | V <sub>ID</sub> | (mV) |              | V <sub>ICM</sub> (V) <sup>(2)</sup>                                                                 |      | Vo  | <sub>D</sub> (mV) | (3) | V <sub>0S</sub> (V) <sup>(3)</sup> |      |       |

|--------------------------------|-------|-----------------------|-------|-----------------|------|--------------|-----------------------------------------------------------------------------------------------------|------|-----|-------------------|-----|------------------------------------|------|-------|

| i/O Stanuaru                   | Min   | Тур                   | Max   | Min             | Max  | Min          | Min Condition N                                                                                     |      | Min | Тур               | Max | Min                                | Тур  | Max   |

| L) (DEOL                       |       |                       |       |                 |      | 0.05         | $D_{MAX} \leq 500 \; Mbps$                                                                          | 1.80 |     |                   |     |                                    |      |       |

| LVPECL<br>(Row I/Os)           | 2.375 | 2.5                   | 2.625 | 100             | _    | 500 Mbps < D |                                                                                                     | 1.80 | _   | _                 |     | _                                  | _    | _     |

|                                |       |                       |       |                 |      | 1.05         | D <sub>MAX</sub> > 700 Mbps                                                                         | 1.55 |     |                   |     |                                    |      |       |

| IV/DEOL                        |       |                       |       |                 |      | 0.05         | $D_{MAX} \leq 500 \text{ Mbps}$                                                                     | 1.80 |     |                   |     |                                    |      |       |

| LVPECL<br>(Column<br>I/Os) (6) | 2.375 | 2.5                   | 2.625 | 100             | _    | 0.55         | $\begin{array}{l} 500 \; \text{Mbps} \leq D_{\text{MAX}} \\ \leq 700 \; \text{Mbps} \end{array}$    | 1.80 | _   | _                 | _   | _                                  | _    | _     |

| 1,00)                          |       |                       |       |                 |      | 1.05         | D <sub>MAX</sub> > 700 Mbps                                                                         | 1.55 |     |                   |     |                                    |      |       |

|                                |       |                       |       |                 |      | 0.05         | $D_{MAX} \leq 500 \; Mbps$                                                                          | 1.80 |     |                   |     |                                    |      |       |

| LVDS (Row<br>I/Os)             | 2.375 | 2.5                   | 2.625 | 100             | _    | 0.55         | $\begin{array}{l} 500 \; \text{Mbps} \leq D_{\text{MAX}} \\ \leq \; 700 \; \text{Mbps} \end{array}$ | 1.80 | 247 | _                 | 600 | 1.125                              | 1.25 | 1.375 |

|                                |       |                       |       |                 |      | 1.05         | D <sub>MAX</sub> > 700 Mbps                                                                         | 1.55 |     |                   |     |                                    |      |       |

<sup>(1)</sup> Differential SSTL requires a  $V_{\text{REF}}$  input.

<sup>(1)</sup> Differential HSTL requires a  $V_{\text{REF}}$  input.

# **Power Consumption**

Use the following methods to estimate power for a design:

- the Excel-based EPE

- the Quartus® II PowerPlay power analyzer feature

The interactive Excel-based EPE is used prior to designing the device to get a magnitude estimate of the device power. The Quartus II PowerPlay power analyzer provides better quality estimates based on the specifics of the design after place-and-route is complete. The PowerPlay power analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, combined with detailed circuit models, can yield very accurate power estimates.

For more information about power estimation tools, refer to the *Early Power Estimator User Guide* and the *PowerPlay Power Analysis* chapter in volume 3 of the *Quartus II Handbook*.

# **Switching Characteristics**

This section provides performance characteristics of Cyclone IV core and periphery blocks for commercial grade devices.

These characteristics can be designated as Preliminary or Final.

- Preliminary characteristics are created using simulation results, process data, and other known parameters. The upper-right hand corner of these tables show the designation as "Preliminary".

- Final numbers are based on actual silicon characterization and testing. The numbers reflect the actual performance of the device under worst-case silicon process, voltage, and junction temperature conditions. There are no designations on finalized tables.

Table 1–21. Transceiver Specification for Cyclone IV GX Devices (Part 2 of 4)

| Symbol/                                                                                        | Oanditions                                                                     |      | C6           |                               |        | C7, I7                 |                                  |      | lleit        |                                  |      |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|--------------|-------------------------------|--------|------------------------|----------------------------------|------|--------------|----------------------------------|------|

| Description                                                                                    | Conditions                                                                     | Min  | Тур          | Max                           | Min    | Тур                    | Max                              | Min  | Тур          | Max                              | Unit |

| Receiver                                                                                       |                                                                                |      | •            |                               |        |                        | •                                |      |              | <u> </u>                         |      |

| Supported I/O<br>Standards                                                                     | 1.4 V PCML,<br>1.5 V PCML,<br>2.5 V PCML,<br>LVPECL, LVDS                      |      |              |                               |        |                        |                                  |      |              |                                  |      |

| Data rate (F324 and smaller package) (15)                                                      | _                                                                              | 600  | _            | 2500                          | 600    | _                      | 2500                             | 600  | _            | 2500                             | Mbps |

| Data rate (F484 and larger package) (15)                                                       | _                                                                              | 600  | _            | 3125                          | 600    | _                      | 3125                             | 600  | _            | 2500                             | Mbps |

| Absolute V <sub>MAX</sub> for a receiver pin (3)                                               | _                                                                              | _    | _            | 1.6                           | _      | _                      | 1.6                              | _    | _            | 1.6                              | V    |

| Operational V <sub>MAX</sub> for a receiver pin                                                | _                                                                              | _    | _            | 1.5                           | _      | _                      | 1.5                              | _    | _            | 1.5                              | V    |

| Absolute V <sub>MIN</sub> for a receiver pin                                                   | _                                                                              | -0.4 | _            | _                             | -0.4   | _                      | _                                | -0.4 | _            | _                                | V    |

| Peak-to-peak<br>differential input<br>voltage V <sub>ID</sub> (diff p-p)                       | V <sub>ICM</sub> = 0.82 V<br>setting, Data Rate<br>= 600 Mbps to<br>3.125 Gbps | 0.1  | _            | 2.7                           | 0.1    | _                      | 2.7                              | 0.1  | _            | 2.7                              | V    |

| V <sub>ICM</sub>                                                                               | V <sub>ICM</sub> = 0.82 V<br>setting                                           | _    | 820 ±<br>10% | _                             | _      | 820 ±<br>10%           | _                                | _    | 820 ±<br>10% | _                                | mV   |

| Differential on-chip                                                                           | 100–Ω setting                                                                  | _    | 100          | _                             | _      | 100                    | _                                | _    | 100          | _                                | Ω    |

| termination resistors                                                                          | 150– $\Omega$ setting                                                          | _    | 150          | _                             | _      | 150                    | _                                | _    | 150          | _                                | Ω    |

| Differential and common mode return loss                                                       | PIPE, Serial<br>Rapid I/O SR,<br>SATA, CPRI LV,<br>SDI, XAUI                   |      |              |                               |        | Compliant              | i                                |      |              |                                  | _    |

| Programmable ppm detector <sup>(4)</sup>                                                       | _                                                                              |      |              |                               | ± 62.5 | , 100, 125<br>250, 300 | 5, 200,                          |      |              |                                  | ppm  |

| Clock data recovery<br>(CDR) ppm<br>tolerance (without<br>spread-spectrum<br>clocking enabled) | _                                                                              |      | _            | ±300 (5),<br>±350<br>(6), (7) |        | _                      | ±300<br>(5),<br>±350<br>(6), (7) | _    | _            | ±300<br>(5),<br>±350<br>(6), (7) | ppm  |

| CDR ppm tolerance<br>(with synchronous<br>spread-spectrum<br>clocking enabled) (8)             | _                                                                              | _    | _            | 350 to<br>-5350<br>(7), (9)   | _      | _                      | 350 to<br>-5350<br>(7), (9)      | _    | _            | 350 to<br>-5350<br>(7), (9)      | ppm  |

| Run length                                                                                     | _                                                                              |      | 80           | _                             | _      | 80                     | _                                |      | 80           |                                  | UI   |

|                                                                                                | No Equalization                                                                | _    | _            | 1.5                           | _      | _                      | 1.5                              | _    | _            | 1.5                              | dB   |

| Programmable                                                                                   | Medium Low                                                                     | _    | _            | 4.5                           | _      | _                      | 4.5                              |      | _            | 4.5                              | dB   |

| equalization                                                                                   | Medium High                                                                    | _    | _            | 5.5                           | _      | _                      | 5.5                              |      | _            | 5.5                              | dB   |

|                                                                                                | High                                                                           | _    | _            | 7                             | _      | _                      | 7                                | _    |              | 7                                | dB   |

Table 1–21. Transceiver Specification for Cyclone IV GX Devices (Part 3 of 4)

| Symbol/                                                        | 0 1111                                                       |     | C6  |       |     | C7, I7   |       |     |     |       |                                |

|----------------------------------------------------------------|--------------------------------------------------------------|-----|-----|-------|-----|----------|-------|-----|-----|-------|--------------------------------|

| Description                                                    | Conditions                                                   | Min | Тур | Max   | Min | Тур      | Max   | Min | Тур | Max   | Unit                           |

| Signal detect/loss threshold                                   | PIPE mode                                                    | 65  | _   | 175   | 65  | _        | 175   | 65  | _   | 175   | mV                             |

| t <sub>LTR</sub> (10)                                          | _                                                            | _   | _   | 75    | _   | _        | 75    | _   | _   | 75    | μs                             |

| t <sub>LTR-LTD_Manual</sub> (11)                               | _                                                            | 15  | _   | _     | 15  | _        | _     | 15  | _   | _     | μs                             |

| t <sub>LTD</sub> (12)                                          | _                                                            | 0   | 100 | 4000  | 0   | 100      | 4000  | 0   | 100 | 4000  | ns                             |

| t <sub>LTD_Manual</sub> (13)                                   | _                                                            |     | _   | 4000  | _   |          | 4000  | _   |     | 4000  | ns                             |

| t <sub>LTD_Auto</sub> (14)                                     | _                                                            |     | _   | 4000  | _   |          | 4000  | _   |     | 4000  | ns                             |

| Receiver buffer and CDR offset cancellation time (per channel) | _                                                            |     | _   | 17000 | _   | _        | 17000 | _   | _   | 17000 | recon<br>fig_c<br>lk<br>cycles |

|                                                                | DC Gain Setting = 0                                          | _   | 0   | _     | _   | 0        | _     | _   | 0   | _     | dB                             |

| Programmable DC gain                                           | DC Gain Setting = 1                                          | _   | 3   | _     | _   | 3        | _     | _   | 3   | _     | dB                             |

|                                                                | DC Gain Setting = 2                                          | _   | 6   | _     | _   | 6        | _     | _   | 6   | _     | dB                             |

| Transmitter                                                    |                                                              |     |     |       |     |          |       |     |     |       |                                |

| Supported I/O<br>Standards                                     | 1.5 V PCML                                                   |     |     |       |     |          |       |     |     |       |                                |

| Data rate (F324 and smaller package)                           | _                                                            | 600 | _   | 2500  | 600 | _        | 2500  | 600 | _   | 2500  | Mbps                           |

| Data rate (F484 and larger package)                            | _                                                            | 600 | _   | 3125  | 600 | _        | 3125  | 600 | _   | 2500  | Mbps                           |

| V <sub>OCM</sub>                                               | 0.65 V setting                                               | _   | 650 | _     | _   | 650      | _     | _   | 650 | _     | mV                             |

| Differential on-chip                                           | 100–Ω setting                                                | _   | 100 | _     | _   | 100      | _     | _   | 100 | _     | Ω                              |

| termination resistors                                          | 150– $\Omega$ setting                                        | _   | 150 | _     | _   | 150      | _     | _   | 150 | _     | Ω                              |

| Differential and common mode return loss                       | PIPE, CPRI LV,<br>Serial Rapid I/O<br>SR, SDI, XAUI,<br>SATA |     |     |       |     | Complian | į     |     |     | ,     | _                              |

| Rise time                                                      | _                                                            | 50  | _   | 200   | 50  | _        | 200   | 50  | _   | 200   | ps                             |

| Fall time                                                      | _                                                            | 50  | _   | 200   | 50  | _        | 200   | 50  | _   | 200   | ps                             |

| Intra-differential pair<br>skew                                | _                                                            | _   | _   | 15    | _   | _        | 15    | _   | _   | 15    | ps                             |

| Intra-transceiver<br>block skew                                | _                                                            | _   | _   | 120   | _   | _        | 120   | _   | _   | 120   | ps                             |

Table 1–21. Transceiver Specification for Cyclone IV GX Devices (Part 4 of 4)

| Symbol/                                          | Conditions                |     | C6                                 |        |     | C7, I7 |        |     | C8  |        |      |  |

|--------------------------------------------------|---------------------------|-----|------------------------------------|--------|-----|--------|--------|-----|-----|--------|------|--|

| Description                                      | Conuntions                | Min | Тур                                | Max    | Min | Тур    | Max    | Min | Тур | Max    | Unit |  |

| PLD-Transceiver Inte                             | PLD-Transceiver Interface |     |                                    |        |     |        |        |     |     |        |      |  |

| Interface speed<br>(F324 and smaller<br>package) | _                         | 25  | _                                  | 125    | 25  | _      | 125    | 25  | _   | 125    | MHz  |  |

| Interface speed<br>(F484 and larger<br>package)  | _                         | 25  | _                                  | 156.25 | 25  | _      | 156.25 | 25  | _   | 156.25 | MHz  |  |

| Digital reset pulse width                        | _                         |     | Minimum is 2 parallel clock cycles |        |     |        |        |     |     |        |      |  |

#### Notes to Table 1-21:

- (1) This specification is valid for transmitter output jitter specification with a maximum total jitter value of 112 ps, typically for 3.125 Gbps SRIO and XAUI protocols.

- (2) The minimum reconfig\_clk frequency is 2.5 MHz if the transceiver channel is configured in **Transmitter Only** mode. The minimum reconfig\_clk frequency is 37.5 MHz if the transceiver channel is configured in **Receiver Only** or **Receiver and Transmitter** mode.

- (3) The device cannot tolerate prolonged operation at this absolute maximum.

- (4) The rate matcher supports only up to ±300 parts per million (ppm).

- (5) Supported for the F169 and F324 device packages only.

- (6) Supported for the F484, F672, and F896 device packages only. Pending device characterization.

- (7) To support CDR ppm tolerance greater than ±300 ppm, implement ppm detector in user logic and configure CDR to Manual Lock Mode.

- (8) Asynchronous spread-spectrum clocking is not supported.

- (9) For the EP4CGX30 (F484 package only), EP4CGX50, and EP4CGX75 devices, the CDR ppl tolerance is ±200 ppm.

- (10) Time taken until pll locked goes high after pll powerdown deasserts.

- (11) Time that the CDR must be kept in lock-to-reference mode after rx analogreset deasserts and before rx locktodata is asserted in manual mode.

- (12) Time taken to recover valid data after the rx\_locktodata signal is asserted in manual mode (Figure 1–2), or after rx\_freqlocked signal goes high in automatic mode (Figure 1–3).

- (13) Time taken to recover valid data after the  $rx\_locktodata$  signal is asserted in manual mode.

- (14) Time taken to recover valid data after the  $rx\_freqlocked$  signal goes high in automatic mode.

- (15) To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

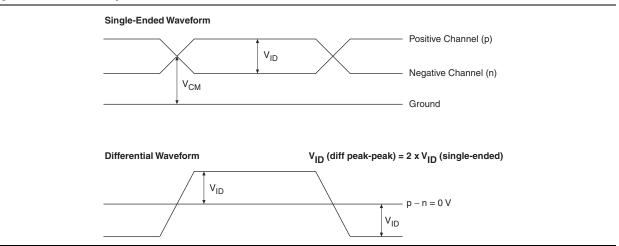

Figure 1–4 shows the differential receiver input waveform.

Figure 1-4. Receiver Input Waveform

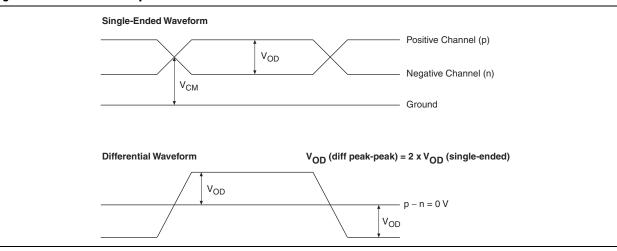

Figure 1–5 shows the transmitter output waveform.

Figure 1-5. Transmitter Output Waveform

Table 1–22 lists the typical  $V_{\text{OD}}$  for Tx term that equals 100  $\Omega$ .

Table 1–22. Typical  $\text{V}_{\text{OD}}$  Setting, Tx Term = 100  $\Omega$

| Cumbal                                                    |     |     | V <sub>op</sub> Sett | ing (mV)     |      |      |

|-----------------------------------------------------------|-----|-----|----------------------|--------------|------|------|

| Symbol                                                    | 1   | 2   | 3                    | <b>4</b> (1) | 5    | 6    |

| V <sub>OD</sub> differential peak<br>to peak typical (mV) | 400 | 600 | 800                  | 900          | 1000 | 1200 |

#### Note to Table 1-22:

(1) This setting is required for compliance with the PCle protocol.

| Davisa    |     |            |     | Perfor  | mance   |       |         |    | 11!4 |

|-----------|-----|------------|-----|---------|---------|-------|---------|----|------|

| Device    | C6  | <b>C</b> 7 | C8  | C8L (1) | C9L (1) | 17    | I8L (1) | A7 | Unit |

| EP4CE55   | 500 | 437.5      | 402 | 362     | 265     | 437.5 | 362     | _  | MHz  |

| EP4CE75   | 500 | 437.5      | 402 | 362     | 265     | 437.5 | 362     | _  | MHz  |

| EP4CE115  | _   | 437.5      | 402 | 362     | 265     | 437.5 | 362     | _  | MHz  |

| EP4CGX15  | 500 | 437.5      | 402 | _       | _       | 437.5 | _       | _  | MHz  |

| EP4CGX22  | 500 | 437.5      | 402 | _       | _       | 437.5 | _       | _  | MHz  |

| EP4CGX30  | 500 | 437.5      | 402 | _       | _       | 437.5 | _       | _  | MHz  |

| EP4CGX50  | 500 | 437.5      | 402 | _       | _       | 437.5 | _       | _  | MHz  |

| EP4CGX75  | 500 | 437.5      | 402 | _       | _       | 437.5 | _       | _  | MHz  |

| EP4CGX110 | 500 | 437.5      | 402 | _       | _       | 437.5 | _       | _  | MHz  |

| EP4CGX150 | 500 | 437.5      | 402 | _       | _       | 437.5 | _       | _  | MHz  |

#### Note to Table 1-24:

# **PLL Specifications**

Table 1–25 lists the PLL specifications for Cyclone IV devices when operating in the commercial junction temperature range (0°C to 85°C), the industrial junction temperature range (-40°C to 100°C), the extended industrial junction temperature range (-40°C to 125°C), and the automotive junction temperature range (-40°C to 125°C). For more information about the PLL block, refer to "Glossary" on page 1–37.

Table 1–25. PLL Specifications for Cyclone IV Devices (1), (2) (Part 1 of 2)

| Symbol                                           | Parameter                                                    | Min | Тур | Max   | Unit |

|--------------------------------------------------|--------------------------------------------------------------|-----|-----|-------|------|

|                                                  | Input clock frequency (-6, -7, -8 speed grades)              | 5   | _   | 472.5 | MHz  |

| f <sub>IN</sub> (3)                              | Input clock frequency (-8L speed grade)                      | 5   | _   | 362   | MHz  |

|                                                  | Input clock frequency (-9L speed grade)                      | 5   | _   | 265   | MHz  |

| f <sub>INPFD</sub>                               | PFD input frequency                                          | 5   | _   | 325   | MHz  |

| f <sub>VCO</sub> (4)                             | PLL internal VCO operating range                             | 600 | _   | 1300  | MHz  |

| f <sub>INDUTY</sub>                              | Input clock duty cycle                                       | 40  | _   | 60    | %    |

| t <sub>INJITTER_CCJ</sub> (5)                    | Input clock cycle-to-cycle jitter F <sub>REF</sub> ≥ 100 MHz | _   | _   | 0.15  | UI   |

|                                                  | F <sub>REF</sub> < 100 MHz                                   | _   | _   | ±750  | ps   |

| f <sub>OUT_EXT</sub> (external clock output) (3) | PLL output frequency                                         | _   | _   | 472.5 | MHz  |

|                                                  | PLL output frequency (-6 speed grade)                        | _   | _   | 472.5 | MHz  |

|                                                  | PLL output frequency (-7 speed grade)                        | _   | _   | 450   | MHz  |

| f <sub>OUT</sub> (to global clock)               | PLL output frequency (-8 speed grade)                        | _   | _   | 402.5 | MHz  |

|                                                  | PLL output frequency (-8L speed grade)                       | _   | _   | 362   | MHz  |

|                                                  | PLL output frequency (-9L speed grade)                       | _   | _   | 265   | MHz  |

| toutduty                                         | Duty cycle for external clock output (when set to 50%)       | 45  | 50  | 55    | %    |

| t <sub>LOCK</sub>                                | Time required to lock from end of device configuration       | _   | _   | 1     | ms   |

<sup>(1)</sup> Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades.

Table 1–29 lists the active configuration mode specifications for Cyclone IV devices.

Table 1–29. Active Configuration Mode Specifications for Cyclone IV Devices

| Programming Mode         | DCLK Range | Typical DCLK | Unit |

|--------------------------|------------|--------------|------|

| Active Parallel (AP) (1) | 20 to 40   | 33           | MHz  |

| Active Serial (AS)       | 20 to 40   | 33           | MHz  |

#### Note to Table 1-29:

(1) AP configuration mode is only supported for Cyclone IV E devices.

Table 1–30 lists the JTAG timing parameters and values for Cyclone IV devices.

Table 1–30. JTAG Timing Parameters for Cyclone IV Devices (1)

| Symbol                | Parameter                                         | Min | Max | Unit |

|-----------------------|---------------------------------------------------|-----|-----|------|

| t <sub>JCP</sub>      | TCK clock period                                  | 40  | _   | ns   |

| t <sub>JCH</sub>      | TCK clock high time                               | 19  | _   | ns   |

| t <sub>JCL</sub>      | TCK clock low time                                | 19  | _   | ns   |

| t <sub>JPSU_TDI</sub> | JTAG port setup time for TDI                      | 1   | _   | ns   |

| t <sub>JPSU_TMS</sub> | JTAG port setup time for TMS                      | 3   | _   | ns   |

| $t_{JPH}$             | JTAG port hold time                               | 10  | _   | ns   |

| t <sub>JPCO</sub>     | JTAG port clock to output (2), (3)                | _   | 15  | ns   |

| t <sub>JPZX</sub>     | JTAG port high impedance to valid output (2), (3) | _   | 15  | ns   |

| t <sub>JPXZ</sub>     | JTAG port valid output to high impedance (2), (3) | _   | 15  | ns   |

| t <sub>JSSU</sub>     | Capture register setup time                       | 5   | _   | ns   |

| t <sub>JSH</sub>      | Capture register hold time                        | 10  | _   | ns   |

| t <sub>JSCO</sub>     | Update register clock to output                   | _   | 25  | ns   |

| t <sub>JSZX</sub>     | Update register high impedance to valid output    | _   | 25  | ns   |

| t <sub>JSXZ</sub>     | Update register valid output to high impedance    |     | 25  | ns   |

#### Notes to Table 1-30:

- (1) For more information about JTAG waveforms, refer to "JTAG Waveform" in "Glossary" on page 1-37.

- (2) The specification is shown for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 16 ns.

- (3) For EP4CGX22, EP4CGX30 (F324 and smaller package), EP4CGX110, and EP4CGX150 devices, the output time specification for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins is 16 ns. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 18 ns.

# **Periphery Performance**

This section describes periphery performance, including high-speed I/O and external memory interface.

I/O performance supports several system interfaces, such as the high-speed I/O interface, external memory interface, and the PCI/PCI-X bus interface. I/Os using the SSTL-18 Class I termination standard can achieve up to the stated DDR2 SDRAM interfacing speeds. I/Os using general-purpose I/O standards such as 3.3-, 3.0-, 2.5-, 1.8-, or 1.5-LVTTL/LVCMOS are capable of a typical 200 MHz interfacing frequency with a 10 pF load.

Table 1–31. RSDS Transmitter Timing Specifications for Cyclone IV Devices (1), (2), (4) (Part 2 of 2)

| Symbol                | Modes |     | C6  |     |     | C7, I | 7   |     | C8, A | 7   |     | C8L, I | BL  |     | C9L |     | Unit |

|-----------------------|-------|-----|-----|-----|-----|-------|-----|-----|-------|-----|-----|--------|-----|-----|-----|-----|------|

| Syllibul              | Mones | Min | Тур | Max | Min | Тур   | Max | Min | Тур   | Max | Min | Тур    | Max | Min | Тур | Max | Unit |

| t <sub>LOCK</sub> (3) | _     | _   |     | 1   | _   | _     | 1   | _   |       | 1   | _   | _      | 1   | _   |     | 1   | ms   |

#### Notes to Table 1-31:

- (1) Applicable for true RSDS and emulated RSDS\_E\_3R transmitter.

- (2) Cyclone IV E devices—true RSDS transmitter is only supported at the output pin of Row I/O Banks 1, 2, 5, and 6. Emulated RSDS transmitter is supported at the output pin of all I/O Banks.

Cyclone IV GX devices—true RSDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of I/O Banks 3, 4, 5, 6, 7, 8, and 9.

- (3)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

- (4) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

Table 1–32. Emulated RSDS\_E\_1R Transmitter Timing Specifications for Cyclone IV Devices (1), (3) (Part 1 of 2)

| Ob.al                              | Madaa                    |     | C6  |     |     | C7, 17 | '   |     | C8, A7 | 7   | (   | C8L, 18 | BL  |     | C9L |      | 11!4 |

|------------------------------------|--------------------------|-----|-----|-----|-----|--------|-----|-----|--------|-----|-----|---------|-----|-----|-----|------|------|

| Symbol                             | Modes                    | Min | Тур | Max | Min | Тур    | Max | Min | Тур    | Max | Min | Тур     | Max | Min | Тур | Max  | Unit |

|                                    | ×10                      | 5   | _   | 85  | 5   |        | 85  | 5   |        | 85  | 5   |         | 85  | 5   | _   | 72.5 | MHz  |

|                                    | ×8                       | 5   | _   | 85  | 5   | _      | 85  | 5   | _      | 85  | 5   |         | 85  | 5   | _   | 72.5 | MHz  |

| f <sub>HSCLK</sub> (input<br>clock | ×7                       | 5   | _   | 85  | 5   | _      | 85  | 5   | _      | 85  | 5   | _       | 85  | 5   | _   | 72.5 | MHz  |

| frequency)                         | ×4                       | 5   | _   | 85  | 5   | _      | 85  | 5   |        | 85  | 5   |         | 85  | 5   | _   | 72.5 | MHz  |

|                                    | ×2                       | 5   |     | 85  | 5   | _      | 85  | 5   | _      | 85  | 5   |         | 85  | 5   | _   | 72.5 | MHz  |

|                                    | ×1                       | 5   | _   | 170 | 5   | _      | 170 | 5   | _      | 170 | 5   |         | 170 | 5   | _   | 145  | MHz  |

|                                    | ×10                      | 100 | _   | 170 | 100 | _      | 170 | 100 | _      | 170 | 100 | _       | 170 | 100 |     | 145  | Mbps |

|                                    | ×8                       | 80  | _   | 170 | 80  | _      | 170 | 80  | _      | 170 | 80  | _       | 170 | 80  | _   | 145  | Mbps |

| Device operation in                | ×7                       | 70  | _   | 170 | 70  | _      | 170 | 70  | _      | 170 | 70  |         | 170 | 70  | _   | 145  | Mbps |

| Mbps                               | ×4                       | 40  | _   | 170 | 40  |        | 170 | 40  | _      | 170 | 40  | _       | 170 | 40  | _   | 145  | Mbps |

|                                    | ×2                       | 20  | 1   | 170 | 20  | _      | 170 | 20  |        | 170 | 20  |         | 170 | 20  |     | 145  | Mbps |

|                                    | ×1                       | 10  | -   | 170 | 10  |        | 170 | 10  |        | 170 | 10  |         | 170 | 10  | _   | 145  | Mbps |

| t <sub>DUTY</sub>                  | _                        | 45  | _   | 55  | 45  |        | 55  | 45  | _      | 55  | 45  | _       | 55  | 45  | _   | 55   | %    |

| TCCS                               | _                        | _   | 1   | 200 | _   | _      | 200 | _   |        | 200 | _   |         | 200 |     |     | 200  | ps   |

| Output jitter<br>(peak to peak)    | _                        | _   |     | 500 | _   | _      | 500 | _   |        | 550 | _   | _       | 600 | _   |     | 700  | ps   |

|                                    | 20 – 80%,                |     |     |     |     |        |     |     |        |     |     |         |     |     |     |      |      |

| t <sub>RISE</sub>                  | C <sub>LOAD</sub> = 5 pF | _   | 500 | _   | _   | 500    | _   | _   | 500    | _   | _   | 500     | _   | _   | 500 | _    | ps   |

|                                    | 20 – 80%,                |     |     |     |     |        |     |     |        |     |     |         |     |     |     |      |      |

| t <sub>FALL</sub>                  | C <sub>LOAD</sub> = 5 pF | _   | 500 | _   | _   | 500    | _   | _   | 500    | _   | _   | 500     | _   |     | 500 | _    | ps   |

| Table 1–34. True LVDS Transmitter Timing Specifications for Cyclone IV Devices (1), (3 | ue LVDS Transmitter Timing Specifications | for Cyclone IV Devices (1), (3) |

|----------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------|

|----------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------|

| Cumbal                          | Madaa | C   | 6   | C7  | , I7  | C8, | , A7  | C8L | , I8L | C   | 9L  | llmit |

|---------------------------------|-------|-----|-----|-----|-------|-----|-------|-----|-------|-----|-----|-------|

| Symbol                          | Modes | Min | Max | Min | Max   | Min | Max   | Min | Max   | Min | Max | Unit  |

|                                 | ×10   | 5   | 420 | 5   | 370   | 5   | 320   | 5   | 320   | 5   | 250 | MHz   |

|                                 | ×8    | 5   | 420 | 5   | 370   | 5   | 320   | 5   | 320   | 5   | 250 | MHz   |

| f <sub>HSCLK</sub> (input       | ×7    | 5   | 420 | 5   | 370   | 5   | 320   | 5   | 320   | 5   | 250 | MHz   |

| clock<br>frequency)             | ×4    | 5   | 420 | 5   | 370   | 5   | 320   | 5   | 320   | 5   | 250 | MHz   |

| , ,,,                           | ×2    | 5   | 420 | 5   | 370   | 5   | 320   | 5   | 320   | 5   | 250 | MHz   |

|                                 | ×1    | 5   | 420 | 5   | 402.5 | 5   | 402.5 | 5   | 362   | 5   | 265 | MHz   |

|                                 | ×10   | 100 | 840 | 100 | 740   | 100 | 640   | 100 | 640   | 100 | 500 | Mbps  |

|                                 | ×8    | 80  | 840 | 80  | 740   | 80  | 640   | 80  | 640   | 80  | 500 | Mbps  |

| HSIODR                          | ×7    | 70  | 840 | 70  | 740   | 70  | 640   | 70  | 640   | 70  | 500 | Mbps  |

| nolubh                          | ×4    | 40  | 840 | 40  | 740   | 40  | 640   | 40  | 640   | 40  | 500 | Mbps  |

|                                 | ×2    | 20  | 840 | 20  | 740   | 20  | 640   | 20  | 640   | 20  | 500 | Mbps  |

|                                 | ×1    | 10  | 420 | 10  | 402.5 | 10  | 402.5 | 10  | 362   | 10  | 265 | Mbps  |

| t <sub>DUTY</sub>               | _     | 45  | 55  | 45  | 55    | 45  | 55    | 45  | 55    | 45  | 55  | %     |

| TCCS                            | _     | _   | 200 | _   | 200   | _   | 200   | _   | 200   | _   | 200 | ps    |

| Output jitter<br>(peak to peak) | _     | _   | 500 | _   | 500   | _   | 550   | _   | 600   | _   | 700 | ps    |

| t <sub>LOCK</sub> (2)           | _     | _   | 1   | _   | 1     | _   | 1     | _   | 1     | _   | 1   | ms    |

#### Notes to Table 1-34:

- (1) Cyclone IV E—true LVDS transmitter is only supported at the output pin of Row I/O Banks 1, 2, 5, and 6. Cyclone IV GX—true LVDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6.

- (2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

- (3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

Table 1–35. Emulated LVDS Transmitter Timing Specifications for Cyclone IV Devices (1), (3) (Part 1 of 2)

| Combal                             | Madaa | C   | 6     | C7, | , I7  | C8, | A7    | C8L, | , I8L | C   | 9L  | IIi4 |

|------------------------------------|-------|-----|-------|-----|-------|-----|-------|------|-------|-----|-----|------|

| Symbol                             | Modes | Min | Max   | Min | Max   | Min | Max   | Min  | Max   | Min | Max | Unit |

|                                    | ×10   | 5   | 320   | 5   | 320   | 5   | 275   | 5    | 275   | 5   | 250 | MHz  |

|                                    | ×8    | 5   | 320   | 5   | 320   | 5   | 275   | 5    | 275   | 5   | 250 | MHz  |

| f <sub>HSCLK</sub> (input<br>clock | ×7    | 5   | 320   | 5   | 320   | 5   | 275   | 5    | 275   | 5   | 250 | MHz  |

| frequency)                         | ×4    | 5   | 320   | 5   | 320   | 5   | 275   | 5    | 275   | 5   | 250 | MHz  |

| , ,,                               | ×2    | 5   | 320   | 5   | 320   | 5   | 275   | 5    | 275   | 5   | 250 | MHz  |

|                                    | ×1    | 5   | 402.5 | 5   | 402.5 | 5   | 402.5 | 5    | 362   | 5   | 265 | MHz  |

|                                    | ×10   | 100 | 640   | 100 | 640   | 100 | 550   | 100  | 550   | 100 | 500 | Mbps |

|                                    | ×8    | 80  | 640   | 80  | 640   | 80  | 550   | 80   | 550   | 80  | 500 | Mbps |

| HSIODR                             | ×7    | 70  | 640   | 70  | 640   | 70  | 550   | 70   | 550   | 70  | 500 | Mbps |

| HOIODI                             | ×4    | 40  | 640   | 40  | 640   | 40  | 550   | 40   | 550   | 40  | 500 | Mbps |

|                                    | ×2    | 20  | 640   | 20  | 640   | 20  | 550   | 20   | 550   | 20  | 500 | Mbps |

|                                    | ×1    | 10  | 402.5 | 10  | 402.5 | 10  | 402.5 | 10   | 362   | 10  | 265 | Mbps |

For more information about the supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to *Section III: System Performance Specifications* of the *External Memory Interface Handbook*.

Table 1–37 lists the memory output clock jitter specifications for Cyclone IV devices.

Table 1–37. Memory Output Clock Jitter Specifications for Cyclone IV Devices (1), (2)

| Parameter                    | Symbol                 | Min  | Max | Unit |

|------------------------------|------------------------|------|-----|------|

| Clock period jitter          | t <sub>JIT(per)</sub>  | -125 | 125 | ps   |

| Cycle-to-cycle period jitter | t <sub>JIT(cc)</sub>   | -200 | 200 | ps   |

| Duty cycle jitter            | t <sub>JIT(duty)</sub> | -150 | 150 | ps   |

#### Notes to Table 1-37:

- Memory output clock jitter measurements are for 200 consecutive clock cycles, as specified in the JEDEC DDR2 standard.

- (2) The clock jitter specification applies to memory output clock pins generated using DDIO circuits clocked by a PLL output routed on a global clock (GCLK) network.

## **Duty Cycle Distortion Specifications**

Table 1–38 lists the worst case duty cycle distortion for Cyclone IV devices.

Table 1–38. Duty Cycle Distortion on Cyclone IV Devices I/O Pins (1), (2), (3)

| Symbol            | C   | C6 C7, I7 |     | , <b>1</b> 7 | C8, I8 | BL, A7 | C   | Unit |       |

|-------------------|-----|-----------|-----|--------------|--------|--------|-----|------|-------|

| Symbol            | Min | Max       | Min | Max          | Min    | Max    | Min | Max  | Ullit |

| Output Duty Cycle | 45  | 55        | 45  | 55           | 45     | 55     | 45  | 55   | %     |

## Notes to Table 1-38:

- (1) The duty cycle distortion specification applies to clock outputs from the PLLs, global clock tree, and IOE driving the dedicated and general purpose I/O pins.

- (2) Cyclone IV devices meet the specified duty cycle distortion at the maximum output toggle rate for each combination of I/O standard and current strength.

- (3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

# **OCT Calibration Timing Specification**

Table 1–39 lists the duration of calibration for series OCT with calibration at device power-up for Cyclone IV devices.

Table 1–39. Timing Specification for Series OCT with Calibration at Device Power-Up for Cyclone IV Devices  $^{(1)}$

| Symbol              | Maximum                                                    | Units |    |

|---------------------|------------------------------------------------------------|-------|----|

| t <sub>OCTCAL</sub> | Duration of series OCT with calibration at device power-up | 20    | μs |

#### Note to Table 1-39:

(1) OCT calibration takes place after device configuration and before entering user mode.

Table 1–44 and Table 1–45 list the IOE programmable delay for Cyclone IV GX devices.

Table 1-44. IOE Programmable Delay on Column Pins for Cyclone IV GX Devices (1), (2)

|                                                                       |                                   | Number   |        | Max Offset |       |        |       |        |        |    |      |

|-----------------------------------------------------------------------|-----------------------------------|----------|--------|------------|-------|--------|-------|--------|--------|----|------|

| Parameter                                                             | Paths<br>Affected                 | of       | Offcot | of Min     |       | Corner |       | Slow ( | Corner |    | Unit |

|                                                                       |                                   | Settings |        | C6         | 17    | C6     | C7    | C8     | 17     |    |      |

| Input delay from pin to internal cells                                | Pad to I/O<br>dataout to<br>core  | 7        | 0      | 1.313      | 1.209 | 2.184  | 2.336 | 2.451  | 2.387  | ns |      |

| Input delay from pin to input register                                | Pad to I/O input register         | 8        | 0      | 1.312      | 1.208 | 2.200  | 2.399 | 2.554  | 2.446  | ns |      |

| Delay from output register to output pin                              | I/O output<br>register to<br>pad  | 2        | 0      | 0.438      | 0.404 | 0.751  | 0.825 | 0.886  | 0.839  | ns |      |

| Input delay from<br>dual-purpose clock pin<br>to fan-out destinations | Pad to global<br>clock<br>network | 12       | 0      | 0.713      | 0.682 | 1.228  | 1.41  | 1.566  | 1.424  | ns |      |

## Notes to Table 1-44:

- (1) The incremental values for the settings are generally linear. For exact values of each setting, use the latest version of the Quartus II software.

- (2) The minimum and maximum offset timing numbers are in reference to setting 0 as available in the Quartus II software.

Table 1-45. IOE Programmable Delay on Row Pins for Cyclone IV GX Devices (1), (2)

|                                                                       |                                  | Number   |        | Max Offset                |       |        |             |       |       |    |      |

|-----------------------------------------------------------------------|----------------------------------|----------|--------|---------------------------|-------|--------|-------------|-------|-------|----|------|

| Parameter                                                             | Paths<br>Affected                | of       | Offcot | Min<br>Offset Fast Corner |       | Corner | Slow Corner |       |       |    | Unit |

|                                                                       |                                  | Settings |        | C6                        | 17    | C6     | <b>C</b> 7  | C8    | 17    |    |      |

| Input delay from pin to internal cells                                | Pad to I/O<br>dataout to<br>core | 7        | 0      | 1.314                     | 1.210 | 2.209  | 2.398       | 2.526 | 2.443 | ns |      |

| Input delay from pin to input register                                | Pad to I/O input register        | 8        | 0      | 1.313                     | 1.208 | 2.205  | 2.406       | 2.563 | 2.450 | ns |      |

| Delay from output register to output pin                              | I/O output<br>register to<br>pad | 2        | 0      | 0.461                     | 0.421 | 0.789  | 0.869       | 0.933 | 0.884 | ns |      |

| Input delay from<br>dual-purpose clock pin<br>to fan-out destinations | Pad to global<br>clock network   | 12       | 0      | 0.712                     | 0.682 | 1.225  | 1.407       | 1.562 | 1.421 | ns |      |

## Notes to Table 1-45:

- (1) The incremental values for the settings are generally linear. For exact values of each setting, use the latest version of Quartus II software.

- (2) The minimum and maximum offset timing numbers are in reference to setting 0 as available in the Quartus II software

Table 1-46. Glossary (Part 3 of 5)

| Letter | Term                                                   | Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

|--------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|        | $R_L$                                                  | Receiver differential input discrete resistor (external to Cyclone IV devices).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

|        |                                                        | Receiver input waveform for LVDS and LVPECL differential standards:  Single-Ended Waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

|        |                                                        | Positive Channel (p) = V <sub>IH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

|        |                                                        | Negative Channel (n) = V <sub>IL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| R      | Receiver Input<br>Waveform                             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

|        |                                                        | Differential Waveform (Mathematical Function of Positive & Negative Channel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|        |                                                        | V <sub>ID</sub> 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|        |                                                        | V <sub>ID</sub> p-n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|        | Receiver input<br>skew margin<br>(RSKM)                | High-speed I/O block: The total margin left after accounting for the sampling window and TCCS. RSKM = (TUI – SW – TCCS) / 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |