## Intel - EP4CGX75DF27I7N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 4620                                                       |

| Number of Logic Elements/Cells | 73920                                                      |

| Total RAM Bits                 | 4257792                                                    |

| Number of I/O                  | 310                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.16V ~ 1.24V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 672-BGA                                                    |

| Supplier Device Package        | 672-FBGA (27x27)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4cgx75df27i7n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Cyclone IV E industrial devices I7 are offered with extended operating temperature range.

# **Absolute Maximum Ratings**

Absolute maximum ratings define the maximum operating conditions for Cyclone IV devices. The values are based on experiments conducted with the device and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied at these conditions. Table 1–1 lists the absolute maximum ratings for Cyclone IV devices.

Conditions beyond those listed in Table 1–1 cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time have adverse effects on the device.

| Symbol                | Parameter                                                                                                                                    | Min  | Max  | Unit |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| V <sub>CCINT</sub>    | Core voltage, PCI Express <sup>®</sup> (PCIe <sup>®</sup> ) hard IP<br>block, and transceiver physical coding sublayer<br>(PCS) power supply | -0.5 | 1.8  | V    |

| V <sub>CCA</sub>      | Phase-locked loop (PLL) analog power supply                                                                                                  | -0.5 | 3.75 | V    |

| V <sub>CCD_PLL</sub>  | PLL digital power supply                                                                                                                     | -0.5 | 1.8  | V    |

| V <sub>CCIO</sub>     | I/O banks power supply                                                                                                                       | -0.5 | 3.75 | V    |

| V <sub>CC_CLKIN</sub> | Differential clock input pins power supply                                                                                                   | -0.5 | 4.5  | V    |

| V <sub>CCH_GXB</sub>  | Transceiver output buffer power supply                                                                                                       | -0.5 | 3.75 | V    |

| V <sub>CCA_GXB</sub>  | Transceiver physical medium attachment (PMA) and auxiliary power supply                                                                      | -0.5 | 3.75 | V    |

| V <sub>CCL_GXB</sub>  | Transceiver PMA and auxiliary power supply                                                                                                   | -0.5 | 1.8  | V    |

| VI                    | DC input voltage                                                                                                                             | -0.5 | 4.2  | V    |

| I <sub>OUT</sub>      | DC output current, per pin                                                                                                                   | -25  | 40   | mA   |

| T <sub>STG</sub>      | Storage temperature                                                                                                                          | -65  | 150  | °C   |

| TJ                    | Operating junction temperature                                                                                                               | -40  | 125  | °C   |

Table 1–1. Absolute Maximum Ratings for Cyclone IV Devices (1)

Note to Table 1–1:

(1) Supply voltage specifications apply to voltage readings taken at the device pins with respect to ground, not at the power supply.

# **Maximum Allowed Overshoot or Undershoot Voltage**

During transitions, input signals may overshoot to the voltage shown in Table 1–2 and undershoot to –2.0 V for a magnitude of currents less than 100 mA and for periods shorter than 20 ns. Table 1–2 lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage over the lifetime of the device. The maximum allowed overshoot duration is specified as a percentage of high-time over the lifetime of the device.

| Table 1–3. | Recommended Operating Conditions for Cyclone IV E Devices <sup>(1), (2</sup> | <sup>9</sup> (Part 2 of 2) |

|------------|------------------------------------------------------------------------------|----------------------------|

|------------|------------------------------------------------------------------------------|----------------------------|

| Symbol             | Parameter                                                     | Parameter Conditions |   |  |    | Unit |

|--------------------|---------------------------------------------------------------|----------------------|---|--|----|------|

| I <sub>Diode</sub> | Magnitude of DC current across<br>PCI-clamp diode when enable | _                    | _ |  | 10 | mA   |

## Notes to Table 1–3:

Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades.

(2)  $V_{CCI0}$  for all I/O banks must be powered up during device operation. All vCCA pins must be powered to 2.5 V (even when PLLs are not used) and must be powered up and powered down at the same time.

(3)  $V_{CC}$  must rise monotonically.

(4) V<sub>CCI0</sub> powers all input buffers.

(5) The POR time for Standard POR ranges between 50 and 200 ms. Each individual power supply must reach the recommended operating range within 50 ms.

(6) The POR time for Fast POR ranges between 3 and 9 ms. Each individual power supply must reach the recommended operating range within 3 ms.

| Symbol                            | Parameter                                                          | Conditions | Min   | Тур | Max   | Unit |

|-----------------------------------|--------------------------------------------------------------------|------------|-------|-----|-------|------|

| V <sub>ccint</sub> <i>(3)</i>     | Core voltage, PCIe hard IP block, and transceiver PCS power supply |            | 1.16  | 1.2 | 1.24  | V    |

| V <sub>CCA</sub> (1), (3)         | PLL analog power supply                                            | _          | 2.375 | 2.5 | 2.625 | V    |

| V <sub>CCD_PLL</sub> <i>(2)</i>   | PLL digital power supply                                           | _          | 1.16  | 1.2 | 1.24  | V    |

|                                   | I/O banks power supply for 3.3-V operation                         | —          | 3.135 | 3.3 | 3.465 | V    |

|                                   | I/O banks power supply for 3.0-V operation                         | —          | 2.85  | 3   | 3.15  | V    |

| \ <i>I</i> (3). (4)               | I/O banks power supply for 2.5-V operation                         | _          | 2.375 | 2.5 | 2.625 | V    |

| V <sub>CCIO</sub> <i>(3), (4)</i> | I/O banks power supply for 1.8-V operation                         | —          | 1.71  | 1.8 | 1.89  | V    |

|                                   | I/O banks power supply for 1.5-V operation                         | —          | 1.425 | 1.5 | 1.575 | V    |

|                                   | I/O banks power supply for 1.2-V operation                         | _          | 1.14  | 1.2 | 1.26  | V    |

|                                   | Differential clock input pins power supply for 3.3-V operation     | —          | 3.135 | 3.3 | 3.465 | V    |

|                                   | Differential clock input pins power supply for 3.0-V operation     | —          | 2.85  | 3   | 3.15  | V    |

| V <sub>CC_CLKIN</sub>             | Differential clock input pins power supply for 2.5-V operation     | —          | 2.375 | 2.5 | 2.625 | V    |

| (3), (5), (6)                     | Differential clock input pins power supply for 1.8-V operation     | —          | 1.71  | 1.8 | 1.89  | V    |

|                                   | Differential clock input pins power supply for 1.5-V operation     | —          | 1.425 | 1.5 | 1.575 | V    |

|                                   | Differential clock input pins power supply for 1.2-V operation     | —          | 1.14  | 1.2 | 1.26  | V    |

| V <sub>CCH_GXB</sub>              | Transceiver output buffer power supply                             | _          | 2.375 | 2.5 | 2.625 | V    |

## Table 1–4. Recommended Operating Conditions for Cyclone IV GX Devices (Part 1 of 2)

| Symbol               | Parameter                                                      | Conditions                                      | Min   | Тур | Max               | Unit |

|----------------------|----------------------------------------------------------------|-------------------------------------------------|-------|-----|-------------------|------|

| V <sub>CCA_GXB</sub> | Transceiver PMA and auxiliary power supply                     | _                                               | 2.375 | 2.5 | 2.625             | V    |

| V <sub>CCL_GXB</sub> | Transceiver PMA and auxiliary power supply                     | _                                               | 1.16  | 1.2 | 1.24              | V    |

| VI                   | DC input voltage                                               | —                                               | -0.5  |     | 3.6               | V    |

| V <sub>0</sub>       | DC output voltage                                              | —                                               | 0     | —   | V <sub>CCIO</sub> | V    |

| т                    | Operating junction temperature                                 | For commercial use                              | 0     | —   | 85                | °C   |

| TJ                   | Operating junction temperature                                 | For industrial use                              | -40   |     | 100               | °C   |

| t <sub>RAMP</sub>    | Power supply ramp time                                         | Standard power-on reset<br>(POR) <sup>(7)</sup> | 50 µs | _   | 50 ms             | _    |

|                      |                                                                | Fast POR <sup>(8)</sup>                         | 50 µs |     | 3 ms              | _    |

| I <sub>Diode</sub>   | Magnitude of DC current across<br>PCI-clamp diode when enabled | _                                               | _     | _   | 10                | mA   |

Table 1-4. Recommended Operating Conditions for Cyclone IV GX Devices (Part 2 of 2)

#### Notes to Table 1-4:

- (1) All VCCA pins must be powered to 2.5 V (even when PLLs are not used) and must be powered up and powered down at the same time.

- (2) You must connect  $V_{CCD PLL}$  to  $V_{CCINT}$  through a decoupling capacitor and ferrite bead.

- (3) Power supplies must rise monotonically.

- (4) V<sub>CCI0</sub> for all I/O banks must be powered up during device operation. Configurations pins are powered up by V<sub>CCI0</sub> of I/O Banks 3, 8, and 9 where I/O Banks 3 and 9 only support V<sub>CCI0</sub> of 1.5, 1.8, 2.5, 3.0, and 3.3 V. For fast passive parallel (FPP) configuration mode, the V<sub>CCI0</sub> level of I/O Bank 8 must be powered up to 1.5, 1.8, 2.5, 3.0, and 3.3 V.

- (5) You must set  $V_{CC_{CLKIN}}$  to 2.5 V if you use CLKIN as a high-speed serial interface (HSSI) refclk or as a DIFFCLK input.

- (6) The CLKIN pins in I/O Banks 3B and 8B can support single-ended I/O standard when the pins are used to clock left PLLs in non-transceiver applications.

- (7) The POR time for Standard POR ranges between 50 and 200 ms. V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCIO</sub> of I/O Banks 3, 8, and 9 must reach the recommended operating range within 50 ms.

- (8) The POR time for Fast POR ranges between 3 and 9 ms. V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCIO</sub> of I/O Banks 3, 8, and 9 must reach the recommended operating range within 3 ms.

# **ESD Performance**

This section lists the electrostatic discharge (ESD) voltages using the human body model (HBM) and charged device model (CDM) for Cyclone IV devices general purpose I/Os (GPIOs) and high-speed serial interface (HSSI) I/Os. Table 1–5 lists the ESD for Cyclone IV devices GPIOs and HSSI I/Os.

| Table 1–5. ESD for Cyclone IV Devices GPIOs and HSSI I/0 |

|----------------------------------------------------------|

|----------------------------------------------------------|

| Symbol              | Parameter                                        | Passing Voltage | Unit |

|---------------------|--------------------------------------------------|-----------------|------|

| M                   | ESD voltage using the HBM (GPIOs) <sup>(1)</sup> | ± 2000          | V    |

| V <sub>ESDHBM</sub> | ESD using the HBM (HSSI I/Os) <sup>(2)</sup>     | ± 1000          | V    |

| V                   | ESD using the CDM (GPIOs)                        | ± 500           | V    |

| VESDCDM             | ESD using the CDM (HSSI I/Os) <sup>(2)</sup>     | ± 250           | V    |

#### Notes to Table 1-5:

(1) The passing voltage for EP4CGX15 and EP4CGX30 row I/Os is ±1000V.

(2) This value is applicable only to Cyclone IV GX devices.

# **DC Characteristics**

This section lists the I/O leakage current, pin capacitance, on-chip termination (OCT) tolerance, and bus hold specifications for Cyclone IV devices.

# **Supply Current**

The device supply current requirement is the minimum current drawn from the power supply pins that can be used as a reference for power size planning. Use the Excel-based early power estimator (EPE) to get the supply current estimates for your design because these currents vary greatly with the resources used. Table 1–6 lists the I/O pin leakage current for Cyclone IV devices.

Table 1–6. I/O Pin Leakage Current for Cyclone IV Devices (1), (2)

| Symbol          | Parameter                            | Conditions                            | Device | Min | Тур | Max | Unit |

|-----------------|--------------------------------------|---------------------------------------|--------|-----|-----|-----|------|

| I <sub>I</sub>  | Input pin leakage current            | $V_{I} = 0 V \text{ to } V_{CCIOMAX}$ | _      | -10 | _   | 10  | μA   |

| I <sub>OZ</sub> | Tristated I/O pin leakage<br>current | $V_0 = 0 V$ to $V_{CCIOMAX}$          |        | -10 |     | 10  | μΑ   |

Notes to Table 1-6:

(1) This value is specified for normal device operation. The value varies during device power-up. This applies for all V<sub>CCI0</sub> settings (3.3, 3.0, 2.5, 1.8, 1.5, and 1.2 V).

(2) The 10  $\mu$ A I/O leakage current limit is applicable when the internal clamping diode is off. A higher current can be observed when the diode is on.

## **Bus Hold**

The bus hold retains the last valid logic state after the source driving it either enters the high impedance state or is removed. Each I/O pin has an option to enable bus hold in user mode. Bus hold is always disabled in configuration mode.

Table 1–7 lists bus hold specifications for Cyclone IV devices.

Table 1–7. Bus Hold Parameter for Cyclone IV Devices (Part 1 of 2)<sup>(1)</sup>

|                                            |                                                |     | V <sub>CC10</sub> (V) |     |      |     |      |     |      |     |      |     |      |      |

|--------------------------------------------|------------------------------------------------|-----|-----------------------|-----|------|-----|------|-----|------|-----|------|-----|------|------|

| Parameter                                  | Condition                                      | 1   | .2                    | 1   | .5   | 1   | .8   | 2   | .5   | 3   | .0   | 3   | .3   | Unit |

|                                            |                                                | Min | Max                   | Min | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  |      |

| Bus hold<br>low,<br>sustaining<br>current  | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 8   | _                     | 12  | _    | 30  | _    | 50  | _    | 70  | _    | 70  | _    | μА   |

| Bus hold<br>high,<br>sustaining<br>current | V <sub>IN</sub> < V <sub>IL</sub><br>(minimum) | -8  | _                     | -12 | _    | -30 |      | -50 | _    | -70 | _    | -70 | _    | μΑ   |

| Bus hold<br>low,<br>overdrive<br>current   | $0 V < V_{\rm IN} < V_{\rm CCI0}$              | _   | 125                   |     | 175  | _   | 200  | _   | 300  |     | 500  |     | 500  | μA   |

| Bus hold<br>high,<br>overdrive<br>current  | $0 V < V_{IN} < V_{CCIO}$                      | _   | -125                  | _   | -175 |     | -200 |     | -300 |     | -500 |     | -500 | μА   |

| Parameter              |           |           |     |       |       |      | V <sub>ccio</sub> | (V) |     |     |     |     |     |    |

|------------------------|-----------|-----------|-----|-------|-------|------|-------------------|-----|-----|-----|-----|-----|-----|----|

|                        | Parameter | Condition | 1   | .2    | 1     | .5   | 1                 | .8  | 2   | .5  | 3   | .0  | 3   | .3 |

|                        |           | Min       | Max | Min   | Max   | Min  | Max               | Min | Max | Min | Max | Min | Max |    |

| Bus hold trip<br>point | —         | 0.3       | 0.9 | 0.375 | 1.125 | 0.68 | 1.07              | 0.7 | 1.7 | 0.8 | 2   | 0.8 | 2   | V  |

Table 1–7. Bus Hold Parameter for Cyclone IV Devices (Part 2 of 2)<sup>(1)</sup>

Note to Table 1-7:

(1) Bus hold trip points are based on the calculated input voltages from the JEDEC standard.

# **OCT Specifications**

Table 1–8 lists the variation of OCT without calibration across process, temperature, and voltage (PVT).

|                                   |                       | Resistance         |                                                               |      |

|-----------------------------------|-----------------------|--------------------|---------------------------------------------------------------|------|

| Description                       | V <sub>CCIO</sub> (V) | Commercial Maximum | Industrial, Extended<br>industrial, and<br>Automotive Maximum | Unit |

|                                   | 3.0                   | ±30                | ±40                                                           | %    |

|                                   | 2.5                   | ±30                | ±40                                                           | %    |

| Series OCT without<br>calibration | 1.8                   | ±40                | ±50                                                           | %    |

|                                   | 1.5                   | ±50                | ±50                                                           | %    |

|                                   | 1.2                   | ±50                | ±50                                                           | %    |

OCT calibration is automatically performed at device power-up for OCT-enabled I/Os.

Table 1–9 lists the OCT calibration accuracy at device power-up.

|                       |                       | Calibratio         |                                                               |      |

|-----------------------|-----------------------|--------------------|---------------------------------------------------------------|------|

| Description           | V <sub>CCIO</sub> (V) | Commercial Maximum | Industrial, Extended<br>industrial, and<br>Automotive Maximum | Unit |

|                       | 3.0                   | ±10                | ±10                                                           | %    |

| Series OCT with       | 2.5                   | ±10                | ±10                                                           | %    |

| calibration at device | 1.8                   | ±10                | ±10                                                           | %    |

| power-up              | 1.5                   | ±10                | ±10                                                           | %    |

|                       | 1.2                   | ±10                | ±10                                                           | %    |

The OCT resistance may vary with the variation of temperature and voltage after calibration at device power-up. Use Table 1–10 and Equation 1–1 to determine the final OCT resistance considering the variations after calibration at device power-up. Table 1–10 lists the change percentage of the OCT resistance with voltage and temperature.

| Nominal Voltage | dR/dT (%/°C) | dR/dV (%/mV) |

|-----------------|--------------|--------------|

| 3.0             | 0.262        | -0.026       |

| 2.5             | 0.234        | -0.039       |

| 1.8             | 0.219        | -0.086       |

| 1.5             | 0.199        | -0.136       |

| 1.2             | 0.161        | -0.288       |

Equation 1–1. Final OCT Resistance <sup>(1), (2), (3), (4), (5), (6)</sup>

$$\begin{split} &\Delta R_V = (V_2 - V_1) \times 1000 \times dR/dV - (7) \\ &\Delta R_T = (T_2 - T_1) \times dR/dT - (8) \\ &For \ \Delta R_x < 0; \ MF_x = 1/ \ (|\Delta R_x|/100 + 1) - (9) \\ &For \ \Delta R_x > 0; \ MF_x = \Delta R_x/100 + 1 - (10) \\ &MF = MF_V \times MF_T - (11) \\ &R_{final} = R_{initial} \times MF - (12) \end{split}$$

## Notes to Equation 1–1:

- (1)  $T_2$  is the final temperature.

- (2)  $T_1$  is the initial temperature.

- (3) MF is multiplication factor.

- (4) R<sub>final</sub> is final resistance.

- (5) R<sub>initial</sub> is initial resistance.

- (6) Subscript  $_x$  refers to both  $_V$  and  $_T$ .

- (7)  $\Delta R_V$  is a variation of resistance with voltage.

- (8)  $\Delta R_T$  is a variation of resistance with temperature.

- (9) dR/dT is the change percentage of resistance with temperature after calibration at device power-up.

- (10) dR/dV is the change percentage of resistance with voltage after calibration at device power-up.

(11)  $V_2$  is final voltage.

(12)  $V_1$  is the initial voltage.

# Internal Weak Pull-Up and Weak Pull-Down Resistor

Table 1–12 lists the weak pull-up and pull-down resistor values for Cyclone IV devices.

Table 1–12. Internal Weak Pull-Up and Weak Pull-Down Resistor Values for Cyclone IV Devices <sup>(1)</sup>

| Symbol | Parameter                                                                | Conditions                                  | Min | Тур | Max | Unit |

|--------|--------------------------------------------------------------------------|---------------------------------------------|-----|-----|-----|------|

|        |                                                                          | $V_{CCIO} = 3.3 \text{ V} \pm 5\%$ (2), (3) | 7   | 25  | 41  | kΩ   |

|        | Value of the I/O pin pull-up resistor                                    | $V_{CCIO} = 3.0 \text{ V} \pm 5\%$ (2), (3) | 7   | 28  | 47  | kΩ   |

| R      | before and during configuration, as                                      | $V_{CCIO} = 2.5 \text{ V} \pm 5\%$ (2), (3) | 8   | 35  | 61  | kΩ   |

|        | well as user mode if you enable the programmable pull-up resistor option | $V_{CCIO} = 1.8 \text{ V} \pm 5\%$ (2), (3) | 10  | 57  | 108 | kΩ   |

|        |                                                                          | $V_{CCIO} = 1.5 \text{ V} \pm 5\%$ (2), (3) | 13  | 82  | 163 | kΩ   |

|        |                                                                          | $V_{CCIO} = 1.2 \text{ V} \pm 5\%$ (2), (3) | 19  | 143 | 351 | kΩ   |

|        | Value of the I/O pin pull-down resistor before and during configuration  | $V_{CCIO} = 3.3 \text{ V} \pm 5\%$ (4)      | 6   | 19  | 30  | kΩ   |

|        |                                                                          | $V_{CCIO} = 3.0 \text{ V} \pm 5\%$ (4)      | 6   | 22  | 36  | kΩ   |

| R_pd   |                                                                          | $V_{CCIO} = 2.5 V \pm 5\%$ (4)              | 6   | 25  | 43  | kΩ   |

|        |                                                                          | $V_{CCIO} = 1.8 V \pm 5\%$ (4)              | 7   | 35  | 71  | kΩ   |

|        |                                                                          | $V_{CCIO} = 1.5 V \pm 5\%$ (4)              | 8   | 50  | 112 | kΩ   |

#### Notes to Table 1–12:

- (1) All I/O pins have an option to enable weak pull-up except the configuration, test, and JTAG pins. The weak pull-down feature is only available for JTAG TCK.

- (2) Pin pull-up resistance values may be lower if an external source drives the pin higher than  $V_{CCIO}$ .

- $\begin{array}{ll} \text{(3)} & \text{R}_{_{PU}} = (\text{V}_{\text{CCI0}} \text{V}_{\text{I}})/\text{I}_{\text{R}_{_{PU}}} \\ & \text{Minimum condition: } -40^{\circ}\text{C}; \ \text{V}_{\text{CCI0}} = \text{V}_{\text{CC}} + 5\%, \ \text{V}_{\text{I}} = \text{V}_{\text{CC}} + 5\% 50 \ \text{mV}; \\ & \text{Typical condition: } 25^{\circ}\text{C}; \ \text{V}_{\text{CCI0}} = \text{V}_{\text{CC}}, \ \text{V}_{\text{I}} = 0 \ \text{V}; \\ & \text{Maximum condition: } 100^{\circ}\text{C}; \ \text{V}_{\text{CCI0}} = \text{V}_{\text{CC}} 5\%, \ \text{V}_{\text{I}} = 0 \ \text{V}; \\ & \text{Maximum condition: } 100^{\circ}\text{C}; \ \text{V}_{\text{CCI0}} = \text{V}_{\text{CC}} 5\%, \ \text{V}_{\text{I}} = 0 \ \text{V}; \\ & \text{maximum condition: } 100^{\circ}\text{C}; \ \text{V}_{\text{CO}} = \text{V}_{\text{CC}} 5\%, \ \text{V}_{\text{I}} = 0 \ \text{V}; \\ & \text{Maximum condition: } 100^{\circ}\text{C}; \ \text{V}_{\text{CO}} = \text{V}_{\text{CC}} 5\%, \ \text{V}_{\text{I}} = 0 \ \text{V}; \\ & \text{Maximum condition: } 100^{\circ}\text{C}; \ \text{V}_{\text{CO}} = \text{V}_{\text{CO}} 5\%, \ \text{V}_{\text{I}} = 0 \ \text{V}; \\ & \text{Maximum condition: } 100^{\circ}\text{C}; \ \text{V}_{\text{CO}} = \text{V}_{\text{CO}} 5\%, \ \text{V}_{\text{I}} = 0 \ \text{V}; \\ & \text{Maximum condition: } 100^{\circ}\text{C}; \ \text{V}_{\text{CO}} = \text{V}_{\text{CO}} 5\%, \ \text{V}_{\text{I}} = 0 \ \text{V}; \\ & \text{Maximum condition: } 100^{\circ}\text{C}; \ \text{V}_{\text{CO}} = \text{V}_{\text{CO}} 5\%, \ \text{V}_{\text{I}} = 0 \ \text{V}; \\ & \text{Maximum condition: } 100^{\circ}\text{C}; \ \text{V}_{\text{CO}} = \text{V}_{\text{CO}} 5\%, \ \text{V}_{\text{I}} = 0 \ \text{V}; \\ & \text{Maximum condition: } 100^{\circ}\text{C}; \ \text{V}_{\text{CO}} = 10^{\circ}\text{C}; \ \text{V}_{\text{CO}} = 10^{\circ$

- $\begin{array}{ll} (4) & R_{\_PD} = V_I/I_{R\_PD} \\ & \text{Minimum condition:} -40^{\circ}\text{C}; \ V_{CCIO} = V_{CC} + 5\%, \ V_I = 50 \ \text{mV}; \\ & \text{Typical condition:} \ 25^{\circ}\text{C}; \ V_{CCIO} = V_{CC}, \ V_I = V_{CC} 5\%; \\ & \text{Maximum condition:} \ 100^{\circ}\text{C}; \ V_{CCIO} = V_{CC} 5\%, \ V_I = V_{CC} 5\%; \ \text{in which } V_I \ \text{refers to the input voltage at the I/O pin.} \end{array}$

# Hot-Socketing

Table 1–13 lists the hot-socketing specifications for Cyclone IV devices.

Table 1–13. Hot-Socketing Specifications for Cyclone IV Devices

| Symbol                  | Parameter                         | Maximum         |

|-------------------------|-----------------------------------|-----------------|

| I <sub>IOPIN(DC)</sub>  | DC current per I/O pin            | 300 μA          |

| I <sub>IOPIN(AC)</sub>  | AC current per I/O pin            | 8 mA <i>(1)</i> |

| I <sub>XCVRTX(DC)</sub> | DC current per transceiver TX pin | 100 mA          |

| I <sub>XCVRRX(DC)</sub> | DC current per transceiver RX pin | 50 mA           |

Note to Table 1-13:

(1) The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns, |IIOPIN| = C dv/dt, in which C is the I/O pin capacitance and dv/dt is the slew rate.

During hot-socketing, the I/O pin capacitance is less than 15 pF and the clock pin capacitance is less than 20 pF.

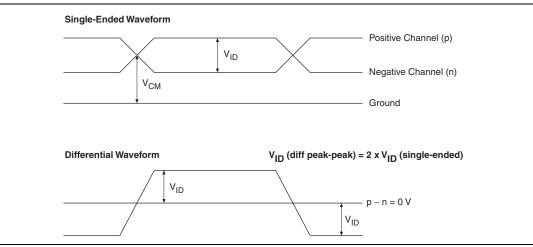

Figure 1–5 shows the transmitter output waveform.

Table 1–22 lists the typical  $V_{OD}$  for Tx term that equals 100  $\Omega$ .

## Table 1–22. Typical V\_{0D} Setting, Tx Term = 100 $\Omega$

| Symbol                                                    | V <sub>op</sub> Setting (mV) |     |     |              |      |      |  |  |  |

|-----------------------------------------------------------|------------------------------|-----|-----|--------------|------|------|--|--|--|

|                                                           | 1                            | 2   | 3   | <b>4</b> (1) | 5    | 6    |  |  |  |

| V <sub>OD</sub> differential peak<br>to peak typical (mV) | 400                          | 600 | 800 | 900          | 1000 | 1200 |  |  |  |

## Note to Table 1-22:

(1) This setting is required for compliance with the PCIe protocol.

| Barlas    | Performance |       |     |                    |                           |       |                |    |        |  |

|-----------|-------------|-------|-----|--------------------|---------------------------|-------|----------------|----|--------|--|

| Device    | C6          | C7    | C8  | C8L <sup>(1)</sup> | <b>C9L</b> <sup>(1)</sup> | 17    | <b>18L</b> (1) | A7 | – Unit |  |

| EP4CE55   | 500         | 437.5 | 402 | 362                | 265                       | 437.5 | 362            | —  | MHz    |  |

| EP4CE75   | 500         | 437.5 | 402 | 362                | 265                       | 437.5 | 362            | —  | MHz    |  |

| EP4CE115  | _           | 437.5 | 402 | 362                | 265                       | 437.5 | 362            | —  | MHz    |  |

| EP4CGX15  | 500         | 437.5 | 402 | —                  | —                         | 437.5 | —              | —  | MHz    |  |

| EP4CGX22  | 500         | 437.5 | 402 | _                  | —                         | 437.5 | _              |    | MHz    |  |

| EP4CGX30  | 500         | 437.5 | 402 | —                  | —                         | 437.5 | —              | —  | MHz    |  |

| EP4CGX50  | 500         | 437.5 | 402 | —                  | —                         | 437.5 | —              | —  | MHz    |  |

| EP4CGX75  | 500         | 437.5 | 402 | _                  | —                         | 437.5 | _              |    | MHz    |  |

| EP4CGX110 | 500         | 437.5 | 402 | —                  | —                         | 437.5 | —              | —  | MHz    |  |

| EP4CGX150 | 500         | 437.5 | 402 |                    |                           | 437.5 |                |    | MHz    |  |

Table 1–24. Clock Tree Performance for Cyclone IV Devices (Part 2 of 2)

#### Note to Table 1-24:

(1) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades.

## **PLL Specifications**

Table 1–25 lists the PLL specifications for Cyclone IV devices when operating in the commercial junction temperature range (0°C to 85°C), the industrial junction temperature range (–40°C to 100°C), the extended industrial junction temperature range (–40°C to 125°C), and the automotive junction temperature range (–40°C to 125°C). For more information about the PLL block, refer to "Glossary" on page 1–37.

Table 1–25. PLL Specifications for Cyclone IV Devices <sup>(1), (2)</sup> (Part 1 of 2)

| Symbol                                                         | Parameter                                                          |     | Тур | Max   | Unit |

|----------------------------------------------------------------|--------------------------------------------------------------------|-----|-----|-------|------|

|                                                                | Input clock frequency (-6, -7, -8 speed grades)                    | 5   | _   | 472.5 | MHz  |

| f <sub>IN</sub> (3)                                            | Input clock frequency (–8L speed grade)                            | 5   |     | 362   | MHz  |

|                                                                | Input clock frequency (–9L speed grade)                            | 5   | _   | 265   | MHz  |

| f <sub>INPFD</sub>                                             | PFD input frequency                                                | 5   |     | 325   | MHz  |

| f <sub>VCO</sub> (4)                                           | PLL internal VCO operating range                                   | 600 |     | 1300  | MHz  |

| f <sub>INDUTY</sub>                                            | Input clock duty cycle                                             | 40  |     | 60    | %    |

| t <sub>INJITTER_CCJ</sub> (5)                                  | Input clock cycle-to-cycle jitter<br>$F_{REF} \ge 100 \text{ MHz}$ |     |     | 0.15  | UI   |

| -                                                              | F <sub>REF</sub> < 100 MHz                                         | —   | _   | ±750  | ps   |

| f <sub>OUT_EXT</sub> (external clock<br>output) <sup>(3)</sup> | PLL output frequency                                               | _   | _   | 472.5 | MHz  |

|                                                                | PLL output frequency (-6 speed grade)                              | —   |     | 472.5 | MHz  |

|                                                                | PLL output frequency (-7 speed grade)                              |     | _   | 450   | MHz  |

| f <sub>OUT</sub> (to global clock)                             | PLL output frequency (-8 speed grade)                              | —   |     | 402.5 | MHz  |

|                                                                | PLL output frequency (-8L speed grade)                             | —   |     | 362   | MHz  |

|                                                                | PLL output frequency (-9L speed grade)                             | —   |     | 265   | MHz  |

| toutduty                                                       | Duty cycle for external clock output (when set to 50%)             | 45  | 50  | 55    | %    |

| t <sub>LOCK</sub>                                              | Time required to lock from end of device configuration             |     | _   | 1     | ms   |

# **Embedded Multiplier Specifications**

Table 1–26 lists the embedded multiplier specifications for Cyclone IV devices.

## Table 1–26. Embedded Multiplier Specifications for Cyclone IV Devices

| Mode                   | <b>Resources Used</b> | Performance |            |     |          |     |      |

|------------------------|-----------------------|-------------|------------|-----|----------|-----|------|

|                        | Number of Multipliers | C6          | C7, I7, A7 | C8  | C8L, 18L | C9L | Unit |

| 9 × 9-bit multiplier   | 1                     | 340         | 300        | 260 | 240      | 175 | MHz  |

| 18 × 18-bit multiplier | 1                     | 287         | 250        | 200 | 185      | 135 | MHz  |

# **Memory Block Specifications**

Table 1–27 lists the M9K memory block specifications for Cyclone IV devices.

## Table 1–27. Memory Block Performance Specifications for Cyclone IV Devices

|           |                                    | <b>Resources Used</b> |               | Performance |            |     |          |     |      |

|-----------|------------------------------------|-----------------------|---------------|-------------|------------|-----|----------|-----|------|

| Memory    | Mode                               | LEs                   | M9K<br>Memory | C6          | C7, I7, A7 | C8  | C8L, 18L | C9L | Unit |

| M9K Block | FIFO 256 × 36                      | 47                    | 1             | 315         | 274        | 238 | 200      | 157 | MHz  |

|           | Single-port 256 × 36               | 0                     | 1             | 315         | 274        | 238 | 200      | 157 | MHz  |

|           | Simple dual-port 256 × 36 CLK      | 0                     | 1             | 315         | 274        | 238 | 200      | 157 | MHz  |

|           | True dual port 512 × 18 single CLK | 0                     | 1             | 315         | 274        | 238 | 200      | 157 | MHz  |

## **Configuration and JTAG Specifications**

Table 1–28 lists the configuration mode specifications for Cyclone IV devices.

## Table 1–28. Passive Configuration Mode Specifications for Cyclone IV Devices (1)

| Programming Mode                           | V <sub>CCINT</sub> Voltage Level (V) | DCLK f <sub>max</sub> | Unit |

|--------------------------------------------|--------------------------------------|-----------------------|------|

| Passive Serial (PS)                        | 1.0 <i>(3</i> )                      | 66                    | MHz  |

|                                            | 1.2                                  | 133                   | MHz  |

| East Dessive Derellel (EDD) (2)            | 1.0 <i>(3)</i>                       | 66                    | MHz  |

| Fast Passive Parallel (FPP) <sup>(2)</sup> | 1.2 (4)                              | 100                   | MHz  |

#### Notes to Table 1-28:

- (1) For more information about PS and FPP configuration timing parameters, refer to the *Configuration and Remote System Upgrades in Cyclone IV Devices* chapter.

- (2) FPP configuration mode supports all Cyclone IV E devices (except for E144 package devices) and EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 only.

- (3) V<sub>CCINT</sub> = 1.0 V is only supported for Cyclone IV E 1.0 V core voltage devices.

- (4) Cyclone IV E devices support 1.2 V V<sub>CCINT</sub>. Cyclone IV E 1.2 V core voltage devices support 133 MHz DCLK f<sub>MAX</sub> for EP4CE6, EP4CE10, EP4CE15, EP4CE22, EP4CE30, and EP4CE40 only.

Table 1–29 lists the active configuration mode specifications for Cyclone IV devices.

| Programming Mode                    | DCLK Range | Typical DCLK | Unit |

|-------------------------------------|------------|--------------|------|

| Active Parallel (AP) <sup>(1)</sup> | 20 to 40   | 33           | MHz  |

| Active Serial (AS)                  | 20 to 40   | 33           | MHz  |

Table 1–29. Active Configuration Mode Specifications for Cyclone IV Devices

#### Note to Table 1-29:

(1) AP configuration mode is only supported for Cyclone IV E devices.

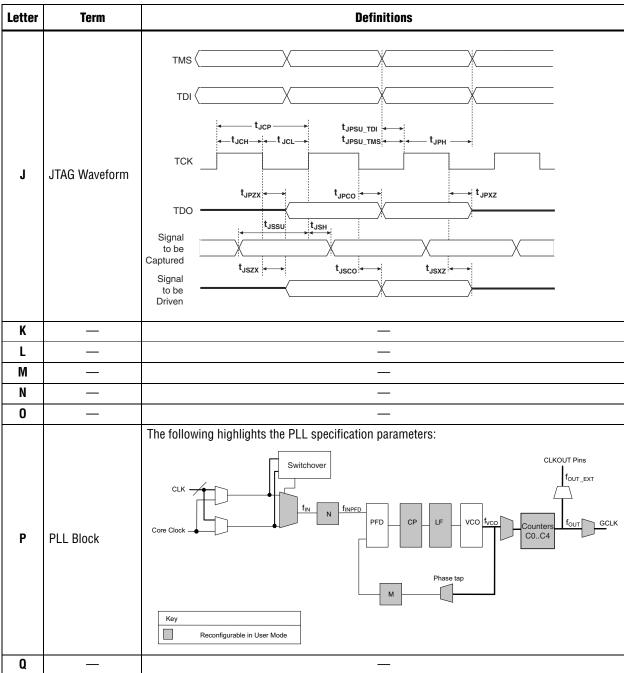

Table 1-30 lists the JTAG timing parameters and values for Cyclone IV devices.

Table 1–30. JTAG Timing Parameters for Cyclone IV Devices (1)

| Symbol                | Parameter                                                    | Min | Max | Unit |

|-----------------------|--------------------------------------------------------------|-----|-----|------|

| t <sub>JCP</sub>      | TCK clock period                                             | 40  | —   | ns   |

| t <sub>JCH</sub>      | TCK clock high time                                          | 19  | _   | ns   |

| t <sub>JCL</sub>      | TCK clock low time                                           | 19  | _   | ns   |

| t <sub>JPSU_TDI</sub> | JTAG port setup time for TDI                                 | 1   | _   | ns   |

| t <sub>JPSU_TMS</sub> | JTAG port setup time for TMS                                 | 3   | _   | ns   |

| t <sub>JPH</sub>      | JTAG port hold time                                          | 10  | _   | ns   |

| t <sub>JPC0</sub>     | JTAG port clock to output <sup>(2), (3)</sup>                | —   | 15  | ns   |

| t <sub>JPZX</sub>     | JTAG port high impedance to valid output <sup>(2), (3)</sup> | —   | 15  | ns   |

| t <sub>JPXZ</sub>     | JTAG port valid output to high impedance <sup>(2), (3)</sup> | —   | 15  | ns   |

| t <sub>JSSU</sub>     | Capture register setup time                                  | 5   | _   | ns   |

| t <sub>JSH</sub>      | Capture register hold time                                   | 10  | _   | ns   |

| t <sub>JSC0</sub>     | Update register clock to output                              | _   | 25  | ns   |

| t <sub>JSZX</sub>     | Update register high impedance to valid output               | _   | 25  | ns   |

| t <sub>JSXZ</sub>     | Update register valid output to high impedance               |     | 25  | ns   |

#### Notes to Table 1-30:

(1) For more information about JTAG waveforms, refer to "JTAG Waveform" in "Glossary" on page 1–37.

- (2) The specification is shown for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 16 ns.

- (3) For EP4CGX22, EP4CGX30 (F324 and smaller package), EP4CGX110, and EP4CGX150 devices, the output time specification for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins is 16 ns. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 18 ns.

# **Periphery Performance**

This section describes periphery performance, including high-speed I/O and external memory interface.

I/O performance supports several system interfaces, such as the high-speed I/O interface, external memory interface, and the PCI/PCI-X bus interface. I/Os using the SSTL-18 Class I termination standard can achieve up to the stated DDR2 SDRAM interfacing speeds. I/Os using general-purpose I/O standards such as 3.3-, 3.0-, 2.5-, 1.8-, or 1.5-LVTTL/LVCMOS are capable of a typical 200 MHz interfacing frequency with a 10 pF load.

| Symbol                          | Modes | C6  |     | C7, 17 |     | C8, A7 |     | C8L, I8L |     | C9L |     | Unit |

|---------------------------------|-------|-----|-----|--------|-----|--------|-----|----------|-----|-----|-----|------|

|                                 |       | Min | Max | Min    | Max | Min    | Max | Min      | Max | Min | Max | Unit |

| t <sub>DUTY</sub>               | —     | 45  | 55  | 45     | 55  | 45     | 55  | 45       | 55  | 45  | 55  | %    |

| TCCS                            | —     | _   | 200 | —      | 200 | _      | 200 | _        | 200 | _   | 200 | ps   |

| Output jitter<br>(peak to peak) | _     |     | 500 | _      | 500 | _      | 550 | _        | 600 | _   | 700 | ps   |

| t <sub>LOCK</sub> (2)           | _     |     | 1   | _      | 1   |        | 1   |          | 1   | _   | 1   | ms   |

## Table 1–35. Emulated LVDS Transmitter Timing Specifications for Cyclone IV Devices <sup>(1), (3)</sup> (Part 2 of 2)

#### Notes to Table 1-35:

(1) Cyclone IV E—emulated LVDS transmitter is supported at the output pin of all I/O Banks.

Cyclone IV GX—emulated LVDS transmitter is supported at the output pin of I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

| Gumbal                                           | Madaa | C   | 6     | C7, | , 17  | C8, | A7    | C8L | , 18L | C   | Unit |      |

|--------------------------------------------------|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|------|------|

| Symbol                                           | Modes | Min | Max   | Min | Max   | Min | Max   | Min | Max   | Min | Max  | Unit |

|                                                  | ×10   | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250  | MHz  |

| f <sub>HSCLK</sub> (input<br>clock<br>frequency) | ×8    | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250  | MHz  |

|                                                  | ×7    | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250  | MHz  |

|                                                  | ×4    | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250  | MHz  |

|                                                  | ×2    | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250  | MHz  |

|                                                  | ×1    | 10  | 437.5 | 10  | 402.5 | 10  | 402.5 | 10  | 362   | 10  | 265  | MHz  |

|                                                  | ×10   | 100 | 875   | 100 | 740   | 100 | 640   | 100 | 640   | 100 | 500  | Mbps |

|                                                  | ×8    | 80  | 875   | 80  | 740   | 80  | 640   | 80  | 640   | 80  | 500  | Mbps |

| HSIODR                                           | ×7    | 70  | 875   | 70  | 740   | 70  | 640   | 70  | 640   | 70  | 500  | Mbps |

| HOIDDN                                           | ×4    | 40  | 875   | 40  | 740   | 40  | 640   | 40  | 640   | 40  | 500  | Mbps |

|                                                  | ×2    | 20  | 875   | 20  | 740   | 20  | 640   | 20  | 640   | 20  | 500  | Mbps |

|                                                  | ×1    | 10  | 437.5 | 10  | 402.5 | 10  | 402.5 | 10  | 362   | 10  | 265  | Mbps |

| SW                                               | —     | _   | 400   | _   | 400   | _   | 400   | _   | 550   | —   | 640  | ps   |

| Input jitter<br>tolerance                        | _     | _   | 500   | _   | 500   | _   | 550   | _   | 600   | _   | 700  | ps   |

| t <sub>LOCK</sub> (2)                            | —     | —   | 1     | —   | 1     | —   | 1     | —   | 1     | —   | 1    | ms   |

Table 1–36. LVDS Receiver Timing Specifications for Cyclone IV Devices (1), (3)

#### Notes to Table 1-36:

(1) Cyclone IV E—LVDS receiver is supported at all I/O Banks.

Cyclone IV GX—LVDS receiver is supported at I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

## **External Memory Interface Specifications**

The external memory interfaces for Cyclone IV devices are auto-calibrating and easy to implement.

# **IOE Programmable Delay**

Table 1–40 and Table 1–41 list the IOE programmable delay for Cyclone IV E 1.0 V core voltage devices.

|                                                                       |                                | Number        | Min<br>Offset | Max Offset |        |       |       |       |    |  |

|-----------------------------------------------------------------------|--------------------------------|---------------|---------------|------------|--------|-------|-------|-------|----|--|

| Parameter                                                             | Paths Affected                 | of<br>Setting |               | Fast (     | Corner | S     | er    | Unit  |    |  |

|                                                                       |                                |               |               | C8L        | 18L    | C8L   | C9L   | 18L   |    |  |

| Input delay from pin to<br>internal cells                             | Pad to I/O<br>dataout to core  | 7             | 0             | 2.054      | 1.924  | 3.387 | 4.017 | 3.411 | ns |  |

| Input delay from pin to<br>input register                             | Pad to I/O input register      | 8             | 0             | 2.010      | 1.875  | 3.341 | 4.252 | 3.367 | ns |  |

| Delay from output register to output pin                              | I/O output<br>register to pad  | 2             | 0             | 0.641      | 0.631  | 1.111 | 1.377 | 1.124 | ns |  |

| Input delay from<br>dual-purpose clock pin to<br>fan-out destinations | Pad to global<br>clock network | 12            | 0             | 0.971      | 0.931  | 1.684 | 2.298 | 1.684 | ns |  |

Notes to Table 1-40:

(1) The incremental values for the settings are generally linear. For the exact values for each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software.

| Parameter                                                             |                                | Number        | Min<br>Offset | Max Offset |        |       |       |       |    |  |

|-----------------------------------------------------------------------|--------------------------------|---------------|---------------|------------|--------|-------|-------|-------|----|--|

|                                                                       | Paths Affected                 | of<br>Setting |               | Fast (     | Corner | S     | Unit  |       |    |  |

|                                                                       |                                |               |               | C8L        | 18L    | C8L   | C9L   | 18L   |    |  |

| Input delay from pin to internal cells                                | Pad to I/O<br>dataout to core  | 7             | 0             | 2.057      | 1.921  | 3.389 | 4.146 | 3.412 | ns |  |

| Input delay from pin to<br>input register                             | Pad to I/O input register      | 8             | 0             | 2.059      | 1.919  | 3.420 | 4.374 | 3.441 | ns |  |

| Delay from output register to output pin                              | I/O output<br>register to pad  | 2             | 0             | 0.670      | 0.623  | 1.160 | 1.420 | 1.168 | ns |  |

| Input delay from<br>dual-purpose clock pin to<br>fan-out destinations | Pad to global<br>clock network | 12            | 0             | 0.960      | 0.919  | 1.656 | 2.258 | 1.656 | ns |  |

Notes to Table 1-41:

(1) The incremental values for the settings are generally linear. For the exact values for each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software.

Table 1–42 and Table 1–43 list the IOE programmable delay for Cyclone IV E 1.2 V core voltage devices.

|                                                                       |                                   | Number        | Min<br>Offset | Max Offset |          |       |       |       |         |       |       |      |

|-----------------------------------------------------------------------|-----------------------------------|---------------|---------------|------------|----------|-------|-------|-------|---------|-------|-------|------|

| Parameter                                                             | Paths<br>Affected                 | of<br>Setting |               | Fa         | ast Corn | er    |       | SI    | ow Corn | er    |       | Unit |

|                                                                       |                                   |               |               | C6         | 17       | A7    | C6    | C7    | C8      | 17    | A7    |      |

| Input delay from pin to internal cells                                | Pad to I/O<br>dataout to<br>core  | 7             | 0             | 1.314      | 1.211    | 1.211 | 2.177 | 2.340 | 2.433   | 2.388 | 2.508 | ns   |

| Input delay from pin to input register                                | Pad to I/O<br>input register      | 8             | 0             | 1.307      | 1.203    | 1.203 | 2.19  | 2.387 | 2.540   | 2.430 | 2.545 | ns   |

| Delay from output<br>register to output pin                           | I/O output<br>register to<br>pad  | 2             | 0             | 0.437      | 0.402    | 0.402 | 0.747 | 0.820 | 0.880   | 0.834 | 0.873 | ns   |

| Input delay from<br>dual-purpose clock pin<br>to fan-out destinations | Pad to global<br>clock<br>network | 12            | 0             | 0.693      | 0.665    | 0.665 | 1.200 | 1.379 | 1.532   | 1.393 | 1.441 | ns   |

Notes to Table 1-42:

(1) The incremental values for the settings are generally linear. For the exact values for each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software.

| Parameter                                                             |                                   | Number        |               | Max Offset |          |       |       |       |         |       |       |      |

|-----------------------------------------------------------------------|-----------------------------------|---------------|---------------|------------|----------|-------|-------|-------|---------|-------|-------|------|

|                                                                       | Paths<br>Affected                 | of<br>Setting | Min<br>Offset | Fa         | ast Corn | er    |       | SI    | ow Corn | er    |       | Unit |

|                                                                       |                                   |               |               | C6         | 17       | A7    | C6    | C7    | C8      | 17    | A7    |      |

| Input delay from pin to internal cells                                | Pad to I/O<br>dataout to<br>core  | 7             | 0             | 1.314      | 1.209    | 1.209 | 2.201 | 2.386 | 2.510   | 2.429 | 2.548 | ns   |

| Input delay from pin to input register                                | Pad to I/O<br>input register      | 8             | 0             | 1.312      | 1.207    | 1.207 | 2.202 | 2.402 | 2.558   | 2.447 | 2.557 | ns   |

| Delay from output<br>register to output pin                           | I/O output<br>register to<br>pad  | 2             | 0             | 0.458      | 0.419    | 0.419 | 0.783 | 0.861 | 0.924   | 0.875 | 0.915 | ns   |

| Input delay from<br>dual-purpose clock pin<br>to fan-out destinations | Pad to global<br>clock<br>network | 12            | 0             | 0.686      | 0.657    | 0.657 | 1.185 | 1.360 | 1.506   | 1.376 | 1.422 | ns   |

Table 1–43. IOE Programmable Delay on Row Pins for Cyclone IV E 1.2 V Core Voltage Devices (1), (2)

#### Notes to Table 1-43:

(1) The incremental values for the settings are generally linear. For the exact values for each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software.

Table 1–44 and Table 1–45 list the IOE programmable delay for Cyclone IV GX devices.

|                                                                       | Paths<br>Affected                 | Number<br>of<br>Settings | Min<br>Offset | Max Offset  |       |             |       |       |       |      |

|-----------------------------------------------------------------------|-----------------------------------|--------------------------|---------------|-------------|-------|-------------|-------|-------|-------|------|

| Parameter                                                             |                                   |                          |               | Fast Corner |       | Slow Corner |       |       |       | Unit |

|                                                                       |                                   |                          |               | C6          | 17    | C6          | C7    | C8    | 17    |      |

| Input delay from pin to internal cells                                | Pad to I/O<br>dataout to<br>core  | 7                        | 0             | 1.313       | 1.209 | 2.184       | 2.336 | 2.451 | 2.387 | ns   |

| Input delay from pin to input register                                | Pad to I/O<br>input register      | 8                        | 0             | 1.312       | 1.208 | 2.200       | 2.399 | 2.554 | 2.446 | ns   |

| Delay from output<br>register to output pin                           | I/O output<br>register to<br>pad  | 2                        | 0             | 0.438       | 0.404 | 0.751       | 0.825 | 0.886 | 0.839 | ns   |

| Input delay from<br>dual-purpose clock pin<br>to fan-out destinations | Pad to global<br>clock<br>network | 12                       | 0             | 0.713       | 0.682 | 1.228       | 1.41  | 1.566 | 1.424 | ns   |

Notes to Table 1-44:

(1) The incremental values for the settings are generally linear. For exact values of each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software.

|                                                                       | Parameter Paths<br>Affected      | Number<br>of<br>Settings | Min<br>Offset | Max Offset  |       |             |            |       |       |      |

|-----------------------------------------------------------------------|----------------------------------|--------------------------|---------------|-------------|-------|-------------|------------|-------|-------|------|

| Parameter                                                             |                                  |                          |               | Fast Corner |       | Slow Corner |            |       |       | Unit |

|                                                                       |                                  |                          |               | C6          | 17    | C6          | <b>C</b> 7 | C8    | 17    |      |

| Input delay from pin to internal cells                                | Pad to I/O<br>dataout to<br>core | 7                        | 0             | 1.314       | 1.210 | 2.209       | 2.398      | 2.526 | 2.443 | ns   |

| Input delay from pin to input register                                | Pad to I/O<br>input register     | 8                        | 0             | 1.313       | 1.208 | 2.205       | 2.406      | 2.563 | 2.450 | ns   |

| Delay from output<br>register to output pin                           | I/O output<br>register to<br>pad | 2                        | 0             | 0.461       | 0.421 | 0.789       | 0.869      | 0.933 | 0.884 | ns   |

| Input delay from<br>dual-purpose clock pin<br>to fan-out destinations | Pad to global<br>clock network   | 12                       | 0             | 0.712       | 0.682 | 1.225       | 1.407      | 1.562 | 1.421 | ns   |

Table 1–45. IOE Programmable Delay on Row Pins for Cyclone IV GX Devices (1), (2)

#### Notes to Table 1-45:

(1) The incremental values for the settings are generally linear. For exact values of each setting, use the latest version of Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software

# I/O Timing

Use the following methods to determine I/O timing:

- the Excel-based I/O Timing

- the Quartus II timing analyzer

The Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get a timing budget estimation as part of the link timing analysis. The Quartus II timing analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after place-and-route is complete.

The Excel-based I/O Timing spreadsheet is downloadable from Cyclone IV Devices Literature website.

# Glossary

Table 1–46 lists the glossary for this chapter.

| Letter | Term                                                            | Definitions                                                                             |  |  |  |  |  |  |

|--------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Α      | —                                                               | _                                                                                       |  |  |  |  |  |  |

| В      | —                                                               |                                                                                         |  |  |  |  |  |  |

| C      | —                                                               | —                                                                                       |  |  |  |  |  |  |

| D      | —                                                               |                                                                                         |  |  |  |  |  |  |

| E      | —                                                               | —                                                                                       |  |  |  |  |  |  |

| F      | f <sub>HSCLK</sub>                                              | High-speed I/O block: High-speed receiver/transmitter input and output clock frequency. |  |  |  |  |  |  |

| G      | GCLK                                                            | Input pin directly to Global Clock network.                                             |  |  |  |  |  |  |

| u      | GCLK PLL                                                        | Input pin to Global Clock network through the PLL.                                      |  |  |  |  |  |  |

| Н      | HSIODR                                                          | High-speed I/O block: Maximum/minimum LVDS data transfer rate (HSIODR = 1/TUI).         |  |  |  |  |  |  |

| I      | Input Waveforms<br>for the SSTL<br>Differential I/O<br>Standard | Vswing<br>Vswing<br>V <sub>IH</sub><br>V <sub>REF</sub><br>V <sub>IL</sub>              |  |  |  |  |  |  |

Table 1-46. Glossary (Part 1 of 5)

## Table 1-46. Glossary (Part 2 of 5)

| Letter | Term                                  | Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|--------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|        | t <sub>C</sub>                        | High-speed receiver and transmitter input and output clock period.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|        | Channel-to-<br>channel-skew<br>(TCCS) | High-speed I/O block: The timing difference between the fastest and slowest output edges, including $t_{CO}$ variation and clock skew. The clock is included in the TCCS measurement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|        | t <sub>cin</sub>                      | Delay from the clock pad to the I/O input register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |