# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | 8051                                                                      |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 50MHz                                                                     |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), CANbus, LINbus, SPI, UART/USART |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                                |

| Number of I/O              | 40                                                                        |

| Program Memory Size        | 128KB (128K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 8.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                              |

| Data Converters            | A/D 32x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-TQFP                                                                   |

| Supplier Device Package    | 48-TQFP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f580-iqr           |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 13.4. SFR Page Stack Upon PCA Interrupt Occurring During a CAN0 ISR             | 110          |

|----------------------------------------------------------------------------------------|--------------|

| Figure 13.5. SFR Page Stack Upon Return From PCA Interrupt                             |              |

| Figure 13.6. SFR Page Stack Upon Return From CAN0 Interrupt                            |              |

| Figure 15.1. Flash Program Memory Map                                                  |              |

| Figure 17.1. Reset Sources                                                             |              |

| Figure 17.2. Power-On and VDD Monitor Reset Timing                                     |              |

| Figure 19.1. Oscillator Options                                                        |              |

| Figure 19.2. Example Clock Multiplier Output                                           | 181          |

| Figure 19.3. External 32.768 kHz Quartz Crystal Oscillator Connection Diagram          | 186          |

| Figure 20.1. Port I/O Functional Block Diagram                                         |              |

| Figure 20.2. Port I/O Cell Block Diagram                                               |              |

| Figure 20.3. Peripheral Availability on Port I/O Pins                                  |              |

| Figure 20.4. Crossbar Priority Decoder in Example Configuration                        |              |

| Figure 21.1. LIN Block Diagram                                                         |              |

| Figure 22.1. Typical CAN Bus Configuration                                             |              |

| Figure 22.2. CAN Controller Diagram                                                    |              |

| Figure 22.3. Four segments of a CAN Bit                                                |              |

|                                                                                        |              |

| Figure 23.1. SMBus Block Diagram                                                       | 239          |

| Figure 23.2. Typical SMBus Configuration                                               |              |

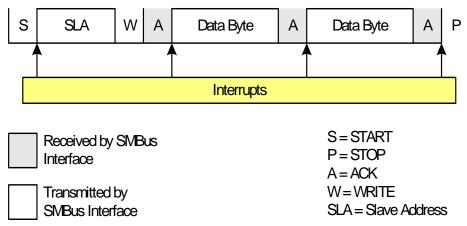

| Figure 23.3. SMBus Transaction                                                         | 241          |

| Figure 23.4. Typical SMBus SCL Generation                                              | 243          |

| Figure 23.5. Typical Master Write Sequence                                             |              |

| Figure 23.6. Typical Master Read Sequence                                              |              |

| Figure 23.7. Typical Slave Write Sequence                                              |              |

| Figure 23.8. Typical Slave Read Sequence                                               |              |

| Figure 24.1. UARTO Block Diagram                                                       |              |

| Figure 24.2. UART0 Timing Without Parity or Extra Bit                                  |              |

| Figure 24.3. UARTO Timing With Parity                                                  |              |

| Figure 24.4. UART0 Timing With Extra Bit                                               |              |

| Figure 24.5. Typical UART Interconnect Diagram                                         |              |

| Figure 24.6. UART Multi-Processor Mode Interconnect Diagram                            |              |

| Figure 26.1. SPI Block Diagram                                                         |              |

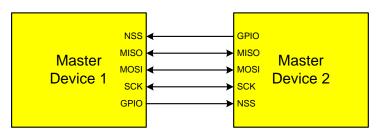

| Figure 26.2. Multiple-Master Mode Connection Diagram                                   |              |

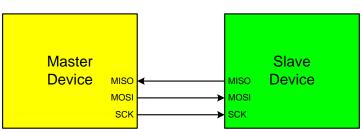

| Figure 26.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagr<br>275 | am           |

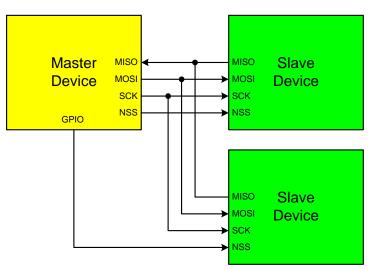

| Figure 26.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diagram        | am           |

|                                                                                        | ~ <b>-</b> - |

| Figure 26.5. Master Mode Data/Clock Timing                                             |              |

| Figure 26.6. Slave Mode Data/Clock Timing (CKPHA = 0)                                  |              |

| Figure 26.7. Slave Mode Data/Clock Timing (CKPHA = 1)                                  |              |

| Figure 26.8. SPI Master Timing (CKPHA = 0)                                             |              |

| Figure 26.9. SPI Master Timing (CKPHA = 1)                                             |              |

| Figure 26.10. SPI Slave Timing (CKPHA = 0)                                             |              |

| Figure 26.11. SPI Slave Timing (CKPHA = 1)                                             | 283          |

| Figure 27.1. T0 Mode 0 Block Diagram                                                   | 288          |

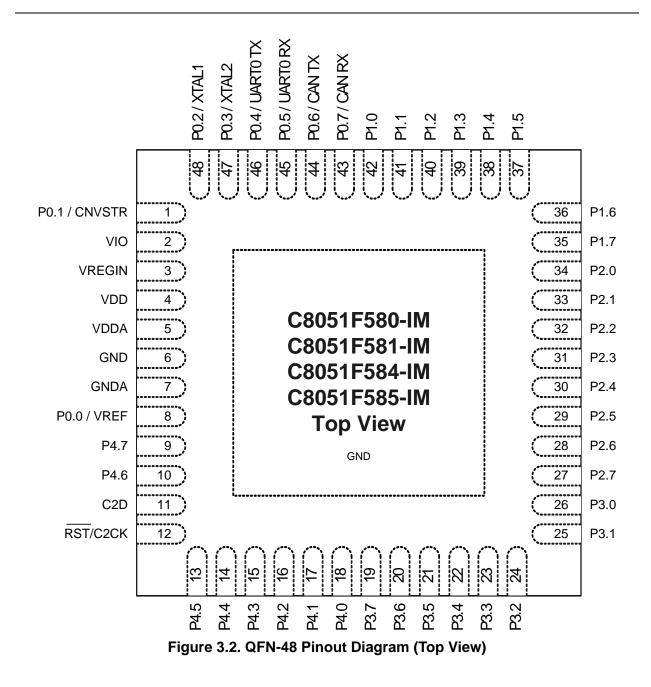

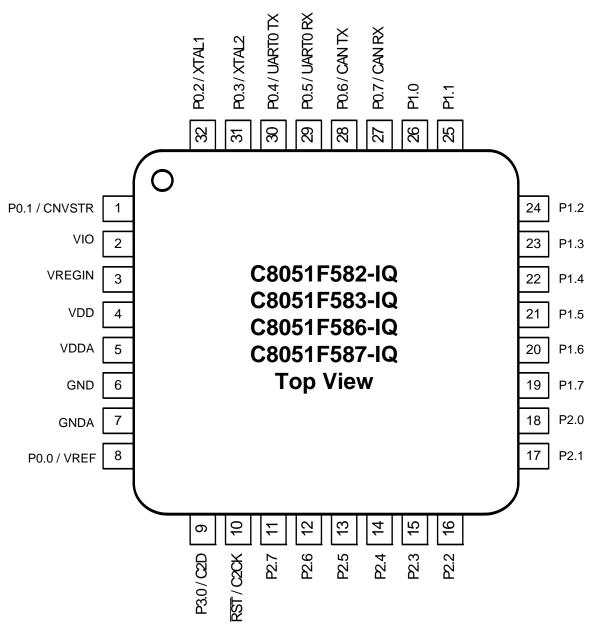

Figure 3.4. QFP-32 Pinout Diagram (Top View)

#### 5.2. Electrical Characteristics

#### **Table 5.2. Global Electrical Characteristics**

-40 to +125 °C, 24 MHz system clock unless otherwise specified.

| Parameter                                    | Conditions                           | Min              | Тур    | Мах   | Units |

|----------------------------------------------|--------------------------------------|------------------|--------|-------|-------|

| Supply Input Voltage (V <sub>REGIN</sub> )   |                                      | 1.8              | _      | 5.25  | V     |

| Digital Supply Voltage (V <sub>DD</sub> )    | System Clock < 25 MHz                | $V_{RST}^{1}$    |        | 2.75  | V     |

|                                              | System Clock > 25 MHz                | 2                |        | 2.75  | v     |

| Analog Supply Voltage (VDDA)                 | System Clock < 25 MHz                | $V_{RST}^{1}$    |        | 2.75  | V     |

| (Must be connected to $V_{DD}$ )             | System Clock > 25 MHz                | 2                |        | 2.75  | v     |

| Digital Supply RAM Data<br>Retention Voltage |                                      | _                | 1.5    | _     |       |

| Port I/O Supply Voltage (V <sub>IO</sub> )   | Normal Operation                     | 1.8 <sup>2</sup> |        | 5.25  | V     |

| SYSCLK (System Clock) <sup>3</sup>           |                                      | 0                |        | 50    | MHz   |

| T <sub>SYSH</sub> (SYSCLK High Time)         |                                      | 9                |        | —     | ns    |

| T <sub>SYSL</sub> (SYSCLK Low Time)          |                                      | 9                |        | —     | ns    |

| Specified Operating<br>Temperature Range     |                                      | -40              | _      | +125  | °C    |

| Digital Supply Current—CPU                   | Active (Normal Mode, fetching instru | uctions          | from F | lash) |       |

| I <sub>DD</sub> <sup>4</sup>                 | V <sub>DD</sub> = 2.1 V, F = 200 kHz | _                | 150    | —     | μA    |

|                                              | V <sub>DD</sub> = 2.1 V, F = 1.5 MHz | —                | 650    | —     | μA    |

|                                              | V <sub>DD</sub> = 2.1 V, F = 25 MHz  | —                | 8.5    | 11    | mA    |

|                                              | V <sub>DD</sub> = 2.1 V, F = 50 MHz  | —                | 15     | 21    | mA    |

| Notes:<br>1 Given in Table 5.4 on page 4     | 18                                   |                  |        | -     |       |

- 1. Given in Table 5.4 on page 48.

- 2.  $V_{IO}$  should not be lower than the  $V_{DD}$  voltage.

- 3. SYSCLK must be at least 32 kHz to enable debugging.

- 4. Based on device characterization data; Not production tested. Does not include oscillator supply current.

- 5. IDD can be estimated for frequencies ≤ 15 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate I<sub>DD</sub> for >15 MHz, the estimate should be the current at 50 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 2.6 V; F = 20 MHz, I<sub>DD</sub> = 21 mA (50 MHz 20 MHz) \* 0.46 mA/MHz = 7.2 mA.

- 6. Idle IDD can be estimated for frequencies  $\leq$  1 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate Idle I<sub>DD</sub> for >1 MHz, the estimate should be the current at 50 MHz minus the difference in current indicated by the frequency sensitivity number.

For example:  $V_{DD}$  = 2.6 V; F = 5 MHz, Idle I<sub>DD</sub> = 19 mA – (50 MHz – 5 MHz) x 0.38 mA/MHz = 1.9 mA.

#### 6.2. Output Code Formatting

The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code. When the repeat count is set to 1, conversion codes are represented in 12-bit unsigned integer format and the output conversion code is updated after each conversion. Inputs are measured from 0 to  $V_{REF} \times 4095/4096$ . Data can be right-justified or left-justified, depending on the setting of the AD0LJST bit (ADC0CN.2). Unused bits in the ADC0H and ADC0L registers are set to 0. Example codes are shown below for both right-justified and left-justified data.

| Input Voltage    | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|------------------|----------------------------------------------|---------------------------------------------|

| VREF x 4095/4096 | 0x0FFF                                       | 0xFFF0                                      |

| VREF x 2048/4096 | 0x0800                                       | 0x8000                                      |

| VREF x 2047/4096 | 0x07FF                                       | 0x7FF0                                      |

| 0                | 0x0000                                       | 0x0000                                      |

When the ADC0 Repeat Count is greater than 1, the output conversion code represents the accumulated result of the conversions performed and is updated after the last conversion in the series is finished. Sets of 4, 8, or 16 consecutive samples can be accumulated and represented in unsigned integer format. The repeat count can be selected using the AD0RPT bits in the ADC0CF register. The value must be right-justified (AD0LJST = 0), and unused bits in the ADC0H and ADC0L registers are set to 0. The following example shows right-justified codes for repeat counts greater than 1. Notice that accumulating  $2^n$  samples is equivalent to left-shifting by *n* bit positions when all samples returned from the ADC have the same value.

| Input Voltage                | Repeat Count = 4 | Repeat Count = 8 | Repeat Count = 16 |

|------------------------------|------------------|------------------|-------------------|

| V <sub>REF</sub> x 4095/4096 | 0x3FFC           | 0x7FF8           | 0xFFF0            |

| V <sub>REF</sub> x 2048/4096 | 0x2000           | 0x4000           | 0x8000            |

| V <sub>REF</sub> x 2047/4096 | 0x1FFC           | 0x3FF8           | 0x7FF0            |

| 0                            | 0x0000           | 0x0000           | 0x0000            |

#### 6.2.1. Settling Time Requirements

A minimum tracking time is required before an accurate conversion is performed. This tracking time is determined by any series impedance, including the AMUX0 resistance, the ADC0 sampling capacitance, and the accuracy required for the conversion.

Figure 6.5 shows the equivalent ADC0 input circuit. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 6.1. When measuring the Temperature Sensor output, use the tracking time specified in Table 5.11 on page 52. When measuring  $V_{DD}$  with respect to GND,  $R_{TO-TAL}$  reduces to  $R_{MUX}$ . See Table 5.10 for ADC0 minimum settling time requirements as well as the mux impedance and sampling capacitor values.

$$t = ln\left(\frac{2^{n}}{SA}\right) \times R_{TOTAL}C_{SAMPLE}$$

#### Equation 6.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

n is the ADC resolution in bits (10).

# 11. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware (see description in "C2 Interface" on page 351), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 11.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 50 MIPS Peak Throughput with 50 MHz Clock

- 0 to 50 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

#### 11.1. Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

#### Table 11.1. CIP-51 Instruction Set Summary (Prefetch-Enabled)

| Mnemonic              | Description                              | Bytes | Clock<br>Cycles |

|-----------------------|------------------------------------------|-------|-----------------|

| Arithmetic Operations |                                          |       |                 |

| ADD A, Rn             | Add register to A                        | 1     | 1               |

| ADD A, direct         | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri            | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data          | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn            | Add register to A with carry             | 1     | 1               |

| ADDC A, direct        | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri           | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data         | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn            | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct        | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri           | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data         | Subtract immediate from A with borrow    | 2     | 2               |

| INC A                 | Increment A                              | 1     | 1               |

| INC Rn                | Increment register                       | 1     | 1               |

| INC direct            | Increment direct byte                    | 2     | 2               |

| INC @Ri               | Increment indirect RAM                   | 1     | 2               |

| DEC A                 | Decrement A                              | 1     | 1               |

| DEC Rn                | Decrement register                       | 1     | 1               |

| DEC direct            | Decrement direct byte                    | 2     | 2               |

| DEC @Ri               | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR              | Increment Data Pointer                   | 1     | 1               |

| MUL AB                | Multiply A and B                         | 1     | 4               |

| DIV AB                | Divide A by B                            | 1     | 8               |

| DA A                  | Decimal adjust A                         | 1     | 1               |

| Logical Operations    |                                          | I     | 1               |

| ANL A, Rn             | AND Register to A                        | 1     | 1               |

| ANL A, direct         | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri            | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data          | AND immediate to A                       | 2     | 2               |

| ANL direct, A         | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data     | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn             | OR Register to A                         | 1     | 1               |

| ORL A, direct         | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri            | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data          | OR immediate to A                        | 2     | 2               |

| ORL direct, A         | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data     | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn             | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct         | Exclusive-OR direct byte to A            | 2     | 2               |

| XRLA, @Ri             | Exclusive-OR indirect RAM to A           | 1     | 2               |

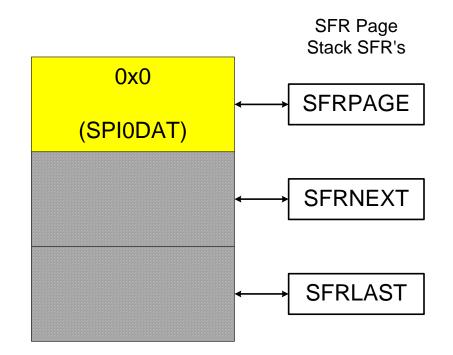

#### Figure 13.2. SFR Page Stack While Using SFR Page 0x0 To Access SPI0DAT

While CIP-51 executes in-line code (writing values to SPI0DAT in this example), the CAN0 Interrupt occurs. The CIP-51 vectors to the CAN0 ISR and pushes the current SFR Page value (SFR Page 0x00) into SFRNEXT in the SFR Page Stack. The SFR page needed to access CAN's SFRs is then automatically placed in the SFRPAGE register (SFR Page 0x0C). SFRPAGE is considered the "top" of the SFR Page Stack. Software can now access the CAN0 SFRs. Software may switch to any SFR Page by writing a new value to the SFRPAGE register at any time during the CAN0 ISR to access SFRs that are not on SFR Page 0x0C. See Figure 13.3.

| Address | Page            | 0(8)               | 1(9)                        | 2(A)                  | 3(B)                        | 4(C)                        | 5(D)                  | 6(E)                  | 7(F)                  |

|---------|-----------------|--------------------|-----------------------------|-----------------------|-----------------------------|-----------------------------|-----------------------|-----------------------|-----------------------|

| F8      | 00<br>10<br>0F  | SPI0CN             | PCA0L<br>PCA1L<br>SN0       | PCA0H<br>PCA1H<br>SN1 | PCA0CPL0<br>PCA1CPL6<br>SN2 | PCA0CPH0<br>PCA1CPH6<br>SN3 | PCACPL4<br>PCA1CPL10  | PCACPH4<br>PCA1CPH10  | VDM0CN                |

| F0      |                 | B<br>(All Pages)   | POMAT                       | POMASK                | P1MAT                       | P1MASK                      | PSBANK<br>(All Pages) | EIP1                  | EIP2                  |

|         | 0F              |                    | POMDIN                      | P1MDIN                | P2MDIN                      | P3MDIN                      |                       | EIP1                  | EIP2                  |

| E8      | 00<br>10<br>0F  | ADC0CN             | PCA0CPL1<br>PCA1CPL7        | PCA0CPH1<br>PCA1CPH7  | PCA0CPL2<br>PCA1CPL8        | PCA0CPH2<br>PCA1CPH8        | PCA0CPL3<br>PCA1CPL9  | PCA0CPL3<br>PCA1CPL9  | RSTSRC                |

| E0      |                 | ACC<br>(All Pages) | XBR0                        | XBR1                  | CCH0CN                      | IT01CF                      |                       | EIE1<br>(All Pages)   | EIE2<br>(All Pages)   |

| D8      | 10<br>0F        | PCA0CN<br>PCA1CN   | PCA0MD<br>PCA1MD<br>PCA0PWM | PCA0CPM0<br>PCA1CPM6  | PCA0CPM1<br>PCA1CPM7        | PCA0CPM2<br>PCA1CPM8        | PCA0CPM3P<br>CA1CPM9  | PCA0CPM4P<br>CA1CPM10 | PCA0CPM5<br>PCA1CPM11 |

| D0      |                 | PSW<br>(All Pages) | REF0CN                      | LIN0DATA              | LIN0ADDR                    | POSKIP                      | P1SKIP                | P2SKIP                | P3SKIP                |

| C8      | 00<br>10<br>0F  | TMR2CN<br>TMR4CN   | REG0CN<br>TMR4CF<br>LIN0CF  | TMR2RLL<br>TMR4CAPL   | TMR2RLH<br>TMR4CAPH         | TMR2L<br>TMR4L              | TMR2H<br>TMR4H        | PCA0CPL5<br>PCA1CPL11 | PCA0CPH5<br>PCA1CPH11 |

| C0      | 00<br>10<br>0F  | SMB0CN             | SMB0CF                      | SMB0DAT               | ADC0GTL                     | ADC0GTH                     | ADC0LTL               | ADC0LTH<br>XBR3       | XBR2                  |

| B8      |                 | IP<br>(All Pages)  |                             | ADC0TK                | ADC0MX                      | ADC0CF                      | ADC0L                 | ADC0H                 |                       |

|         | 10<br>0F        | P3<br>(All Pages)  | P2MAT                       | P2MASK<br>EMI0CF      |                             |                             | P4<br>(All Pages)     | FLSCL<br>(All Pages)  | FLKEY<br>(All Pages)  |

| A8      | <mark>10</mark> | IE<br>(All Pages)  | SMOD0                       | EMI0CN<br>EMI0TC      | SBCON0                      | SBRLL0                      | SBRLH0                | P3MAT<br>P3MDOUT      | P3MASK<br>P4MDOUT     |

| ۸0      | 0F              | P2                 | SPI0CFG                     | SPIOCKR               | SPIODAT                     | SBILLED                     | SBILLIN               | TSMDOUT               | SFRPAGE               |

| A0      |                 | (All Pages)        | OSCICN                      | OSCICRS               | SI IUDAI                    | POMDOUT                     | P1MDOUT               | P2MDOUT               | (All Pages)           |

| 98      | 10              | SCON0<br>SCON1     | SBUF0<br>SBUF1              | CPT0CN<br>CPT2CN      | CPT0MD<br>CPT2MD            | CPT0MX<br>CPT2MX            | CPT1CN                | CPT1MD<br>OSCIFIN     | CPT1MX<br>OSCXCN      |

|         | 0F              | 0(8)               | 1(9)                        | 2(A)                  | 3(B)                        | 4(C)                        | 5(D)                  | 6(E)                  | 7(F)                  |

|         | (               | bit address        | . ,                         | ~(~)                  | 5(6)                        | -(0)                        | 5(D)                  | 0(L)                  | <i>(</i> ()           |

| Table 13.1. Special Function Register (SFR) Memo | ory Map for Pages 0x00, 0x10, and 0x0F |

|--------------------------------------------------|----------------------------------------|

|--------------------------------------------------|----------------------------------------|

# SFR Definition 14.2. IP: Interrupt Priority

| Bit   | 7                                                     | 6                                                                                                                                                                                                                        | 5                                                                                                                                                                                                                        | 4                              | 3        | 2 | 1 | 0 |  |  |

|-------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------|---|---|---|--|--|

| Nam   | e                                                     | PSPI0                                                                                                                                                                                                                    | PSPI0 PT2 PS0 PT1 PX1 PT0 PX1                                                                                                                                                                                            |                                |          |   |   |   |  |  |

| Туре  | R                                                     | R/W                                                                                                                                                                                                                      | R/W R/W R/W R/W R/W R/W                                                                                                                                                                                                  |                                |          |   |   |   |  |  |

| Rese  | t 1                                                   | 0                                                                                                                                                                                                                        | 0 0 0 0 0 0 0 0                                                                                                                                                                                                          |                                |          |   |   |   |  |  |

| SFR A | Address = 0xB8; Bit-Addressable; SFR Page = All Pages |                                                                                                                                                                                                                          |                                                                                                                                                                                                                          |                                |          |   |   |   |  |  |

| Bit   | Name                                                  |                                                                                                                                                                                                                          |                                                                                                                                                                                                                          |                                | Function |   |   |   |  |  |

| 7     | Unused                                                | Read = 1b, W                                                                                                                                                                                                             | rite = Don't (                                                                                                                                                                                                           | Care.                          |          |   |   |   |  |  |

| 6     | PSPI0                                                 | This bit sets th<br>0: SPI0 interru                                                                                                                                                                                      | Serial Peripheral Interface (SPI0) Interrupt Priority Control.<br>This bit sets the priority of the SPI0 interrupt.<br>0: SPI0 interrupt set to low priority level.<br>1: SPI0 interrupt set to high priority level.     |                                |          |   |   |   |  |  |

| 5     | PT2                                                   | <b>Timer 2 Intern</b><br>This bit sets th<br>0: Timer 2 inter<br>1: Timer 2 inter                                                                                                                                        | ne priority of<br>errupt set to                                                                                                                                                                                          | the Timer 2<br>low priority le | evel.    |   |   |   |  |  |

| 4     | PS0                                                   | This bit sets th<br>0: UART0 inte                                                                                                                                                                                        | UARTO Interrupt Priority Control.<br>This bit sets the priority of the UARTO interrupt.<br>0: UARTO interrupt set to low priority level.<br>1: UARTO interrupt set to high priority level.                               |                                |          |   |   |   |  |  |

| 3     | PT1                                                   | This bit sets th<br>0: Timer 1 inte                                                                                                                                                                                      | Timer 1 Interrupt Priority Control.This bit sets the priority of the Timer 1 interrupt.0: Timer 1 interrupt set to low priority level.1: Timer 1 interrupt set to high priority level.                                   |                                |          |   |   |   |  |  |

| 2     | PX1                                                   | This bit sets th<br>0: External Int                                                                                                                                                                                      | External Interrupt 1 Priority Control.<br>This bit sets the priority of the External Interrupt 1 interrupt.<br>0: External Interrupt 1 set to low priority level.<br>1: External Interrupt 1 set to high priority level. |                                |          |   |   |   |  |  |

| 1     | PT0                                                   | This bit sets th<br>0: Timer 0 inte                                                                                                                                                                                      | Timer 0 Interrupt Priority Control.         This bit sets the priority of the Timer 0 interrupt.         0: Timer 0 interrupt set to low priority level.         1: Timer 0 interrupt set to high priority level.        |                                |          |   |   |   |  |  |

| 0     | PX0                                                   | External Interrupt 0 Priority Control.<br>This bit sets the priority of the External Interrupt 0 interrupt.<br>0: External Interrupt 0 set to low priority level.<br>1: External Interrupt 0 set to high priority level. |                                                                                                                                                                                                                          |                                |          |   |   |   |  |  |

| Bit   | 7            | 6                                                                                                                                                                                                         | 5                                                                                              | 4        | 3        | 2        | 1        | 0      |

|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------|----------|----------|----------|--------|

| Nam   | e Reserved   | Reserved                                                                                                                                                                                                  | CHPFEN                                                                                         | Reserved | Reserved | Reserved | Reserved | CHBLKW |

| Туре  | R/W          | R/W                                                                                                                                                                                                       | R/W                                                                                            | R/W      | R/W      | R/W      | R/W      | R/W    |

| Rese  | et 0         | 0                                                                                                                                                                                                         | 1                                                                                              | 0        | 0        | 0        | 0        | 0      |

| SFR A | ddress = 0xE | 3; SFR Page                                                                                                                                                                                               | e = 0x0F                                                                                       |          |          |          |          |        |

| Bit   | Name         |                                                                                                                                                                                                           |                                                                                                |          | Function |          |          |        |

| 7:6   | Reserved     | Must Write 0                                                                                                                                                                                              | 0b                                                                                             |          |          |          |          |        |

| 5     | CHPFEN       | 0: Prefetch e                                                                                                                                                                                             | Cache Prefect Enable Bit.<br>D: Prefetch engine is disabled.<br>I: Prefetch engine is enabled. |          |          |          |          |        |

| 4:1   | Reserved     | Must Write 0                                                                                                                                                                                              | 000b.                                                                                          |          |          |          |          |        |

| 0     | CHBLKW       | Block Write Enable Bit.<br>This bit allows block writes to Flash memory from firmware.<br>D: Each byte of a software Flash write is written individually.<br>1: Flash bytes are written in groups of two. |                                                                                                |          |          |          |          |        |

## SFR Definition 15.5. ONESHOT: Flash Oneshot Period

| Bit   | 7 | 6 | 5 | 4 | 3   | 2     | 1      | 0   |

|-------|---|---|---|---|-----|-------|--------|-----|

| Name  |   |   |   |   |     | PERIC | D[3:0] |     |

| Туре  | R | R | R | R | R/W | R/W   | R/W    | R/W |

| Reset | 0 | 0 | 0 | 0 | 1   | 1     | 1      | 1   |

#### SFR Address = 0xBE; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Unused      | Read = 0000b. Write = don't care.                                                                                                                                                                                                                                                                                                                                                 |

| 3:0 | PERIOD[3:0] | <b>Oneshot Period Control Bits.</b><br>These bits limit the internal Flash read strobe width as follows. When the Flash read strobe is de-asserted, the Flash memory enters a low-power state for the remainder of the system clock cycle. These bits have no effect when the system clocks is greater than 12.5 MHz and FLRT = 0.<br>$FLASH_{RDMAX} = 5ns + (PERIOD \times 5ns)$ |

# **19. Oscillators and Clock Selection**

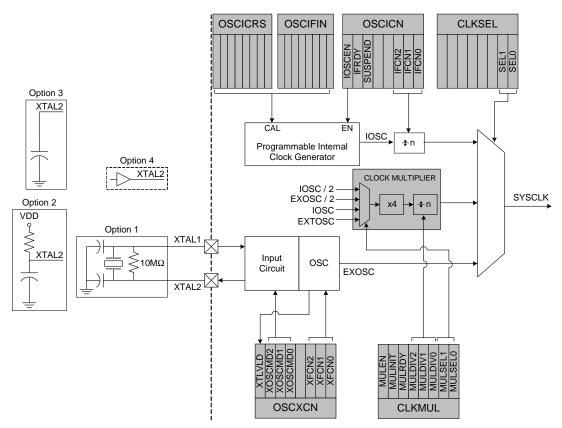

C8051F58x/F59x devices include a programmable internal high-frequency oscillator, an external oscillator drive circuit, and a clock multiplier. The internal oscillator can be enabled/disabled and calibrated using the OSCICN, OSCICRS, and OSCIFIN registers, as shown in Figure 19.1. The system clock can be sourced by the external oscillator circuit or the internal oscillator. The clock multiplier can produce three possible base outputs which can be scaled by a programmable factor of 1, 2/3, 2/4 (or 1/2), 2/5, 2/6 (or 1/3), or 2/7: Internal Oscillator x 2, External Oscillator x 2, or External Oscillator x 4.

Figure 19.1. Oscillator Options

#### 19.1. System Clock Selection

The CLKSL[1:0] bits in register CLKSEL select which oscillator source is used as the system clock. CLKSL[1:0] must be set to 01b for the system clock to run from the external oscillator; however the external oscillator may still clock certain peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal oscillator, external oscillator, and Clock Multiplier so long as the selected clock source is enabled and has settled.

The internal oscillator requires little start-up time and may be selected as the system clock immediately following the register write which enables the oscillator. The external RC and C modes also typically require no startup time.

External crystals and ceramic resonators however, typically require a start-up time before they are settled and ready for use. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to 1 by hardware when the external crystal or ceramic resonator is settled. In crystal mode, to avoid reading a false XTLVLD, software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD.

#### 20.6. Special Function Registers for Accessing and Configuring Port I/O

All Port I/O are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable, except for P4 which is only byte addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

Ports 0–3 have a corresponding PnSKIP register which allows its individual Port pins to be assigned to digital functions or skipped by the Crossbar. All Port pins used for analog functions, GPIO, or dedicated digital functions such as the EMIF should have their PnSKIP bit set to 1.

The Port input mode of the I/O pins is defined using the Port Input Mode registers (PnMDIN). Each Port cell can be configured for analog or digital I/O. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is P4, which can only be used for digital I/O.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings.

#### SFR Definition 20.13. P0: Port 0

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | P0[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W     |   |   |   |   |   |   |   |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Address = 0x80; SFR Page = All Pages; Bit-Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P0[7:0] | <b>Port 0 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P0.n Port pin is logic<br>LOW.<br>1: P0.n Port pin is logic<br>HIGH. |

# SFR Definition 20.16. P0SKIP: Port 0 Skip

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-------------|---|---|---|---|---|---|

| Name  |   | P0SKIP[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W         |   |   |   |   |   |   |

| Reset | 0 | 0           | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xD4; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0SKIP[7:0] | Port 0 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 0 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P0.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P0.n pin is skipped by the Crossbar.</li> </ul> |

#### SFR Definition 20.17. P1: Port 1

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | P1[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W     |   |   |   |   |   |   |   |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Address = 0x90; SFR Page = All Pages; Bit-Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|

| 7:0 | P1[7:0] | <b>Port 1 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW. |

# C8051F58x/F59x

#### 23.5.1. Write Sequence (Master)

During a write sequence, an SMBus master writes data to a slave device. The master in this transfer will be a transmitter during the address byte, and a transmitter during all data bytes. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 0 (WRITE). The master then transmits one or more bytes of serial data. After each byte is transmitted, an acknowledge bit is generated by the slave. The transfer is ended when the STO bit is set and a STOP is generated. Note that the interface will switch to Master Receiver Mode if SMB0DAT is not written following a Master Transmitter interrupt. Figure 23.5 shows a typical master write sequence. Two transmit data bytes are shown, though any number of bytes may be transmitted. Notice that all of the 'data byte transferred' interrupts occur **after** the ACK cycle in this mode.

Figure 23.5. Typical Master Write Sequence

# C8051F58x/F59x

Figure 26.2. Multiple-Master Mode Connection Diagram

Figure 26.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram

Figure 26.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diagram

# 27. Timers

Each MCU includes six counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and the other four are 16-bit auto-reload timers for use with the ADC, SMBus, or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 and Timer 3 offer 16-bit and split 8-bit timer functionality with auto-reload. Timer 4 and Timer 5 have 16-bit auto reload and capture and can also produce a 50% duty-cycle square wave (toggle output) at an general purpose port pin.

| Timer 0 and Timer 1 Modes               | Timer 2 and 3 Modes               | Timer 4 and 5 Modes               |

|-----------------------------------------|-----------------------------------|-----------------------------------|

| 13-bit counter/timer                    | 16-bit timer with auto-reload     | 16-bit timer with auto-reload     |

| 16-bit counter/timer                    |                                   |                                   |

| 8-bit counter/timer with auto-reload    | Two 8-bit timers with auto-reload | 16-bit counter/timer with capture |

| Two 8-bit counter/timers (Timer 0 only) |                                   | Toggle Output                     |

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M– T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked (See SFR Definition 27.1 for pre-scaled clock selection).Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock.

Timer 2 and Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 4 and Timer 5 may be clocked by the system clock, system clock divided by 2 or 12, or the external oscillator clock source divided by 8.

Timers 0, 1, 4, and 5 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin. Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it should be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

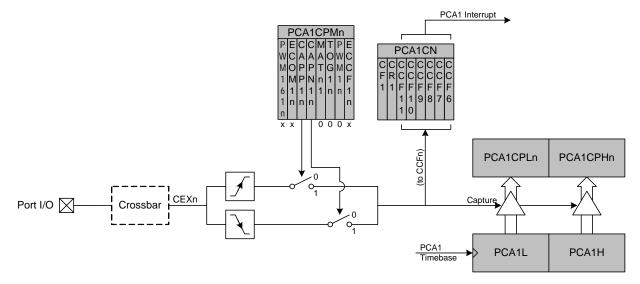

#### 29.3.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes PCA1 to capture the value of the PCA1 counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA1CPLn and PCA1CPHn). The CAPP1n and CAPN1n bits in the PCA1CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA1CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPP1n and CAPN1n bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.

Figure 29.4. PCA1 Capture Mode Diagram

**Note:** The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.

#### 29.4. Register Descriptions for PCA1

Following are detailed descriptions of the special function registers related to the operation of the PCA.

### SFR Definition 29.1. PCA1CN: PCA1 Control

| Bit   | 7                                                    | 6                                                                                                                                                                                                                                                                | 5                             | 4                              | 3                              | 2                               | 1               | 0           |  |  |

|-------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------|--------------------------------|---------------------------------|-----------------|-------------|--|--|

| Nam   | e CF1                                                | CR1                                                                                                                                                                                                                                                              | CCF6                          | CCF7                           | CCF8                           | CCF9                            | CCF10           | CCF11       |  |  |

| Туре  | e R/W R/W R/W R/W R/W R/W R/W                        |                                                                                                                                                                                                                                                                  |                               |                                |                                | R/W                             | R/W             |             |  |  |

| Rese  | t 0                                                  | 0                                                                                                                                                                                                                                                                | 0                             | 0                              | 0                              | 0                               | 0               | 0           |  |  |

| SFR A | SFR Address = 0xD8; Bit-Addressable; SFR Page = 0x10 |                                                                                                                                                                                                                                                                  |                               |                                |                                |                                 |                 |             |  |  |

| Bit   | Name                                                 | Function                                                                                                                                                                                                                                                         |                               |                                |                                |                                 |                 |             |  |  |

| 7     | CF1                                                  | PCA1 Counte                                                                                                                                                                                                                                                      | er/Timer Ov                   | erflow Flag                    |                                |                                 |                 |             |  |  |

|       |                                                      | Set by hardwa<br>When the Cou<br>CPU to vector<br>cleared by ha                                                                                                                                                                                                  | inter/Timer C                 | Overflow (CF<br>1 interrupt se | 1) interrupt is ervice routine | s enabled, se<br>e. This bit is | etting this bit | causes the  |  |  |

| 6     | CR1                                                  | PCA1 Counte                                                                                                                                                                                                                                                      | er/Timer Ru                   | n Control.                     |                                |                                 |                 |             |  |  |

|       |                                                      | This bit enable                                                                                                                                                                                                                                                  |                               |                                | ounter/Timer.                  |                                 |                 |             |  |  |

|       |                                                      | 0: PCA1 Cour<br>1: PCA1 Cour                                                                                                                                                                                                                                     |                               |                                |                                |                                 |                 |             |  |  |

| 5     | CCF11                                                | PCA1 Module                                                                                                                                                                                                                                                      |                               |                                | Flag                           |                                 |                 |             |  |  |

| Ū     |                                                      | This bit is set<br>is enabled, se<br>tine. This bit is                                                                                                                                                                                                           | by hardware<br>tting this bit | when a mat<br>causes the (     | ch or capture<br>CPU to vecto  | or to the PCA                   | 1 interrupt s   | ervice rou- |  |  |

| 4     | CCF10                                                | PCA1 Module                                                                                                                                                                                                                                                      | e 10 Capture                  | e/Compare                      | Flag.                          |                                 |                 |             |  |  |

|       |                                                      | This bit is set<br>is enabled, se<br>tine. This bit is                                                                                                                                                                                                           | tting this bit                | causes the (                   | CPU to vecto                   | or to the PCA                   | 1 interrupt s   | ervice rou- |  |  |

| 3     | CCF9                                                 | PCA1 Module                                                                                                                                                                                                                                                      | e 9 Capture                   | Compare F                      | lag.                           |                                 |                 |             |  |  |

|       |                                                      | This bit is set<br>is enabled, se<br>tine. This bit is                                                                                                                                                                                                           | tting this bit                | causes the (                   | CPU to vecto                   | or to the PCA                   | 1 interrupt s   | ervice rou- |  |  |

| 2     | CCF8                                                 | PCA1 Module                                                                                                                                                                                                                                                      | e 8 Capture                   | Compare F                      | lag.                           |                                 |                 |             |  |  |

|       |                                                      | This bit is set by hardware when a match or capture occurs. When the CCF8 inte is enabled, setting this bit causes the CPU to vector to the PCA1 interrupt service tine. This bit is not automatically cleared by hardware and must be cleared by soft           |                               |                                |                                |                                 | ervice rou-     |             |  |  |

| 1     | CCF7                                                 | PCA1 Module                                                                                                                                                                                                                                                      | e 7 Capture                   | Compare F                      | lag.                           |                                 |                 |             |  |  |

|       |                                                      | This bit is set by hardware when a match or capture occurs. When the CCF7 interru is enabled, setting this bit causes the CPU to vector to the PCA1 interrupt service ro tine. This bit is not automatically cleared by hardware and must be cleared by software |                               |                                |                                |                                 |                 | ervice rou- |  |  |

| 0     | CCF6                                                 | PCA1 Module                                                                                                                                                                                                                                                      | -                             | •                              | -                              |                                 |                 |             |  |  |

|       |                                                      | This bit is set<br>is enabled, se<br>tine. This bit is                                                                                                                                                                                                           | tting this bit                | causes the (                   | CPU to vecto                   | or to the PCA                   | 1 interrupt s   | ervice rou- |  |  |

### SFR Definition 29.4. PCA1CPMn: PCA1 Capture/Compare Mode

| Bit   | 7       | 6      | 5      | 4      | 3     | 2     | 1     | 0      |

|-------|---------|--------|--------|--------|-------|-------|-------|--------|

| Name  | PWM161n | ECOM1n | CAPP1n | CAPN1n | MAT1n | TOG1n | PWM1n | ECCF1n |

| Туре  | R/W     | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   | R/W    |

| Reset | 0       | 0      | 0      | 0      | 0     | 0     | 0     | 0      |

|       |         |        |        |        |       |       |       |        |

SFR Addresses: PCA1CPM6 = 0xDA, PCA1CPM7 = 0xDB, PCA1CPM8 = 0xDC; PCA1CPM9 = 0xDD, PCA1CPM10 = 0xDE, PCA1CPM11 = 0xDF, SFR Page (all registers) = 0x10

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                           |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PWM161n | <ul> <li>16-bit Pulse Width Modulation Enable.</li> <li>This bit enables 16-bit mode when Pulse Width Modulation mode is enabled.</li> <li>0: 8 to 11-bit PWM selected.</li> <li>1: 16-bit PWM selected.</li> </ul>                                                                                                                                                |

| 6   | ECOM1n  | <b>Comparator Function Enable.</b><br>This bit enables the comparator function for PCA1 module n when set to 1.                                                                                                                                                                                                                                                    |

| 5   | CAPP1n  | Capture Positive Function Enable.<br>This bit enables the positive edge capture for PCA1 module n when set to 1.                                                                                                                                                                                                                                                   |

| 4   | CAPN1n  | Capture Negative Function Enable.<br>This bit enables the negative edge capture for PCA1 module n when set to 1.                                                                                                                                                                                                                                                   |

| 3   | MAT1n   | Match Function Enable.<br>This bit enables the match function for PCA1 module n when set to 1. When enabled,<br>matches of the PCA1 counter with a module's capture/compare register cause the<br>CCFn bit in PCA1MD register to be set to logic 1.                                                                                                                |

| 2   | TOG1n   | <b>Toggle Function Enable.</b><br>This bit enables the toggle function for PCA1 module n when set to 1. When enabled, matches of the PCA1 counter with a module's capture/compare register cause the logic level on the CEXn pin to toggle. If the PWMn bit is also set to logic 1, the module operates in Frequency Output Mode.                                  |

| 1   | PWM1n   | <b>Pulse Width Modulation Mode Enable.</b><br>This bit enables the PWM function for PCA1 module n when set to 1. When enabled, a pulse width modulated signal is output on the CEXn pin. 8 to 11-bit PWM is used if PWM16n is cleared; 16-bit mode is used if PWM16n is set to logic 1. If the TOGn bit is also set, the module operates in Frequency Output Mode. |

| 0   | ECCF1n  | Capture/Compare Flag Interrupt Enable.<br>This bit sets the masking of the Capture/Compare Flag (CCFn) interrupt.<br>0: Disable CCFn interrupts.<br>1: Enable a Capture/Compare Flag interrupt request when CCFn is set.                                                                                                                                           |