# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART      |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 40                                                             |

| Program Memory Size        | 128KB (128K x 8)                                               |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 8.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 32x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f581-iq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 5.3. Port I/O DC Electrical Characteristics

$V_{DD}$  = 1.8 to 2.75 V, –40 to +125 °C unless otherwise specified.

| Parameters          | Conditions                                     | Min                    | Тур                   | Max       | Units  |

|---------------------|------------------------------------------------|------------------------|-----------------------|-----------|--------|

| Output High Voltage | I <sub>OH</sub> = –3 mA, Port I/O push-pull    | V <sub>IO</sub> – 0.4  | —                     | —         | V      |

|                     | I <sub>OH</sub> = −10 μA, Port I/O push-pull   | V <sub>IO</sub> – 0.02 |                       |           |        |

|                     | I <sub>OH</sub> = –10 mA, Port I/O push-pull   | —                      | V <sub>IO</sub> – 0.7 | —         |        |

| Output Low Voltage  | V <sub>IO</sub> = 1.8 V:                       |                        |                       |           |        |

|                     | l <sub>OL</sub> = 70 μA                        | _                      |                       | 50        |        |

|                     | l <sub>OL</sub> = 8.5 mA                       | —                      |                       | 750       |        |

|                     | V <sub>IO</sub> = 2.7 V:                       |                        |                       |           |        |

|                     | I <sub>OL</sub> = 70 μΑ                        | —                      |                       | 45        | mV     |

|                     | I <sub>OL</sub> = 8.5 mA                       | —                      |                       | 550       |        |

|                     | V <sub>IO</sub> = 5.25 V:                      |                        |                       |           |        |

|                     | I <sub>OL</sub> = 70 μA                        | —                      |                       | 40        |        |

|                     | I <sub>OL</sub> = 8.5 mA                       | —                      | —                     | 400       |        |

| Input High Voltage  | V <sub>REGIN</sub> = 5.25 V                    | 0.7 x VIO              | —                     | —         | V      |

| Input Low Voltage   | V <sub>REGIN</sub> = 2.7 V                     | —                      | —                     | 0.3 x VIO | V      |

|                     | Weak Pullup Off                                | —                      | —                     | 2         |        |

|                     | Weak Pullup On, V <sub>IO</sub> = 2.1 V,       |                        |                       |           |        |

|                     | $V_{IN} = 0 V, V_{DD} = 1.8 V$                 | _                      | 6                     | 9         |        |

| Input Leakage       | Weak Pullup On, $V_{IO} = 2.6 V$ ,             |                        | _                     | _         | μA     |

| Current             | $V_{IN} = 0 V, V_{DD} = 2.6 V$                 |                        | 16                    | 22        | Part 1 |

|                     |                                                |                        |                       |           |        |

|                     | Weak Pullup On, $V_{IO} = 5.0 V$ ,             |                        |                       |           |        |

|                     | V <sub>IN</sub> = 0 V, V <sub>DD</sub> = 2.6 V | —                      | 45                    | 115       |        |

#### Table 5.6. Internal High-Frequency Oscillator Electrical Characteristics

V<sub>DD</sub> = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified; Using factory-calibrated settings.

| Parameter                                            | Conditions                                      | Min              | Тур             | Max        | Units               |

|------------------------------------------------------|-------------------------------------------------|------------------|-----------------|------------|---------------------|

| Oscillator Frequency                                 | IFCN = 111b;<br>VDD $\geq$ VREGMIN <sup>1</sup> | 24 – 0.5%        | 24 <sup>2</sup> | 24 + 0.5%  | MHz                 |

|                                                      | IFCN = 111b;<br>VDD < VREGMIN <sup>1</sup>      | 24 – 1.0%        | 24 <sup>2</sup> | 24 + 1.0%  |                     |

| Oscillator Supply Current<br>(from V <sub>DD</sub> ) | Internal Oscillator On<br>OSCICN[7:6] = 11b     |                  | 880             | 1300       | μA                  |

| Internal Oscillator Suspend                          | Temp = 25 °C                                    | —                | 300             | _          | μA                  |

| OSCICN[7:6] = 00b                                    | Temp = 85 °C                                    | —                | 320             | —          |                     |

| ZTCEN = 1                                            | Temp = 125 °C                                   | —                | 400             | —          |                     |

| Wake-up Time From Suspend                            | OSCICN[7:6] = 00b                               | —                | 1               | —          | μs                  |

| Power Supply Sensitivity                             | Constant Temperature                            | —                | 0.13            | —          | %/V                 |

| Temperature Sensitivity <sup>3</sup>                 | Constant Supply                                 |                  |                 |            |                     |

|                                                      | TC <sub>1</sub>                                 | —                | 5.0             | —          | ppm/°C              |

|                                                      | TC <sub>2</sub>                                 | —                | -0.65           | —          | ppm/°C <sup>2</sup> |

| 1. VREGMIN is the minimum of                         | output of the voltage regulator for             | r its low settin | g (REG00        | CN: REG0MD | = 0b). See          |

Table 5.9, "Voltage Regulator Electrical Characteristics," on page 50 2. This is the average frequency across the operating temperature range 3. Use temperature coefficients  $TC_1$  and  $TC_2$  to calculate the new internal oscillator frequency using the

following equation:

$f(T) = f0 x (1 + TC_1 x (T - T0) + TC_2 x (T - T0)^2)$

where f0 is the internal oscillator frequency at 25 °C and T0 is 25 °C.

#### 6.2. Output Code Formatting

The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code. When the repeat count is set to 1, conversion codes are represented in 12-bit unsigned integer format and the output conversion code is updated after each conversion. Inputs are measured from 0 to  $V_{REF} \times 4095/4096$ . Data can be right-justified or left-justified, depending on the setting of the AD0LJST bit (ADC0CN.2). Unused bits in the ADC0H and ADC0L registers are set to 0. Example codes are shown below for both right-justified and left-justified data.

| Input Voltage    | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|------------------|----------------------------------------------|---------------------------------------------|

| VREF x 4095/4096 | 0x0FFF                                       | 0xFFF0                                      |

| VREF x 2048/4096 | 0x0800                                       | 0x8000                                      |

| VREF x 2047/4096 | 0x07FF                                       | 0x7FF0                                      |

| 0                | 0x0000                                       | 0x0000                                      |

When the ADC0 Repeat Count is greater than 1, the output conversion code represents the accumulated result of the conversions performed and is updated after the last conversion in the series is finished. Sets of 4, 8, or 16 consecutive samples can be accumulated and represented in unsigned integer format. The repeat count can be selected using the AD0RPT bits in the ADC0CF register. The value must be right-justified (AD0LJST = 0), and unused bits in the ADC0H and ADC0L registers are set to 0. The following example shows right-justified codes for repeat counts greater than 1. Notice that accumulating  $2^n$  samples is equivalent to left-shifting by *n* bit positions when all samples returned from the ADC have the same value.

| Input Voltage                | Repeat Count = 4 | Repeat Count = 8 | Repeat Count = 16 |

|------------------------------|------------------|------------------|-------------------|

| V <sub>REF</sub> x 4095/4096 | 0x3FFC           | 0x7FF8           | 0xFFF0            |

| V <sub>REF</sub> x 2048/4096 | 0x2000           | 0x4000           | 0x8000            |

| V <sub>REF</sub> x 2047/4096 | 0x1FFC           | 0x3FF8           | 0x7FF0            |

| 0                            | 0x0000           | 0x0000           | 0x0000            |

#### 6.2.1. Settling Time Requirements

A minimum tracking time is required before an accurate conversion is performed. This tracking time is determined by any series impedance, including the AMUX0 resistance, the ADC0 sampling capacitance, and the accuracy required for the conversion.

Figure 6.5 shows the equivalent ADC0 input circuit. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 6.1. When measuring the Temperature Sensor output, use the tracking time specified in Table 5.11 on page 52. When measuring  $V_{DD}$  with respect to GND,  $R_{TO-TAL}$  reduces to  $R_{MUX}$ . See Table 5.10 for ADC0 minimum settling time requirements as well as the mux impedance and sampling capacitor values.

$$t = ln\left(\frac{2^{n}}{SA}\right) \times R_{TOTAL}C_{SAMPLE}$$

#### Equation 6.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

n is the ADC resolution in bits (10).

## SFR Definition 9.6. CPT2MD: Comparator2 Mode Selection

| Bit   | 7 | 6 | 5      | 4      | 3 | 2 | 1    | 0      |

|-------|---|---|--------|--------|---|---|------|--------|

| Name  |   |   | CP2RIE | CP2FIE |   |   | CP2M | D[1:0] |

| Туре  | R | R | R/W    | R/W    | R | R | R/W  |        |

| Reset | 0 | 0 | 0      | 0      | 0 | 0 | 1    | 0      |

#### SFR Address = 0x9B; SFR Page = 0x10

| Bit | Name       | Function                                                                                                                                                                                                                                                            |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b, Write = Don't Care.                                                                                                                                                                                                                                     |

| 5   | CP2RIE     | Comparator2 Rising-Edge Interrupt Enable.<br>0: Comparator2 Rising-edge interrupt disabled.<br>1: Comparator2 Rising-edge interrupt enabled.                                                                                                                        |

| 4   | CP2FIE     | Comparator2 Falling-Edge Interrupt Enable.<br>0: Comparator2 Falling-edge interrupt disabled.<br>1: Comparator2 Falling-edge interrupt enabled.                                                                                                                     |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                                                                                                                                                                                                                     |

| 1:0 | CP2MD[1:0] | Comparator2 Mode Select.<br>These bits affect the response time and power consumption for Comparator2.<br>00: Mode 0 (Fastest Response Time, Highest Power Consumption)<br>01: Mode 1<br>10: Mode 2<br>11: Mode 3 (Slowest Response Time, Lowest Power Consumption) |

## SFR Definition 9.8. CPT1MX: Comparator1 MUX Selection

| Bit   | 7             | 6                    | 5           | 4         | 3          | 2          | 1 | 0 |  |

|-------|---------------|----------------------|-------------|-----------|------------|------------|---|---|--|

| Nam   | e             | CMX1N[3:0]           |             |           |            | CMX1P[3:0] |   |   |  |

| Туре  | •             | R/W                  |             |           | R/W        |            |   |   |  |

| Rese  | <b>t</b> 0    | 0 1 1                |             |           | 0          | 1          | 1 | 1 |  |

| SFR A | ddress = 0x9l | :9F; SFR Page = 0x00 |             |           |            |            |   |   |  |

| Bit   | Name          |                      | Function    |           |            |            |   |   |  |

| 7:4   | CMX1N[3:0]    | Comparato            | r1 Negative | Input MUX | Selection. |            |   |   |  |

|       |               | 0000:                | P0.         | 1         |            |            |   |   |  |

|       |               | 0001:                | P0.         | 3         |            |            |   |   |  |

|       |               | 0010:                | P0.         | 5         |            |            |   |   |  |

|       |               | 0011:                | P0.         | 7         |            |            |   |   |  |

|       |               | 0100:                | P1.         | 1         |            |            |   |   |  |

|       |               | 0101:                | P1.         | 3         |            |            |   |   |  |

|       |               | 0110:                | P1.         | 5         |            |            |   |   |  |

|       |               | 0111:                | P1.         | 7         |            |            |   |   |  |

|       |               | 1000:                | P2.         | 1         |            |            |   |   |  |

|       |               | 1001:                | P2.         | 3         |            |            |   |   |  |

|       |               | 1010:                | P2.         | 5         |            |            |   |   |  |

|       |               | 1011:                | P2.         | 7         |            |            |   |   |  |

|       |               | 1100–1111:           | Nor         | ne        |            |            |   |   |  |

| 3:0   | CMX1P[3:0]    | Comparato            | r1 Positive | Input MUX | Selection. |            |   |   |  |

|       |               | 0000:                | P0.         | 0         |            |            |   |   |  |

|       |               | 0001:                | P0.         | 2         |            |            |   |   |  |

|       |               | 0010:                | P0.         | 4         |            |            |   |   |  |

|       |               | 0011:                | P0.         | 6         |            |            |   |   |  |

|       |               | 0100:                | P1.         | 0         |            |            |   |   |  |

|       |               | 0101:                | P1.         | 2         |            |            |   |   |  |

|       |               | 0110:                | P1.         | 4         |            |            |   |   |  |

|       |               | 0111:                | P1.         | 6         |            |            |   |   |  |

|       |               | 1000:                | P2.         | 0         |            |            |   |   |  |

|       |               | 1001:                | P2.         | 2         |            |            |   |   |  |

|       |               | 1010:                | P2.         | 4         |            |            |   |   |  |

|       |               | 1011:                | P2.         | 6         |            |            |   |   |  |

|       |               | 1100–1111:           | Nor         | ne        |            |            |   |   |  |

### 14. Interrupts

The C8051F58x/F59x devices include an extended interrupt system supporting a total of 23 interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regard-less of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE, EIE1, or EIE2). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

**Note:** Any instruction that clears a bit to disable an interrupt should be immediately followed by an instruction that has two or more opcode bytes. Using EA (global interrupt enable) as an example:

```

// in 'C':

EA = 0; // clear EA bit.

EA = 0; // this is a dummy instruction with two-byte opcode.

; in assembly:

CLR EA ; clear EA bit.

CLR EA ; this is a dummy instruction with two-byte opcode.

```

For example, if an interrupt is posted during the execution phase of a "CLR EA" opcode (or any instruction which clears a bit to disable an interrupt source), and the instruction is followed by a single-cycle instruction, the interrupt may be taken. However, a read of the enable bit will return a 0 inside the interrupt service routine. When the bit-clearing opcode is followed by a multi-cycle instruction, the interrupt will not be taken.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

#### 14.1. MCU Interrupt Sources and Vectors

The C8051F58x/F59x MCUs support 23 interrupt sources. Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 14.1. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

### SFR Definition 14.5. EIE2: Extended Interrupt Enable 2

| Bit   | 7   | 6   | 5    | 4     | 3   | 2    | 1     | 0     |

|-------|-----|-----|------|-------|-----|------|-------|-------|

| Name  | ET5 | ET4 | ECP2 | EPCA1 | ES1 | EMAT | ECAN0 | EREG0 |

| Туре  | R/W | R/W | R/W  | R/W   | R/W | R/W  | R/W   | R/W   |

| Reset | 0   | 0   | 0    | 0     | 0   | 0    | 0     | 0     |

#### SFR Address = 0xE7; SFR Page = All Pages

| Bit | Name  | Function                                                                                                                                                                                                                                                                |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ET5   | <ul> <li>Enable Timer 5 Interrupt.</li> <li>This bit sets the masking of the Timer 5 interrupt.</li> <li>0: Disable Timer 5 interrupts.</li> <li>1: Enable interrupt requests generated by the TF5L or TF5H flags.</li> </ul>                                           |

| 6   | ET4   | <ul> <li>Enable Timer 4 Interrupt.</li> <li>This bit sets the masking of the Timer 4 interrupt.</li> <li>0: Disable Timer 4 interrupts.</li> <li>1: Enable interrupt requests generated by the TF4L or TF4H flags.</li> </ul>                                           |

| 5   | ECP2  | <ul> <li>Enable Comparator2 (CP2) Interrupt.</li> <li>This bit sets the masking of the CP2 interrupt.</li> <li>0: Disable CP2 interrupts.</li> <li>1: Enable interrupt requests generated by the CP2RIF or CP2FIF flags.</li> </ul>                                     |

| 4   | EPCA1 | <ul> <li>Enable Programmable Counter Array (PCA1) Interrupt.</li> <li>This bit sets the masking of the PCA1 interrupts.</li> <li>0: Disable all PCA1 interrupts.</li> <li>1: Enable interrupt requests generated by PCA1</li> </ul>                                     |

| 3   | ES1   | Enable UART1 Interrupt.<br>This bit sets the masking of the UART1 interrupt.<br>0: Disable UART1 interrupt.<br>1: Enable UART1 interrupt                                                                                                                                |

| 2   | EMAT  | Enable Port Match Interrupt.<br>This bit sets the masking of the Port Match interrupt.<br>0: Disable all Port Match interrupts.<br>1: Enable interrupt requests generated by a Port Match                                                                               |

| 1   | ECAN0 | Enable CAN0 Interrupts.<br>This bit sets the masking of the CAN0 interrupt.<br>0: Disable all CAN0 interrupts.<br>1: Enable interrupt requests generated by CAN0.                                                                                                       |

| 0   | EREG0 | <ul> <li>Enable Voltage Regulator Dropout Interrupt.</li> <li>This bit sets the masking of the Voltage Regulator Dropout interrupt.</li> <li>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> </ul> |

#### 15.4. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of  $V_{DD}$ , system clock frequency, or temperature. This accidental execution of Flash modi-fying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

The following guidelines are recommended for any system which contains routines which write or erase Flash from code.

#### 15.4.1. $V_{DD}$ Maintenance and the $V_{DD}$ monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- 2. Make certain that the minimum  $V_{REGIN}$  rise time specification of 1 ms is met. If the system cannot meet this rise time specification, then add an external  $V_{DD}$  brownout circuit to the RST pin of the device that holds the device in reset until  $V_{DD}$  reaches the minimum threshold and re-asserts RST if  $V_{DD}$  drops below the minimum threshold.

- 3. Enable the on-chip V<sub>DD</sub> monitor to the high setting and enable the V<sub>DD</sub> monitor as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For C-based systems, this will involve modifying the startup code added by the C compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the V<sub>DD</sub> monitor and enabling the V<sub>DD</sub> monitor as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware", available from the Silicon Laboratories web site.

- 4. As an added precaution, explicitly enable the V<sub>DD</sub> monitor and enable the V<sub>DD</sub> monitor as a reset source inside the functions that write and erase Flash memory. The V<sub>DD</sub> monitor enable instructions should be placed just after the instruction to set PSWE to a 1, but before the Flash write or erase operation instruction.

- **Note:** The output of the internal voltage regulator is calibrated by the MCU immediately after any reset event. The output of the un-calibrated internal regulator could be below the high threshold setting of the VDD Monitor. If this is the case, and the MCU receives a non-power on reset (POR) when the VDD Monitor is set to the high threshold setting, the MCU will remain in reset until a POR occurs (i.e. VDD Monitor will keep the device in reset). A POR will force the VDD Monitor to the low threshold setting, which is guaranteed to be below the un-calibrated output of the internal regulator. The device will then exit reset and resume normal operation. It is for this reason Silicon Labs strongly recommends that the VDD Monitor is always left in the low threshold setting (i.e. default value upon POR). When programming the Flash in-system, the VDD Monitor must be set to the high threshold setting. To prevent this issue from happening and ensure the highest system reliability, firmware can change the V<sub>DD</sub> Monitor high threshold, and the system must use an external supply monitor. For instructions on how to do this, see "Reprogramming the VDD Monitor High Threshold" on page 138.

- Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct. "RSTSRC |= 0x02" is incorrect.

- 6. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a 1. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

#### 19.3. Clock Multiplier

The Clock Multiplier generates an output clock which is 4 times the input clock frequency scaled by a programmable factor of 1, 2/3, 2/4 (or 1/2), 2/5, 2/6 (or 1/3), or 2/7. The Clock Multiplier's input can be selected from the external oscillator, or the internal or external oscillators divided by 2. This produces three possible base outputs which can be scaled by a programmable factor: Internal Oscillator x 2, External Oscillator x 2, or External Oscillator x 4. See Section 19.1 on page 176 for details on system clock selection.

The Clock Multiplier is configured via the CLKMUL register (SFR Definition 19.5). The procedure for configuring and enabling the Clock Multiplier is as follows:

- 1. Reset the Multiplier by writing 0x00 to register CLKMUL.

- 2. Select the Multiplier input source via the MULSEL bits.

- 3. Select the Multiplier output scaling factor via the MULDIV bits

- 4. Enable the Multiplier with the MULEN bit (CLKMUL | = 0x80).

- 5. Delay for  $>5 \ \mu s$ .

- 6. Initialize the Multiplier with the MULINIT bit (CLKMUL | = 0xC0).

- 7. Poll for MULRDY => 1.

**Important Note**: When using an external oscillator as the input to the Clock Multiplier, the external source must be enabled and stable before the Multiplier is initialized. See "19.4. External Oscillator Drive Circuit" on page 183 for details on selecting an external oscillator source.

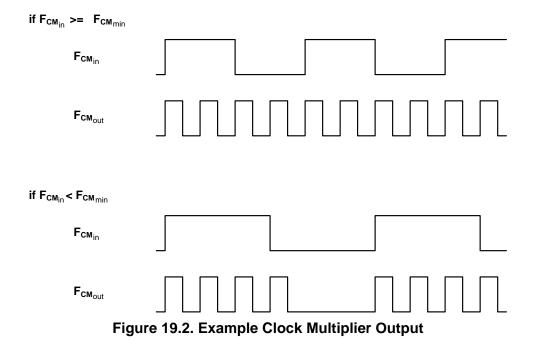

The Clock Multiplier allows faster operation of the CIP-51 core and is intended to generate an output frequency between 25 and 50 MHz. The clock multiplier can also be used with slow input clocks. However, if the clock is below the minimum Clock Multiplier input frequency (FCM<sub>min</sub>), the generated clock will consist of four fast pulses followed by a long delay until the next input clock rising edge. The average frequency of the output is equal to 4x the input, but the instantaneous frequency may be faster. See Figure 19.2 below for more information.

### SFR Definition 20.16. P0SKIP: Port 0 Skip

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-------------|---|---|---|---|---|---|

| Name  |   | P0SKIP[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W         |   |   |   |   |   |   |

| Reset | 0 | 0           | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xD4; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                       |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0SKIP[7:0] | Port 0 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                              |

|     |             | <ul><li>These bits select Port 0 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li><li>0: Corresponding P0.n pin is not skipped by the Crossbar.</li><li>1: Corresponding P0.n pin is skipped by the Crossbar.</li></ul> |

#### SFR Definition 20.17. P1: Port 1

| Bit   | 7 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|

| Name  |   | P1[7:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |   |   |   |   |   |  |  |

| Туре  |   | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |   |   |   |   |   |  |  |

| Reset | 1 | 1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <th1< th=""> <th1< th=""> <th1< th=""> <th1< th=""></th1<></th1<></th1<></th1<> |   |   |   |   |   |   |  |  |

#### SFR Address = 0x90; SFR Page = All Pages; Bit-Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|

| 7:0 | P1[7:0] | <b>Port 1 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW. |

## SFR Definition 22.1. CAN0CFG: CAN Clock Configuration

| Bit   | 7      | 6      | 5      | 4      | 3      | 2      | 1           | 0 |

|-------|--------|--------|--------|--------|--------|--------|-------------|---|

| Name  | Unused | Unused | Unused | Unused | Unused | Unused | SYSDIV[1:0] |   |

| Туре  | R      | R      | R      | R      | R      | R      | R/W         |   |

| Reset | 0      | 0      | 0      | 0      | 0      | 0      | 0           | 0 |

#### SFR Address = 0x92; SFR Page = 0x0C

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                      |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused      | Read = 000000b; Write = Don't Care.                                                                                                                                                                                                                                                                                           |

| 1:0 | SYSDIV[1:0] | CAN System Clock Divider Bits.                                                                                                                                                                                                                                                                                                |

|     |             | The CAN controller clock is derived from the CIP-51 system clock. The CAN control-<br>ler clock must be less than or equal to 25 MHz.<br>00: CAN controller clock = System Clock/1.<br>01: CAN controller clock = System Clock/2.<br>10: CAN controller clock = System Clock/4.<br>11: CAN controller clock = System Clock/8. |

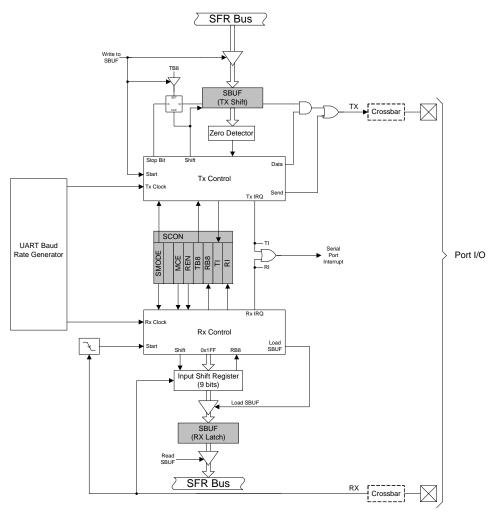

## 25. UART1

UART1 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in Section "25.1. Enhanced Baud Rate Generation" on page 266). Received data buffering allows UART1 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART1 has two associated SFRs: Serial Control Register 1 (SCON1) and Serial Data Buffer 1 (SBUF1). The single SBUF1 location provides access to both transmit and receive registers. Writes to SBUF1 always access the Transmit register. Reads of SBUF1 always access the buffered Receive register; it is not possible to read data from the Transmit register.

With UART1 interrupts enabled, an interrupt is generated each time a transmit is completed (TI1 is set in SCON1), or a data byte has been received (RI1 is set in SCON1). The UART1 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART1 interrupt (transmit complete or receive complete).

## SFR Definition 25.1. SCON1: Serial Port 1 Control

| Bit   | 7      | 6 | 5    | 4    | 3    | 2    | 1   | 0   |

|-------|--------|---|------|------|------|------|-----|-----|

| Name  | S1MODE |   | MCE1 | REN1 | TB81 | RB81 | TI1 | RI1 |

| Туре  | R/W    | R | R/W  | R/W  | R/W  | R/W  | R/W | R/W |

| Reset | 0      | 1 | 0    | 0    | 0    | 0    | 0   | 0   |

SFR Address = 0x98; SFR Page = 0x10; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | S1MODE | Serial Port 1 Operation Mode.<br>Selects the UART1 Operation Mode.<br>0: 8-bit UART with Variable Baud Rate.<br>1: 9-bit UART with Variable Baud Rate.                                                                                                                                                                                                                                                                                                                                                         |

| 6   | Unused | Read = 1b, Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5   | MCE1   | <ul> <li>Multiprocessor Communication Enable.</li> <li>The function of this bit is dependent on the Serial Port 1 Operation Mode:</li> <li>Mode 0: Checks for valid stop bit.</li> <li>0: Logic level of stop bit is ignored.</li> <li>1: RI1 will only be activated if stop bit is logic level 1.</li> <li>Mode 1: Multiprocessor Communications Enable.</li> <li>0: Logic level of ninth bit is ignored.</li> <li>1: RI1 is set and an interrupt is generated only when the ninth bit is logic 1.</li> </ul> |

| 4   | REN1   | Receive Enable.       0: UART1 reception disabled.       1: UART1 reception enabled.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3   | TB81   | Ninth Transmission Bit.<br>The logic level of this bit will be sent as the ninth transmission bit in 9-bit UART Mode (Mode 1). Unused in 8-bit mode (Mode 0).                                                                                                                                                                                                                                                                                                                                                  |

| 2   | RB81   | Ninth Receive Bit.<br>RB81 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the<br>9th data bit in Mode 1.                                                                                                                                                                                                                                                                                                                                                                         |

| 1   | TI1    | <b>Transmit Interrupt Flag.</b><br>Set by hardware when a byte of data has been transmitted by UART1 (after the 8th bit in 8-bit UART Mode, or at the beginning of the STOP bit in 9-bit UART Mode). When the UART1 interrupt is enabled, setting this bit causes the CPU to vector to the UART1 interrupt service routine. This bit must be cleared manually by software.                                                                                                                                     |

| 0   | RI1    | <b>Receive Interrupt Flag.</b><br>Set to '1' by hardware when a byte of data has been received by UART1 (set at the STOP bit sampling time). When the UART1 interrupt is enabled, setting this bit to '1' causes the CPU to vector to the UART1 interrupt service routine. This bit must be cleared manually by software.                                                                                                                                                                                      |

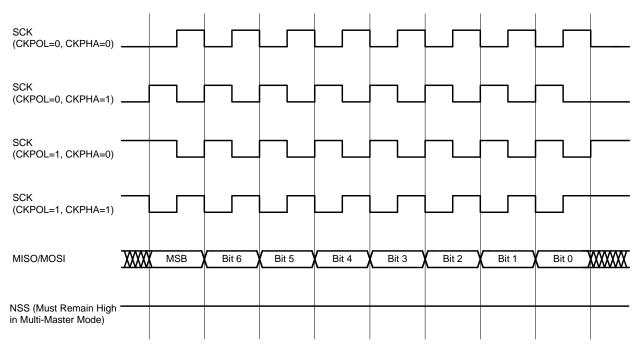

#### 26.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 26.5. For slave mode, the clock and data relationships are shown in Figure 26.6 and Figure 26.7. CKPHA must be set to 0 on both the master and slave SPI when communicating between two of the following devices: C8051F04x, C8051F06x, C8051F12x, C8051F31x, C8051F32x, and C8051F33x.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 26.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

Figure 26.5. Master Mode Data/Clock Timing

## 27. Timers

Each MCU includes six counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and the other four are 16-bit auto-reload timers for use with the ADC, SMBus, or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 and Timer 3 offer 16-bit and split 8-bit timer functionality with auto-reload. Timer 4 and Timer 5 have 16-bit auto reload and capture and can also produce a 50% duty-cycle square wave (toggle output) at an general purpose port pin.

| Timer 0 and Timer 1 Modes               | Timer 2 and 3 Modes               | Timer 4 and 5 Modes               |

|-----------------------------------------|-----------------------------------|-----------------------------------|

| 13-bit counter/timer                    | 16-bit timer with auto-reload     | 16-bit timer with auto-reload     |

| 16-bit counter/timer                    |                                   |                                   |

| 8-bit counter/timer with auto-reload    | Two 8-bit timers with auto-reload | 16-bit counter/timer with capture |

| Two 8-bit counter/timers (Timer 0 only) |                                   | Toggle Output                     |

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M– T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked (See SFR Definition 27.1 for pre-scaled clock selection).Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock.

Timer 2 and Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 4 and Timer 5 may be clocked by the system clock, system clock divided by 2 or 12, or the external oscillator clock source divided by 8.

Timers 0, 1, 4, and 5 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin. Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it should be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

## SFR Definition 27.2. TCON: Timer Control

| Bit   | 7            | 6                                                                                                                                                                                                                                                                                                            | 5                                           | 4                   | 3     | 2                                          | 1   | 0   |  |  |  |  |  |

|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------|-------|--------------------------------------------|-----|-----|--|--|--|--|--|

|       | <b></b>      | TR1                                                                                                                                                                                                                                                                                                          | TF0                                         | TR0                 | IE1   | IT1                                        | IE0 | ITO |  |  |  |  |  |

| Name  | ,            |                                                                                                                                                                                                                                                                                                              |                                             |                     |       |                                            |     |     |  |  |  |  |  |

| Туре  | R/W          | R/W                                                                                                                                                                                                                                                                                                          | R/W                                         | R/W                 | R/W   | R/W                                        | R/W | R/W |  |  |  |  |  |

| Rese  | t 0          | 0                                                                                                                                                                                                                                                                                                            | 0                                           | 0                   | 0     | 0                                          | 0   | 0   |  |  |  |  |  |

| SFR A | ddress = 0x8 | 8; Bit-Addres                                                                                                                                                                                                                                                                                                | 8; Bit-Addressable; SFR Page = All Pages    |                     |       |                                            |     |     |  |  |  |  |  |

| Bit   | Name         |                                                                                                                                                                                                                                                                                                              | Function                                    |                     |       |                                            |     |     |  |  |  |  |  |

| 7     | TF1          | Timer 1 Ov                                                                                                                                                                                                                                                                                                   | erflow Flag                                 |                     |       |                                            |     |     |  |  |  |  |  |

|       |              |                                                                                                                                                                                                                                                                                                              |                                             |                     |       | his flag can b<br>ors to the Tim           |     |     |  |  |  |  |  |

| 6     | TR1          | Timer 1 Ru                                                                                                                                                                                                                                                                                                   | n Control.                                  |                     |       |                                            |     |     |  |  |  |  |  |

|       |              | Timer 1 is e                                                                                                                                                                                                                                                                                                 | nabled by se                                | etting this bit     | to 1. |                                            |     |     |  |  |  |  |  |

| 5     | TF0          | Timer 0 Ov                                                                                                                                                                                                                                                                                                   | erflow Flag                                 |                     |       |                                            |     |     |  |  |  |  |  |

|       |              |                                                                                                                                                                                                                                                                                                              |                                             |                     |       | his flag can t<br>ors to the Tim           |     |     |  |  |  |  |  |

| 4     | TR0          | Timer 0 Ru                                                                                                                                                                                                                                                                                                   | n Control.                                  |                     |       |                                            |     |     |  |  |  |  |  |

|       |              | Timer 0 is e                                                                                                                                                                                                                                                                                                 | nabled by se                                | etting this bit     | to 1. |                                            |     |     |  |  |  |  |  |

| 3     | IE1          | External In                                                                                                                                                                                                                                                                                                  | terrupt 1.                                  |                     |       |                                            |     |     |  |  |  |  |  |

|       |              | can be clear                                                                                                                                                                                                                                                                                                 | red by softwa                               | are but is au       |       | of type defin<br>leared when<br>ered mode. |     |     |  |  |  |  |  |

| 2     | IT1          | Interrupt 1                                                                                                                                                                                                                                                                                                  | Type Select                                 | t.                  |       |                                            |     |     |  |  |  |  |  |

|       |              |                                                                                                                                                                                                                                                                                                              | igured active<br>on 14.7).<br>vel triggered | e low or high<br>d. |       | rrupt will be<br>PL bit in the I           |     |     |  |  |  |  |  |

| 1     | IE0          | External In                                                                                                                                                                                                                                                                                                  | •                                           |                     |       |                                            |     |     |  |  |  |  |  |

|       |              | can be clea                                                                                                                                                                                                                                                                                                  | red by softwa                               | are but is au       |       | of type defin<br>leared when<br>ered mode. |     |     |  |  |  |  |  |

| 0     | IT0          | Interrupt 0                                                                                                                                                                                                                                                                                                  | Type Select                                 |                     |       |                                            |     |     |  |  |  |  |  |

|       |              | Interrupt 0 Type Select.         This bit selects whether the configured INT0 interrupt will be edge or level sensitive.         INT0 is configured active low or high by the IN0PL bit in register IT01CF (see SFR Definition 14.7).         0: INT0 is level triggered.         1: INT0 is edge triggered. |                                             |                     |       |                                            |     |     |  |  |  |  |  |

### SFR Definition 27.4. TL0: Timer 0 Low Byte

| Bit                                      | 7          | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|------------------------------------------|------------|----------|---|---|---|---|---|---|--|--|

| Nam                                      | 9          | TL0[7:0] |   |   |   |   |   |   |  |  |

| Туре                                     | •          | R/W      |   |   |   |   |   |   |  |  |

| Rese                                     | <b>t</b> 0 | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR Address = 0x8A; SFR Page = All Pages |            |          |   |   |   |   |   |   |  |  |

| Bit                                      | Name       |          |   |   |   |   |   |   |  |  |

| Dit | Nume     | i unotion                                               |

|-----|----------|---------------------------------------------------------|

| 7:0 | TL0[7:0] | Timer 0 Low Byte.                                       |

|     |          | The TL0 register is the low byte of the 16-bit Timer 0. |

## SFR Definition 27.5. TL1: Timer 1 Low Byte

| Bit   | 7             | 6           | 5                 | 4             | 3             | 2     | 1 | 0 |  |

|-------|---------------|-------------|-------------------|---------------|---------------|-------|---|---|--|

| Nam   | Name TL1[7:0] |             |                   |               |               |       |   |   |  |

| Туре  | •             | R/W         |                   |               |               |       |   |   |  |

| Rese  | et 0          | 0           | 0                 | 0             | 0             | 0     | 0 | 0 |  |

| SFR A | Address = 0x8 | B; SFR Page | = All Pages       | 5             |               |       |   |   |  |

| Bit   | Name          |             |                   |               | Function      |       |   |   |  |

| 7:0   | TL1[7:0]      | Timer 1 Lov | Fimer 1 Low Byte. |               |               |       |   |   |  |

|       |               | The TL1 reg | jister is the l   | ow byte of th | ne 16-bit Tim | er 1. |   |   |  |

#### 27.4. Timer 4 and Timer 5

Timers 4 and 5 are 16-bit counter/timers, each formed by two 8-bit SFRs: TMRnL (low byte) and TMRnH (high byte) where n = 4 and 5 for timers 4 and 5 respectively. Timers 4 and 5 feature auto-reload, capture, and toggle output modes with the ability to count up or down. Capture mode and Auto-Reload mode are selected using bits in the Timer4 and 5 Control registers (TMRnCN). Toggle Output mode is selected using the Timer 4 and 5 Configuration registers (TMRnCF). These timers may also be used to generate a square-wave at an external pin. As with Timers 0 and 1, Timers 4 and 5 can use either the system clock (divided by one, two, or twelve), external clock (divided by eight) or transitions on an external input pin as its clock source.

The Counter/Timer Select bit CTn bit (TMRnCN.1) configures the peripheral as a counter or timer. Clearing CTn to 0 configures the Timer to be in a timer mode (i.e., the system clock or transitions on an external pin as the input for the timer). When CTn is set to 1, the timer is configured as a counter (i.e., high-to-low transitions at the Tn input pin increment (or decrement) the counter/timer register. Refer to Section "20.4. Port I/O Initialization" on page 195 for information on selecting and configuring external I/O pins for digital peripherals, such as the Tn pin.

The Timers can use either SYSCLK, SYSCLK divided by 2, SYSCLK divided by 12, an external clock divided by 8, or high-to-low transitions on the Tn input pin as its clock source when operating in Counter/Timer with Capture mode. Clearing the CTn bit (TMRnCN.1) selects the system clock/external clock as the input for the timer. The Timer Clock Select bits TnM0 and TnM1 in TMRnCF can be used to select the system clock undivided, system clock divided by two, system clock divided by 12, or an external clock provided at the XTAL1/XTAL2 pins divided by 8 (see SFR Definition 27.19). When CTn is set to logic 1, a high-to-low transition at the Tn input pin increments the counter/timer register (i.e., configured as a counter).

#### 27.4.1. Configuring Timer 4 and 5 to Count Down

Timers 4 and 5 have the ability to count down. When the timer's Decrement Enable Bit (DCENn) in the Timer Configuration Register (see SFR Definition 27.19) is set to 1, the timer can then count *up* or *down*. When DCENn = 1, the direction of the timer's count is controlled by the TnEX pin's logic level. When TnEX = 1, the counter/timer will count up; when TnEX = 0, the counter/timer will count down. To use this feature, TnEX must be enabled in the digital crossbar and configured as a digital input.

**Note:** When DCENn = 1, other functions of the TnEX input (i.e., capture and auto-reload) are not available. TnEX will only control the direction of the timer when DCENn = 1.

#### 27.4.2. Capture Mode

In Capture Mode, Timers 4 and 5 will operate as a 16-bit counter/timer with capture facility. When the Timer External Enable bit (see SFR Definition 27.18) is set to 1, a high-to-low transition on the TnEX input pin causes the 16-bit value in the associated timer (THn, TLn) to be loaded into the capture registers (TMRn-CAPH, TMRnCAPL). If a capture is triggered in the counter/timer, the Timer External Flag (TMRnCN.6) will be set to 1 and an interrupt will occur if the interrupt is enabled. See Section "14. Interrupts" on page 126 for further information concerning the configuration of interrupt sources.

As the 16-bit timer register increments and overflows TMRnH:TMRnL, the TFn Timer Overflow/Underflow Flag (TMRnCN.7) is set to 1 and an interrupt will occur if the interrupt is enabled. The timer can be configured to count down by setting the Decrement Enable Bit (TMRnCF.0) to 1. This will cause the timer to decrement with every timer clock/count event and underflow when the timer transitions from 0x0000 to 0xFFFF. Just as in overflows, the Overflow/Underflow Flag (TFn) will be set to 1, and an interrupt will occur if enabled.

## SFR Definition 28.3. PCA0PWM: PCA0 PWM Configuration

| Bit   | 7     | 6    | 5    | 4 | 3 | 2 | 1          | 0 |

|-------|-------|------|------|---|---|---|------------|---|

| Name  | ARSEL | ECOV | COVF |   |   |   | CLSEL[1:0] |   |

| Туре  | R/W   | R/W  | R/W  | R | R | R | R/W        |   |

| Reset | 0     | 0    | 0    | 0 | 0 | 0 | 0          | 0 |

#### SFR Address = 0xD9; SFR Page = 0x0F

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ARSEL      | Auto-Reload Register Select.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | This bit selects whether to read and write the normal PCA0 capture/compare registers (PCA0CPn), or the Auto-Reload registers at the same SFR addresses. This function is used to define the reload value for 9, 10, and 11-bit PWM modes. In all other modes, the Auto-Reload registers have no function.<br>0: Read/Write Capture/Compare Registers at PCA0CPHn and PCA0CPLn.<br>1: Read/Write Auto-Reload Registers at PCA0CPHn and PCA0CPLn.               |

| 6   | ECOV       | Cycle Overflow Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |            | This bit sets the masking of the Cycle Overflow Flag (COVF) interrupt.<br>0: COVF will not generate PCA0 interrupts.                                                                                                                                                                                                                                                                                                                                          |

|     |            | 1: A PCA0 interrupt will be generated when COVF is set.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5   | COVF       | Cycle Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |            | <ul> <li>This bit indicates an overflow of the 8th, 9th, 10th, or 11th bit of the main PCA0 counter (PCA0). The specific bit used for this flag depends on the setting of the Cycle Length Select bits. The bit can be set by hardware or software, but must be cleared by software.</li> <li>0: No overflow has occurred since the last time this bit was cleared.</li> <li>1: An overflow has occurred since the last time this bit was cleared.</li> </ul> |

| 4:2 | Unused     | Read = 000b; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1:0 | CLSEL[1:0] | Cycle Length Select.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |            | <ul> <li>When 16-bit PWM mode is not selected, these bits select the length of the PWM cycle, between 8, 9, 10, or 11 bits. This affects all channels configured for PWM which are not using 16-bit PWM mode. These bits are ignored for individual channels configured to16-bit PWM mode.</li> <li>00: 8 bits.</li> <li>01: 9 bits.</li> <li>10: 10 bits.</li> <li>11: 11 bits.</li> </ul>                                                                   |