Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 50MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), CANbus, LINbus, SPI, UART/USART |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                       |

| Number of I/O              | 25                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                 |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | - ·                                                              |

| RAM Size                   | 8.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                     |

| Data Converters            | A/D 25x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-VFQFN Exposed Pad                                             |

| Supplier Device Package    | 32-QFN (5x5)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f582-im   |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 21.2. LIN0DAT: LIN0 Indirect Data Register                | 219 |

|--------------------------------------------------------------------------|-----|

| SFR Definition 21.3. LIN0CF: LIN0 Control Mode Register                  | 220 |

| SFR Definition 22.1. CAN0CFG: CAN Clock Configuration                    | 236 |

| SFR Definition 23.1. SMB0CF: SMBus Clock/Configuration                   |     |

| SFR Definition 23.2. SMB0CN: SMBus Control                               |     |

| SFR Definition 23.3. SMB0DAT: SMBus Data                                 | 247 |

| SFR Definition 24.1. SCON0: Serial Port 0 Control                        |     |

| SFR Definition 24.2. SMOD0: Serial Port 0 Control                        |     |

| SFR Definition 24.3. SBUF0: Serial (UART0) Port Data Buffer              |     |

| SFR Definition 24.4. SBCON0: UART0 Baud Rate Generator Control           | 261 |

| SFR Definition 24.6. SBRLL0: UART0 Baud Rate Generator Reload Low Byte   | 262 |

| SFR Definition 24.5. SBRLH0: UART0 Baud Rate Generator Reload High Byte  |     |

| SFR Definition 25.1. SCON1: Serial Port 1 Control                        |     |

| SFR Definition 25.2. SBUF1: Serial (UART1) Port Data Buffer              |     |

| SFR Definition 26.1. SPI0CFG: SPI0 Configuration                         |     |

| SFR Definition 26.2. SPI0CN: SPI0 Control                                |     |

| SFR Definition 26.3. SPI0CKR: SPI0 Clock Rate                            |     |

| SFR Definition 26.4. SPI0DAT: SPI0 Data                                  |     |

| SFR Definition 27.1. CKCON: Clock Control                                |     |

| SFR Definition 27.2. TCON: Timer Control                                 |     |

| SFR Definition 27.3. TMOD: Timer Mode                                    |     |

| SFR Definition 27.4. TL0: Timer 0 Low Byte                               |     |

| SFR Definition 27.5. TL1: Timer 1 Low Byte                               |     |

| SFR Definition 27.6. TH0: Timer 0 High Byte                              |     |

| SFR Definition 27.7. TH1: Timer 1 High Byte                              | 292 |

| SFR Definition 27.8. TMR2CN: Timer 2 Control                             |     |

| SFR Definition 27.9. TMR2RLL: Timer 2 Reload Register Low Byte           |     |

| SFR Definition 27.10. TMR2RLH: Timer 2 Reload Register High Byte         |     |

| SFR Definition 27.11. TMR2L: Timer 2 Low Byte                            |     |

| SFR Definition 27.12. TMR2H Timer 2 High Byte                            | 298 |

| SFR Definition 27.13. TMR3CN: Timer 3 Control                            | 302 |

| SFR Definition 27.14. TMR3RLL: Timer 3 Reload Register Low Byte          |     |

| SFR Definition 27.15. TMR3RLH: Timer 3 Reload Register High Byte         |     |

| SFR Definition 27.16. TMR3L: Timer 3 Low Byte                            |     |

| SFR Definition 27.17. TMR3H Timer 3 High Byte                            |     |

| SFR Definition 27.18. TMRnCN: Timer 4 and 5 Control                      |     |

| SFR Definition 27.19. TMRnCF: Timer 4 and 5 Configuration                |     |

| SFR Definition 27.20. TMRnCAPL: Timer 4 and 5 Capture Register Low Byte  |     |

| SFR Definition 27.21. TMRnCAPH: Timer 4 and 5 Capture Register High Byte |     |

| SFR Definition 27.22. TMRnL: Timer 4 and 5 Low Byte                      |     |

| SFR Definition 27.23. TMRnH Timer 4 and 5 High Byte                      |     |

| SFR Definition 28.1. PCA0CN: PCA0 Control                                |     |

| SFR Definition 28.2. PCA0MD: PCA0 Mode                                   |     |

| SFR Definition 28.3. PCA0PWM: PCA0 PWM Configuration                     |     |

| SFR Definition 28.4. PCA0CPMn: PCA0 Capture/Compare Mode                 | 328 |

|                                                                          |     |

# 3. Pin Definitions

| Name   | Pin<br>F580/1/4/5 | Pin<br>F588/9-<br>F590/1 | Pin<br>F582/3/6/7 | Туре          | Description                                                                                                                                  |

|--------|-------------------|--------------------------|-------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|        | (48-pin)          | (40-pin)                 | (32-pin)          |               |                                                                                                                                              |

| VDD    | 4                 | 4                        | 4                 |               | Digital Supply Voltage. Must be connected.                                                                                                   |

| GND    | 6                 | 6                        | 6                 |               | Digital Ground. Must be connected.                                                                                                           |

| VDDA   | 5                 | 5                        | 5                 |               | Analog Supply Voltage. Must be connected.                                                                                                    |

| GNDA   | 7                 | 7                        | 7                 |               | Analog Ground. Must be connected.                                                                                                            |

| VREGIN | 3                 | 3                        | 3                 |               | Voltage Regulator Input                                                                                                                      |

| VIO    | 2                 | 2                        | 2                 |               | Port I/O Supply Voltage. Must be connected.                                                                                                  |

| RST/   | 12                | 10                       | 10                | d I/O         | Device Reset. Open-drain output of internal POR or $V_{DD}$ Monitor. An external source can initiate a system reset by driving this pin low. |

| C2CK   |                   |                          |                   | D I/O         | Clock signal for the C2 Debug Interface.                                                                                                     |

| C2D    | 11                | _                        | _                 | D I/O         | Bi-directional data signal for the C2 Debug Interface.                                                                                       |

| P4.0/  | —                 | 9                        | _                 | D I/O or A In | Port 4.0. See SFR Definition 20.29 for a description.                                                                                        |

| C2D    |                   |                          |                   | D I/O         | Bi-directional data signal for the C2 Debug Interface.                                                                                       |

| P3.0/  | —                 |                          | 9                 | D I/O or A In | Port 3.0. See SFR Definition 20.25 for a description.                                                                                        |

| C2D    |                   |                          |                   | D I/O         | Bi-directional data signal for the C2 Debug Interface.                                                                                       |

| P0.0   | 8                 | 8                        | 8                 | D I/O or A In | Port 0.0. See SFR Definition 20.13 for a description.                                                                                        |

| P0.1   | 1                 | 1                        | 1                 | D I/O or A In | Port 0.1                                                                                                                                     |

| P0.2   | 48                | 40                       | 32                | D I/O or A In | Port 0.2                                                                                                                                     |

| P0.3   | 47                | 39                       | 31                | D I/O or A In | Port 0.3                                                                                                                                     |

| P0.4   | 46                | 38                       | 30                | D I/O or A In | Port 0.4                                                                                                                                     |

| P0.5   | 45                | 37                       | 29                | D I/O or A In | Port 0.5                                                                                                                                     |

Table 3.1. Pin Definitions for the C8051F58x/F59x

# Table 5.11. Temperature Sensor Electrical Characteristics

VDDA = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter                                               | Conditions  | Min | Тур   | Max | Units |  |

|---------------------------------------------------------|-------------|-----|-------|-----|-------|--|

| Linearity                                               |             | _   | ± 0.1 | _   | °C    |  |

| Slope                                                   |             | _   | 3.33  | _   | mV/°C |  |

| Slope Error*                                            |             | _   | 100   | —   | µV/°C |  |

| Offset                                                  | Temp = 0 °C | _   | 856   | —   | mV    |  |

| Offset Error*                                           | Temp = 0 °C | _   | 12    | —   | mV    |  |

| Power Supply Current                                    |             | _   | 22    | _   | μA    |  |

| Tracking Time                                           |             | 12  |       | —   | μs    |  |

| *Note: Represents one standard deviation from the mean. |             |     |       |     |       |  |

# Table 5.12. Voltage Reference Electrical Characteristics

VDDA = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter                       | Conditions                                  | Min  | Тур  | Мах       | Units  |

|---------------------------------|---------------------------------------------|------|------|-----------|--------|

| Internal Reference (REFBE       | = 1)                                        | 1    | 1    | 1         |        |

| Output Voltage                  | 25 °C ambient (REFLV = 0)                   | 1.45 | 1.50 | 1.55      | v      |

|                                 | 25 °C ambient (REFLV = 1), $V_{DD}$ = 2.6 V | 2.15 | 2.20 | 2.25      | V      |

| VREF Short-Circuit Current      |                                             | —    | 5    | 10        | mA     |

| VREF Temperature<br>Coefficient |                                             | _    | 22   |           | ppm/°C |

| Power Consumption               | Internal                                    | _    | 30   | 50        | μA     |

| Load Regulation                 | Load = 0 to 200 µA to AGND                  | _    | 3    |           | μV/μA  |

| VREF Turn-on Time 1             | 4.7 $\mu$ F and 0.1 $\mu$ F bypass          |      | 1.5  |           | ms     |

| VREF Turn-on Time 2             | 0.1 μF bypass                               |      | 46   |           | μs     |

| Power Supply Rejection          |                                             | —    | 1.2  | —         | mV/V   |

| External Reference (REFBI       | E = 0)                                      | 1    | 1    |           |        |

| Input Voltage Range             |                                             | 1.5  | _    | $V_{DDA}$ | V      |

| Input Current                   | Sample Rate = 200 ksps; VREF = 1.5 V        |      | 2.5  |           | μA     |

| Power Specifications            |                                             | 1    | 1    |           |        |

| Reference Bias Generator        | REFBE = 1 or TEMPE = 1                      |      | 21   | 40        | μA     |

## SFR Definition 6.8. ADC0TK: ADC0 Tracking Mode Select

| Bit   | 7 | 6     | 5       | 4 | 3          | 2 | 1          | 0 |

|-------|---|-------|---------|---|------------|---|------------|---|

| Name  |   | AD0PV | VR[3:0] |   | AD0TM[1:0] |   | AD0TK[1:0] |   |

| Туре  |   | R/    | W       |   | R/W        |   | R/W        |   |

| Reset | 1 | 1     | 1       | 1 | 1          | 1 | 1          | 1 |

SFR Address = 0xBA; SFR Page = 0x00;

| Bit | Name        | Function                                                                                                                                                                                   |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | AD0PWR[3:0] |                                                                                                                                                                                            |

|     |             | For BURSTEN = 0: ADC0 Power state controlled by AD0EN<br>For BURSTEN = 1, AD0EN = 1: ADC0 remains enabled and does not enter the<br>very low power state                                   |

|     |             | For BURSTEN = 1, AD0EN = 0: ADC0 enters the very low power state and is<br>enabled after each convert start signal. The Power-Up time is programmed accord-<br>ing the following equation: |

|     |             | $AD0PWR = \frac{Tstartup}{200ns} - 1 \text{ or } Tstartup = (AD0PWR + 1)200ns$                                                                                                             |

| 3:2 | AD0TM[1:0]  | ADC0 Tracking Mode Enable Select Bits.                                                                                                                                                     |

|     |             | 00: Reserved.                                                                                                                                                                              |

|     |             | 01: ADC0 is configured to Post-Tracking Mode.                                                                                                                                              |

|     |             | 10: ADC0 is configured to Pre-Tracking Mode.<br>11: ADC0 is configured to Dual Tracking Mode.                                                                                              |

| 1.0 |             | ADC0 Post-Track Time.                                                                                                                                                                      |

| 1:0 | AD0TK[1:0]  |                                                                                                                                                                                            |

|     |             | 00: Post-Tracking time is equal to 2 SAR clock cycles + 2 FCLK cycles.<br>01: Post-Tracking time is equal to 4 SAR clock cycles + 2 FCLK cycles.                                           |

|     |             | 10: Post-Tracking time is equal to 8 SAR clock cycles + 2 FCLK cycles.                                                                                                                     |

|     |             | 11: Post-Tracking time is equal to 16 SAR clock cycles + 2 FCLK cycles.                                                                                                                    |

## 6.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

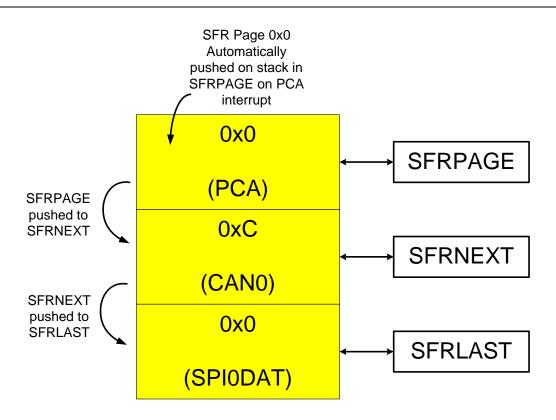

## Figure 13.4. SFR Page Stack Upon PCA Interrupt Occurring During a CAN0 ISR

On exit from the PCA interrupt service routine, the CIP-51 will return to the CAN0 ISR. On execution of the RETI instruction, SFR Page 0x00 used to access the PCA registers will be automatically popped off of the SFR Page Stack, and the contents of the SFRNEXT register will be moved to the SFRPAGE register. Software in the CAN0 ISR can continue to access SFRs as it did prior to the PCA interrupt. Likewise, the contents of SFRLAST are moved to the SFRNEXT register. Recall this was the SFR Page value 0x00 being used to access SPI0DAT before the CAN0 interrupt occurred. See Figure 13.5.

# SFR Definition 14.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0xA8; Bit-Addressable; SFR Page = All Pages

| Bit | Name  | Function                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <ul> <li>Enable All Interrupts.</li> <li>Globally enables/disables all interrupts. It overrides individual interrupt mask settings.</li> <li>0: Disable all interrupt sources.</li> <li>1: Enable each interrupt according to its individual mask setting.</li> </ul> |

| 6   | ESPI0 | <ul> <li>Enable Serial Peripheral Interface (SPI0) Interrupt.</li> <li>This bit sets the masking of the SPI0 interrupts.</li> <li>0: Disable all SPI0 interrupts.</li> <li>1: Enable interrupt requests generated by SPI0.</li> </ul>                                 |

| 5   | ET2   | <ul> <li>Enable Timer 2 Interrupt.</li> <li>This bit sets the masking of the Timer 2 interrupt.</li> <li>0: Disable Timer 2 interrupt.</li> <li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li> </ul>                                          |

| 4   | ES0   | Enable UART0 Interrupt.<br>This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.<br>1: Enable UART0 interrupt.                                                                                                                             |

| 3   | ET1   | <ul> <li>Enable Timer 1 Interrupt.</li> <li>This bit sets the masking of the Timer 1 interrupt.</li> <li>0: Disable all Timer 1 interrupt.</li> <li>1: Enable interrupt requests generated by the TF1 flag.</li> </ul>                                                |

| 2   | EX1   | <ul> <li>Enable External Interrupt 1.</li> <li>This bit sets the masking of External Interrupt 1.</li> <li>0: Disable external interrupt 1.</li> <li>1: Enable interrupt requests generated by the INT1 input.</li> </ul>                                             |

| 1   | ET0   | <ul> <li>Enable Timer 0 Interrupt.</li> <li>This bit sets the masking of the Timer 0 interrupt.</li> <li>0: Disable all Timer 0 interrupt.</li> <li>1: Enable interrupt requests generated by the TF0 flag.</li> </ul>                                                |

| 0   | EX0   | <ul> <li>Enable External Interrupt 0.</li> <li>This bit sets the masking of External Interrupt 0.</li> <li>0: Disable external interrupt 0.</li> <li>1: Enable interrupt requests generated by the INTO input.</li> </ul>                                             |

# SFR Definition 14.2. IP: Interrupt Priority

| Bit   | 7          | 6                                                                                                                                                                                                                        | 5                                                                                                                                                                                                                        | 4                              | 3              | 2             | 1 | 0 |  |

|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|---------------|---|---|--|

| Nam   | e          | PSPI0                                                                                                                                                                                                                    | PSPI0 PT2 PS0 PT1 PX1 PT0                                                                                                                                                                                                |                                |                |               |   |   |  |

| Туре  | R R        | R/W R/W R/W R/W R/W                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                |                |               |   |   |  |

| Rese  | t 1        | 0                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                        | 0                              | 0              | 0             | 0 | 0 |  |

| SFR A | ddress = 0 | xB8; Bit-Addres                                                                                                                                                                                                          | sable; SFR                                                                                                                                                                                                               | Page = All F                   | Pages          |               |   |   |  |

| Bit   | Name       |                                                                                                                                                                                                                          |                                                                                                                                                                                                                          |                                | Function       |               |   |   |  |

| 7     | Unused     | Read = 1b, W                                                                                                                                                                                                             | rite = Don't (                                                                                                                                                                                                           | Care.                          |                |               |   |   |  |

| 6     | PSPI0      | Serial Periph<br>This bit sets th<br>0: SPI0 interru<br>1: SPI0 interru                                                                                                                                                  | ne priority of<br>opt set to low                                                                                                                                                                                         | the SPI0 int                   | errupt.<br>el. | rity Control. |   |   |  |

| 5     | PT2        | <b>Timer 2 Intern</b><br>This bit sets th<br>0: Timer 2 inter<br>1: Timer 2 inter                                                                                                                                        | ne priority of<br>errupt set to                                                                                                                                                                                          | the Timer 2<br>low priority le | evel.          |               |   |   |  |

| 4     | PS0        | This bit sets th<br>0: UART0 inte                                                                                                                                                                                        | UART0 Interrupt Priority Control.<br>This bit sets the priority of the UART0 interrupt.<br>0: UART0 interrupt set to low priority level.<br>1: UART0 interrupt set to high priority level.                               |                                |                |               |   |   |  |

| 3     | PT1        | This bit sets th<br>0: Timer 1 inte                                                                                                                                                                                      | Timer 1 Interrupt Priority Control.         This bit sets the priority of the Timer 1 interrupt.         0: Timer 1 interrupt set to low priority level.         1: Timer 1 interrupt set to high priority level.        |                                |                |               |   |   |  |

| 2     | PX1        | This bit sets th<br>0: External Int                                                                                                                                                                                      | External Interrupt 1 Priority Control.<br>This bit sets the priority of the External Interrupt 1 interrupt.<br>D: External Interrupt 1 set to low priority level.<br>1: External Interrupt 1 set to high priority level. |                                |                |               |   |   |  |

| 1     | PT0        | This bit sets th<br>0: Timer 0 inte                                                                                                                                                                                      | Timer 0 Interrupt Priority Control.         This bit sets the priority of the Timer 0 interrupt.         0: Timer 0 interrupt set to low priority level.         1: Timer 0 interrupt set to high priority level.        |                                |                |               |   |   |  |

| 0     | PX0        | External Interrupt 0 Priority Control.<br>This bit sets the priority of the External Interrupt 0 interrupt.<br>D: External Interrupt 0 set to low priority level.<br>1: External Interrupt 0 set to high priority level. |                                                                                                                                                                                                                          |                                |                |               |   |   |  |

input voltage (on CP0+) is less than the inverting input voltage (on CP0–), the device is put into the reset state. After a Comparator0 reset, the C0RSEF flag (RST<u>SRC</u>.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

# 17.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA0) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "28.4. Watchdog Timer Mode" on page 324; the WDT is enabled and clocked by SYSCLK/12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

## 17.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address above address 0xFBFF in Bank 3 on C8051F580/1/2/3/8/9 or any address in Bank 3 on C8051F584/5/6/7-F590/1 devices.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above address 0xFBFF in Bank 3 on C8051F580/1/2/3/8/9 or any address in Bank 3 on C8051F584/5/6/7-F590/1 devices.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above 0xFBFF in Bank 3 on C8051F580/1/2/3/8/9 or any address in Bank 3 on C8051F584/5/6/7-F590/1 devices.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "15.3. Security Options" on page 141).

- A Flash read, write, or erase is attempted when the VDD Monitor is not enabled to the high threshold and set as a reset source

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

# 17.8. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the RST pin is unaffected by this reset.

## 19.4. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 19.1. A 10 M $\Omega$  resistor also must be wired across the XTAL2 and XTAL1 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 19.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 19.6).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.2 and P0.3 are used as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.3 is used as XTAL2. The Port I/O Crossbar should be configured to skip the Port pins used by the oscillator circuit; see Section "20.3. Priority Crossbar Decoder" on page 192 for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as **analog inputs**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See Section "20.4. Port I/O Initialization" on page 195 for details on Port input mode selection.

# SFR Definition 21.3. LIN0CF: LIN0 Control Mode Register

| Bit   | 7     | 6    | 5     | 4 | 3 | 2 | 1 | 0 |

|-------|-------|------|-------|---|---|---|---|---|

|       |       |      |       |   |   |   |   |   |

| Name  | LINEN | MODE | ABAUD |   |   |   |   |   |

|       |       |      |       |   |   |   |   |   |

| Туре  | R/W   | R/W  | R/W   | R | R | R | R | R |

|       | 0     | 4    | 4     | 0 | 0 | 0 | 0 | 0 |

| Reset | 0     | ľ    | 1     | 0 | 0 | 0 | 0 | 0 |

|       |       |      |       |   |   |   |   |   |

### SFR Address = 0xC9; SFR Page = 0x0F

| Bit | Name   | Function                                                                                                                                                                                                            |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | LINEN  | LIN Interface Enable Bit.<br>0: LIN0 is disabled.<br>1: LIN0 is enabled.                                                                                                                                            |

| 6   | MODE   | LIN Mode Selection Bit.<br>0: LIN0 operates in slave mode.<br>1: LIN0 operates in master mode.                                                                                                                      |

| 5   | ABAUD  | LIN Mode Automatic Baud Rate Selection.<br>This bit only has an effect when the MODE bit is configured for slave mode.<br>0: Manual baud rate selection is enabled.<br>1: Automatic baud rate selection is enabled. |

| 4:0 | Unused | Read = 00000b; Write = Don't Care                                                                                                                                                                                   |

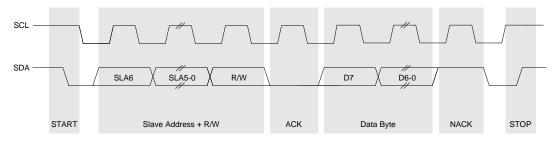

All transactions are initiated by a master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the slave address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time waiting for an ACK from the slave at the end of each byte. For READ operations, the slave transmits the data waiting for an ACK from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 23.3 illustrates a typical SMBus transaction.

Figure 23.3. SMBus Transaction

### 23.3.1. Transmitter Vs. Receiver

On the SMBus communications interface, a device is the "transmitter" when it is sending an address or data byte to another device on the bus. A device is a "receiver" when an address or data byte is being sent to it from another device on the bus. The transmitter controls the SDA line during the address or data byte. After each byte of address or data information is sent by the transmitter, the receiver sends an ACK or NACK bit during the ACK phase of the transfer, during which time the receiver controls the SDA line.

#### 23.3.2. Arbitration

A master may start a transfer only if the bus is free. The bus is free after a STOP condition or after the SCL and SDA lines remain high for a specified time (see Section "23.3.5. SCL High (SMBus Free) Timeout" on page 242). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one master to give up the bus. The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW. Since the bus is open-drain, the bus will be pulled LOW. The master attempting the HIGH will detect a LOW SDA and lose the arbitration. The winning master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer if addressed. This arbitration scheme is non-destructive: one device always wins, and no data is lost.

#### 23.3.3. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I<sup>2</sup>C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 23.3.4. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

When the SMBTOE bit in SMB0CF is set, Timer 3 is used to detect SCL low timeouts. Timer 3 is forced to reload when SCL is high, and allowed to count when SCL is low. With Timer 3 enabled and configured to

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 23.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                                                                                                                                                                                                                                                                                                          | Minimum SDA Setup Time             | Minimum SDA Hold Time |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|--|--|--|--|

| 0                                                                                                                                                                                                                                                                                                                | T <sub>low</sub> – 4 system clocks | 3 system clocks       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                  | or                                 |                       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                  | 1 system clock + s/w delay*        |                       |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                | 11 system clocks                   | 12 system clocks      |  |  |  |  |

| *Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. When using software acknowledgement, the s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero. |                                    |                       |  |  |  |  |

Table 23.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "23.3.4. SCL Low Timeout" on page 241). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 23.4).

## 24.3. Configuration and Operation

UART0 provides standard asynchronous, full duplex communication. It can operate in a point-to-point serial communications application, or as a node on a multi-processor serial interface. To operate in a point-to-point application, where there are only two devices on the serial bus, the MCE0 bit in SMOD0 should be cleared to 0. For operation as part of a multi-processor communications bus, the MCE0 and XBE0 bits should both be set to 1. In both types of applications, data is transmitted from the microcontroller on the TX0 pin, and received on the RX0 pin. The TX0 and RX0 pins are configured using the crossbar and the Port I/O registers, as detailed in Section "20. Port Input/Output" on page 188.

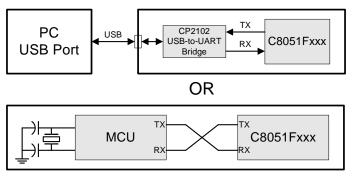

In typical UART communications, The transmit (TX) output of one device is connected to the receive (RX) input of the other device, either directly or through a bus transceiver, as shown in Figure 24.5.

Figure 24.5. Typical UART Interconnect Diagram

#### 24.3.1. Data Transmission

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) will be set at the end of any transmission (the beginning of the stop-bit time). If enabled, an interrupt will occur when TI0 is set.

**Note:** THRE0 can have a momentary glitch high when the UART Transmit Holding Register is not empty. The glitch will occur some time after SBUF0 was written with the previous byte and does not occur if THRE0 is checked in the instruction(s) immediately following the write to SBUF0. When firmware writes SBUF0 and SBUF0 is not empty, TX0 will be stuck low until the next device reset. Firmware should use or poll on TI0 rather than THRE0 for asynchronous UART writes that may have a random delay in between transactions.

If the extra bit function is enabled (XBE0 = 1) and the parity function is disabled (PE0 = 0), the value of the TBX0 (SCON0.3) bit will be sent in the extra bit position. When the parity function is enabled (PE0 = 1), hardware will generate the parity bit according to the selected parity type (selected with S0PT[1:0]), and append it to the data field. Note: when parity is enabled, the extra bit function is not available.

#### 24.3.2. Data Reception

Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be stored in the receive FIFO if the following conditions are met: the receive FIFO (3 bytes deep) must not be full, and the stop bit(s) must be logic 1. In the event that the receive FIFO is full, the incoming byte will be lost, and a Receive FIFO Overrun Error will be generated (OVR0 in register SCON0 will be set to logic 1). If the stop bit(s) were logic 0, the incoming data will not be stored in the receive FIFO. If the reception conditions are met, the data is stored in the receive FIFO, and the RI0 flag will be set. Note: when MCE0 = 1, RI0 will only be set if the extra bit was equal to 1. Data can be read from the receive FIFO by reading the SBUF0 register. The SBUF0 register represents the oldest byte in the FIFO. After SBUF0 is read, the next byte in the FIFO is immediately loaded into SBUF0, and space is made available in the FIFO for another incoming byte. If enabled, an interrupt will occur when RI0

# SFR Definition 26.2. SPI0CN: SPI0 Control

| Bit   | 7             | 6                                                                                                                                                                                                                                                                               | 5                                                                                                                                                                                                                                                                                                                                                                                            | 4           | 3     | 2       | 1     | 0     |  |  |

|-------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|---------|-------|-------|--|--|

| Name  | SPIF          | WCOL                                                                                                                                                                                                                                                                            | MODF                                                                                                                                                                                                                                                                                                                                                                                         | RXOVRN      | NSSM  | ID[1:0] | TXBMT | SPIEN |  |  |

| Туре  | R/W           | R/W                                                                                                                                                                                                                                                                             | R/W                                                                                                                                                                                                                                                                                                                                                                                          | R/W         | R/W R |         | R     | R/W   |  |  |

| Reset | t 0           | 0                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                            | 0           | 0     | 1       | 1     | 0     |  |  |

| SFR A | ddress = 0xF8 | ; Bit-Addres                                                                                                                                                                                                                                                                    | sable; SFR                                                                                                                                                                                                                                                                                                                                                                                   | Page = 0x00 | )     | I       |       |       |  |  |

| Bit   | Name          |                                                                                                                                                                                                                                                                                 | Function                                                                                                                                                                                                                                                                                                                                                                                     |             |       |         |       |       |  |  |

| 7     | SPIF          | This bit is enabled, s                                                                                                                                                                                                                                                          | <b>SPI0 Interrupt Flag.</b><br>This bit is set to logic 1 by hardware at the end of a data transfer. If interrupts are enabled, setting this bit causes the CPU to vector to the SPI0 interrupt service routine. This bit is not automatically cleared by hardware. It must be cleared by software.                                                                                          |             |       |         |       |       |  |  |

| 6     | WCOL          | This bit is write to the                                                                                                                                                                                                                                                        | Write Collision Flag.<br>This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) to indicate a write to the SPI0 data register was attempted while a data transfer was in progress.<br>It must be cleared by software.                                                                                                                                                       |             |       |         |       |       |  |  |

| 5     | MODF          | <b>Mode Fault Flag.</b><br>This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) when a master mode collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01).<br>This bit is not automatically cleared by hardware. It must be cleared by software. |                                                                                                                                                                                                                                                                                                                                                                                              |             |       |         |       |       |  |  |

| 4     | RXOVRN        | Receive C                                                                                                                                                                                                                                                                       | Receive Overrun Flag (valid in slave mode only).                                                                                                                                                                                                                                                                                                                                             |             |       |         |       |       |  |  |

|       |               | receive bu<br>current tra                                                                                                                                                                                                                                                       | This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) when the receive buffer still holds unread data from a previous transfer and the last bit of the current transfer is shifted into the SPI0 shift register. This bit is not automatically cleared by hardware. It must be cleared by software.                                                                        |             |       |         |       |       |  |  |

| 3:2   | NSSMD[1:0]    | Slave Sel                                                                                                                                                                                                                                                                       | Slave Select Mode.                                                                                                                                                                                                                                                                                                                                                                           |             |       |         |       |       |  |  |

|       | -             | (See Sect<br>00: 3-Wire<br>01: 4-Wire<br>1x: 4-Wire                                                                                                                                                                                                                             | Selects between the following NSS operation modes:<br>(See Section 26.2 and Section 26.3).<br>00: 3-Wire Slave or 3-Wire Master Mode. NSS signal is not routed to a port pin.<br>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is an input to the device.<br>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the<br>device and will assume the value of NSSMD0. |             |       |         |       |       |  |  |

| 1     | TXBMT         | Transmit                                                                                                                                                                                                                                                                        | Buffer Emp                                                                                                                                                                                                                                                                                                                                                                                   | oty.        |       |         |       |       |  |  |

|       |               | This bit will be set to logic 0 when new data has been written to the transmit buffer.<br>When data in the transmit buffer is transferred to the SPI shift register, this bit will<br>be set to logic 1, indicating that it is safe to write a new byte to the transmit buffer. |                                                                                                                                                                                                                                                                                                                                                                                              |             |       |         |       |       |  |  |

| 0     | SPIEN         | SPI0 Enable.<br>0: SPI disabled.<br>1: SPI enabled.                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                              |             |       |         |       |       |  |  |

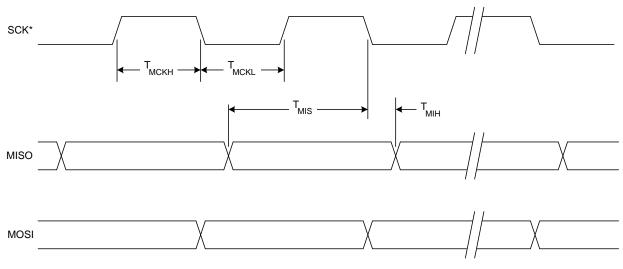

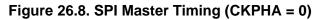

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

## Figure 26.9. SPI Master Timing (CKPHA = 1)

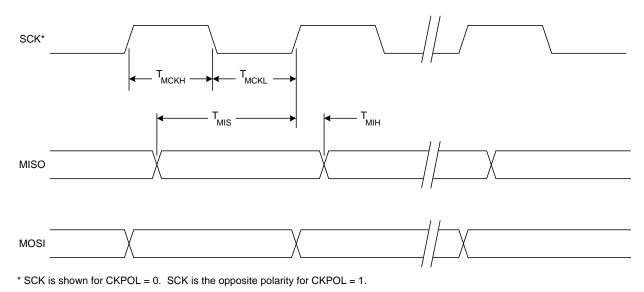

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 27.5. Timer 2 8-Bit Mode Block Diagram

### 27.2.3. External Oscillator Capture Mode

Capture Mode allows the external oscillator to be measured against the system clock. Timer 2 can be clocked from the system clock, or the system clock divided by 12, depending on the T2ML (CKCON.4), and T2XCLK bits. When a capture event is generated, the contents of Timer 2 (TMR2H:TMR2L) are loaded into the Timer 2 reload registers (TMR2RLH:TMR2RLL) and the TF2H flag is set. A capture event is generated by the falling edge of the clock source being measured, which is the external oscillator / 8. By recording the difference between two successive timer capture values, the external oscillator frequency can be determined with respect to the Timer 2 clock. The Timer 2 clock should be much faster than the capture clock to achieve an accurate reading. Timer 2 should be in 16-bit auto-reload mode when using Capture Mode.

For example, if T2ML = 1b and TF2CEN = 1b, Timer 2 will clock every SYSCLK and capture every external clock divided by 8. If the SYSCLK is 24 MHz and the difference between two successive captures is 5984, then the external clock frequency is as follows:

24 MHz/(5984/8) = 0.032086 MHz or 32.086 kHz

This mode allows software to determine the external oscillator frequency when an RC network or capacitor is used to generate the clock source.

# SFR Definition 28.2. PCA0MD: PCA0 Mode

| Bit   | 7                                                                                                                                                                                               | 6                                                                                                                                                                                                                                                                                                                                                                                                                          | 5        | 4 | 3    | 2    | 1    | 0        |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|------|------|------|----------|--|

| Name  | CIDL                                                                                                                                                                                            | WDTE                                                                                                                                                                                                                                                                                                                                                                                                                       | WDLCK    |   | CPS2 | CPS1 | CPS0 | ECF      |  |

| Туре  | R/W                                                                                                                                                                                             | R/W                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W      | R | R/W  | R/W  | R/W  | R/W      |  |

| Rese  | t 0                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                          | 0        | 0 | 0    | 0    | 0    | 0        |  |

| SFR A | ddress = 0                                                                                                                                                                                      | kD9; SFR Page                                                                                                                                                                                                                                                                                                                                                                                                              | e = 0x00 |   |      |      |      |          |  |

| Bit   | Name                                                                                                                                                                                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                   |          |   |      |      |      |          |  |

| 7     | CIDL                                                                                                                                                                                            | <ul> <li>PCA0 Counter/Timer Idle Control.</li> <li>Specifies PCA0 behavior when CPU is in Idle Mode.</li> <li>0: PCA0 continues to function normally while the system controller is in Idle Mode.</li> <li>1: PCA0 operation is suspended while the system controller is in Idle Mode.</li> </ul>                                                                                                                          |          |   |      |      |      |          |  |

| 6     | WDTE                                                                                                                                                                                            | Watchdog Timer EnableIf this bit is set, PCA0 Module 5 is used as the watchdog timer.0: Watchdog Timer disabled.1: PCA0 Module 5 enabled as Watchdog Timer.                                                                                                                                                                                                                                                                |          |   |      |      |      |          |  |

| 5     | WDLCK                                                                                                                                                                                           | <ul> <li>Watchdog Timer Lock</li> <li>This bit locks/unlocks the Watchdog Timer Enable. When WDLCK is set, the Watchdog</li> <li>Timer may not be disabled until the next system reset.</li> <li>0: Watchdog Timer Enable unlocked.</li> <li>1: Watchdog Timer Enable locked.</li> </ul>                                                                                                                                   |          |   |      |      |      |          |  |

| 4     | Unused                                                                                                                                                                                          | Read = 0b, Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                             |          |   |      |      |      |          |  |

| 3:1   | CPS[2:0]                                                                                                                                                                                        | PCA0 Counter/Timer Pulse Select.<br>These bits select the timebase source for the PCA0 counter<br>000: System clock divided by 12<br>001: System clock divided by 4<br>010: Timer 0 overflow<br>011: High-to-low transitions on ECI (max rate = system clock divided by 4)<br>100: System clock<br>101: External clock divided by 8 (synchronized with the system clock)<br>110: Timer 4 overflow<br>111: Timer 5 overflow |          |   |      |      |      |          |  |

| 0     | ECF                                                                                                                                                                                             | <ul> <li>PCA0 Counter/Timer Overflow Interrupt Enable.</li> <li>This bit sets the masking of the PCA0 Counter/Timer Overflow (CF) interrupt.</li> <li>0: Disable the CF interrupt.</li> <li>1: Enable a PCA0 Counter/Timer Overflow interrupt request when CF (PCA0CN.7) is set.</li> </ul>                                                                                                                                |          |   |      |      |      |          |  |

| Note: | <b>Note:</b> When the WDTE bit is set to 1, the other bits in the PCA0MD register cannot be modified. To change the contents of the PCA0MD register, the Watchdog Timer must first be disabled. |                                                                                                                                                                                                                                                                                                                                                                                                                            |          |   |      |      |      | ange the |  |

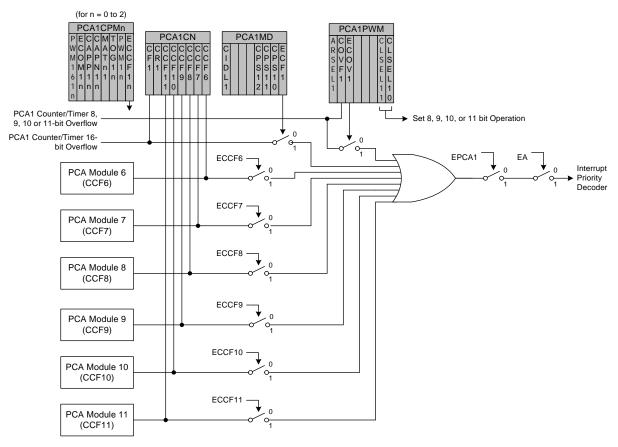

## 29.2. PCA1 Interrupt Sources

Figure 29.3 shows a diagram of the PCA1 interrupt tree. There are five independent event flags that can be used to generate a PCA1 interrupt. They are as follows: the main PCA1 counter overflow flag (CF1), which is set upon a 16-bit overflow of the PCA1 counter, an intermediate overflow flag (COVF1), which can be set on an overflow from the 8th, 9th, 10th, or 11th bit of the PCA1 counter, and the individual flags for each PCA1 channel (CCF6, CCF7, CCF8, CCF9, CCF10 and CCF11), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA1 interrupt, using the corresponding interrupt enable flag (ECF1 for CF1, ECOV1 for COVF1, and ECCF1n for each CCFn). PCA1 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA1 interrupts are globally enabled by setting the EA bit and the EPCA1 bit to logic 1.

Figure 29.3. PCA1 Interrupt Block Diagram

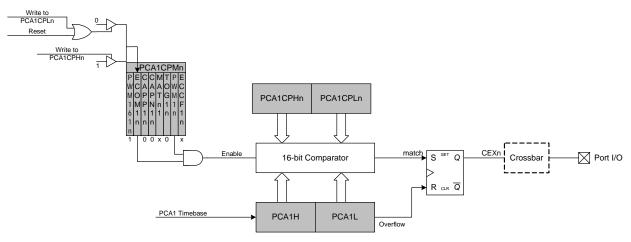

#### 29.3.6. 16-Bit Pulse Width Modulator Mode

A PCA1 module may also be operated in 16-Bit PWM mode. 16-bit PWM mode is independent of the other (8/9/10/11-bit) PWM modes. In this mode, the 16-bit capture/compare module defines the number of PCA1 clocks for the low time of the PWM signal. When the PCA1 counter matches the module contents, the output on CEXn is asserted high; when the 16-bit counter overflows, CEXn is asserted low. To output a varying duty cycle, new value writes should be synchronized with PCA1 CCFn match interrupts. 16-Bit PWM Mode is enabled by setting the ECOM1n, PWM1n, and PWM161n bits in the PCA1CPMn register. For a varying duty cycle, match interrupts should be enabled (ECCF1n = 1 AND MAT1n = 1) to help synchronize the capture/compare register writes. If the MAT1n bit is set to 1, the CCFn flag for the module will be set each time a 16-bit comparator match (rising edge) occurs. The CF1 flag in PCA1CN can be used to detect the overflow (falling edge). The duty cycle for 16-Bit PWM Mode is given by Equation 29.4.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA1 Capture/Compare registers, the low byte should always be written first. Writing to PCA1CPLn clears the ECOM1n bit to 0; writing to PCA1CPHn sets ECOM1n to 1.

Duty Cycle =  $\frac{(65536 - PCA1CPn)}{65536}$

Equation 29.4. 16-Bit PWM Duty Cycle

Using Equation 29.4, the largest duty cycle is 100% (PCA1CPn = 0), and the smallest duty cycle is 0.0015% (PCA1CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOM1n bit to 0.

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

# http://www.silabs.com