#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 128KB (128K x 8)                                               |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 8.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 25x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-LQFP                                                        |

| Supplier Device Package    | 32-LQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f583-iq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 21.2. LIN0DAT: LIN0 Indirect Data Register                | 219 |

|--------------------------------------------------------------------------|-----|

| SFR Definition 21.3. LIN0CF: LIN0 Control Mode Register                  | 220 |

| SFR Definition 22.1. CAN0CFG: CAN Clock Configuration                    | 236 |

| SFR Definition 23.1. SMB0CF: SMBus Clock/Configuration                   |     |

| SFR Definition 23.2. SMB0CN: SMBus Control                               |     |

| SFR Definition 23.3. SMB0DAT: SMBus Data                                 | 247 |

| SFR Definition 24.1. SCON0: Serial Port 0 Control                        |     |

| SFR Definition 24.2. SMOD0: Serial Port 0 Control                        |     |

| SFR Definition 24.3. SBUF0: Serial (UART0) Port Data Buffer              |     |

| SFR Definition 24.4. SBCON0: UART0 Baud Rate Generator Control           | 261 |

| SFR Definition 24.6. SBRLL0: UART0 Baud Rate Generator Reload Low Byte   | 262 |

| SFR Definition 24.5. SBRLH0: UART0 Baud Rate Generator Reload High Byte  |     |

| SFR Definition 25.1. SCON1: Serial Port 1 Control                        |     |

| SFR Definition 25.2. SBUF1: Serial (UART1) Port Data Buffer              |     |

| SFR Definition 26.1. SPI0CFG: SPI0 Configuration                         |     |

| SFR Definition 26.2. SPI0CN: SPI0 Control                                |     |

| SFR Definition 26.3. SPI0CKR: SPI0 Clock Rate                            |     |

| SFR Definition 26.4. SPI0DAT: SPI0 Data                                  |     |

| SFR Definition 27.1. CKCON: Clock Control                                |     |

| SFR Definition 27.2. TCON: Timer Control                                 |     |

| SFR Definition 27.3. TMOD: Timer Mode                                    |     |

| SFR Definition 27.4. TL0: Timer 0 Low Byte                               |     |

| SFR Definition 27.5. TL1: Timer 1 Low Byte                               |     |

| SFR Definition 27.6. TH0: Timer 0 High Byte                              |     |

| SFR Definition 27.7. TH1: Timer 1 High Byte                              | 292 |

| SFR Definition 27.8. TMR2CN: Timer 2 Control                             |     |

| SFR Definition 27.9. TMR2RLL: Timer 2 Reload Register Low Byte           |     |

| SFR Definition 27.10. TMR2RLH: Timer 2 Reload Register High Byte         |     |

| SFR Definition 27.11. TMR2L: Timer 2 Low Byte                            |     |

| SFR Definition 27.12. TMR2H Timer 2 High Byte                            | 298 |

| SFR Definition 27.13. TMR3CN: Timer 3 Control                            | 302 |

| SFR Definition 27.14. TMR3RLL: Timer 3 Reload Register Low Byte          |     |

| SFR Definition 27.15. TMR3RLH: Timer 3 Reload Register High Byte         |     |

| SFR Definition 27.16. TMR3L: Timer 3 Low Byte                            |     |

| SFR Definition 27.17. TMR3H Timer 3 High Byte                            |     |

| SFR Definition 27.18. TMRnCN: Timer 4 and 5 Control                      |     |

| SFR Definition 27.19. TMRnCF: Timer 4 and 5 Configuration                |     |

| SFR Definition 27.20. TMRnCAPL: Timer 4 and 5 Capture Register Low Byte  |     |

| SFR Definition 27.21. TMRnCAPH: Timer 4 and 5 Capture Register High Byte |     |

| SFR Definition 27.22. TMRnL: Timer 4 and 5 Low Byte                      |     |

| SFR Definition 27.23. TMRnH Timer 4 and 5 High Byte                      |     |

| SFR Definition 28.1. PCA0CN: PCA0 Control                                |     |

| SFR Definition 28.2. PCA0MD: PCA0 Mode                                   |     |

| SFR Definition 28.3. PCA0PWM: PCA0 PWM Configuration                     |     |

| SFR Definition 28.4. PCA0CPMn: PCA0 Capture/Compare Mode                 | 328 |

|                                                                          |     |

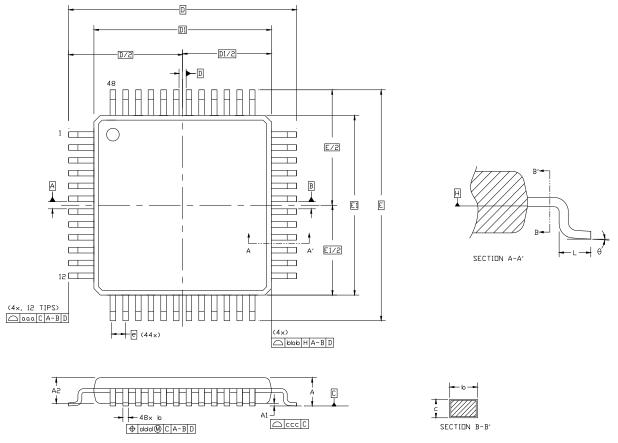

## 4. Package Specifications

### 4.1. QFP-48 Package Specifications

#### Figure 4.1. QFP-48 Package Drawing

| Dimension | Min       | Тур       | Max  | Dimension | Min       | Тур  | Мах  |  |

|-----------|-----------|-----------|------|-----------|-----------|------|------|--|

| А         | _         | —         | 1.20 | E         | 9.00 BSC. |      |      |  |

| A1        | 0.05      | _         | 0.15 | E1        | 7.00 BSC. |      |      |  |

| A2        | 0.95      | 1.00      | 1.05 | L         | 0.45      | 0.60 | 0.75 |  |

| b         | 0.17      | 0.22      | 0.27 | aaa       | 0.20      |      |      |  |

| С         | 0.09      | _         | 0.20 | bbb       |           | 0.20 |      |  |

| D         | 9.00 BSC. |           |      | CCC       |           | 0.08 |      |  |

| D1        | 7.00 BSC. |           |      | ddd       | 0.08      |      |      |  |

| е         |           | 0.50 BSC. |      | θ         | 0°        | 3.5° | 7°   |  |

#### Table 4.1. QFP-48 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC outline MS-026, variation ABC.

- Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### SFR Definition 6.11. ADC0LTH: ADC0 Less-Than Data High Byte

| Bit   | 7             | 6            | 5                                         | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---------------|--------------|-------------------------------------------|---|---|---|---|---|--|--|--|

| Nam   | e             | ADC0LTH[7:0] |                                           |   |   |   |   |   |  |  |  |

| Туре  | 9             | R/W          |                                           |   |   |   |   |   |  |  |  |

| Rese  | et O          | 0            | 0                                         | 0 | 0 | 0 | 0 | 0 |  |  |  |

| SFR A | ddress = 0xC6 | ; SFR Page   | e = 0x00                                  |   |   |   |   |   |  |  |  |

| Bit   | Name          |              | Function                                  |   |   |   |   |   |  |  |  |

| 7:0   | ADC0LTH[7:0]  | ADC0 Le      | ADC0 Less-Than Data Word High-Order Bits. |   |   |   |   |   |  |  |  |

#### SFR Definition 6.12. ADC0LTL: ADC0 Less-Than Data Low Byte

| Bit    | 7            | 6           | 5        | 4 | 3 | 2 | 1 | 0 |  |

|--------|--------------|-------------|----------|---|---|---|---|---|--|

| Name   | ADC0LTL[7:0] |             |          |   |   |   |   |   |  |

| Туре   | R/W          |             |          |   |   |   |   |   |  |

| Reset  | 0            | 0           | 0        | 0 | 0 | 0 | 0 | 0 |  |

| SFR Ad | dress = 0xC  | 5; SFR Page | e = 0x00 |   |   |   |   |   |  |

| Bit | Name         | Function                                 |

|-----|--------------|------------------------------------------|

| 7:0 | ADC0LTL[7:0] | ADC0 Less-Than Data Word Low-Order Bits. |

#### 6.4.1. Window Detector In Single-Ended Mode

Figure 6.6 example shows two window comparisons for right-justified data with ADC0LTH:ADC0LTL = 0x0200 (512d) and ADC0GTH:ADC0GTL = 0x0100 (256d). The input voltage can range from 0 to V<sub>REF</sub> x (4095/4096) with respect to GND, and is represented by a 12-bit unsigned integer value. The repeat count is set to one. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0100 < ADC0H:ADC0L < 0x0200). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0100 or ADC0H:ADC0L > 0x0200). Figure 6.7 shows an example using left-justified data with the same comparison values.

## SFR Definition 9.3. CPT1CN: Comparator1 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP1EN | CP1OUT | CP1RIF | CP1FIF | CP1HYP[1:0] |   | CP1HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/          | W |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

#### SFR Address = 0x9D; SFR Page = 0x00

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP1EN       | Comparator1 Enable Bit.                                                       |

|     |             | 0: Comparator1 Disabled.                                                      |

|     |             | 1: Comparator1 Enabled.                                                       |

| 6   | CP1OUT      | Comparator1 Output State Flag.                                                |

|     |             | 0: Voltage on CP1+ < CP1                                                      |

|     |             | 1: Voltage on CP1+ > CP1                                                      |

| 5   | CP1RIF      | Comparator1 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator1 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator1 Rising Edge has occurred.                                      |

| 4   | CP1FIF      | Comparator1 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator1 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator1 Falling-Edge has occurred.                                     |

| 3:2 | CP1HYP[1:0] | Comparator1 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP1HYN[1:0] | Comparator1 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

## SFR Definition 9.8. CPT1MX: Comparator1 MUX Selection

| Bit   | 7             | 6           | 5                                         | 4         | 3          | 2   | 1 | 0 |  |  |

|-------|---------------|-------------|-------------------------------------------|-----------|------------|-----|---|---|--|--|

| Nam   | e             | CMX1        | N[3:0]                                    |           | CMX1P[3:0] |     |   |   |  |  |

| Туре  | •             | R/          | W                                         |           |            | R/W |   |   |  |  |

| Rese  | <b>t</b> 0    | 1           | 1                                         | 1         | 0          | 1   | 1 | 1 |  |  |

| SFR A | ddress = 0x9l | F; SFR Page | = 0x00                                    |           |            |     |   |   |  |  |

| Bit   | Name          |             |                                           |           | Function   |     |   |   |  |  |

| 7:4   | CMX1N[3:0]    | Comparato   | Comparator1 Negative Input MUX Selection. |           |            |     |   |   |  |  |

|       |               | 0000:       | P0.                                       | 1         |            |     |   |   |  |  |

|       |               | 0001:       | P0.                                       | 3         |            |     |   |   |  |  |

|       |               | 0010:       | P0.                                       | 5         |            |     |   |   |  |  |

|       |               | 0011:       | P0.                                       | 7         |            |     |   |   |  |  |

|       |               | 0100:       | P1.                                       | 1         |            |     |   |   |  |  |

|       |               | 0101:       | P1.                                       | 3         |            |     |   |   |  |  |

|       |               | 0110:       | P1.                                       | 5         |            |     |   |   |  |  |

|       |               | 0111:       | P1.                                       | 7         |            |     |   |   |  |  |

|       |               | 1000:       | P2.                                       | 1         |            |     |   |   |  |  |

|       |               | 1001:       | P2.                                       | 3         |            |     |   |   |  |  |

|       |               | 1010:       | P2.                                       | 5         |            |     |   |   |  |  |

|       |               | 1011:       | P2.                                       | 7         |            |     |   |   |  |  |

|       |               | 1100–1111:  | Nor                                       | ne        |            |     |   |   |  |  |

| 3:0   | CMX1P[3:0]    | Comparato   | r1 Positive                               | Input MUX | Selection. |     |   |   |  |  |

|       |               | 0000:       | P0.                                       | 0         |            |     |   |   |  |  |

|       |               | 0001:       | P0.                                       | 2         |            |     |   |   |  |  |

|       |               | 0010:       | P0.                                       | 4         |            |     |   |   |  |  |

|       |               | 0011:       | P0.                                       | 6         |            |     |   |   |  |  |

|       |               | 0100:       | P1.                                       | 0         |            |     |   |   |  |  |

|       |               | 0101:       | P1.                                       | 2         |            |     |   |   |  |  |

|       |               | 0110:       | P1.                                       | 4         |            |     |   |   |  |  |

|       |               | 0111:       | P1.                                       | 6         |            |     |   |   |  |  |

|       |               | 1000:       | P2.                                       | 0         |            |     |   |   |  |  |

|       |               | 1001:       | P2.                                       | 2         |            |     |   |   |  |  |

|       |               | 1010:       | P2.                                       | 4         |            |     |   |   |  |  |

|       |               | 1011:       | P2.                                       | 6         |            |     |   |   |  |  |

|       |               | 1100–1111:  | Nor                                       | ne        |            |     |   |   |  |  |

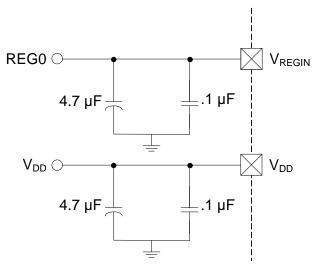

## 10. Voltage Regulator (REG0)

C8051F58x/F59x devices include an on-chip low dropout voltage regulator (REG0). The input to REG0 at the  $V_{REGIN}$  pin can be as high as 5.25 V. The output can be selected by software to 2.1 V or 2.6 V. When enabled, the output of REG0 appears on the  $V_{DD}$  pin, powers the microcontroller core, and can be used to power external devices. On reset, REG0 is enabled and can be disabled by software.

The Voltage regulator can generate an interrupt (if enabled by EREG0, EIE2.0) that is triggered whenever the  $V_{REGIN}$  input voltage drops below the dropout threshold voltage. This dropout interrupt has no pending flag and the recommended procedure to use it is as follows:

- 1. Wait enough time to ensure the  $V_{REGIN}$  input voltage is stable

- 2. Enable the dropout interrupt (EREG0, EIE2.0) and select the proper priority (PREG0, EIP2.0)

- 3. If triggered, inside the interrupt disable it (clear EREG0, EIE2.0), execute all procedures necessary to protect your application (put it in a safe mode and leave the interrupt now disabled.

- 4. In the main application, now running in the safe mode, regularly checks the DROPOUT bit (REG0CN.0). Once it is cleared by the regulator hardware the application can enable the interrupt again (EREG0, EIE1.6) and return to the normal mode operation.

The input ( $V_{REGIN}$ ) and output ( $V_{DD}$ ) of the voltage regulator should both be bypassed with a large capacitor (4.7  $\mu$ F + 0.1  $\mu$ F) to ground as shown in Figure 10.1 below. This capacitor will eliminate power spikes and provide any immediate power required by the microcontroller. The settling time associated with the voltage regulator is shown in Table 5.9 on page 50.

**Note:** The output of the internal voltage regulator is calibrated by the MCU immediately after any reset event. The output of the un-calibrated internal regulator could be below the high threshold setting of the VDD Monitor. If this is the case, and the MCU receives a non-power on reset (POR) when the VDD Monitor is set to the high threshold setting, the MCU will remain in reset until a POR occurs (i.e. VDD Monitor will keep the device in reset). A POR will force the VDD Monitor to the low threshold setting, which is guaranteed to be below the un-calibrated output of the internal regulator. The device will then exit reset and resume normal operation. It is for this reason Silicon Labs strongly recommends that the V<sub>DD</sub> Monitor is always left in the low threshold setting (i.e. default value upon POR). If the system contains routines to modify flash contents, follow the recommendations in "Reprogramming the VDD Monitor High Threshold" on page 138.

#### Figure 10.1. External Capacitors for Voltage Regulator Input/Output—Regulator Enabled

## Table 13.3. Special Function Registers (Continued)

| Register          | Address | Description                      | Page |

|-------------------|---------|----------------------------------|------|

| P4MDOUT 0xAF Port |         | Port 4 Output Mode Configuration | 213  |

| PCA0CN            | 0xD8    | PCA0 Control                     | 327  |

| PCA0CPH0          | 0xFC    | PCA0 Capture 0 High              | 332  |

| PCA0CPH1          | 0xEA    | PCA0 Capture 1 High              | 332  |

| PCA0CPH2          | 0xEC    | PCA0 Capture 2 High              | 332  |

| PCA0CPH3          | 0xEE    | PCA0 Capture 3 High              | 332  |

| PCA0CPH4          | 0xFE    | PCA0 Capture 4 High              | 332  |

| PCA0CPH5          | 0xCF    | PCA0 Capture 5 High              | 332  |

| PCA0CPL0          | 0xFB    | PCA0 Capture 0 Low               | 332  |

| PCA0CPL1          | 0xE9    | PCA0 Capture 1 Low               | 332  |

| PCA0CPL2          | 0xEB    | PCA0 Capture 2 Low               | 332  |

| PCA0CPL3          | 0xED    | PCA0 Capture 3 Low               | 332  |

| PCA0CPL4          | 0xFD    | PCA0 Capture 4 Low               | 332  |

| PCA0CPL5          | 0xCE    | PCA0 Capture 5 Low               | 332  |

| PCA0CPM0          | 0xDA    | PCA0 Module 0 Mode Register      | 330  |

| PCA0CPM1          | 0xDB    | PCA0 Module 1 Mode Register      | 330  |

| PCA0CPM2          | 0xDC    | PCA0 Module 2 Mode Register      | 330  |

| PCA0CPM3          | 0xDD    | PCA0 Module 3 Mode Register      | 330  |

| PCA0CPM4          | 0xDE    | PCA0 Module 4 Mode Register      | 330  |

| PCA0CPM5          | 0xDF    | PCA0 Module 5 Mode Register      | 330  |

| PCA0H             | 0xFA    | PCA0 Counter High                | 331  |

| PCA0L             | 0xF9    | PCA0 Counter Low                 | 331  |

| PCA0MD            | 0xD9    | PCA0 Mode                        | 328  |

| PCA0PWM           | 0xD9    | PCA0 PWM Configuration           | 329  |

| PCA1CN            | 0xD8    | PCA1 Control                     | 345  |

| PCA1CPH6          | 0xFC    | PCA1 Capture 6 High              | 350  |

| PCA1CPH7          | 0xEA    | PCA1 Capture 7 High              | 350  |

| PCA1CPH8          | 0xEC    | PCA1 Capture 8 High              | 350  |

| PCA1CPH9          | 0xEE    | PCA1 Capture 9 High              | 350  |

| PCA1CPH10         | 0xFE    | PCA1 Capture 10 High             | 350  |

| PCA1CPH11         | 0xCF    | PCA1 Capture 11 High             | 350  |

| PCA1CPL6          | 0xFB    | PCA1 Capture 6 Low               | 350  |

| PCA1CPL7          | 0xE9    | PCA1 Capture 7 Low               | 350  |

| PCA1CPL8          | 0xEB    | PCA1 Capture 8 Low               | 350  |

| PCA1CPL9          | 0xED    | PCA1 Capture 9 Low               | 350  |

| PCA1CPL10         | 0xFD    | PCA1 Capture 10 Low              | 350  |

## SFR Definition 15.2. FLKEY: Flash Lock and Key

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|---|---|---|---|---|--|

| Name  | FLKEY[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

#### SFR Address = 0xB7; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | FLKEY[7:0] | Flash Lock and Key Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7:0 | FLKEY[7:0] | Flash Lock and Key Register.<br>Write:<br>This register provides a lock and key function for Flash erasures and writes. Flash<br>writes and erases are enabled by writing 0xA5 followed by 0xF1 to the FLKEY regis-<br>ter. Flash writes and erases are automatically disabled after the next write or erase is<br>complete. If any writes to FLKEY are performed incorrectly, or if a Flash write or erase<br>operation is attempted while these operations are disabled, the Flash will be perma-<br>nently locked from writes or erasures until the next device reset. If an application<br>never writes to Flash, it can intentionally lock the Flash by writing a non-0xA5 value to<br>FLKEY from software.<br>Read:<br>When read, bits 1–0 indicate the current Flash lock state.<br>00: Flash is write/erase locked. |

|     |            | 01: The first key code has been written (0xA5).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |            | 10: Flash is unlocked (writes/erases allowed).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |            | 11: Flash writes/erases disabled until the next reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

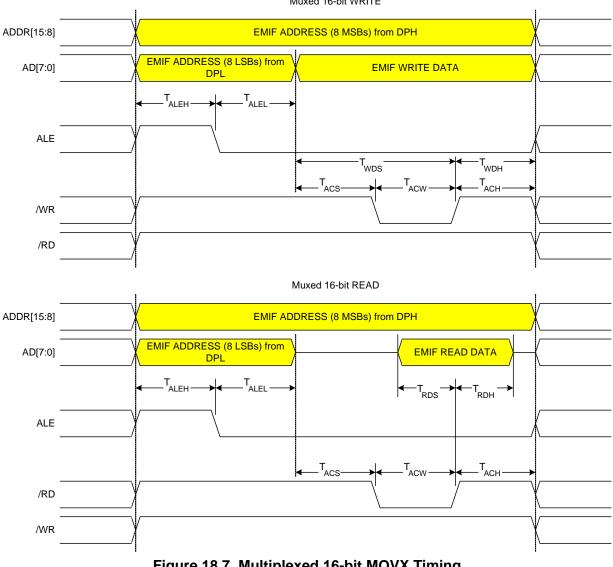

### 18.6.2. Multiplexed Mode 18.6.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011

Muxed 16-bit WRITE

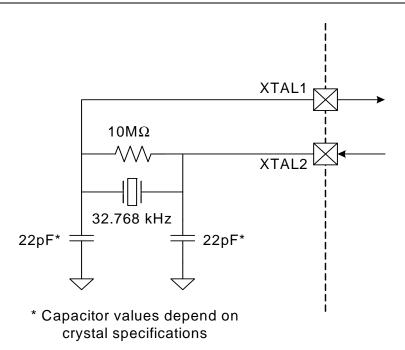

#### Figure 19.3. External 32.768 kHz Quartz Crystal Oscillator Connection Diagram

#### 19.4.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 19.1, Option 2. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation, according to Equation , where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and R = the pull-up resistor value in  $k\Omega$ .

$$f = 1.23 \times 10^3 / (R \times C)$$

#### Equation 19.1. RC Mode Oscillator Frequency

For example: If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

f = 1.23(10<sup>3</sup>)/RC = 1.23(10<sup>3</sup>)/[246 x 50] = 0.1 MHz = 100 kHz

Referring to the table in SFR Definition 19.6, the required XFCN setting is 010b.

#### **19.4.3. External Capacitor Example**

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 19.1, Option 3. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation , where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and  $V_{DD}$  = the MCU power supply in volts.

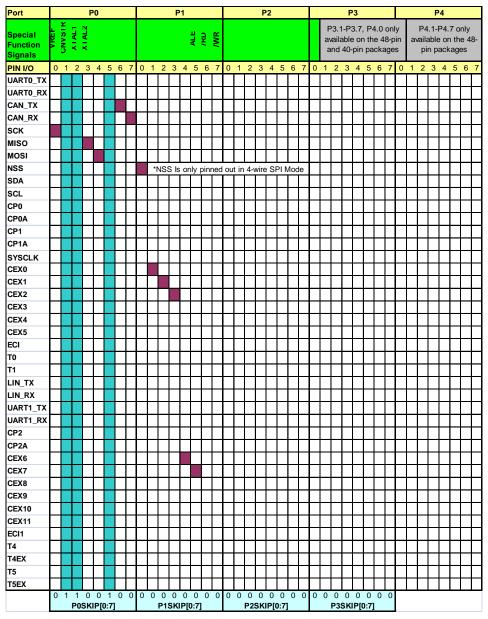

UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.4; UART RX0 is always assigned to P0.5. CAN0 pin assignments are fixed to P0.6 for CAN\_TX and P0.7 for CAN\_RX. Standard Port I/Os appear contiguously after the prioritized functions have been assigned.

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, pending the state of the NSS-MD1–NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

As an example configuration, if CAN0, SPI0 in 4-wire mode, and PCA0 Modules 0, 1, and 2, 6, and 7 are enabled on the crossbar with P0.1, P0.2, and P0.5 skipped, the registers should be set as follows: XBR0 = 0x06 (CAN0 and SPI0 enabled), XBR1 = 0x0C (PCA0 modules 0, 1, and 2 enabled), XBR2 = 0x40 (Crossbar enabled), XBR3 = 0x02 (PCA1 modules 6 and 7) and P0SKIP = 0x26 (P0.1, P0.2, and P0.5 skipped). The resulting crossbar would look as shown in Figure 20.4.

Figure 20.4. Crossbar Priority Decoder in Example Configuration

### LIN Register Definition 21.4. LIN0DTn: LIN0 Data Byte n

| Bit                                                                                                                                              | 7          | 6                                                                          | 5 | 4  | 3 | 2 | 1 | 0 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------|---|----|---|---|---|---|

| Nam                                                                                                                                              | e          | DATAn[7:0]                                                                 |   |    |   |   |   |   |

| Туре                                                                                                                                             | )          |                                                                            |   | R/ | W |   |   |   |

| Rese                                                                                                                                             | et 0       | 0                                                                          | 0 | 0  | 0 | 0 | 0 | 0 |

| Indirect Address: LIN0DT1 = 0x00, LIN0DT2 = 0x01, LIN0DT3 = 0x02, LIN0DT4 = 0x03, LIN0DT5 = 0x04, LIN0DT6 = 0x05, LIN0DT7 = 0x06, LIN0DT8 = 0x07 |            |                                                                            |   |    |   |   |   |   |

| Bit                                                                                                                                              | Name       | Function                                                                   |   |    |   |   |   |   |

| 7:0                                                                                                                                              | DATAn[7:0] | LIN Data Byte n.                                                           |   |    |   |   |   |   |

|                                                                                                                                                  |            | Serial Data Byte that is received or transmitted across the LIN interface. |   |    |   |   |   |   |

overflow after 25 ms (and SMBTOE set), the Timer 3 interrupt service routine can be used to reset (disable and re-enable) the SMBus in the event of an SCL low timeout.

#### 23.3.5. SCL High (SMBus Free) Timeout

The SMBus specification stipulates that if the SCL and SDA lines remain high for more that 50  $\mu$ s, the bus is designated as free. When the SMBFTE bit in SMB0CF is set, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods (as defined by the timer configured for the SMBus clock source). If the SMBus is waiting to generate a Master START, the START will be generated following this timeout. Note that a clock source is required for free timeout detection, even in a slave-only implementation.

#### 23.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

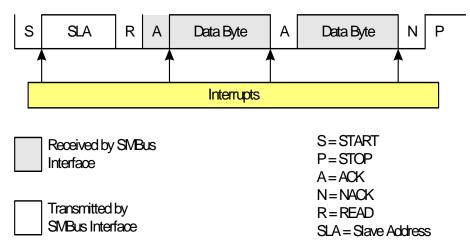

SMBus interrupts are generated for each data byte or slave address that is transferred. The point at which the interrupt is generated depends on whether the hardware is acting as a data transmitter or receiver. When a transmitter (i.e. sending address/data, receiving an ACK), this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data (i.e. receiving address/data, sending an ACK), this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. See Section 23.5 for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in Section 23.4.2; Table 23.4 provides a quick SMB0CN decoding reference.

#### 23.4.1. SMBus Configuration Register

The SMBus Configuration register (SMB0CF) is used to enable the SMBus Master and/or Slave modes, select the SMBus clock source, and select the SMBus timing and timeout options. When the ENSMB bit is set, the SMBus is enabled for all master and slave events. Slave events may be disabled by setting the INH bit. With slave events inhibited, the SMBus interface will still monitor the SCL and SDA pins; however, the interface will NACK all received addresses and will not generate any slave interrupts. When the INH bit is set, all slave events will be inhibited following the next START (interrupts will continue for the duration of the current transfer).

## SFR Definition 23.1. SMB0CF: SMBus Clock/Configuration

| Bit   | 7     | 6   | 5    | 4       | 3      | 2      | 1    | 0       |

|-------|-------|-----|------|---------|--------|--------|------|---------|

| Name  | ENSMB | INH | BUSY | EXTHOLD | SMBTOE | SMBFTE | SMBC | :S[1:0] |

| Туре  | R/W   | R/W | R    | R/W     | R/W    | R/W    | R/   | W       |

| Reset | 0     | 0   | 0    | 0       | 0      | 0      | 0    | 0       |

#### SFR Address = 0xC1; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ENSMB      | SMBus Enable.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | This bit enables the SMBus interface when set to 1. When enabled, the interface constantly monitors the SDA and SCL pins.                                                                                                                                                                                                                                                                                                             |

| 6   | INH        | SMBus Slave Inhibit.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | When this bit is set to logic 1, the SMBus does not generate an interrupt when slave events occur. This effectively removes the SMBus slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                                                                                                    |

| 5   | BUSY       | SMBus Busy Indicator.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                                                                                                                |

| 4   | EXTHOLD    | SMBus Setup and Hold Time Extension Enable.                                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | This bit controls the SDA setup and hold times according to Table 23.2.<br>0: SDA Extended Setup and Hold Times disabled.                                                                                                                                                                                                                                                                                                             |

|     |            | 1: SDA Extended Setup and Hold Times enabled.                                                                                                                                                                                                                                                                                                                                                                                         |

| 3   | SMBTOE     | SMBus SCL Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |            | This bit enables SCL low timeout detection. If set to logic 1, the SMBus forces<br>Timer 3 to reload while SCL is high and allows Timer 3 to count when SCL goes low.<br>If Timer 3 is configured to Split Mode, only the High Byte of the timer is held in reload<br>while SCL is high. Timer 3 should be programmed to generate interrupts at 25 ms,<br>and the Timer 3 interrupt service routine should reset SMBus communication. |

| 2   | SMBFTE     | SMBus Free Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | When this bit is set to logic 1, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods.                                                                                                                                                                                                                                                                                              |

| 1:0 | SMBCS[1:0] | SMBus Clock Source Selection.                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | These two bits select the SMBus clock source, which is used to generate the SMBus bit rate. The selected device should be configured according to Equation 23.1.                                                                                                                                                                                                                                                                      |

|     |            | 00: Timer 0 Overflow                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | 01: Timer 1 Overflow                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | 10:Timer 2 High Byte Overflow                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | 11: Timer 2 Low Byte Overflow                                                                                                                                                                                                                                                                                                                                                                                                         |

#### 23.5.2. Read Sequence (Master)

During a read sequence, an SMBus master reads data from a slave device. The master in this transfer will be a transmitter during the address byte, and a receiver during all data bytes. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 (READ). Serial data is then received from the slave on SDA while the SMBus outputs the serial clock. The slave transmits one or more bytes of serial data. An interrupt is generated after each received byte.

Software must write the ACK bit at that time to ACK or NACK the received byte. Writing a 1 to the ACK bit generates an ACK; writing a 0 generates a NACK. Software should write a 0 to the ACK bit for the last data transfer, to transmit a NACK. The interface exits Master Receiver Mode after the STO bit is set and a STOP is generated. The interface will switch to Master Transmitter Mode if SMB0DAT is written while an active Master Receiver. Figure 23.6 shows a typical master read sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur **before** the ACK cycle in this mode.

Figure 23.6. Typical Master Read Sequence

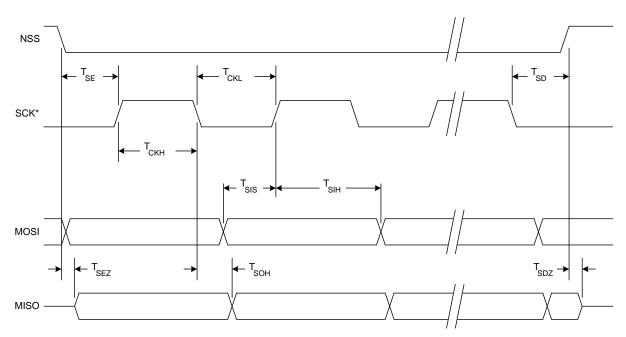

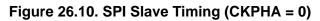

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

Figure 26.11. SPI Slave Timing (CKPHA = 1)

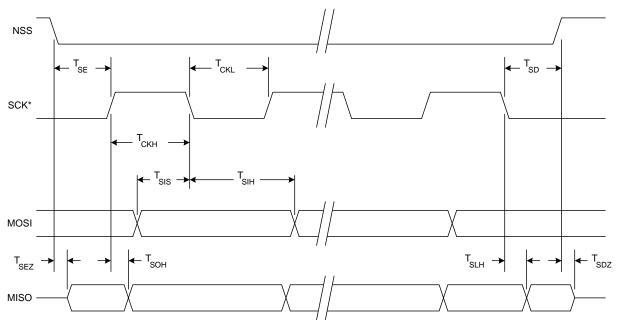

Figure 28.6. PCA0 High-Speed Output Mode Diagram

#### 28.3.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA0 clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 28.1.

$$\mathsf{F}_{\mathsf{CEXn}} = \frac{\mathsf{F}_{\mathsf{PCA}}}{2 \times \mathsf{PCA0CPHn}}$$

Note: A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

#### Equation 28.1. Square Wave Frequency Output

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2–0 bits in the PCA0 mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA0 counter low byte; on a match, CEXn is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register. Note that the MATn bit should normally be set to 0 in this mode. If the MATn bit is set to 1, the CCFn flag for the channel will be set when the 16-bit PCA0 counter and the 16-bit capture/compare register for the channel are equal.

#### 29.3.5.2. 9/10/11-bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 9/10/11-bit PWM mode should be varied by writing to an "Auto-Reload" Register, which is dual-mapped into the PCA1CPHn and PCA1CPLn register locations. The data written to define the duty cycle should be right-justified in the registers. The auto-reload registers are accessed (read or written) when the bit ARSEL1 in PCA1PWM is set to 1. The capture/compare registers are accessed when ARSEL1 is set to 0.

When the least-significant N bits of the PCA1 counter match the value in the associated module's capture/compare register (PCA1CPn), the output on CEXn is asserted high. When the counter overflows from the Nth bit, CEXn is asserted low (see Figure 29.9). Upon an overflow from the Nth bit, the COVF1 flag is set, and the value stored in the module's auto-reload register is loaded into the capture/compare register. The value of N is determined by the CLSEL1 bits in register PCA1PWM.

The 9, 10 or 11-bit PWM mode is selected by setting the ECOM1n and PWM1n bits in the PCA1CPMn register, and setting the CLSEL1 bits in register PCA1PWM to the desired cycle length (other than 8-bits). If the MAT1n bit is set to 1, the CCFn flag for the module will be set each time a comparator match (rising edge) occurs. The COVF1 flag in PCA1PWM can be used to detect the overflow (falling edge), which will occur every 512 (9-bit), 1024 (10-bit) or 2048 (11-bit) PCA1 clock cycles. The duty cycle for 9/10/11-Bit PWM Mode is given in Equation 29.2, where N is the number of bits in the PWM cycle.

**Important Note About PCA1CPHn and PCA1CPLn Registers**: When writing a 16-bit value to the PCA1CPn registers, the low byte should always be written first. Writing to PCA1CPLn clears the ECOM1n bit to 0; writing to PCA1CPHn sets ECOM1n to 1.

Duty Cycle =

$$\frac{(2^{N} - PCA1CPn)}{2^{N}}$$

Write to PCA1CPI r PCA1PWM R/W when (Auto-Reload) ARSEL1 = Rese PCA1CPH<sup>·</sup>I n (right-justified) Write to PCA1CPHn R/W when (Capture/Compare) ARSEL1 = 0Set "N" bits PCA1CPH:Ln 01 = 9 bits (right-justified 10 = 10 bits 11 = 11 bits Enable CEXn match SET s Q Port I/O N-bit Comparator Crossbar  $R \ CLR \ \overline{Q}$ PCA1 Timebase PCA1H:L Overflow of N<sup>th</sup> Bit

Equation 29.3. 9, 10, and 11-Bit PWM Duty Cycle

A 0% duty cycle may be generated by clearing the ECOM1n bit to 0.

Figure 29.9. PCA1 9, 10 and 11-Bit PWM Mode Diagram

## SFR Definition 29.4. PCA1CPMn: PCA1 Capture/Compare Mode

| Bit   | 7       | 6      | 5      | 4      | 3     | 2     | 1     | 0      |

|-------|---------|--------|--------|--------|-------|-------|-------|--------|

| Name  | PWM161n | ECOM1n | CAPP1n | CAPN1n | MAT1n | TOG1n | PWM1n | ECCF1n |

| Туре  | R/W     | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   | R/W    |

| Reset | 0       | 0      | 0      | 0      | 0     | 0     | 0     | 0      |

|       |         |        |        |        |       |       |       |        |

SFR Addresses: PCA1CPM6 = 0xDA, PCA1CPM7 = 0xDB, PCA1CPM8 = 0xDC; PCA1CPM9 = 0xDD, PCA1CPM10 = 0xDE, PCA1CPM11 = 0xDF, SFR Page (all registers) = 0x10

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                           |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PWM161n | <ul> <li>16-bit Pulse Width Modulation Enable.</li> <li>This bit enables 16-bit mode when Pulse Width Modulation mode is enabled.</li> <li>0: 8 to 11-bit PWM selected.</li> <li>1: 16-bit PWM selected.</li> </ul>                                                                                                                                                |

| 6   | ECOM1n  | <b>Comparator Function Enable.</b><br>This bit enables the comparator function for PCA1 module n when set to 1.                                                                                                                                                                                                                                                    |

| 5   | CAPP1n  | Capture Positive Function Enable.<br>This bit enables the positive edge capture for PCA1 module n when set to 1.                                                                                                                                                                                                                                                   |

| 4   | CAPN1n  | Capture Negative Function Enable.<br>This bit enables the negative edge capture for PCA1 module n when set to 1.                                                                                                                                                                                                                                                   |

| 3   | MAT1n   | Match Function Enable.<br>This bit enables the match function for PCA1 module n when set to 1. When enabled,<br>matches of the PCA1 counter with a module's capture/compare register cause the<br>CCFn bit in PCA1MD register to be set to logic 1.                                                                                                                |

| 2   | TOG1n   | <b>Toggle Function Enable.</b><br>This bit enables the toggle function for PCA1 module n when set to 1. When enabled, matches of the PCA1 counter with a module's capture/compare register cause the logic level on the CEXn pin to toggle. If the PWMn bit is also set to logic 1, the module operates in Frequency Output Mode.                                  |

| 1   | PWM1n   | <b>Pulse Width Modulation Mode Enable.</b><br>This bit enables the PWM function for PCA1 module n when set to 1. When enabled, a pulse width modulated signal is output on the CEXn pin. 8 to 11-bit PWM is used if PWM16n is cleared; 16-bit mode is used if PWM16n is set to logic 1. If the TOGn bit is also set, the module operates in Frequency Output Mode. |

| 0   | ECCF1n  | Capture/Compare Flag Interrupt Enable.<br>This bit sets the masking of the Capture/Compare Flag (CCFn) interrupt.<br>0: Disable CCFn interrupts.<br>1: Enable a Capture/Compare Flag interrupt request when CCFn is set.                                                                                                                                           |

The FPSEL register is a Special Function Register (SFR) that is only accessible through the C2 interface. When reading, writing. or erasing Flash through the C2 interface, this register must be set first in order to access the different banks. SFRs are accessed through the C2 interface using the WriteAR and ReadDR / Write DR commands described in Application Note 127: Flash Programming via the C2 Interface.

### C2 Register Definition 30.6. FPSEL: C2 Flash Bank Select

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0    |

|-------|---|---|---|---|---|---|---|------|

| Name  |   |   |   |   |   |   |   | BSEL |

| Туре  | R | R | R | R | R | R | R | R/W  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    |

SFR Address = 0xC6; SFR Page = 0x01

| Bit | Name   | Function                                                  |  |  |  |

|-----|--------|-----------------------------------------------------------|--|--|--|

| 7:1 | Unused | Read = 0000000b; Write = Don't Care.                      |  |  |  |

| 0   | BSEL   | Flash Programming Bank Select.                            |  |  |  |

|     |        | The address range 0x0000 - 0xFFFF accesses Banks 0 - 1    |  |  |  |

|     |        | 1: The address range 0x0000 - 0xFFFF accesses Banks 2 - 3 |  |  |  |