# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART      |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 40                                                             |

| Program Memory Size        | 96KB (96K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                |                                                                |

| RAM Size                   | 8.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 32x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f585-iq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Registers

| SFR | Definition | 6.4. A | ADC0CF: ADC0 Configuration                    | 65 |

|-----|------------|--------|-----------------------------------------------|----|

|     |            |        | ADC0H: ADC0 Data Word MSB                     |    |

|     |            |        | ADC0L: ADC0 Data Word LSB                     |    |

|     |            |        | ADC0CN: ADC0 Control                          |    |

|     |            |        | ADC0TK: ADC0 Tracking Mode Select             |    |

| SFR | Definition | 6.9. A | ADC0GTH: ADC0 Greater-Than Data High Byte     | 69 |

|     |            |        | ADC0GTL: ADC0 Greater-Than Data Low Byte      |    |

|     |            |        | ADC0LTH: ADC0 Less-Than Data High Byte        |    |

|     |            |        | ADC0LTL: ADC0 Less-Than Data Low Byte         |    |

|     |            |        | ADC0MX: ADC0 Channel Select                   |    |

| SFR | Definition | 8.1. F | REF0CN: Reference Control                     | 76 |

|     |            |        | CPT0CN: Comparator0 Control                   |    |

| SFR | Definition | 9.2. 0 | CPT0MD: Comparator0 Mode Selection            | 80 |

| SFR | Definition | 9.3. 0 | CPT1CN: Comparator1 Control                   | 81 |

| SFR | Definition | 9.4. 0 | CPT1MD: Comparator1 Mode Selection            | 82 |

| SFR | Definition | 9.5. C | CPT2CN: Comparator2 Control                   | 83 |

|     |            |        | CPT2MD: Comparator2 Mode Selection            |    |

|     |            |        | CPT0MX: Comparator0 MUX Selection             |    |

|     |            |        | CPT1MX: Comparator1 MUX Selection             |    |

|     |            |        | CPT2MX: Comparator2 MUX Selection             |    |

|     |            |        | REG0CN: Regulator Control                     |    |

|     |            |        | DPL: Data Pointer Low Byte                    |    |

| SFR | Definition | 11.2.  | DPH: Data Pointer High Byte                   | 98 |

|     |            |        | SP: Stack Pointer                             |    |

|     |            |        | ACC: Accumulator                              |    |

|     |            |        | B: B Register                                 |    |

|     |            |        | PSW: Program Status Word 1                    |    |

|     |            |        | SNn: Serial Number n 1                        |    |

|     |            |        | PSBANK: Program Space Bank Select 1           |    |

|     |            |        | SFR0CN: SFR Page Control 1                    |    |

|     |            |        | SFRPAGE: SFR Page1                            |    |

|     |            |        | SFRNEXT: SFR Next                             |    |

|     |            |        | SFRLAST: SFR Last 1                           |    |

|     |            |        | IE: Interrupt Enable                          |    |

|     |            |        | IP: Interrupt Priority1                       |    |

|     |            |        | EIE1: Extended Interrupt Enable 1 1           |    |

|     |            |        | EIP1: Extended Interrupt Priority 1 1         |    |

|     |            |        | EIE2: Extended Interrupt Enable 2 1           |    |

|     |            |        | EIP2: Extended Interrupt Priority Enabled 2 1 |    |

|     |            |        | IT01CF: INT0/INT1 Configuration1              |    |

|     |            |        | PSCTL: Program Store R/W Control 1            |    |

|     |            |        | FLKEY: Flash Lock and Key 1                   |    |

| SFR | Definition | 15.3.  | FLSCL: Flash Scale 1                          | 45 |

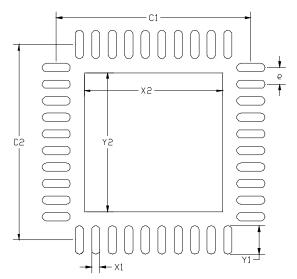

Figure 4.6. QFN-40 Landing Diagram

#### Table 4.6. QFN-40 Landing Diagram Dimensions

| Dimension | Min  | Max      |  | Dimension | Min  | Max  |

|-----------|------|----------|--|-----------|------|------|

| C1        | 5.80 | 5.90     |  | X2        | 4.10 | 4.20 |

| C2        | 5.80 | 5.90     |  | Y1        | 0.75 | 0.85 |

| е         | 0.50 | 0.50 BSC |  |           | 4.10 | 4.20 |

| X1        | 0.15 | 0.25     |  |           |      |      |

## Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimension and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on the IPC-SM-7351 guidelines.

- 4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Solder Mask Design

5. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### **Stencil Design**

- 6. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 7. The stencil thickness should be 0.125 mm (5 mils).

- 8. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- 9. A 4x4 array of 0.80 mm square openings on a 1.05 mm pitch should be used for the center ground pad.

#### Card Assembly

- **10.** A No-Clean, Type-3 solder paste is recommended.

- **11.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### Table 5.7. Clock Multiplier Electrical Specifications

$V_{DD}$  = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter                            | Conditions | Min | Тур | Max | Units |

|--------------------------------------|------------|-----|-----|-----|-------|

| Input Frequency (Fcm <sub>in</sub> ) |            | 2   | _   | _   | MHz   |

| Output Frequency                     |            |     | _   | 50  | MHz   |

| Power Supply Current                 |            | —   | 1.4 | 1.9 | μA    |

#### Table 5.8. Crystal Oscillator Electrical Characteristics

$V_{DD}$  = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter             | Conditions    | Min  | Тур | Max | Units |

|-----------------------|---------------|------|-----|-----|-------|

| Crystal Frequency     |               | 0.02 |     | 25  | MHz   |

|                       | XOSCMD = 110b |      |     |     |       |

|                       | XFCN = 000b   | —    | 1.3 | —   | μA    |

|                       | XFCN = 001b   | —    | 3.5 | —   | μA    |

|                       | XFCN = 010b   | —    | 10  | —   | μA    |

| Crystal Drive Current | XFCN = 011b   | —    | 27  | —   | μA    |

|                       | XFCN = 100b   | —    | 70  | —   | μA    |

|                       | XFCN = 101b   | —    | 200 | —   | μA    |

|                       | XFCN = 110b   | —    | 800 | —   | μA    |

|                       | XFCN = 111b   | —    | 2.8 |     | mA    |

### Table 5.9. Voltage Regulator Electrical Characteristics

$V_{DD}$  = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter                                  | Conditions                                                                     | Min         | Тур      | Мах   | Units |

|--------------------------------------------|--------------------------------------------------------------------------------|-------------|----------|-------|-------|

| Input Voltage Range (V <sub>REGIN</sub> )* |                                                                                | 1.8*        |          | 5.25  | V     |

| Dropout Voltage (V <sub>DO</sub> )         | Maximum Current = 50 mA                                                        | _           | 10       | _     | mV/mA |

| Output Voltage (V <sub>DD</sub> )          | 2.1 V operation (REG0MD = 0)                                                   | 2.0         | 2.1      | 2.25  | V     |

|                                            | 2.6 V operation (REG0MD = 1)                                                   | 2.5         | 2.6      | 2.75  | v     |

| Bias Current                               |                                                                                |             | 1        | 9     | μA    |

| Dropout Indicator Detection<br>Threshold   | With respect to V <sub>DD</sub>                                                | -0.21       | _        | -0.02 | V     |

| Output Voltage Temperature<br>Coefficient  |                                                                                | _           | 0.04     | _     | mV/°C |

| VREG Settling Time                         | 50 mA load with $V_{REGIN} = 2.4 V$ and $V_{DD}$ load capacitor of 4.8 $\mu$ F | _           | 450      | _     | μs    |

| *Note: The minimum input voltage           | is 1.8 V or V <sub>DD</sub> + V <sub>DO</sub> (max load), whi                  | chever is g | greater. |       | •     |

## Gain Register Definition 6.1. ADC0GNH: ADC0 Selectable Gain High Byte

| Bit    | 7                                                                                                  | 7 6 5 4 3 2 1 0                                                           |            |  |          |   |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------|--|----------|---|--|--|--|--|

| Nam    | е                                                                                                  | GAINH[7:0]                                                                |            |  |          |   |  |  |  |  |

| Тур    | e                                                                                                  | W                                                                         |            |  |          |   |  |  |  |  |

| Rese   | et 1                                                                                               | 1 1 1 1 1 1 0 0                                                           |            |  |          |   |  |  |  |  |

| Indire | ct Address = (                                                                                     | )x04;                                                                     |            |  |          | • |  |  |  |  |

| Bit    | Name                                                                                               |                                                                           |            |  | Function |   |  |  |  |  |

| 7:0    | GAINH[7:0]                                                                                         | ADC0 Gain                                                                 | High Byte. |  |          |   |  |  |  |  |

|        |                                                                                                    | See Section 6.3.1 for details on calculating the value for this register. |            |  |          |   |  |  |  |  |

| Note:  | te: This register is accessed indirectly; See Section 6.3.2 for details for writing this register. |                                                                           |            |  |          |   |  |  |  |  |

#### Gain Register Definition 6.2. ADC0GNL: ADC0 Selectable Gain Low Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2        | 1        | 0        |

|-------|---|------------|---|---|---|----------|----------|----------|

| Name  |   | GAINL[3:0] |   |   |   | Reserved | Reserved | Reserved |

| Туре  |   | W          |   |   |   | W        | W        | W        |

| Reset | 0 | 0          | 0 | 0 | 0 | 0        | 0        | 0        |

Indirect Address = 0x07;

| Bit   | Name                                                                                                 | Function                                                                        |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|--|

| 7:4   | GAINL[3:0]                                                                                           | ADC0 Gain Lower 4 Bits.                                                         |  |  |  |  |  |

|       |                                                                                                      | See Figure 6.3.1 for details for setting this register.                         |  |  |  |  |  |

|       |                                                                                                      | This register is only accessed indirectly through the ADC0H and ADC0L register. |  |  |  |  |  |

| 3:0   | Reserved                                                                                             | Must Write 0000b                                                                |  |  |  |  |  |

| Note: | lote: This register is accessed indirectly; See Section 6.3.2 for details for writing this register. |                                                                                 |  |  |  |  |  |

## 11. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware (see description in "C2 Interface" on page 351), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 11.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 50 MIPS Peak Throughput with 50 MHz Clock

- 0 to 50 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

#### 11.1. Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

### Table 11.1. CIP-51 Instruction Set Summary (Prefetch-Enabled)

| Mnemonic              | Description                              | Bytes | Clock<br>Cycles |  |

|-----------------------|------------------------------------------|-------|-----------------|--|

| Arithmetic Operations |                                          |       |                 |  |

| ADD A, Rn             | Add register to A                        | 1     | 1               |  |

| ADD A, direct         | Add direct byte to A                     | 2     | 2               |  |

| ADD A, @Ri            | Add indirect RAM to A                    | 1     | 2               |  |

| ADD A, #data          | Add immediate to A                       | 2     | 2               |  |

| ADDC A, Rn            | Add register to A with carry             | 1     | 1               |  |

| ADDC A, direct        | Add direct byte to A with carry          | 2     | 2               |  |

| ADDC A, @Ri           | Add indirect RAM to A with carry         | 1     | 2               |  |

| ADDC A, #data         | Add immediate to A with carry            | 2     | 2               |  |

| SUBB A, Rn            | Subtract register from A with borrow     | 1     | 1               |  |

| SUBB A, direct        | Subtract direct byte from A with borrow  | 2     | 2               |  |

| SUBB A, @Ri           | Subtract indirect RAM from A with borrow | 1     | 2               |  |

| SUBB A, #data         | Subtract immediate from A with borrow    | 2     | 2               |  |

| INC A                 | Increment A                              | 1     | 1               |  |

| INC Rn                | Increment register                       | 1     | 1               |  |

| INC direct            | Increment direct byte                    | 2     | 2               |  |

| INC @Ri               | Increment indirect RAM                   | 1     | 2               |  |

| DEC A                 | Decrement A                              | 1     | 1               |  |

| DEC Rn                | Decrement register                       | 1     | 1               |  |

| DEC direct            | Decrement direct byte                    | 2     | 2               |  |

| DEC @Ri               | Decrement indirect RAM                   | 1     | 2               |  |

| INC DPTR              | Increment Data Pointer                   | 1     | 1               |  |

| MUL AB                | Multiply A and B                         | 1     | 4               |  |

| DIV AB                | Divide A by B                            | 1     | 8               |  |

| DA A                  | Decimal adjust A                         | 1     | 1               |  |

| Logical Operations    |                                          | I     | 1               |  |

| ANL A, Rn             | AND Register to A                        | 1     | 1               |  |

| ANL A, direct         | AND direct byte to A                     | 2     | 2               |  |

| ANL A, @Ri            | AND indirect RAM to A                    | 1     | 2               |  |

| ANL A, #data          | AND immediate to A                       | 2     | 2               |  |

| ANL direct, A         | AND A to direct byte                     | 2     | 2               |  |

| ANL direct, #data     | AND immediate to direct byte             | 3     | 3               |  |

| ORL A, Rn             | OR Register to A                         | 1     | 1               |  |

| ORL A, direct         | OR direct byte to A                      | 2     | 2               |  |

| ORL A, @Ri            | OR indirect RAM to A                     | 1     | 2               |  |

| ORL A, #data          | OR immediate to A                        | 2     | 2               |  |

| ORL direct, A         | OR A to direct byte                      | 2     | 2               |  |

| ORL direct, #data     | OR immediate to direct byte              | 3     | 3               |  |

| XRL A, Rn             | Exclusive-OR Register to A               | 1     | 1               |  |

| XRL A, direct         | Exclusive-OR direct byte to A            | 2     | 2               |  |

| XRLA, @Ri             | Exclusive-OR indirect RAM to A           | 1     | 2               |  |

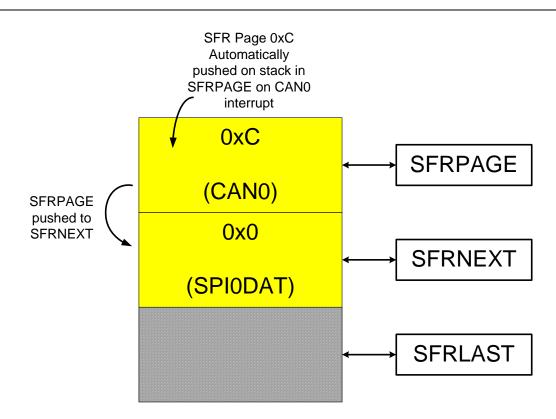

Figure 13.3. SFR Page Stack After CAN0 Interrupt Occurs

While in the CAN0 ISR, a PCA interrupt occurs. Recall the PCA interrupt is configured as a high priority interrupt, while the CAN0 interrupt is configured as a *low* priority interrupt. Thus, the CIP-51 will now vector to the high priority PCA ISR. Upon doing so, the CIP-51 will automatically place the SFR page needed to access the PCA's special function registers into the SFRPAGE register, SFR Page 0x00. The value that was in the SFRPAGE register before the PCA interrupt (SFR Page 0x0C for CAN0) is pushed down the stack into SFRNEXT. Likewise, the value that was in the SFRNEXT register before the PCA interrupt (in this case SFR Page 0x00 for SPI0DAT) is pushed down to the SFRLAST register, the "bottom" of the stack. Note that a value stored in SFRLAST (via a previous software write to the SFRLAST register) will be overwritten. See Figure 13.4.

#### 15.1.2. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 15.2.

#### 15.1.3. Flash Erase Procedure

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before writing to Flash memory using MOVX, Flash write operations must be enabled by doing the following: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software.

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. **A byte location to be programmed should be erased before a new value is written.** The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire 512-byte page, perform the following steps:

- 1. Disable interrupts (recommended).

- 2. If erasing a page in Banks 1, 2, or 3, set the COBANK[1:0] bits (register PSBANK) for the appropriate bank.

- 3. Set the FLEWT bit (register FLSCL).

- 4. Set the PSEE bit (register PSCTL).

- 5. Set the PSWE bit (register PSCTL).

- 6. Write the first key code to FLKEY: 0xA5.

- 7. Write the second key code to FLKEY: 0xF1.

- 8. Using the MOVX instruction, write a data byte to any location within the 512-byte page to be erased.

- 9. Clear the PSWE and PSEE bits.

#### 15.1.4. Flash Write Procedure

Flash bytes are programmed by software with the following sequence:

- 1. Disable interrupts (recommended).

- 2. If writing to an address in Banks 1, 2, or 3, set the COBANK[1:0] (register PSBANK) for the appropriate bank.

- 3. Erase the 512-byte Flash page containing the target location, as described in Section 15.1.3.

- 4. Set the FLEWT bit (register FLSCL).

- 5. Set the PSWE bit (register PSCTL).

- 6. Clear the PSEE bit (register PSCTL).

- 7. Write the first key code to FLKEY: 0xA5.

- 8. Write the second key code to FLKEY: 0xF1.

- 9. Using the MOVX instruction, write a single data byte to the desired location within the 512-byte sector.

- 10.Clear the PSWE bit.

#### 15.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. Note that MOVX read instructions always target XRAM.

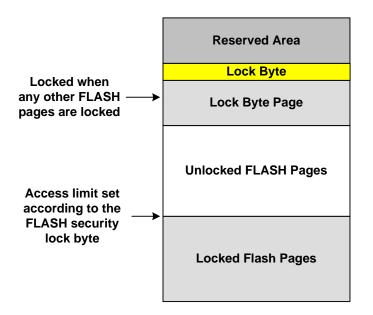

#### 15.3. Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to 1 before software can modify the Flash memory; both PSWE and PSEE must be set to 1 before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

A Security Lock Byte located at the last byte of Flash user space offers protection of the Flash program memory from access (reads, writes, or erases) by unprotected code or the C2 interface. The Flash security mechanism allows the user to lock n 512-byte Flash pages, starting at page 0 (addresses 0x0000 to 0x01FF), where n is the ones complement number represented by the Security Lock Byte. Note that the page containing the Flash Security Lock Byte is unlocked when no other Flash pages are locked (all bits of the Lock Byte are 1) and locked when any other Flash pages are locked (any bit of the Lock Byte is 0). See example in Figure 15.1.

| Security Lock Byte: | 11111101b                                  |

|---------------------|--------------------------------------------|

| 1s Complement:      | 0000010b                                   |

| Flash pages locked: | 3 (First two Flash pages + Lock Byte Page) |

#### Figure 15.1. Flash Program Memory Map

input voltage (on CP0+) is less than the inverting input voltage (on CP0–), the device is put into the reset state. After a Comparator0 reset, the C0RSEF flag (RST<u>SRC</u>.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

### 17.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA0) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "28.4. Watchdog Timer Mode" on page 324; the WDT is enabled and clocked by SYSCLK/12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

#### 17.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address above address 0xFBFF in Bank 3 on C8051F580/1/2/3/8/9 or any address in Bank 3 on C8051F584/5/6/7-F590/1 devices.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above address 0xFBFF in Bank 3 on C8051F580/1/2/3/8/9 or any address in Bank 3 on C8051F584/5/6/7-F590/1 devices.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above 0xFBFF in Bank 3 on C8051F580/1/2/3/8/9 or any address in Bank 3 on C8051F584/5/6/7-F590/1 devices.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "15.3. Security Options" on page 141).

- A Flash read, write, or erase is attempted when the VDD Monitor is not enabled to the high threshold and set as a reset source

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

### 17.8. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the RST pin is unaffected by this reset.

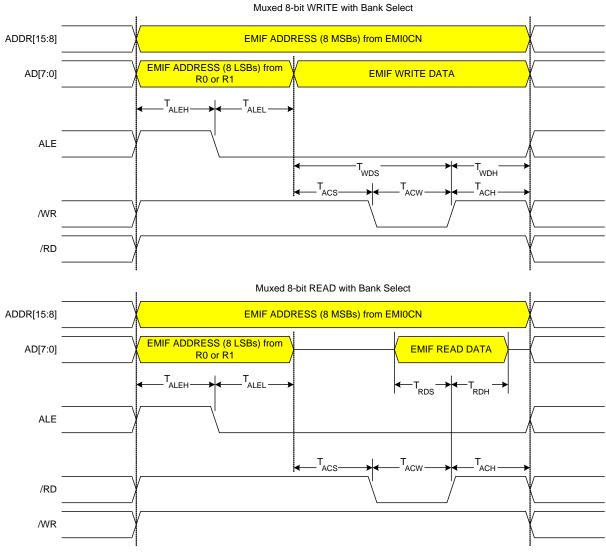

Figure 18.9. Multiplexed 8-bit MOVX with Bank Select Timing

#### **19.2. Programmable Internal Oscillator**

All C8051F58x/F59x devices include a programmable internal high-frequency oscillator that defaults as the system clock after a system reset. The internal oscillator period can be adjusted via the OSCICRS and OSCIFIN registers defined in SFR Definition 19.3 and SFR Definition 19.4. On C8051F58x/F59x devices, OSCICRS and OSCIFIN are factory calibrated to obtain a 24 MHz base frequency. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, 8, 16, 32, 64, or 128, as defined by the IFCN bits in register OSCICN. The divide value defaults to 128 following a reset.

#### 19.2.1. Internal Oscillator Suspend Mode

When software writes a logic 1 to SUSPEND (OSCICN.5), the internal oscillator is suspended. If the system clock is derived from the internal oscillator, the input clock to the peripheral or CIP-51 will be stopped until one of the following events occur:

- Port 0 Match Event.

- Port 1 Match Event.

- Port 2 Match Event.

- Port 3 Match Event.

- Comparator 0 enabled and output is logic 0.

When one of the oscillator awakening events occur, the internal oscillator, CIP-51, and affected peripherals resume normal operation, regardless of whether the event also causes an interrupt. The CPU resumes execution at the instruction following the write to SUSPEND.

Note: When entering suspend mode, firmware must be the ZTCEN bit in REF0CN (SFR Definition 8.1).

### LIN Register Definition 21.7. LIN0ERR: LIN0 Error Register

| Bit   | 7 | 6 | 5 | 4     | 3    | 2    | 1   | 0      |

|-------|---|---|---|-------|------|------|-----|--------|

| Name  |   |   |   | SYNCH | PRTY | TOUT | СНК | BITERR |

| Туре  | R | R | R | R     | R    | R    | R   | R      |

| Reset | 0 | 0 | 0 | 0     | 0    | 0    | 0   | 0      |

Indirect Address = 0x0A

| Bit | Name   | Function                                                                                                                                                  |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Unused | Read = 000b; Write = Don't Care                                                                                                                           |

| 4   | SYNCH  | Synchronization Error Bit (slave mode only).                                                                                                              |

|     |        | 0: No error with the SYNCH FIELD has been detected.                                                                                                       |

|     |        | 1: Edges of the SYNCH FIELD are outside of the maximum tolerance.                                                                                         |

| 3   | PRTY   | Parity Error Bit (slave mode only).                                                                                                                       |

|     |        | 0: No parity error has been detected.                                                                                                                     |

|     |        | 1: A parity error has been detected.                                                                                                                      |

| 2   | TOUT   | Timeout Error Bit.                                                                                                                                        |

|     |        | 0: A timeout error has not been detected.                                                                                                                 |

|     |        | 1: A timeout error has been detected. This error is detected whenever one of the fol-<br>lowing conditions is met:                                        |

|     |        | • The master is expecting data from a slave and the slave does not respond.                                                                               |

|     |        | The slave is expecting data but no data is transmitted on the bus.                                                                                        |

|     |        | <ul> <li>A frame is not finished within the maximum frame length.</li> <li>The application does not set the DTACK bit (LIN0CTRL.4) or STOP bit</li> </ul> |

|     |        | (LINOCTRL.7) until the end of the reception of the first byte after the identifier.                                                                       |

| 1   | СНК    | Checksum Error Bit.                                                                                                                                       |

|     |        | 0: Checksum error has not been detected.                                                                                                                  |

|     |        | 1: Checksum error has been detected.                                                                                                                      |

| 0   | BITERR | Bit Transmission Error Bit.                                                                                                                               |

|     |        | 0: No error in transmission has been detected.                                                                                                            |

|     |        | 1: The bit value monitored during transmission is different than the bit value sent.                                                                      |

#### LIN Register Definition 21.11. LIN0ID: LIN0 Identifier Register

| Bit   | 7 | 6 | 5       | 4   | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|---|---------|-----|---|---|---|---|--|--|--|

| Name  |   |   | ID[5:0] |     |   |   |   |   |  |  |  |

| Туре  | R | R |         | R/W |   |   |   |   |  |  |  |

| Reset | 0 | 0 | 0       | 0   | 0 | 0 | 0 | 0 |  |  |  |

Indirect Address = 0x0E

| Bit | Name    | Function                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused  | Read = 00b; Write = Don't Care.                                                                                                                                                             |

| 5:0 | ID[5:0] | LIN Identifier Bits.                                                                                                                                                                        |

|     |         | These bits form the data identifier.                                                                                                                                                        |

|     |         | If the LINSIZE bits (LIN0SIZE[3:0]) are 1111b, bits ID[5:4] are used to determine the data size and are interpreted as follows:<br>00: 2 bytes<br>01: 2 bytes<br>10: 4 bytes<br>11: 8 bytes |

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 23.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                 | Minimum SDA Setup Time                                                                                                                                                                                                                                                                                                                                                   | Minimum SDA Hold Time |  |  |  |  |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|--|--|--|--|

| 0                       | T <sub>low</sub> – 4 system clocks                                                                                                                                                                                                                                                                                                                                       | 3 system clocks       |  |  |  |  |  |  |  |  |

|                         | or                                                                                                                                                                                                                                                                                                                                                                       |                       |  |  |  |  |  |  |  |  |

|                         | 1 system clock + s/w delay*                                                                                                                                                                                                                                                                                                                                              |                       |  |  |  |  |  |  |  |  |

| 1                       | 11 system clocks                                                                                                                                                                                                                                                                                                                                                         | 12 system clocks      |  |  |  |  |  |  |  |  |

| software a<br>ACK is wi | 1       11 system clocks       12 system clocks         *Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. When using software acknowledgement, the s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero. |                       |  |  |  |  |  |  |  |  |

Table 23.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "23.3.4. SCL Low Timeout" on page 241). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 23.4).

| Baud Rate : | SYSCLK                                                          | <b>v</b> 1 | v   | 1         |

|-------------|-----------------------------------------------------------------|------------|-----|-----------|

| Dauu Nale = | $\frac{\text{SYSCLK}}{(65536 - (\text{SBRLH0}:\text{SBRLL0}))}$ | $^{2}$     | - 2 | Prescaler |

### Equation 24.1. UART0 Baud Rate

A quick reference for typical baud rates and clock frequencies is given in Table 24.1.

|        | Target Baud | Actual Baud | Baud Rate | Oscillator | SB0PS[1:0]       | Reload Value in |

|--------|-------------|-------------|-----------|------------|------------------|-----------------|

|        | Rate (bps)  | Rate (bps)  | Error     | Divide     | (Prescaler Bits) | SBRLH0:SBRLL0   |

|        |             |             |           | Factor     |                  |                 |

|        | 230400      | 230769      | 0.16%     | 208        | 11               | 0xFF98          |

|        | 115200      | 115385      | 0.16%     | 416        | 11               | 0xFF30          |

| : 48   | 57600       | 57554       | 0.08%     | 834        | 11               | 0xFE5F          |

| н<br>Т | 28800       | 28812       | 0.04%     | 1666       | 11               | 0xFCBF          |

| SYSCLK | 14400       | 14397       | 0.02%     | 3334       | 11               | 0xF97D          |

| SYS    | 9600        | 9600        | 0.00%     | 5000       | 11               | 0xF63C          |

| .,     | 2400        | 2400        | 0.00%     | 20000      | 11               | 0xD8F0          |

|        | 1200        | 1200        | 0.00%     | 40000      | 11               | 0xB1E0          |

|        | 230400      | 230769      | 0.16%     | 104        | 11               | 0xFFCC          |

|        | 115200      | 115385      | 0.16%     | 208        | 11               | 0xFF98          |

| 24     | 57600       | 57692       | 0.16%     | 416        | 11               | 0xFF30          |

| н<br>Т | 28800       | 28777       | 0.08%     | 834        | 11               | 0xFE5F          |

| SCL    | 14400       | 14406       | 0.04%     | 1666       | 11               | 0xFCBF          |

| SYSCLK | 9600        | 9600        | 0.00%     | 2500       | 11               | 0xFB1E          |

| •,     | 2400        | 2400        | 0.00%     | 10000      | 11               | 0xEC78          |

|        | 1200        | 1200        | 0.00%     | 20000      | 11               | 0xD8F0          |

|        | 230400      | 230769      | 0.16%     | 52         | 11               | 0xFFE6          |

|        | 115200      | 115385      | 0.16%     | 104        | 11               | 0xFFCC          |

| 12     | 57600       | 57692       | 0.16%     | 208        | 11               | 0xFF98          |

| =<br>T | 28800       | 28846       | 0.16%     | 416        | 11               | 0xFF30          |

| SYSCLK | 14400       | 14388       | 0.08%     | 834        | 11               | 0xFE5F          |

| λS     | 9600        | 9600        | 0.00%     | 1250       | 11               | 0xFD8F          |

| Ŭ,     | 2400        | 2400        | 0.00%     | 5000       | 11               | 0xF63C          |

|        | 1200        | 1200        | 0.00%     | 10000      | 11               | 0xEC78          |

### Table 24.1. Baud Rate Generator Settings for Standard Baud Rates

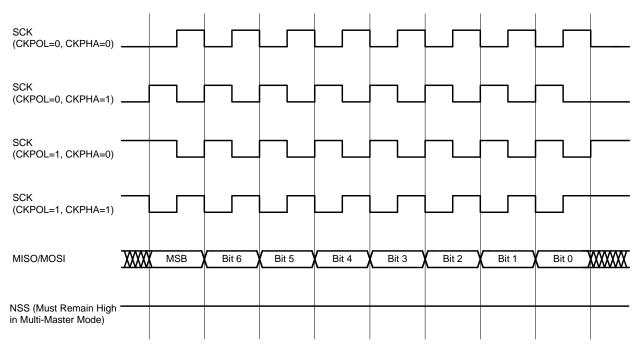

### 26.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 26.5. For slave mode, the clock and data relationships are shown in Figure 26.6 and Figure 26.7. CKPHA must be set to 0 on both the master and slave SPI when communicating between two of the following devices: C8051F04x, C8051F06x, C8051F12x, C8051F31x, C8051F32x, and C8051F33x.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 26.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

Figure 26.5. Master Mode Data/Clock Timing

## SFR Definition 27.16. TMR3L: Timer 3 Low Byte

| Bit   | 7          | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |

|-------|------------|---|---|----|---|---|---|---|--|--|--|

| Name  | TMR3L[7:0] |   |   |    |   |   |   |   |  |  |  |

| Туре  |            |   |   | R/ | W |   |   |   |  |  |  |

| Reset | 0          | 0 | 0 | 0  | 0 | 0 | 0 | 0 |  |  |  |

SFR Address = 0x94; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                          |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3L[7:0] | Timer 3 Low Byte.                                                                                                                                 |

|     |            | In 16-bit mode, the TMR3L register contains the low byte of the 16-bit Timer 3. In 8-<br>bit mode, TMR3L contains the 8-bit low byte timer value. |

### SFR Definition 27.17. TMR3H Timer 3 High Byte

| Bit   | 7          | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |

|-------|------------|---|---|----|---|---|---|---|--|--|--|

| Name  | TMR3H[7:0] |   |   |    |   |   |   |   |  |  |  |

| Туре  |            |   |   | R/ | W |   |   |   |  |  |  |

| Reset | 0          | 0 | 0 | 0  | 0 | 0 | 0 | 0 |  |  |  |

SFR Address = 0x95; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3H[7:0] | Timer 3 High Byte.                                                                                                                                  |

|     |            | In 16-bit mode, the TMR3H register contains the high byte of the 16-bit Timer 3. In 8-<br>bit mode, TMR3H contains the 8-bit high byte timer value. |

## SFR Definition 28.2. PCA0MD: PCA0 Mode

| Bit   | 7          | 6                                                                                                                                                                                                                                                                                           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4                             | 3             | 2            | 1               | 0        |  |  |

|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------|--------------|-----------------|----------|--|--|

| Name  | CIDL       | WDTE                                                                                                                                                                                                                                                                                        | WDLCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               | CPS2          | CPS1         | CPS0            | ECF      |  |  |

| Туре  | R/W        | R/W                                                                                                                                                                                                                                                                                         | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                             | R/W           | R/W          | R/W             | R/W      |  |  |

| Reset | t 0        | 1                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                             | 0             | 0            | 0               | 0        |  |  |

| SFR A | ddress = 0 | xD9; SFR Page                                                                                                                                                                                                                                                                               | e = 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |               |              |                 |          |  |  |

| Bit   | Name       |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               | Function      |              |                 |          |  |  |

| 7     | CIDL       | PCA0 Counte<br>Specifies PCA<br>0: PCA0 conti<br>1: PCA0 oper                                                                                                                                                                                                                               | 0 behavior v<br>nues to func                                                                                                                                                                                                                                                                                                                                                                                                                                            | when CPU is tion normall      | y while the s | ystem contro |                 |          |  |  |

| 6     | WDTE       | If this bit is se<br>0: Watchdog                                                                                                                                                                                                                                                            | Watchdog Timer Enable<br>If this bit is set, PCA0 Module 5 is used as the watchdog timer.<br>D: Watchdog Timer disabled.<br>1: PCA0 Module 5 enabled as Watchdog Timer.                                                                                                                                                                                                                                                                                                 |                               |               |              |                 |          |  |  |

| 5     | WDLCK      | Watchdog Tin<br>This bit locks/<br>Timer may no<br>0: Watchdog <sup>-</sup><br>1: Watchdog <sup>-</sup>                                                                                                                                                                                     | unlocks the N<br>t be disabled<br>Fimer Enable                                                                                                                                                                                                                                                                                                                                                                                                                          | l until the ne<br>e unlocked. |               |              | CK is set, the  | Watchdog |  |  |

| 4     | Unused     | Read = 0b, W                                                                                                                                                                                                                                                                                | rite = Don't d                                                                                                                                                                                                                                                                                                                                                                                                                                                          | are.                          |               |              |                 |          |  |  |

| 3:1   | CPS[2:0]   | These bits sel<br>000: System of<br>010: Timer 0 of<br>011: High-to-lo<br>100: System of<br>101: External<br>110: Timer 4 of                                                                                                                                                                | PCA0 Counter/Timer Pulse Select.         These bits select the timebase source for the PCA0 counter         000: System clock divided by 12         001: System clock divided by 4         010: Timer 0 overflow         011: High-to-low transitions on ECI (max rate = system clock divided by 4)         100: System clock         101: External clock divided by 8 (synchronized with the system clock)         110: Timer 4 overflow         111: Timer 5 overflow |                               |               |              |                 |          |  |  |

| 0     | ECF        | <ul> <li>PCA0 Counter/Timer Overflow Interrupt Enable.</li> <li>This bit sets the masking of the PCA0 Counter/Timer Overflow (CF) interrupt.</li> <li>0: Disable the CF interrupt.</li> <li>1: Enable a PCA0 Counter/Timer Overflow interrupt request when CF (PCA0CN.7) is set.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |               |              |                 |          |  |  |

| Note: |            | VDTE bit is set to<br>the PCA0MD re                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               | -             |              | odified. To cha | ange the |  |  |

### 29.4. Register Descriptions for PCA1

Following are detailed descriptions of the special function registers related to the operation of the PCA.

### SFR Definition 29.1. PCA1CN: PCA1 Control

| Bit   | 7          | 6                                                               | 5                                                                                                                                                                                                                                                                        | 4                              | 3                              | 2                               | 1               | 0           |  |

|-------|------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|---------------------------------|-----------------|-------------|--|

| Nam   | e CF1      | CR1                                                             | CCF6                                                                                                                                                                                                                                                                     | CCF7                           | CCF8                           | CCF9                            | CCF10           | CCF11       |  |

| Туре  | R/W        | R/W                                                             | R/W                                                                                                                                                                                                                                                                      | R/W                            | R/W                            | R/W                             | R/W             | R/W         |  |

| Rese  | <b>t</b> 0 | 0                                                               | 0                                                                                                                                                                                                                                                                        | 0                              | 0                              | 0                               | 0               | 0           |  |

| SFR A | ddress = 0 | xD8; Bit-Addres                                                 | sable; SFR                                                                                                                                                                                                                                                               | Page = 0x1                     | 0                              |                                 |                 | II          |  |

| Bit   | Name       |                                                                 |                                                                                                                                                                                                                                                                          | -                              | Function                       |                                 |                 |             |  |

| 7     | CF1        | PCA1 Counte                                                     | er/Timer Ov                                                                                                                                                                                                                                                              | erflow Flag.                   |                                |                                 |                 |             |  |

|       |            | Set by hardwa<br>When the Cou<br>CPU to vector<br>cleared by ha | inter/Timer C                                                                                                                                                                                                                                                            | Overflow (CF<br>1 interrupt se | 1) interrupt is ervice routine | s enabled, se<br>e. This bit is | etting this bit | causes the  |  |

| 6     | CR1        | PCA1 Counte                                                     | er/Timer Ru                                                                                                                                                                                                                                                              | n Control.                     |                                |                                 |                 |             |  |

|       |            | This bit enable                                                 |                                                                                                                                                                                                                                                                          |                                | ounter/Timer.                  |                                 |                 |             |  |

|       |            | 0: PCA1 Cour<br>1: PCA1 Cour                                    |                                                                                                                                                                                                                                                                          |                                |                                |                                 |                 |             |  |

| 5     | CCF11      | PCA1 Module                                                     |                                                                                                                                                                                                                                                                          |                                | Flag                           |                                 |                 |             |  |

| Ū     |            | This bit is set<br>is enabled, se<br>tine. This bit is          | by hardware<br>tting this bit                                                                                                                                                                                                                                            | when a mat<br>causes the (     | ch or capture<br>CPU to vecto  | or to the PCA                   | 1 interrupt s   | ervice rou- |  |

| 4     | CCF10      | PCA1 Module                                                     | e 10 Capture                                                                                                                                                                                                                                                             | e/Compare                      | Flag.                          |                                 |                 |             |  |

|       |            | This bit is set<br>is enabled, se<br>tine. This bit is          | tting this bit                                                                                                                                                                                                                                                           | causes the (                   | CPU to vecto                   | or to the PCA                   | 1 interrupt s   | ervice rou- |  |

| 3     | CCF9       | PCA1 Module                                                     | e 9 Capture                                                                                                                                                                                                                                                              | Compare F                      | lag.                           |                                 |                 |             |  |

|       |            | This bit is set<br>is enabled, se<br>tine. This bit is          | tting this bit                                                                                                                                                                                                                                                           | causes the (                   | CPU to vecto                   | or to the PCA                   | 1 interrupt s   | ervice rou- |  |

| 2     | CCF8       | PCA1 Module                                                     | e 8 Capture                                                                                                                                                                                                                                                              | Compare F                      | lag.                           |                                 |                 |             |  |

|       |            | is enabled, se                                                  | This bit is set by hardware when a match or capture occurs. When the CCF8 interrupt is enabled, setting this bit causes the CPU to vector to the PCA1 interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software. |                                |                                |                                 |                 |             |  |

| 1     | CCF7       | PCA1 Module                                                     | e 7 Capture                                                                                                                                                                                                                                                              | Compare F                      | lag.                           |                                 |                 |             |  |

|       |            | is enabled, se                                                  | This bit is set by hardware when a match or capture occurs. When the CCF7 interrupt is enabled, setting this bit causes the CPU to vector to the PCA1 interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.      |                                |                                |                                 |                 |             |  |

| 0     | CCF6       | PCA1 Module                                                     | e 6 Capture                                                                                                                                                                                                                                                              | Compare F                      | lag.                           |                                 |                 |             |  |

|       |            | This bit is set<br>is enabled, se<br>tine. This bit is          | tting this bit                                                                                                                                                                                                                                                           | causes the (                   | CPU to vecto                   | or to the PCA                   | 1 interrupt s   | ervice rou- |  |