Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 50MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), CANbus, LINbus, SPI, UART/USART |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                       |

| Number of I/O              | 25                                                               |

| Program Memory Size        | 96KB (96K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | · .                                                              |

| RAM Size                   | 8.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                     |

| Data Converters            | A/D 25x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-VFQFN Exposed Pad                                             |

| Supplier Device Package    | 32-QFN (5x5)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f586-im   |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | 18.4.2. Non-multiplexed Configuration                                       | 163 |

|-----|-----------------------------------------------------------------------------|-----|

|     | 18.5. Memory Mode Selection                                                 | 164 |

|     | 18.5.1. Internal XRAM Only                                                  |     |

|     | 18.5.2. Split Mode without Bank Select                                      | 164 |

|     | 18.5.3. Split Mode with Bank Select                                         | 165 |

|     | 18.5.4. External Only                                                       |     |

|     | 18.6. Timing                                                                | 165 |

|     | 18.6.1. Non-Multiplexed Mode                                                |     |

|     | 18.6.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111                       |     |

|     | 18.6.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111          |     |

|     | 18.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110                    |     |

|     | 18.6.2. Multiplexed Mode                                                    |     |

|     | 18.6.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011                       | 170 |

|     | 18.6.2.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011          |     |

|     | 18.6.2.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010                    |     |

| 19. | Oscillators and Clock Selection                                             |     |

|     | 19.1. System Clock Selection                                                |     |

|     | 19.2. Programmable Internal Oscillator                                      |     |

|     | 19.2.1. Internal Oscillator Suspend Mode                                    |     |

|     | 19.3. Clock Multiplier                                                      |     |

|     | 19.4. External Oscillator Drive Circuit                                     | 181 |

|     | 19.4.1. External Crystal Example                                            | 183 |

|     | 19.4.2. External RC Example.                                                |     |

|     | 19.4.3. External Capacitor Example                                          |     |

| 20. | Port Input/Output                                                           |     |

|     | 20.1. Port I/O Modes of Operation                                           | 188 |

|     | 20.1.1. Port Pins Configured for Analog I/O                                 |     |

|     | 20.1.2. Port Pins Configured For Digital I/O                                |     |

|     | 20.1.3. Interfacing Port I/O in a Multi-Voltage System                      | 189 |

|     | 20.2. Assigning Port I/O Pins to Analog and Digital Functions               |     |

|     | 20.2.1. Assigning Port I/O Pins to Analog Functions                         |     |

|     | 20.2.2. Assigning Port I/O Pins to Digital Functions                        | 189 |

|     | 20.2.3. Assigning Port I/O Pins to External Digital Event Capture Functions | 190 |

|     | 20.3. Priority Crossbar Decoder                                             |     |

|     | 20.4. Port I/O Initialization                                               |     |

|     | 20.5. Port Match                                                            | 198 |

|     | 20.6. Special Function Registers for Accessing and Configuring Port I/O     | 202 |

| 21. | Local Interconnect Network (LIN0)                                           |     |

|     | 21.1. Software Interface with the LIN Controller                            |     |

|     | 21.2. LIN Interface Setup and Operation                                     | 213 |

|     | 21.2.1. Mode Definition                                                     | 213 |

|     | 21.2.2. Baud Rate Options: Manual or Autobaud                               | 213 |

|     | 21.2.3. Baud Rate Calculations: Manual Mode                                 |     |

|     | 21.2.4. Baud Rate Calculations—Automatic Mode                               | 215 |

|     | 21.3. LIN Master Mode Operation                                             | 216 |

|     |                                                                             |     |

# Table 5.11. Temperature Sensor Electrical Characteristics

VDDA = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter                      | Conditions                                             | Min | Тур   | Max | Units |  |  |  |

|--------------------------------|--------------------------------------------------------|-----|-------|-----|-------|--|--|--|

| Linearity                      |                                                        | _   | ± 0.1 | _   | °C    |  |  |  |

| Slope                          |                                                        | _   | 3.33  | _   | mV/°C |  |  |  |

| Slope Error*                   |                                                        | _   | 100   | —   | µV/°C |  |  |  |

| Offset                         | Temp = 0 °C                                            | _   | 856   | —   | mV    |  |  |  |

| Offset Error*                  | Temp = 0 °C                                            | _   | 12    | —   | mV    |  |  |  |

| Power Supply Current           |                                                        | _   | 22    | _   | μA    |  |  |  |

| Tracking Time                  |                                                        | 12  |       | —   | μs    |  |  |  |

| *Note: Represents one standard | Note: Represents one standard deviation from the mean. |     |       |     |       |  |  |  |

## Table 5.12. Voltage Reference Electrical Characteristics

VDDA = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter                       | Parameter Conditions                            |      |      |           | Units  |

|---------------------------------|-------------------------------------------------|------|------|-----------|--------|

| Internal Reference (REFBE       | = 1)                                            | 1    | 1    | 1         |        |

| Output Voltage                  | 25 °C ambient (REFLV = 0)                       | 1.45 | 1.50 | 1.55      | v      |

|                                 | 25 °C ambient (REFLV = 1), $V_{DD}$ = 2.6 V     | 2.15 | 2.20 | 2.25      | V      |

| VREF Short-Circuit Current      |                                                 | —    | 5    | 10        | mA     |

| VREF Temperature<br>Coefficient |                                                 | _    | 22   |           | ppm/°C |

| Power Consumption               | Internal                                        | _    | 30   | 50        | μA     |

| Load Regulation                 | Load = 0 to 200 µA to AGND                      | _    | 3    |           | μV/μA  |

| VREF Turn-on Time 1             | 4.7 $\mu$ F and 0.1 $\mu$ F bypass              |      | 1.5  |           | ms     |

| VREF Turn-on Time 2             | 0.1 μF bypass                                   |      | 46   |           | μs     |

| Power Supply Rejection          |                                                 | —    | 1.2  | —         | mV/V   |

| External Reference (REFBI       | E = 0)                                          | 1    | 1    |           |        |

| Input Voltage Range             |                                                 | 1.5  | _    | $V_{DDA}$ | V      |

| Input Current                   | Sample Rate = 200 ksps; VREF = 1.5 V            |      | 2.5  |           | μA     |

| Power Specifications            |                                                 | 1    | 1    |           |        |

| Reference Bias Generator        | Reference Bias Generator REFBE = 1 or TEMPE = 1 |      |      | 40        | μA     |

### 6.5. ADC0 Analog Multiplexer

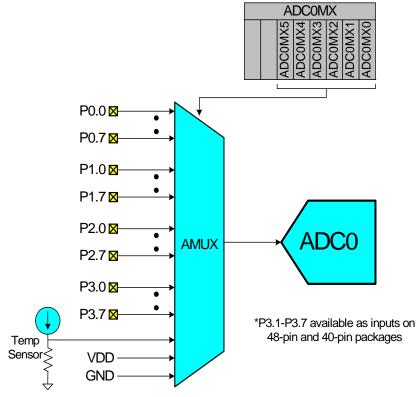

ADC0 includes an analog multiplexer to enable multiple analog input sources. Any of the following may be selected as an input: P0.0–P3.7, the on-chip temperature sensor, the core power supply ( $V_{DD}$ ), or ground (GND). **ADC0 is single-ended and all signals measured are with respect to GND.** The ADC0 input channels are selected using the ADC0MX register as described in SFR Definition 6.13.

Figure 6.8. ADC0 Multiplexer Block Diagram

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to 0 the corresponding bit in register PnMDIN. To force the Crossbar to skip a Port pin, set to 1 the corresponding bit in register PnSKIP. See Section "20. Port Input/Output" on page 188 for more Port I/O configuration details.

# SFR Definition 6.13. ADC0MX: ADC0 Channel Select

| Bit                                  | 7                                              | 6           | 5                             | 4        | 3             | 2            | 1           | 0  |  |  |  |

|--------------------------------------|------------------------------------------------|-------------|-------------------------------|----------|---------------|--------------|-------------|----|--|--|--|

| Nam                                  | е                                              |             |                               |          | ADCON         | /IX[5:0]     |             |    |  |  |  |

| Туре                                 |                                                | R           |                               |          | R/            | W            |             |    |  |  |  |

| Rese                                 | et 0                                           | 0           | 1                             | 1        | 1             | 1            | 1           | 1  |  |  |  |

| SFR Address = 0xBB; SFR Page = 0x00; |                                                |             |                               |          |               |              |             |    |  |  |  |

| Bit                                  | Name                                           |             | Function                      |          |               |              |             |    |  |  |  |

| 7:6                                  | Unused                                         | Read = 00b; | ad = 00b; Write = Don't Care. |          |               |              |             |    |  |  |  |

| 5:0                                  | 5:0 AMX0P[5:0] AMUX0 Positive Input Selection. |             |                               |          |               |              |             |    |  |  |  |

|                                      |                                                | 000000:     | P0.0                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 000001:     | P0.1                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 000010:     | P0.2                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 000011:     | P0.3                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 000100:     | P0.4                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 000101:     | P0.5                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 000110:     | P0.6                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 000111:     | P0.7                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 001000:     | P1.0                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 001001:     | P1.1                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 001010:     | P1.2                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 001011:     | P1.3                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 001100:     | P1.4                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 001101:     | P1.5                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 001110:     | P1.6                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 001111:     | P1.7                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 010000:     | P2.0                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 010001:     | P2.1                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 010010:     | P2.2                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 010011:     | P2.3                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 010100:     | P2.4                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 010101:     | P2.5                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 010110:     | P2.6                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 010111:     | P2.7                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 011000:     | P3.0                          |          |               |              |             |    |  |  |  |

|                                      |                                                | 011001:     |                               | •        | on 48-pin and |              | -           |    |  |  |  |

|                                      |                                                | 011010:     |                               | •        | on 48-pin and |              | -           |    |  |  |  |

|                                      |                                                | 011011:     |                               | •        | on 48-pin and |              | -           | ,  |  |  |  |

|                                      |                                                | 011100:     |                               | •        | on 48-pin and |              | -           | ,  |  |  |  |

|                                      |                                                | 011101:     |                               | •        | on 48-pin and |              | -           | ,  |  |  |  |

|                                      |                                                | 011110:     |                               | •        | on 48-pin and |              | -           |    |  |  |  |

|                                      |                                                | 011111:     |                               | •        | on 48-pin and | d 40-pin pac | kage device | S) |  |  |  |

|                                      |                                                | 100000-101  |                               | erved    |               |              |             |    |  |  |  |

|                                      |                                                | 110000:     |                               | p Sensor |               |              |             |    |  |  |  |

|                                      |                                                | 110001:     | V <sub>DD</sub>               |          |               |              |             |    |  |  |  |

|                                      |                                                | 110010-1111 | 11: GNE                       | )        |               |              |             |    |  |  |  |

### SFR Definition 12.1. PSBANK: Program Space Bank Select

| Bit   | 7   | 6   | 5    | 4       | 3   | 2   | 1     | 0       |

|-------|-----|-----|------|---------|-----|-----|-------|---------|

| Name  |     |     | COBA | NK[1:0] |     |     | IFBAN | IK[1:0] |

| Туре  | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W   | R/W     |

| Reset | 0   | 0   | 0    | 1       | 0   | 0   | 0     | 1       |

#### SFR Address = 0xF5; SFR Page = All Pages

| Bit   | Name                   | Function                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6   | Reserved               | Read = 00b, Must Write = 00b.                                                                                                                                                                                                                                                                                                                                                                                     |

| 5:4   | COBANK[1:0]            | Constant Operations Bank Select.                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                        | <ul> <li>These bits select which Flash bank is targeted during constant operations (MOVC and Flash MOVX) involving address 0x8000 to 0xFFF.</li> <li>00: Constant Operations Target Bank 0 (note that Bank 0 is also mapped between 0x0000 to 0x7FFF).</li> <li>01: Constant operations target Bank 1.</li> <li>10: Constant operations target Bank 2.</li> <li>11: Constant operations target Bank 3.</li> </ul> |

| 3:2   | Reserved               | Read = 00b, Must Write = 00b.                                                                                                                                                                                                                                                                                                                                                                                     |

| 1:0   | IFBANK[1:0]            | Instruction Fetch Operations Bank Select.These bits select which Flash bank is used for instruction fetches involving address0x8000 to 0xFFFF. These bits can only be changed from code in Bank 0.00: Instructions fetch from Bank 0 (note that Bank 0 is also mapped between0x0000 to 0x7FFF).01: Instructions fetch from Bank 1.10: Instructions fetch from Bank 2.11: Instructions fetch from Bank 3.          |

| Note: | COBANK[1:0] a devices. | nd IFBANK[1:0] should not be set to select Bank 3 (11b) on the C8051F584/5/6/7-F590/1                                                                                                                                                                                                                                                                                                                             |

#### 12.1.1. MOVX Instruction and Program Memory

The MOVX instruction in an 8051 device is typically used to access external data memory. On the C8051F58x/F59x devices, the MOVX instruction is normally used to read and write on-chip XRAM, but can be re-configured to write and erase on-chip Flash memory space. MOVC instructions are always used to read Flash memory, while MOVX write instructions are used to erase and write Flash. This Flash access feature provides a mechanism for the C8051F58x/F59x to update program code and use the program memory space for non-volatile data storage. Refer to Section "15. Flash Memory" on page 138 for further details.

#### 12.2. Data Memory

The C8051F58x/F59x devices include 8448 bytes of RAM data memory. 256 bytes of this memory is mapped into the internal RAM space of the 8051. The other 8192 bytes of this memory is on-chip "external" memory. The data memory map is shown in Figure 12.1 for reference.

# SFR Definition 14.2. IP: Interrupt Priority

| Bit   | 7          | 6                                                                                 | 5                                                                                                                                                                                                                       | 4                              | 3              | 2             | 1   | 0   |

|-------|------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|---------------|-----|-----|

| Nam   | e          | PSPI0                                                                             | PT2                                                                                                                                                                                                                     | PS0                            | PT1            | PX1           | PT0 | PX0 |

| Туре  | R          | R/W                                                                               | R/W                                                                                                                                                                                                                     | R/W                            | R/W            | R/W           | R/W | R/W |

| Rese  | t 1        | 0                                                                                 | 0                                                                                                                                                                                                                       | 0                              | 0              | 0             | 0   | 0   |

| SFR A | ddress = 0 | xB8; Bit-Addres                                                                   | sable; SFR                                                                                                                                                                                                              | Page = All F                   | Pages          |               |     |     |

| Bit   | Name       |                                                                                   |                                                                                                                                                                                                                         |                                | Function       |               |     |     |

| 7     | Unused     | Read = 1b, W                                                                      | rite = Don't (                                                                                                                                                                                                          | Care.                          |                |               |     |     |

| 6     | PSPI0      | Serial Periph<br>This bit sets th<br>0: SPI0 interru<br>1: SPI0 interru           | ne priority of<br>opt set to low                                                                                                                                                                                        | the SPI0 int<br>priority leve  | errupt.<br>el. | rity Control. |     |     |

| 5     | PT2        | <b>Timer 2 Intern</b><br>This bit sets th<br>0: Timer 2 inter<br>1: Timer 2 inter | ne priority of<br>errupt set to                                                                                                                                                                                         | the Timer 2<br>low priority le | evel.          |               |     |     |

| 4     | PS0        | UART0 Interr<br>This bit sets th<br>0: UART0 inte<br>1: UART0 inte                | ne priority of<br>rrupt set to l                                                                                                                                                                                        | the UART0<br>ow priority le    | evel.          |               |     |     |

| 3     | PT1        | Timer 1 Intern<br>This bit sets th<br>0: Timer 1 inte<br>1: Timer 1 inte          | ne priority of<br>errupt set to                                                                                                                                                                                         | the Timer 1<br>low priority le | evel.          |               |     |     |

| 2     | PX1        | This bit sets th<br>0: External Int                                               | External Interrupt 1 Priority Control.<br>This bit sets the priority of the External Interrupt 1 interrupt.<br>D: External Interrupt 1 set to low priority level.<br>: External Interrupt 1 set to high priority level. |                                |                |               |     |     |

| 1     | PT0        | This bit sets th<br>0: Timer 0 inte                                               | Finer 0 Interrupt Priority Control.         This bit sets the priority of the Timer 0 interrupt.         D: Timer 0 interrupt set to low priority level.         I: Timer 0 interrupt set to high priority level.       |                                |                |               |     |     |

| 0     | PX0        | This bit sets th<br>0: External Int                                               | External Interrupt 0 Priority Control.<br>This bit sets the priority of the External Interrupt 0 interrupt.<br>D: External Interrupt 0 set to low priority level.<br>: External Interrupt 0 set to high priority level. |                                |                |               |     |     |

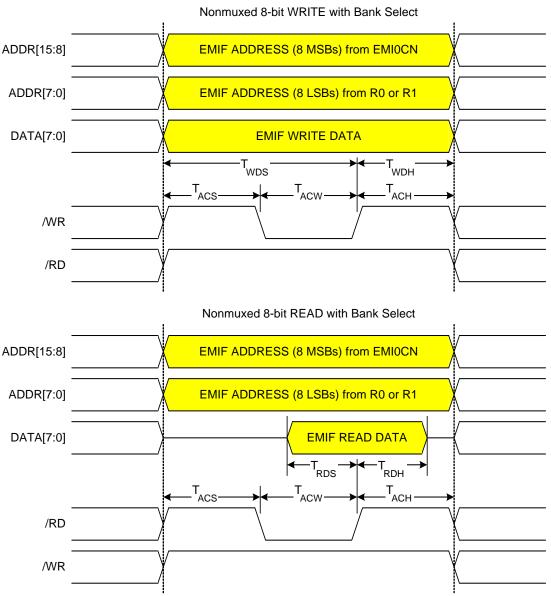

### 18.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110

Figure 18.6. Non-multiplexed 8-bit MOVX with Bank Select Timing

# SFR Definition 19.5. CLKMUL: Clock Multiplier

| Bit   | 7     | 6       | 5      | 4                   | 3 | 2 | 1       | 0 |

|-------|-------|---------|--------|---------------------|---|---|---------|---|

| Name  | MULEN | MULINIT | MULRDY | MULDIV[2:0] MULSEL[ |   |   | EL[1:0] |   |

| Туре  | R/W   | R/W     | R      | R/W                 |   |   | R/      | W |

| Reset | 0     | 0       | 0      | 0                   | 0 | 0 | 0       | 0 |

#### SFR Address = 0x97; SFR Page = 0x0F;

| Bit   | Name        |                                      | Function                                                                        |                                                                            |  |  |  |  |  |

|-------|-------------|--------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|

| 7     | MULEN       | Clock Multiplie<br>0: Clock Multipli |                                                                                 |                                                                            |  |  |  |  |  |

|       |             |                                      | 1: Clock Multiplier enabled.                                                    |                                                                            |  |  |  |  |  |

| 6     | MULINIT     | Clock Multiplie                      | r Initialize.                                                                   |                                                                            |  |  |  |  |  |

|       |             |                                      | the Clock Multiplier. The MULRD                                                 | . Once enabled, writing a 1 to this<br>Y bit reads 1 when the Clock Mul-   |  |  |  |  |  |

| 5     | MULRDY      | Clock Multiplie                      | er Ready.                                                                       |                                                                            |  |  |  |  |  |

|       |             | 0: Clock Multipli                    |                                                                                 |                                                                            |  |  |  |  |  |

|       |             | 1: Clock Multipli                    | er is ready (PLL is locked).                                                    |                                                                            |  |  |  |  |  |

| 4:2   | MULDIV[2:0] | <b>Clock Multiplie</b>               | r Output Scaling Factor.                                                        |                                                                            |  |  |  |  |  |

|       |             |                                      | iplier Output scaled by a factor o                                              |                                                                            |  |  |  |  |  |

|       |             |                                      | iplier Output scaled by a factor o                                              |                                                                            |  |  |  |  |  |

|       |             |                                      | iplier Output scaled by a factor o                                              |                                                                            |  |  |  |  |  |

|       |             |                                      | plier Output scaled by a factor of                                              |                                                                            |  |  |  |  |  |

|       |             |                                      | iplier Output scaled by a factor o<br>iplier Output scaled by a factor o        | . ,                                                                        |  |  |  |  |  |

|       |             |                                      | iplier Output scaled by a factor o                                              |                                                                            |  |  |  |  |  |

|       |             |                                      | plier Output scaled by a factor of                                              |                                                                            |  |  |  |  |  |

|       |             |                                      | ck Multiplier output duty cycle is i                                            |                                                                            |  |  |  |  |  |

| 1:0   | MULSEL[1:0] | Clock Multiplie                      | er Input Select.                                                                |                                                                            |  |  |  |  |  |

|       |             | These bits seled                     | ct the clock supplied to the Clock                                              | Multiplier                                                                 |  |  |  |  |  |

|       |             | MULSEL[1:0]                          | Selected Input Clock                                                            | Clock Multiplier Output<br>for MULDIV[2:0] = 000b                          |  |  |  |  |  |

|       |             | 00                                   | 00 Internal Oscillator Internal Oscillator x 2                                  |                                                                            |  |  |  |  |  |

|       |             | 01                                   | 01 External Oscillator External Oscillator x 2                                  |                                                                            |  |  |  |  |  |

|       |             | 10                                   | Internal Oscillator                                                             | Internal Oscillator x 4                                                    |  |  |  |  |  |

|       |             | 11                                   | External Oscillator                                                             | External Oscillator x 4                                                    |  |  |  |  |  |

| Notes |             |                                      | MHz, and so the Clock Multiplier outp<br>scillator x 2 is selected using the MU | ut should be scaled accordingly. If<br>JLSEL bits, MULDIV[2:0] is ignored. |  |  |  |  |  |

## 19.4. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 19.1. A 10 M $\Omega$  resistor also must be wired across the XTAL2 and XTAL1 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 19.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 19.6).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.2 and P0.3 are used as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.3 is used as XTAL2. The Port I/O Crossbar should be configured to skip the Port pins used by the oscillator circuit; see Section "20.3. Priority Crossbar Decoder" on page 192 for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as **analog inputs**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See Section "20.4. Port I/O Initialization" on page 195 for details on Port input mode selection.

#### 19.4.1. External Crystal Example

If a crystal or ceramic resonator is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 19.1, Option 1. The External Oscillator Frequency Control value (XFCN) should be chosen from the Crystal column of the table in SFR Definition 19.6 (OSCXCN register). For example, an 11.0592 MHz crystal requires an XFCN setting of 111b and a 32.768 kHz Watch Crystal requires an XFCN setting of 001b. After an external 32.768 kHz oscillator is stabilized, the XFCN setting can be switched to 000 to save power. It is recommended to enable the missing clock detector before switching the system clock to any external oscillator source.

**Note:** Small surface mount crystals can have maximum drive level specifications that are exceeded by the above XFCN recommendations. In these cases, a software-controlled startup sequence may be used to reliably start the crystal using a higher XFCN setting, and then lowering the XFCN setting once the oscillator has started to reduce the drive level and prevent damage or premature aging of the crystal. In all cases, the drive level should be measured to ensure that the crystal is being driven within its operational guidelines as part of robust oscillator system design. Contact technical support for additional details and recommendations if using surface mount crystals with these devices.

When the crystal oscillator is first enabled, the oscillator amplitude detection circuit requires a settling time to achieve proper bias. Introducing a delay of 1 ms between enabling the oscillator and checking the XTLVLD bit will prevent a premature switch to the external oscillator as the system clock. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure is:

- 1. Force XTAL1 and XTAL2 to a high state. This involves enabling the Crossbar and writing 1 to the port pins associated with XTAL1 and XTAL2.

- 2. Configure XTAL1 and XTAL2 as analog inputs using.

- 3. Enable the external oscillator.

- 4. Wait at least 1 ms.

- 5. Poll for XTLVLD => 1.

- 6. Enable the Missing Clock Detector.

- 7. Switch the system clock to the external oscillator.

**Important Note on External Crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

The capacitors shown in the external crystal configuration provide the load capacitance required by the crystal for correct oscillation. These capacitors are "in series" as seen by the crystal and "in parallel" with the stray capacitance of the XTAL1 and XTAL2 pins.

**Note:** The desired load capacitance depends upon the crystal and the manufacturer. Refer to the crystal data sheet when completing these calculations.

For example, a tuning-fork crystal of 32.768 kHz with a recommended load capacitance of 12.5 pF should use the configuration shown in Figure 19.1, Option 1. The total value of the capacitors and the stray capacitance of the XTAL pins should equal 25 pF. With a stray capacitance of 3 pF per pin, the 22 pF capacitors yield an equivalent capacitance of 12.5 pF across the crystal, as shown in Figure 19.3.

## SFR Definition 20.22. P2MDIN: Port 2 Input Mode

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|-------------|---|---|---|---|---|---|--|--|

| Name  |   | P2MDIN[7:0] |   |   |   |   |   |   |  |  |

| Туре  |   | R/W         |   |   |   |   |   |   |  |  |

| Reset | 1 | 1           | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

#### SFR Address = 0xF3; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                  |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P2MDIN[7:0] | Analog Configuration Bits for P2.7–P2.0 (respectively).                                                                                                                                                                                                                                                                                                   |

|     |             | <ul> <li>Port pins configured for analog mode have their weak pull-up and digital receiver disabled. For analog mode, the pin also needs to be configured for open-drain mode in the P2MDOUT register.</li> <li>0: Corresponding P2.n pin is configured for analog mode.</li> <li>1: Corresponding P2.n pin is not configured for analog mode.</li> </ul> |

## SFR Definition 20.23. P2MDOUT: Port 2 Output Mode

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|--------------|---|---|---|---|---|---|--|

| Name  |   | P2MDOUT[7:0] |   |   |   |   |   |   |  |

| Туре  |   | R/W          |   |   |   |   |   |   |  |

| Reset | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |  |

### SFR Address = 0xA6; SFR Page = 0x0F

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P2MDOUT[7:0] | Output Configuration Bits for P2.7–P2.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P2MDIN is logic 0.<br>0: Corresponding P2.n Output is open-drain.<br>1: Corresponding P2.n Output is push-pull. |

## SFR Definition 20.30. P4MDOUT: Port 4 Output Mode

| Bit   | 7                | 6                                                                                         | 5        | 4 | 3        | 2 | 1 | 0 |  |  |

|-------|------------------|-------------------------------------------------------------------------------------------|----------|---|----------|---|---|---|--|--|

| Nam   | e                | P4MDOUT[7:0]                                                                              |          |   |          |   |   |   |  |  |

| Туре  | e                | R/W                                                                                       |          |   |          |   |   |   |  |  |

| Rese  | et 0 0 0 0 0 0 0 |                                                                                           |          |   |          |   |   | 0 |  |  |

| SFR A | Address = 0xA    | F; SFR Pag                                                                                | e = 0x0F |   |          |   |   |   |  |  |

| Bit   | Name             |                                                                                           |          |   | Function |   |   |   |  |  |

| 7:0   | P4MDOUT[7:       | 4MDOUT[7:0] Output Configuration Bits for P4.7–P4.0 (respectively).                       |          |   |          |   |   |   |  |  |

|       |                  | 0: Corresponding P4.n Output is open-drain.<br>1: Corresponding P4.n Output is push-pull. |          |   |          |   |   |   |  |  |

Note: Port 4.0 is only available on the 48-pin and 40-pin packages.; P4.1-P4.7 is only available on the 48-pin packages.

213

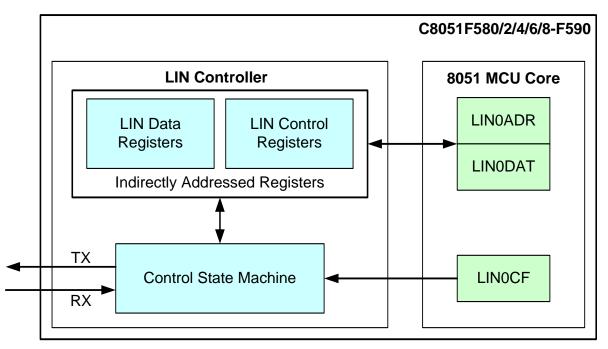

# 21. Local Interconnect Network (LIN0)

**Important Note:** This chapter assumes an understanding of the Local Interconnect Network (LIN) protocol. For more information about the LIN protocol, including specifications, please refer to the LIN consortium (http://www.lin-subbus.org).

LIN is an asynchronous, serial communications interface used primarily in automotive networks. The Silicon Laboratories LIN controller is compliant to the 2.1 Specification, implements a complete hardware LIN interface and includes the following features:

- Selectable Master and Slave modes.

- Automatic baud rate option in slave mode.

- The internal oscillator is accurate to within 0.5% of 24 MHz across the entire temperature range and for VDD voltages greater than or equal to the minimum output of the on-chip voltage regulator, so an external oscillator is not necessary for master mode operation for most systems.

Note: The minimum system clock (SYSCLK) required when using the LIN controller is 8 MHz.

Figure 21.1. LIN Block Diagram

The LIN controller has four main components:

- LIN Access Registers—Provide the interface between the MCU core and the LIN controller.

- LIN Data Registers—Where transmitted and received message data bytes are stored.

- LIN Control Registers—Control the functionality of the LIN interface.

- Control State Machine and Bit Streaming Logic—Contains the hardware that serializes messages and controls the bus timing of the controller.

|                 | Baud (bits/sec) |       |      |        |       |      |       |       |      |       |       |      |       |       |      |

|-----------------|-----------------|-------|------|--------|-------|------|-------|-------|------|-------|-------|------|-------|-------|------|

|                 | 20 K            |       |      | 19.2 K |       |      |       | 9.6 K |      | 4.8 K |       |      | 1 K   |       |      |

| SYSCLK<br>(MHz) | Mult.           | Pres. | Div. | Mult.  | Pres. | Div. | Mult. | Pres. | Div. | Mult. | Pres. | Div. | Mult. | Pres. | Div. |

| 25              | 0               | 1     | 312  | 0      | 1     | 325  | 1     | 1     | 325  | 3     | 1     | 325  | 19    | 1     | 312  |

| 24.5            | 0               | 1     | 306  | 0      | 1     | 319  | 1     | 1     | 319  | 3     | 1     | 319  | 19    | 1     | 306  |

| 24              | 0               | 1     | 300  | 0      | 1     | 312  | 1     | 1     | 312  | 3     | 1     | 312  | 19    | 1     | 300  |

| 22.1184         | 0               | 1     | 276  | 0      | 1     | 288  | 1     | 1     | 288  | 3     | 1     | 288  | 19    | 1     | 276  |

| 16              | 0               | 1     | 200  | 0      | 1     | 208  | 1     | 1     | 208  | 3     | 1     | 208  | 19    | 1     | 200  |

| 12.25           | 0               | 0     | 306  | 0      | 0     | 319  | 1     | 0     | 319  | 3     | 0     | 319  | 19    | 0     | 306  |

| 12              | 0               | 0     | 300  | 0      | 0     | 312  | 1     | 0     | 312  | 3     | 0     | 312  | 19    | 0     | 300  |

| 11.0592         | 0               | 0     | 276  | 0      | 0     | 288  | 1     | 0     | 288  | 3     | 0     | 288  | 19    | 0     | 276  |

| 8               | 0               | 0     | 200  | 0      | 0     | 208  | 1     | 0     | 208  | 3     | 0     | 208  | 19    | 0     | 200  |

Table 21.2. Manual Baud Rate Parameters Examples

#### 21.2.4. Baud Rate Calculations—Automatic Mode

If the LIN controller is configured for slave mode, only the prescaler and divider need to be calculated:

prescaler =

$$\ln \left[ \frac{\text{SYSCLK}}{4000000} \right] \times \frac{1}{\ln 2} - 1$$

divider =  $\frac{\text{SYSCLK}}{2^{(\text{prescaler} + 1)} \times 20000}$

The following example calculates the values of these variables for a 24 MHz system clock:

prescaler =

$$ln \left[ \frac{24000000}{4000000} \right] \times \frac{1}{ln2} - 1 = 1.585 \cong 1$$

divider =

$$\frac{24000000}{2^{(1+1)} \times 20000}$$

= 300

Table 21.3 presents some typical values of system clock and baud rate along with their factors.

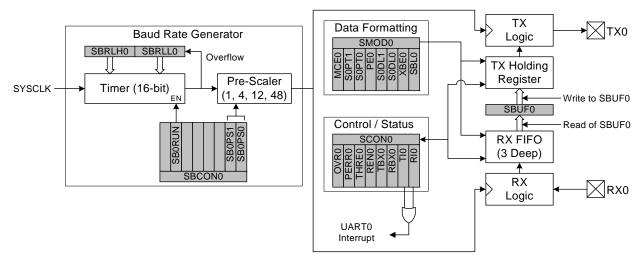

# 24. UART0

UART0 is an asynchronous, full duplex serial port offering a variety of data formatting options. A dedicated baud rate generator with a 16-bit timer and selectable prescaler is included, which can generate a wide range of baud rates (details in Section "24.1. Baud Rate Generator" on page 256). A received data FIFO allows UART0 to receive up to three data bytes before data is lost and an overflow occurs.

UART0 has six associated SFRs. Three are used for the Baud Rate Generator (SBCON0, SBRLH0, and SBRLL0), two are used for data formatting, control, and status functions (SCON0, SMOD0), and one is used to send and receive data (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Writes to SBUF0 always access the Transmit register. Reads of SBUF0 always access the buffered Receive register; it is not possible to read data from the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete). If additional bytes are available in the Receive FIFO, the RI0 bit cannot be cleared by software.

Figure 24.1. UART0 Block Diagram

### 24.1. Baud Rate Generator

The UART0 baud rate is generated by a dedicated 16-bit timer which runs from the controller's core clock (SYSCLK) and has prescaler options of 1, 4, 12, or 48. The timer and prescaler options combined allow for a wide selection of baud rates over many clock frequencies.

The baud rate generator is configured using three registers: SBCON0, SBRLH0, and SBRLL0. The UART0 Baud Rate Generator Control Register (SBCON0, SFR Definition 24.4) enables or disables the baud rate generator, selects the clock source for the baud rate generator, and selects the prescaler value for the timer. The baud rate generator must be enabled for UART0 to function. Registers SBRLH0 and SBRLL0 contain a 16-bit reload value for the dedicated 16-bit timer. The internal timer counts up from the reload value on every clock tick. On timer overflows (0xFFFF to 0x0000), the timer is reloaded. The baud rate for UART0 is defined in Equation 24.1, where "BRG Clock" is the baud rate generator's selected clock source. For reliable UART operation, it is recommended that the UART baud rate is not configured for baud rates faster than SYSCLK/16.

| Table 25.1. Timer Settings for Standard Baud Rates |

|----------------------------------------------------|

| Using The Internal 24 MHz Oscillator               |

|                                     |                              |                      | Fre                              | equency: 24 Ml        | Hz                                              |                  |                                  |  |

|-------------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|--|

|                                     | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |  |

|                                     | 230400                       | 0.16%                | 104                              | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCC                             |  |

|                                     | 115200                       | 0.16%                | 208                              | SYSCLK                | XX                                              | 1                | 0x98                             |  |

|                                     | 57600                        | -0.08%               | 417                              | SYSCLK                | XX                                              | 1                | 0x30                             |  |

| from<br>Jsc.                        | 28800                        | 0.04%                | 833                              | SYSCLK/4              | 01                                              | 0                | 0x98                             |  |

| <ul><li>froi</li><li>Osc.</li></ul> | 14400                        | -0.02%               | 1667                             | SYSCLK/12             | 00                                              | 0                | 0x30                             |  |

| 'SCLK<br>ernal C                    | 9600                         | 0.00%                | 2500                             | SYSCLK/12             | 00                                              | 0                | 0x98                             |  |

| SYSCL <sup>I</sup><br>Internal      | 2400                         | 0.00%                | 10000                            | SYSCLK/48             | 10                                              | 0                | 0x98                             |  |

| SY<br>Inte                          | 1200                         | 0.00%                | 20000                            | SYSCLK/48             | 10                                              | 0                | 0x30                             |  |

|                                     |                              |                      |                                  |                       |                                                 |                  |                                  |  |

## SFR Definition 27.13. TMR3CN: Timer 3 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1 | 0      |

|-------|------|------|--------|--------|---------|-----|---|--------|

| Name  | TF3H | TF3L | TF3LEN | TF3CEN | T3SPLIT | TR3 |   | T3XCLK |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R | R/W    |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0 | 0      |

### SFR Address = 0x91; SFR Page = 0x00

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF3H    | Timer 3 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |         | Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                               |

| 6   | TF3L    | Timer 3 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |         | Set by hardware when the Timer 3 low byte overflows from 0xFF to 0x00. TF3L will be set when the low byte overflows regardless of the Timer 3 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                            |

| 5   | TF3LEN  | Timer 3 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |         | When set to 1, this bit enables Timer 3 Low Byte interrupts. If Timer 3 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 3 overflows.                                                                                                                                                                                                                                                                                                       |

| 4   | TF3CEN  | Timer 3 Capture Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |         | 0: Timer 3 Capture Mode is disabled.<br>1: Timer 3 Capture Mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3   | T3SPLIT | Timer 3 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |         | When this bit is set, Timer 3 operates as two 8-bit timers with auto-reload.                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |         | 0: Timer 3 operates in 16-bit auto-reload mode.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |         | 1: Timer 3 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2   | TR3     | Timer 3 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |         | Timer 3 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables TMR3H only; TMR3L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                          |

| 1   | Unused  | Read = 0b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0   | T3XCLK  | Timer 3 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |         | This bit selects the external clock source for Timer 3. If Timer 3 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 3 Clock Select bits (T3MH and T3ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.<br>0: Timer 3 clock is the system clock divided by 12.<br>1: Timer 3 clock is the external clock divided by 8 (synchronized with SYSCLK). |

## SFR Definition 27.20. TMRnCAPL: Timer 4 and 5 Capture Register Low Byte

| Bit  | 7           | 6                                                                                                                                                                                                            | 5           | 4           | 3            | 2           | 1      | 0 |  |

|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|--------------|-------------|--------|---|--|

| Nam  | e           | TMRnRLL[7:0]                                                                                                                                                                                                 |             |             |              |             |        |   |  |

| Туре | •           | R/W                                                                                                                                                                                                          |             |             |              |             |        |   |  |

| Rese | et 0        | 0 0 0 0 0 0                                                                                                                                                                                                  |             |             |              |             | 0      |   |  |

| TMR4 | CAPL SFR Ac | ldress = 0x0                                                                                                                                                                                                 | CA; TMR5CA  | NPL SFR Add | dress = 0x92 | 2; SFR Page | = 0x10 |   |  |

| Bit  | Name        |                                                                                                                                                                                                              |             |             | Functio      | n           |        |   |  |

| 7:0  | TMRnCAPL[7  | 7:0] Timer                                                                                                                                                                                                   | n Reload Re | egister Low | Byte.        |             |        |   |  |

|      |             | TMRnCAPL captures the low byte of Timer 4 and 5 when Timer 4 and 5 are con-<br>figured in capture mode. When Timer 4 and 5 are configured in auto-reload<br>mode, it holds the low byte of the reload value. |             |             |              |             |        |   |  |

## SFR Definition 27.21. TMRnCAPH: Timer 4 and 5 Capture Register High Byte

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|--------------|---|---|---|---|---|---|--|

| Name  |   | TMRnRLH[7:0] |   |   |   |   |   |   |  |

| Туре  |   | R/W          |   |   |   |   |   |   |  |

| Reset | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |  |

TMR4CAPH SFR Address = 0xCB; TMR5CAPH SFR Address = 0x93; SFR Page = 0x10

| Bit | Name          | Function                                                                                                                                                                                               |

|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMRnCAPH[7:0] | Timer n Reload Register High Byte.                                                                                                                                                                     |

|     |               | TMRnCAPH captures the high byte of Timer 4 and 5 when Timer 4 and 5 are configured in capture mode. When Timer 4 and 5 are configured in auto-reload mode, it holds the high byte of the reload value. |

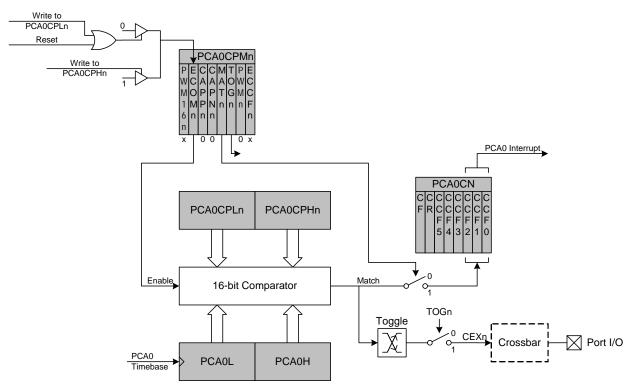

Figure 28.6. PCA0 High-Speed Output Mode Diagram

#### 28.3.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA0 clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 28.1.

$$\mathsf{F}_{\mathsf{CEXn}} = \frac{\mathsf{F}_{\mathsf{PCA}}}{2 \times \mathsf{PCA0CPHn}}$$

Note: A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

#### Equation 28.1. Square Wave Frequency Output

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2–0 bits in the PCA0 mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA0 counter low byte; on a match, CEXn is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register. Note that the MATn bit should normally be set to 0 in this mode. If the MATn bit is set to 1, the CCFn flag for the channel will be set when the 16-bit PCA0 counter and the 16-bit capture/compare register for the channel are equal.

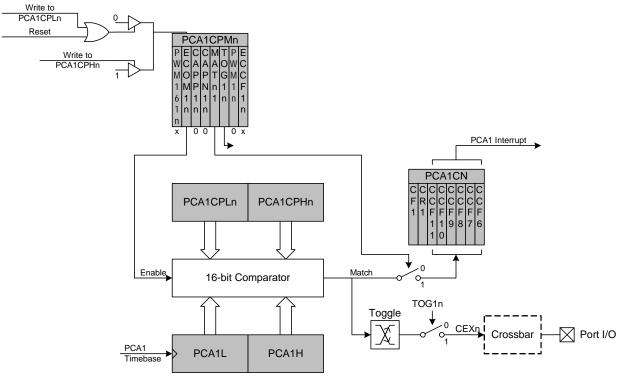

#### 29.3.3. High-Speed Output Mode

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA1 Counter and the module's 16-bit capture/compare register (PCA1CPHn and PCA1CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA1CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the TOG1n, MAT1n, and ECOM1n bits in the PCA1CPMn register enables the High-Speed Output mode. If ECOM1n is cleared, the associated pin will retain its state, and not toggle on the next match event.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA1 Capture/Compare registers, the low byte should always be written first. Writing to PCA1CPLn clears the ECOM1n bit to 0; writing to PCA1CPHn sets ECOM1n to 1.

Figure 29.6. PCA1 High-Speed Output Mode Diagram