# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | 8051                                                                      |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 50MHz                                                                     |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), CANbus, LINbus, SPI, UART/USART |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                                |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 96KB (96K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 8.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                              |

| Data Converters            | A/D 32x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 40-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 40-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f590-imr           |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 21.2. LIN0DAT: LIN0 Indirect Data Register                | 219 |

|--------------------------------------------------------------------------|-----|

| SFR Definition 21.3. LIN0CF: LIN0 Control Mode Register                  | 220 |

| SFR Definition 22.1. CAN0CFG: CAN Clock Configuration                    | 236 |

| SFR Definition 23.1. SMB0CF: SMBus Clock/Configuration                   |     |

| SFR Definition 23.2. SMB0CN: SMBus Control                               |     |

| SFR Definition 23.3. SMB0DAT: SMBus Data                                 | 247 |

| SFR Definition 24.1. SCON0: Serial Port 0 Control                        |     |

| SFR Definition 24.2. SMOD0: Serial Port 0 Control                        |     |

| SFR Definition 24.3. SBUF0: Serial (UART0) Port Data Buffer              |     |

| SFR Definition 24.4. SBCON0: UART0 Baud Rate Generator Control           | 261 |

| SFR Definition 24.6. SBRLL0: UART0 Baud Rate Generator Reload Low Byte   | 262 |

| SFR Definition 24.5. SBRLH0: UART0 Baud Rate Generator Reload High Byte  |     |

| SFR Definition 25.1. SCON1: Serial Port 1 Control                        |     |

| SFR Definition 25.2. SBUF1: Serial (UART1) Port Data Buffer              |     |

| SFR Definition 26.1. SPI0CFG: SPI0 Configuration                         |     |

| SFR Definition 26.2. SPI0CN: SPI0 Control                                |     |

| SFR Definition 26.3. SPI0CKR: SPI0 Clock Rate                            |     |

| SFR Definition 26.4. SPI0DAT: SPI0 Data                                  |     |

| SFR Definition 27.1. CKCON: Clock Control                                |     |

| SFR Definition 27.2. TCON: Timer Control                                 |     |

| SFR Definition 27.3. TMOD: Timer Mode                                    |     |

| SFR Definition 27.4. TL0: Timer 0 Low Byte                               |     |

| SFR Definition 27.5. TL1: Timer 1 Low Byte                               |     |

| SFR Definition 27.6. TH0: Timer 0 High Byte                              |     |

| SFR Definition 27.7. TH1: Timer 1 High Byte                              | 292 |

| SFR Definition 27.8. TMR2CN: Timer 2 Control                             |     |

| SFR Definition 27.9. TMR2RLL: Timer 2 Reload Register Low Byte           |     |

| SFR Definition 27.10. TMR2RLH: Timer 2 Reload Register High Byte         |     |

| SFR Definition 27.11. TMR2L: Timer 2 Low Byte                            |     |

| SFR Definition 27.12. TMR2H Timer 2 High Byte                            | 298 |

| SFR Definition 27.13. TMR3CN: Timer 3 Control                            | 302 |

| SFR Definition 27.14. TMR3RLL: Timer 3 Reload Register Low Byte          |     |

| SFR Definition 27.15. TMR3RLH: Timer 3 Reload Register High Byte         |     |

| SFR Definition 27.16. TMR3L: Timer 3 Low Byte                            |     |

| SFR Definition 27.17. TMR3H Timer 3 High Byte                            |     |

| SFR Definition 27.18. TMRnCN: Timer 4 and 5 Control                      |     |

| SFR Definition 27.19. TMRnCF: Timer 4 and 5 Configuration                |     |

| SFR Definition 27.20. TMRnCAPL: Timer 4 and 5 Capture Register Low Byte  |     |

| SFR Definition 27.21. TMRnCAPH: Timer 4 and 5 Capture Register High Byte |     |

| SFR Definition 27.22. TMRnL: Timer 4 and 5 Low Byte                      |     |

| SFR Definition 27.23. TMRnH Timer 4 and 5 High Byte                      |     |

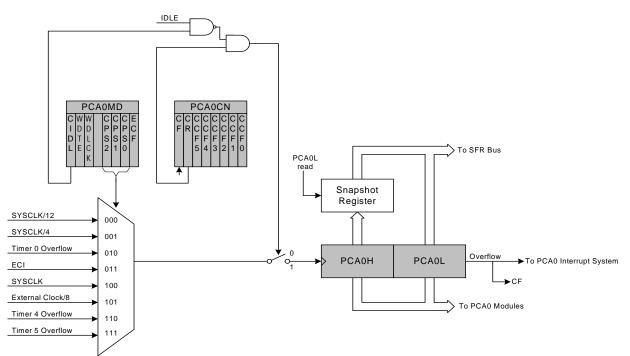

| SFR Definition 28.1. PCA0CN: PCA0 Control                                |     |

| SFR Definition 28.2. PCA0MD: PCA0 Mode                                   |     |

| SFR Definition 28.3. PCA0PWM: PCA0 PWM Configuration                     |     |

| SFR Definition 28.4. PCA0CPMn: PCA0 Capture/Compare Mode                 | 328 |

|                                                                          |     |

## 3. Pin Definitions

| Name   | Pin<br>F580/1/4/5 | Pin<br>F588/9-<br>F590/1 | Pin<br>F582/3/6/7 | Туре          | Description                                                                                                                                  |  |  |

|--------|-------------------|--------------------------|-------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        | (48-pin)          | (40-pin)                 | (32-pin)          |               |                                                                                                                                              |  |  |

| VDD    | 4                 | 4                        | 4                 |               | Digital Supply Voltage. Must be connected.                                                                                                   |  |  |

| GND    | 6                 | 6                        | 6                 |               | Digital Ground. Must be connected.                                                                                                           |  |  |

| VDDA   | 5                 | 5                        | 5                 |               | Analog Supply Voltage. Must be connected.                                                                                                    |  |  |

| GNDA   | 7                 | 7                        | 7                 |               | Analog Ground. Must be connected.                                                                                                            |  |  |

| VREGIN | 3                 | 3                        | 3                 |               | Voltage Regulator Input                                                                                                                      |  |  |

| VIO    | 2                 | 2                        | 2                 |               | Port I/O Supply Voltage. Must be connected.                                                                                                  |  |  |

| RST/   | 12                | 10                       | 10                | d I/O         | Device Reset. Open-drain output of internal POR or $V_{DD}$ Monitor. An external source can initiate a system reset by driving this pin low. |  |  |

| C2CK   |                   |                          |                   | D I/O         | Clock signal for the C2 Debug Interface.                                                                                                     |  |  |

| C2D    | 11                | _                        | _                 | D I/O         | Bi-directional data signal for the C2 Debu Interface.                                                                                        |  |  |

| P4.0/  | —                 | 9                        | _                 | D I/O or A In | Port 4.0. See SFR Definition 20.29 for a description.                                                                                        |  |  |

| C2D    |                   |                          |                   | D I/O         | Bi-directional data signal for the C2 Debug Interface.                                                                                       |  |  |

| P3.0/  | —                 |                          | 9                 | D I/O or A In | Port 3.0. See SFR Definition 20.25 for a description.                                                                                        |  |  |

| C2D    |                   |                          |                   | D I/O         | Bi-directional data signal for the C2 Debug Interface.                                                                                       |  |  |

| P0.0   | 8                 | 8                        | 8                 | D I/O or A In | Port 0.0. See SFR Definition 20.13 for a description.                                                                                        |  |  |

| P0.1   | 1                 | 1                        | 1                 | D I/O or A In | Port 0.1                                                                                                                                     |  |  |

| P0.2   | 48                | 40                       | 32                | D I/O or A In | Port 0.2                                                                                                                                     |  |  |

| P0.3   | 47                | 39                       | 31                | D I/O or A In | Port 0.3                                                                                                                                     |  |  |

| P0.4   | 46                | 38                       | 30                | D I/O or A In | Port 0.4                                                                                                                                     |  |  |

| P0.5   | 45                | 37                       | 29                | D I/O or A In | Port 0.5                                                                                                                                     |  |  |

Table 3.1. Pin Definitions for the C8051F58x/F59x

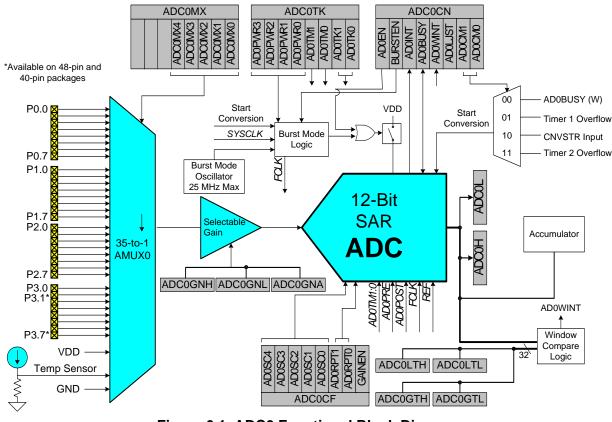

## 6. 12-Bit ADC (ADC0)

The ADC0 on the C8051F58x/F59x consists of an analog multiplexer (AMUX0) with 35/28 total input selections and a 200 ksps, 12-bit successive-approximation-register (SAR) ADC with integrated track-and-hold, programmable window detector, programmable attenuation (1:2), and hardware accumulator. The ADC0 subsystem has a special Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. The AMUX0, data conversion modes, and window detector are all configurable under software control via the Special Function Registers shows in Figure 6.1. ADC0 inputs are single-ended and may be configured to measure P0.0-P3.7, the Temperature Sensor output,  $V_{DD}$ , or GND with respect to GND. The voltage reference for ADC0 is selected as described in Section "7. Temperature Sensor" on page 74. ADC0 is enabled when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1, or when performing conversions in Burst Mode. ADC0 is in low power shutdown when AD0EN is logic 0 and no Burst Mode conversions are taking place.

Figure 6.1. ADC0 Functional Block Diagram

## SFR Definition 9.9. CPT2MX: Comparator2 MUX Selection

| Bit   | 7            | 6           | 5           | 4         | 3          | 2    | 1      | 0 |  |  |

|-------|--------------|-------------|-------------|-----------|------------|------|--------|---|--|--|

| Nam   | e            | CMX2        | N[3:0]      | I         |            | CMX2 | P[3:0] |   |  |  |

| Туре  | ;            | R/          | W           |           | R/W        |      |        |   |  |  |

| Rese  | <b>t</b> 0   | 1           | 1           | 1         | 0          | 1    | 1      | 1 |  |  |

| SFR A | ddress = 0x9 | C; SFR Page | e = 0x10    |           |            |      |        |   |  |  |

| Bit   | Name         |             |             |           | Function   |      |        |   |  |  |

| 7:4   | CMX2N[3:0]   | Comparato   | r2 Negative | Input MUX | Selection. |      |        |   |  |  |

|       |              | 0000:       | P0.         | 1         |            |      |        |   |  |  |

|       |              | 0001:       | P0.         | 3         |            |      |        |   |  |  |

|       |              | 0010:       | P0.         | 5         |            |      |        |   |  |  |

|       |              | 0011:       | P0.         | 7         |            |      |        |   |  |  |

|       |              | 0100:       | P1.         | 1         |            |      |        |   |  |  |

|       |              | 0101:       | P1.         | 3         |            |      |        |   |  |  |

|       |              | 0110:       | P1.         | 5         |            |      |        |   |  |  |

|       |              | 0111:       | P1.         | 7         |            |      |        |   |  |  |

|       |              | 1000:       | P2.         | 1         |            |      |        |   |  |  |

|       |              | 1001:       | P2.         | 3         |            |      |        |   |  |  |

|       |              | 1010:       | P2.         | 5         |            |      |        |   |  |  |

|       |              | 1011:       | P2.         | 7         |            |      |        |   |  |  |

|       |              | 1100–1111:  | Nor         | ne        |            |      |        |   |  |  |

| 3:0   | CMX2P[3:0]   | Comparato   | r2 Positive | Input MUX | Selection. |      |        |   |  |  |

|       |              | 0000:       | P0.         | 0         |            |      |        |   |  |  |

|       |              | 0001:       | P0.         | 2         |            |      |        |   |  |  |

|       |              | 0010:       | P0.         | 4         |            |      |        |   |  |  |

|       |              | 0011:       | P0.         | 6         |            |      |        |   |  |  |

|       |              | 0100:       | P1.         | 0         |            |      |        |   |  |  |

|       |              | 0101:       | P1.         | 2         |            |      |        |   |  |  |

|       |              | 0110:       | P1.         | 4         |            |      |        |   |  |  |

|       |              | 0111:       | P1.         | 6         |            |      |        |   |  |  |

|       |              | 1000:       | P2.         | 0         |            |      |        |   |  |  |

|       |              | 1001:       | P2.         | 2         |            |      |        |   |  |  |

|       |              | 1010:       | P2.         | 4         |            |      |        |   |  |  |

|       |              | 1011:       | P2.         | 6         |            |      |        |   |  |  |

|       |              | 1100–1111:  | Nor         | ne        |            |      |        |   |  |  |

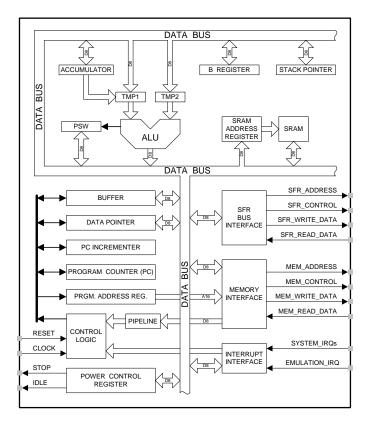

Figure 11.1. CIP-51 Block Diagram

With the CIP-51's maximum system clock at 50 MHz, it has a peak throughput of 50 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

#### **Programming and Debugging Support**

In-system programming of the Flash program memory and communication with on-chip debug support logic is accomplished via the Silicon Labs 2-Wire Development Interface (C2).

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive, requiring no RAM, Stack, timers, or other on-chip resources. C2 details can be found in "C2 Interface" on page 351.

The CIP-51 is supported by development tools from Silicon Labs and third party vendors. Silicon Labs provides an integrated development environment (IDE) including editor, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via the C2 interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

## SFR Definition 11.3. SP: Stack Pointer

| Name     SP[7:0]       Type     R/W                               |                 |  |         | 7:0] | SDI. | • |  |  |  |  |  |  |  |

|-------------------------------------------------------------------|-----------------|--|---------|------|------|---|--|--|--|--|--|--|--|

| Type R/W                                                          |                 |  | SP[7:0] |      |      |   |  |  |  |  |  |  |  |

|                                                                   | R/W             |  |         |      |      |   |  |  |  |  |  |  |  |

| Reset         0         0         0         0         1         1 | 0 0 0 0 0 1 1 1 |  |         |      |      |   |  |  |  |  |  |  |  |

| Bit | Name    | Function                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

#### SFR Definition 11.4. ACC: Accumulator

| Bit    | 7           | 7 6 5 4 3 2 1 0 |               |              |       |  |  |  |  |  |  |  |  |

|--------|-------------|-----------------|---------------|--------------|-------|--|--|--|--|--|--|--|--|

| Name   |             | ACC[7:0]        |               |              |       |  |  |  |  |  |  |  |  |

| Туре   |             | R/W             |               |              |       |  |  |  |  |  |  |  |  |

| Reset  | 0           | 0 0 0 0 0 0 0 0 |               |              |       |  |  |  |  |  |  |  |  |

| SFR Ad | dress = 0xE | 0; SFR Page     | e = All Pages | ; Bit-Addres | sable |  |  |  |  |  |  |  |  |

| -      |             |                 |               |              |       |  |  |  |  |  |  |  |  |

| Bit | Name     | Function                                                    |

|-----|----------|-------------------------------------------------------------|

| 7:0 | ACC[7:0] | Accumulator.                                                |

|     |          | This register is the accumulator for arithmetic operations. |

#### SFR Definition 11.5. B: B Register

| Bit   | 7               | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |  |

|-------|-----------------|-----------------|--|--|--|--|--|--|--|--|--|--|

| Name  |                 | B[7:0]          |  |  |  |  |  |  |  |  |  |  |

| Туре  |                 | R/W             |  |  |  |  |  |  |  |  |  |  |

| Reset | 0 0 0 0 0 0 0 0 |                 |  |  |  |  |  |  |  |  |  |  |

SFR Address = 0xF0; SFR Page = All Pages; Bit-Addressable

| Bit | Name   | Function                                                                        |

|-----|--------|---------------------------------------------------------------------------------|

| 7:0 | B[7:0] | B Register.                                                                     |

|     |        | This register serves as a second accumulator for certain arithmetic operations. |

## SFR Definition 13.2. SFRPAGE: SFR Page

| Bit   | 7 | 7 6 5 4 3 2 1 0 |   |   |   |   |   |   |  |  |  |  |

|-------|---|-----------------|---|---|---|---|---|---|--|--|--|--|

| Name  |   | SFRPAGE[7:0]    |   |   |   |   |   |   |  |  |  |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |  |  |  |

| Reset | 0 | 0               | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |  |

#### SFR Address = 0xA7; SFR Page = All Pages

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SFRPAGE[7:0] | SFR Page Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |              | Represents the SFR Page the C8051 core uses when reading or modifying SFRs.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |              | Write: Sets the SFR Page.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |              | Read: Byte is the SFR page the C8051 core is using.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |              | When enabled in the SFR Page Control Register (SFR0CN), the C8051 core will automatically switch to the SFR Page that contains the SFRs of the corresponding peripheral/function that caused the interrupt, and return to the previous SFR page upon return from interrupt (unless SFR Stack was altered before a returning from the interrupt). SFRPAGE is the top byte of the SFR Page Stack, and push/pop events of this stack are caused by interrupts (and not by reading/writing to the SFRPAGE register) |

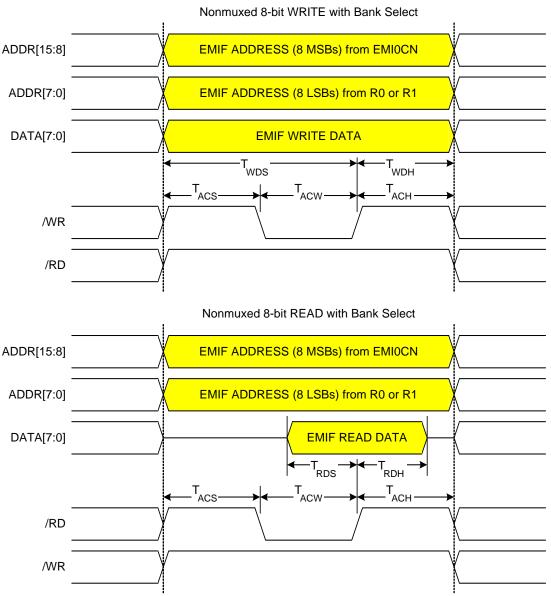

#### 18.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110

Figure 18.6. Non-multiplexed 8-bit MOVX with Bank Select Timing

### **19. Oscillators and Clock Selection**

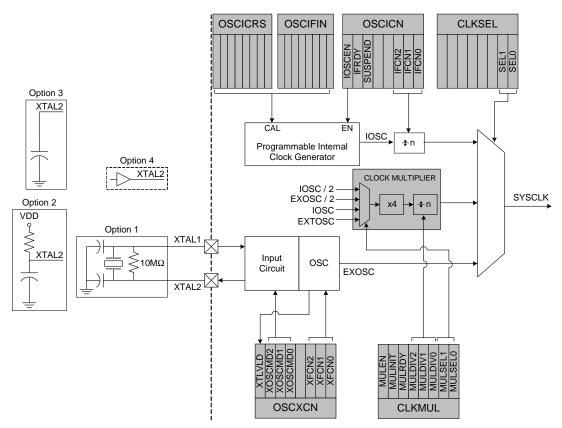

C8051F58x/F59x devices include a programmable internal high-frequency oscillator, an external oscillator drive circuit, and a clock multiplier. The internal oscillator can be enabled/disabled and calibrated using the OSCICN, OSCICRS, and OSCIFIN registers, as shown in Figure 19.1. The system clock can be sourced by the external oscillator circuit or the internal oscillator. The clock multiplier can produce three possible base outputs which can be scaled by a programmable factor of 1, 2/3, 2/4 (or 1/2), 2/5, 2/6 (or 1/3), or 2/7: Internal Oscillator x 2, External Oscillator x 2, or External Oscillator x 4.

Figure 19.1. Oscillator Options

#### 19.1. System Clock Selection

The CLKSL[1:0] bits in register CLKSEL select which oscillator source is used as the system clock. CLKSL[1:0] must be set to 01b for the system clock to run from the external oscillator; however the external oscillator may still clock certain peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal oscillator, external oscillator, and Clock Multiplier so long as the selected clock source is enabled and has settled.

The internal oscillator requires little start-up time and may be selected as the system clock immediately following the register write which enables the oscillator. The external RC and C modes also typically require no startup time.

External crystals and ceramic resonators however, typically require a start-up time before they are settled and ready for use. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to 1 by hardware when the external crystal or ceramic resonator is settled. In crystal mode, to avoid reading a false XTLVLD, software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD.

#### LIN Register Definition 21.11. LIN0ID: LIN0 Identifier Register

| Bit   | 7 | 6 | 5           | 4 | 3  | 2 | 1 | 0 |

|-------|---|---|-------------|---|----|---|---|---|

| Name  |   |   | ID[5:0]     |   |    |   |   |   |

| Туре  | R | R |             |   | R/ | W |   |   |

| Reset | 0 | 0 | 0 0 0 0 0 0 |   |    |   |   |   |

Indirect Address = 0x0E

| Bit | Name    | Function                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused  | Read = 00b; Write = Don't Care.                                                                                                                                                             |

| 5:0 | ID[5:0] | LIN Identifier Bits.                                                                                                                                                                        |

|     |         | These bits form the data identifier.                                                                                                                                                        |

|     |         | If the LINSIZE bits (LINOSIZE[3:0]) are 1111b, bits ID[5:4] are used to determine the data size and are interpreted as follows:<br>00: 2 bytes<br>01: 2 bytes<br>10: 4 bytes<br>11: 8 bytes |

#### SFR Definition 23.2. SMB0CN: SMBus Control

| Bit   | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0   |

|-------|--------|--------|-----|-----|-------|---------|-----|-----|

| Name  | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI  |

| Туре  | R      | R      | R/W | R/W | R     | R       | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0   |

#### SFR Address = 0xC0; Bit-Addressable; SFR Page =0x00

| Bit | Name    | Description                                                                                                                                                                                                      | Read                                                                                                                       | Write                                                                                                                                                                                |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | SMBus Master/Slave<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a master.                                                                                                     | 0: SMBus operating in<br>slave mode.<br>1: SMBus operating in<br>master mode.                                              | N/A                                                                                                                                                                                  |

| 6   | TXMODE  | SMBus Transmit Mode<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a transmitter.                                                                                               | 0: SMBus in Receiver<br>Mode.<br>1: SMBus in Transmitter<br>Mode.                                                          | N/A                                                                                                                                                                                  |

| 5   | STA     | SMBus Start Flag.                                                                                                                                                                                                | 0: No Start or repeated<br>Start detected.<br>1: Start or repeated Start<br>detected.                                      | 0: No Start generated.<br>1: When Configured as a<br>Master, initiates a START<br>or repeated START.                                                                                 |

| 4   | STO     | SMBus Stop Flag.                                                                                                                                                                                                 | 0: No Stop condition<br>detected.<br>1: Stop condition detected<br>(if in Slave Mode) or pend-<br>ing (if in Master Mode). | 0: No STOP condition is<br>transmitted.<br>1: When configured as a<br>Master, causes a STOP<br>condition to be transmit-<br>ted after the next ACK<br>cycle.<br>Cleared by Hardware. |

| 3   | ACKRQ   | SMBus Acknowledge<br>Request.                                                                                                                                                                                    | 0: No Ack requested<br>1: ACK requested                                                                                    | N/A                                                                                                                                                                                  |

| 2   | ARBLOST | SMBus Arbitration Lost<br>Indicator.                                                                                                                                                                             | 0: No arbitration error.<br>1: Arbitration Lost                                                                            | N/A                                                                                                                                                                                  |

| 1   | ACK     | SMBus Acknowledge.                                                                                                                                                                                               | 0: NACK received.<br>1: ACK received.                                                                                      | 0: Send NACK<br>1: Send ACK                                                                                                                                                          |

| 0   | SI      | <b>SMBus Interrupt Flag.</b><br>This bit is set by hardware<br>under the conditions listed in<br>Table 15.3. SI must be cleared<br>by software. While SI is set,<br>SCL is held low and the<br>SMBus is stalled. | 0: No interrupt pending<br>1: Interrupt Pending                                                                            | <ul><li>0: Clear interrupt, and initiate next state machine event.</li><li>1: Force interrupt.</li></ul>                                                                             |

### SFR Definition 24.2. SMOD0: Serial Port 0 Control

| Bit                    | 7           | 6                                                                                                                           | 5             | 4               | 3            | 2               | 1                | 0            |

|------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|--------------|-----------------|------------------|--------------|

| Nam                    | e MCE0      | SOP                                                                                                                         | [1:0]         | PE0             | SOD          | L[1:0]          | XBE0             | SBL0         |

| Туре                   | e R/W       | R/W                                                                                                                         | R             | R/W             | R/W          | R/W             | R/W              | R/W          |

| <b>Reset</b> 0 0 0 0 1 |             |                                                                                                                             |               | 1               | 1            | 0               | 0                |              |

| SFR A                  | Address = 0 | xA9; SFR Page                                                                                                               | e = 0x00      |                 |              |                 |                  |              |

| Bit                    | Name        |                                                                                                                             |               |                 | Function     |                 |                  |              |

| 7                      | MCE0        | Multiprocess<br>0: RI0 will be a<br>1: RI0 will be a<br>XBE0.                                                               | activated if  | stop bit(s) are | e 1.         | re 1. Extra bit | must be ena      | abled using  |

| 6:5                    | S0PT[1:0]   | Parity Type S                                                                                                               | elect Bits.   |                 |              |                 |                  |              |

|                        |             | 00: Odd Parity<br>01: Even Parit                                                                                            |               |                 |              |                 |                  |              |

|                        |             | 10: Mark Parit                                                                                                              | y<br>y        |                 |              |                 |                  |              |

|                        |             | 11: Space Par                                                                                                               | •             |                 |              |                 |                  |              |

| 4                      | PE0         | Parity Enable                                                                                                               |               |                 |              |                 |                  |              |

|                        |             | This bit enable<br>by bits S0PT[                                                                                            |               |                 |              | hecking. The    | parity type is   | s selected   |

|                        |             | 0: Hardware p                                                                                                               |               | •               |              |                 |                  |              |

|                        |             | 1: Hardware p                                                                                                               | arity is enal | bled.           |              |                 |                  |              |

| 3:2                    | S0DL[1:0]   | -                                                                                                                           |               |                 |              |                 |                  |              |

|                        |             | 00: 5-bit data                                                                                                              |               |                 |              |                 |                  |              |

|                        |             | 01: 6-bit data<br>10: 7-bit data                                                                                            |               |                 |              |                 |                  |              |

|                        |             | 11: 8-bit data                                                                                                              |               |                 |              |                 |                  |              |

| 1                      | XBE0        | Extra Bit Ena                                                                                                               | ble.          |                 |              |                 |                  |              |

|                        |             | When enabled, the value of TBX0 will be appended to the data field<br>0: Extra Bit is disabled.<br>1: Extra Bit is enabled. |               |                 |              |                 |                  |              |

| 0                      | SBL0        | Stop Bit Leng                                                                                                               |               |                 |              |                 |                  |              |

|                        |             | 0: Short—stop                                                                                                               |               |                 |              |                 |                  |              |

|                        |             | 1: Long—stop<br>(data length =                                                                                              |               | for two bit tir | nes (data le | ngth = 6, 7, c  | or 8 bits), or 1 | .5 bit times |

#### SFR Definition 24.3. SBUF0: Serial (UART0) Port Data Buffer

| Bit   | 7 | 6               | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|----|---|---|---|---|--|

| Name  |   | SBUF0[7:0]      |   |    |   |   |   |   |  |

| Туре  |   |                 |   | R/ | W |   |   |   |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |    |   |   |   |   |  |

SFR Address = 0x99; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                    |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SBUF0[7:0] | Serial Data Buffer Bits 7–0 (MSB–LSB).                                                                                                                                                                                                                                                                                      |

|     |            | This SFR accesses two registers; a transmit shift register and a receive latch register.<br>When data is written to SBUF0, it goes to the transmit shift register and is held for<br>serial transmission. Writing a byte to SBUF0 initiates the transmission. A read of<br>SBUF0 returns the contents of the receive latch. |

#### SFR Definition 24.4. SBCON0: UART0 Baud Rate Generator Control

| Bit   | 7        | 6      | 5        | 4        | 3        | 2        | 1    | 0      |

|-------|----------|--------|----------|----------|----------|----------|------|--------|

| Name  | Reserved | SB0RUN | Reserved | Reserved | Reserved | Reserved | SB0P | S[1:0] |

| Туре  | R/W      | R/W    | R/W      | R/W      | R/W      | R/W      | R/   | W      |

| Reset | 0        | 0      | 0        | 0        | 0        | 0        | 0    | 0      |

SFR Address = 0xAB; SFR Page = 0x0F

| Bit | Name       | Function                                                                                                            |

|-----|------------|---------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved   | Read = 0b; Must Write 0b;                                                                                           |

| 6   | SB0RUN     | Baud Rate Generator Enable.                                                                                         |

|     |            | <ul><li>0: Baud Rate Generator disabled. UART0 will not function.</li><li>1: Baud Rate Generator enabled.</li></ul> |

| 5:2 | Reserved   | Read = 0000b; Must Write = 0000b;                                                                                   |

| 1:0 | SB0PS[1:0] | Baud Rate Prescaler Select.                                                                                         |

|     |            | 00: Prescaler = 12.                                                                                                 |

|     |            | 01: Prescaler = 4.                                                                                                  |

|     |            | 10: Prescaler = 48.                                                                                                 |

|     |            | 11: Prescaler = 1.                                                                                                  |

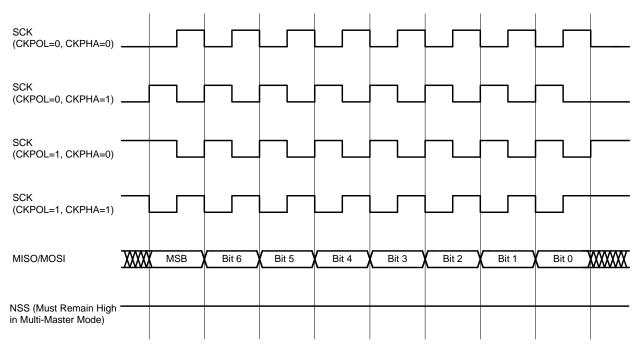

#### 26.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 26.5. For slave mode, the clock and data relationships are shown in Figure 26.6 and Figure 26.7. CKPHA must be set to 0 on both the master and slave SPI when communicating between two of the following devices: C8051F04x, C8051F06x, C8051F12x, C8051F31x, C8051F32x, and C8051F33x.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 26.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

Figure 26.5. Master Mode Data/Clock Timing

### SFR Definition 26.2. SPI0CN: SPI0 Control

| Bit   | 7                                                                 | 6                                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4                           | 3                             | 2                            | 1                                                      | 0              |

|-------|-------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------|------------------------------|--------------------------------------------------------|----------------|

| Name  | SPIF                                                              | WCOL                                                | MODF                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RXOVRN                      | NSSM                          | NSSMD[1:0] TXBMT S           |                                                        | SPIEN          |

| Туре  | R/W                                                               | R/W                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W                         | R/W R R/V                     |                              |                                                        |                |

| Reset | Reset         0         0         0         0         1         1 |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |                               |                              | 0                                                      |                |

| SFR A | ddress = 0xF8                                                     | ; Bit-Addres                                        | sable; SFR                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page = 0x00                 | )                             |                              |                                                        | 11             |

| Bit   | Name                                                              |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             | Function                      | 1                            |                                                        |                |

| 7     | SPIF                                                              | This bit is enabled, s                              | setting this b                                                                                                                                                                                                                                                                                                                                                                                                                                               | it causes the               | e CPU to ve                   | ctor to the S                | transfer. If int<br>SPI0 interrupt<br>must be clear    | service rou-   |

| 6     | WCOL                                                              | This bit is write to the                            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 by hardwa<br>register was | · •                           |                              | PIO interrupt) t<br>transfer was                       |                |

| 5     | MODF                                                              | ter mode of                                         | set to logic collision is d                                                                                                                                                                                                                                                                                                                                                                                                                                  | etected (NS                 | S is low, MS                  | STEN = 1, a                  | PIO interrupt) v<br>nd NSSMD[1<br>be cleared by        | :0] = 01).     |

| 4     | RXOVRN                                                            | Receive C                                           | Overrun Fla                                                                                                                                                                                                                                                                                                                                                                                                                                                  | g (valid in s               | lave mode                     | only).                       |                                                        |                |

|       |                                                                   | receive bu<br>current tra                           | iffer still hold                                                                                                                                                                                                                                                                                                                                                                                                                                             | ds unread da                | ta from a pr<br>SPI0 shift re | evious trans<br>gister. This | Pl0 interrupt) v<br>sfer and the la<br>bit is not auto | ast bit of the |

| 3:2   | NSSMD[1:0]                                                        | Slave Sel                                           | ect Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                             |                               |                              |                                                        |                |

|       | -                                                                 | (See Sect<br>00: 3-Wire<br>01: 4-Wire<br>1x: 4-Wire | <ul> <li>Slave Select Mode.</li> <li>Selects between the following NSS operation modes:<br/>(See Section 26.2 and Section 26.3).</li> <li>00: 3-Wire Slave or 3-Wire Master Mode. NSS signal is not routed to a port pin.</li> <li>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is an input to the device.</li> <li>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the device and will assume the value of NSSMD0.</li> </ul> |                             |                               |                              |                                                        |                |

| 1     | TXBMT                                                             | Transmit                                            | Buffer Emp                                                                                                                                                                                                                                                                                                                                                                                                                                                   | oty.                        |                               |                              |                                                        |                |

|       |                                                                   | When data                                           | This bit will be set to logic 0 when new data has been written to the transmit buffer.<br>When data in the transmit buffer is transferred to the SPI shift register, this bit will<br>be set to logic 1, indicating that it is safe to write a new byte to the transmit buffer.                                                                                                                                                                              |                             |                               |                              |                                                        |                |

| 0     | SPIEN                                                             | SPI0 Enal<br>0: SPI disa<br>1: SPI ena              | abled.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |                               |                              |                                                        |                |

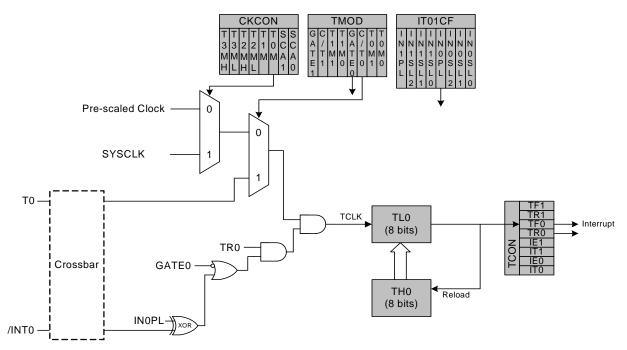

### 27. Timers

Each MCU includes six counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and the other four are 16-bit auto-reload timers for use with the ADC, SMBus, or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 and Timer 3 offer 16-bit and split 8-bit timer functionality with auto-reload. Timer 4 and Timer 5 have 16-bit auto reload and capture and can also produce a 50% duty-cycle square wave (toggle output) at an general purpose port pin.

| Timer 0 and Timer 1 Modes               | Timer 2 and 3 Modes               | Timer 4 and 5 Modes               |

|-----------------------------------------|-----------------------------------|-----------------------------------|

| 13-bit counter/timer                    | 16-bit timer with auto-reload     | 16-bit timer with auto-reload     |

| 16-bit counter/timer                    |                                   |                                   |

| 8-bit counter/timer with auto-reload    | Two 8-bit timers with auto-reload | 16-bit counter/timer with capture |

| Two 8-bit counter/timers (Timer 0 only) |                                   | Toggle Output                     |

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M– T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked (See SFR Definition 27.1 for pre-scaled clock selection).Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock.

Timer 2 and Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 4 and Timer 5 may be clocked by the system clock, system clock divided by 2 or 12, or the external oscillator clock source divided by 8.

Timers 0, 1, 4, and 5 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin. Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it should be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

#### 27.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and/or UART, and/or initiate ADC conversions. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

### SFR Definition 27.3. TMOD: Timer Mode

| Bit                                                                                                                                                                                                        | 7                                                                    | 6                                                                                    | 5           | 4     | 3            | 2            | 1            | 0            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------|-------|--------------|--------------|--------------|--------------|

| Name                                                                                                                                                                                                       | GATE1                                                                | C/T1                                                                                 | T1M         | [1:0] | GATE0        | C/T0         | T0M[1:0]     |              |

| Туре                                                                                                                                                                                                       | R/W                                                                  | R/W                                                                                  | R/W         |       | R/W          | R/W          | R/W          |              |

| Rese                                                                                                                                                                                                       | Reset 0 0 0 0 0 0 0                                                  |                                                                                      | 0           | 0     |              |              |              |              |

| SFR A                                                                                                                                                                                                      | ddress = 0x8                                                         | 9; SFR Page                                                                          | = All Pages |       |              |              |              |              |

| Bit                                                                                                                                                                                                        |                                                                      |                                                                                      |             |       |              |              |              |              |

| 7                                                                                                                                                                                                          | GATE1                                                                | Timer 1 Gate Control.                                                                |             |       |              |              |              |              |

|                                                                                                                                                                                                            |                                                                      |                                                                                      |             |       | espective of |              |              |              |

|                                                                                                                                                                                                            |                                                                      |                                                                                      |             |       | 1 AND INT1   | is active as | defined by I | oit IN1PL in |

|                                                                                                                                                                                                            |                                                                      | register IT01CF (see SFR Definition 14.7).                                           |             |       |              |              |              |              |

| 6                                                                                                                                                                                                          | C/T1                                                                 | Counter/Timer 1 Select.                                                              |             |       |              |              |              |              |

| 0: Timer: Timer 1 incremented by clock defined by T1M bit in register                                                                                                                                      |                                                                      |                                                                                      |             |       | -            |              |              |              |

|                                                                                                                                                                                                            | <b>T</b> (1) (1) (1)                                                 | 1: Counter: Timer 1 incremented by high-to-low transitions on external pin (T1).     |             |       |              |              |              |              |

| 5:4                                                                                                                                                                                                        | 5:4 T1M[1:0] Timer 1 Mode Select.                                    |                                                                                      |             |       |              |              |              |              |

| These bits select the Timer 1 operation mode.                                                                                                                                                              |                                                                      |                                                                                      |             |       |              |              |              |              |

|                                                                                                                                                                                                            | 00: Mode 0, 13-bit Counter/Timer<br>01: Mode 1, 16-bit Counter/Timer |                                                                                      |             |       |              |              |              |              |

|                                                                                                                                                                                                            |                                                                      | 10: Mode 2, 8-bit Counter/Timer with Auto-Reload                                     |             |       |              |              |              |              |

|                                                                                                                                                                                                            | 11: Mode 3, Timer 1 Inactive                                         |                                                                                      |             |       |              |              |              |              |

| 3                                                                                                                                                                                                          | 3 GATE0 Timer 0 Gate Control.                                        |                                                                                      |             |       |              |              |              |              |

| 0: Timer 0 enabled when TR0 = 1 irrespective of $\overline{INT0}$ logic level<br>1: Timer 0 enabled only when TR0 = 1 AND $\overline{INT0}$ is active as def<br>register IT01CF (see SFR Definition 14.7). |                                                                      |                                                                                      |             |       |              |              |              |              |

|                                                                                                                                                                                                            |                                                                      |                                                                                      |             |       | defined by I | oit IN0PL in |              |              |

| -                                                                                                                                                                                                          | C/T0                                                                 | Counter/Timer 0 Select.                                                              |             |       |              |              |              |              |

| 2                                                                                                                                                                                                          | C/10                                                                 |                                                                                      |             |       |              |              |              |              |

| 0: Timer: Timer 0 incremented by clock defined by T0M bit in register<br>1: Counter: Timer 0 incremented by high-to-low transitions on extern                                                              |                                                                      |                                                                                      |             |       | -            |              |              |              |

| 1:0                                                                                                                                                                                                        | T0M[1:0]                                                             | Timer 0 Mode Select.                                                                 |             |       |              |              |              |              |

|                                                                                                                                                                                                            |                                                                      | These bits select the Timer 0 operation mode.                                        |             |       |              |              |              |              |

|                                                                                                                                                                                                            |                                                                      | 00: Mode 0, 13-bit Counter/Timer                                                     |             |       |              |              |              |              |