THE MUNICIPALITY OF THE PARTY O

Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application charific microcontrollars are analyzared to

#### Details

| Product Status          | Active                                                                      |

|-------------------------|-----------------------------------------------------------------------------|

| Applications            | USB 3.0 Hub Controller                                                      |

| Core Processor          | ARM® Cortex®-M0                                                             |

| Program Memory Type     | ROM (32kB)                                                                  |

| Controller Series       | CYUSB                                                                       |

| RAM Size                | 16K x 8                                                                     |

| Interface               | I <sup>2</sup> C                                                            |

| Number of I/O           | 10                                                                          |

| Voltage - Supply        | 1.14V ~ 1.26V, 2.5V ~ 2.7V, 3V ~ 3.6V                                       |

| Operating Temperature   | 0°C ~ 70°C                                                                  |

| Mounting Type           | Surface Mount                                                               |

| Package / Case          | 88-VFQFN Exposed Pad                                                        |

| Supplier Device Package | 88-QFN (10x10)                                                              |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cyusb3314-88ltxc |

|                         |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

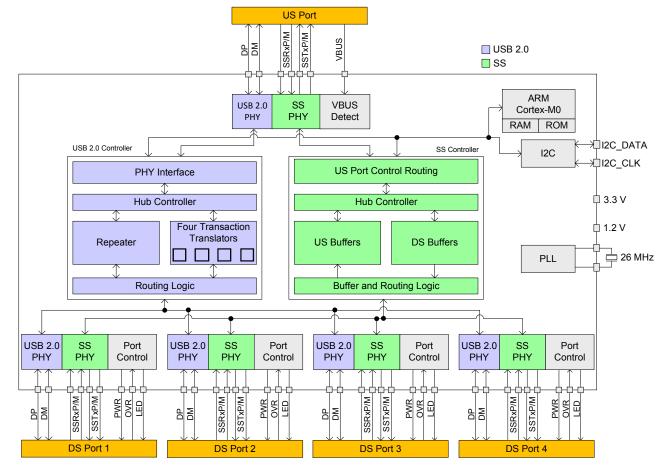

## **Block Diagram**

## **Architecture Overview**

The Block Diagram on page 2 shows the HX3 architecture. HX3 consists of two independent hub controllers (SS and USB 2.0), the Cortex-M0 CPU subsystem, an  $I^2C$  interface, and port controller blocks.

### SS Hub Controller

This block supports the SS hub functionality based on the USB 3.0 specification. The SS hub controller supports the following:

- SS link power management (U0, U1, U2, U3 states)

- Full-duplex data transmission

#### **USB 2.0 Hub Controller**

This block supports the LS, FS, and HS hub functionalities. It includes the repeater, frame timer, and four transaction translators.

The USB 2.0 hub controller block supports the following:

- USB 2.0 link power management (L0, L1, L2, L3 states)

- Suspend, resume, and remote wake-up signaling

- Multi-TT (one TT for each DS port)

### CPU

The ARM Cortex-M0 CPU subsystem is used for the following functions:

- System configuration and initialization

- Battery charging control

- Vendor-specific commands for the USB-to-I<sup>2</sup>C bridge

- String-descriptor support

- Suspend status indicator

- Shared Link support in embedded systems

## I<sup>2</sup>C Interface

The I<sup>2</sup>C interface in HX3 supports the following:

- I<sup>2</sup>C Slave, Master, and Multi-master configurations

- $\square$  Configure HX3 by an external I<sup>2</sup>C master in I<sup>2</sup>C slave mode  $\square$  Configure HX3 from an I<sup>2</sup>C EEPROM

- Multi-master mode to share EEPROM with other I<sup>2</sup>C masters

- In-System Programming of the I<sup>2</sup>C EEPROM from HX3's US port

### **Port Controller**

The port controller block controls DS port power to comply with the BC v1.2 and USB 3.0 specifications. This block also controls the US port power in the ACA-Dock mode. Control signals for external power switches are implemented within the chip. HX3 controls the external power switches at power-on to reduce in-rush current.

The port controller block supports the following:

- Overcurrent detection

- SS and USB 2.0 port indicators for each DS port

- Ganged and individual power control modes

- Automatic port numbering based on active ports

## Applications

- Standalone hubs

- PC and tablet motherboards

- Docking station

- Hand-held cradles

- Monitors

- Digital TVs

- Set-top boxes

- Printers

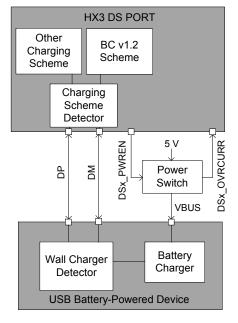

When the US port is disconnected from the host, HX3 detects if any of the DS ports are connected to a device requesting charging. It determines the charging method and then switches to the appropriate signaling based on the detected charging specification as shown in Figure 4. The hub either emulates a USB-compliant dedicated charging port by connecting DP and DM (see the BC v1.2 specification) or other supported proprietary charging schemes.

#### Figure 4. Ghost Charge Implementation in HX3

Ghost Charge is enabled by default and can be disabled through configuration. Refer to Configuration Options on page 24.

### Vendor-Command Support

HX3 supports vendor-specific requests and can also enumerate as a vendor-specific device. The vendor-specific request can be used to (a) bridge USB and  $I^2C$  and (b) configure HX3. This feature can be used for the following applications:

- Firmware upgrade of an external ASSP connected to HX3 through USB

- In-System programming (ISP) of an EEPROM connected to HX3 through USB

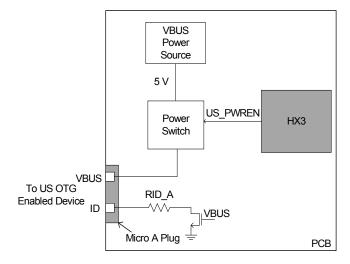

### **ACA-Dock Support**

In traditional USB topologies, the host provides VBUS to enable and charge the connected devices. For OTG hosts, however, an ACA-Dock provides VBUS and a method to charge the host. HX3 supports the ACA-Dock standard (see BC v1.2 specification) by integrating the functions of the adapter controller.

Figure 5 shows the ACA-Dock system. If the ACA-Dock feature is enabled, HX3 turns on the external power switch to drive VBUS on the US port. To inform the OTG host that it is connected to an ACA-Dock, the ID pin is tied to ground using a resistor RID\_A,<sup>3</sup> as shown in Figure 5. The ACA-Dock feature can be disabled using the Configuration Options on page 24.

For example, a BC v1.2 compliant phone such as a Sony Xperia (neo V) can be docked to a HX3-based ACA-Dock system. The phone acts as an OTG host and the ACA-Dock charges the phone connected to the US port while also powering the four DS ports.

#### Figure 5. ACA-Dock Support

#### Note

3. 124 k $\Omega$  is the recommended RID\_A value as per BC v1.2 specification, but some portable devices use custom RID\_A values.

| A1     | A2            | A3            | A4              | A5              | A6          | A7      | A8       | A9         | A10     |

|--------|---------------|---------------|-----------------|-----------------|-------------|---------|----------|------------|---------|

| NC     | NC            | NC            | AVDD33          | DS2_DM          | DS2_DP      | AVDD33  | US_DM    | US_DP      | AVDD12  |

| B1     | B2            | B3            | B4              | B5              | B6          | B7      | B8       | B9         | B10     |

| NC     | NC            | NC            | VDD_IO          | VSS             | AVDD33      | NC      | NC       | NC         | DVDD12  |

| C1     | C2            | C3            | C4              | C5              | C6          | C7      | C8       | C9         | C10     |

| US_TXM | NC            | NC            | NC              | NC              | VSS         | DS1_DP  | DS1_DM   | AVDD12     | DS1_RXM |

| D1     | D2            | D3            | D4              | D5              | D6          | D7      | D8       | D9         | D10     |

| US_TXP | NC            | NC            | DVDD12          | VSS             | DVDD12      | VSS     | DVDD12   | VSS        | DS1_RXP |

| E1     | E2            | E3            | E4              | E5              | E6          | E7      | E8       | E9         | E10     |

| DVDD12 | RREF_US<br>B2 | NC            | NC              | XTL_IN          | XTL_OUT     | VDD_IO  | DS1_TXM  | VSS        | DVDD12  |

| F1     | F2            | F3            | F4              | F5              | F6          | F7      | F8       | F9         | F10     |

| US_RXM | VSS           | AVDD33        | MODE_SE<br>L[1] | DVDD12          | OVRCUR<br>R | RESETN  | DS1_TXP  | AVDD12     | DS2_RXP |

| G1     | G2            | G3            | G4              | G5              | G6          | G7      | G8       | G9         | G10     |

| US_RXP | VBUS_DS       | SUSPEND       | RESERVE<br>D1   | MODE_SE<br>L[0] | VDD_IO      | PWR_EN  | I2C_DATA | VSS        | DS2_RXM |

| H1     | H2            | H3            | H4              | H5              | H6          | H7      | H8       | H9         | H10     |

| AVDD12 | VBUS_US       | VDD_EFU<br>SE | RESERVE<br>D2   | RREF_SS         | VSS         | DS2_TXM | DS2_TXP  | NC         | AVDD12  |

| J1     | J2            | J3            | J4              | J5              | J6          | J7      | J8       | <b>J</b> 9 | J10     |

| VSS    | AVDD12        | VSS           | GPIO            | NC              | I2C_CLK     | NC      | NC       | VSS        | NC      |

| K1     | K2            | K3            | K4              | K5              | K6          | K7      | K8       | K9         | K10     |

| NC     | NC            | DVDD12        | NC              | NC              | NC          | NC      | NC       | DVDD12     | NC      |

### Figure 8. HX3 100-Ball BGA Pinout for CYUSB3302

| Pin I | Name      |          |             |        |                            |

|-------|-----------|----------|-------------|--------|----------------------------|

|       | CYUSB3304 | Туре     | 68-QFN Pin# | Ball # | Description                |

|       |           |          |             | US P   | ort                        |

| US    | US RXP    |          | 9           | G1     | SuperSpeed receive plus    |

| US    | RXM       | I        | 8           | F1     | SuperSpeed receive minus   |

| US    | TXP       | 0        | 6           | D1     | SuperSpeed transmit plus   |

| US    | TXM       | 0        | 5           | C1     | SuperSpeed transmit minus  |

| US    | _DP       | I/O      | 57          | A9     | USB 2.0 data plus          |

| US    | _DM       | I/O      | 58          | A8     | USB 2.0 data minus         |

|       |           |          |             | DS1 F  | Port                       |

| DS1   | RXP       | I        | 51          | D10    | SuperSpeed receive plus    |

| DS1   | RXM       | I        | 50          | C10    | SuperSpeed receive minus   |

| DS1   | _TXP      | 0        | 47          | F8     | SuperSpeed transmit plus   |

| DS1   | TXM       | 0        | 48          | E8     | SuperSpeed transmit minus  |

| DS1   | 1_DP      | I/O      | 60          | C7     | USB 2.0 data plus          |

| DS1   | _DM       | I/O      | 59          | C8     | USB 2.0 data minus         |

|       |           |          |             | DS2 P  | ort                        |

| DS2   | _RXP      | I        | 45          | F10    | SuperSpeed receive plus    |

| DS2   | RXM       | I        | 44          | G10    | SuperSpeed receive minus   |

| DS2   | _TXP      | 0        | 41          | H8     | SuperSpeed transmit plus   |

| DS2   | _TXM      | 0        | 42          | H7     | SuperSpeed transmit minus  |

| DS2   | 2_DP      | I/O      | 62          | A6     | USB 2.0 data plus          |

| DS2   | 2_DM      | I/O      | 63          | A5     | USB 2.0 data minus         |

|       | _         |          |             | DS3 P  | ort                        |

| NC    | DS3_RXP   | I        | 35          | K10    | SuperSpeed receive plus    |

| NC    | DS3_RXM   | I        | 36          | J10    | SuperSpeed receive minus   |

| NC    | DS3_TXP   | 0        | 38          | K7     | SuperSpeed transmit plus   |

| NC    | DS3_TXM   | 0        | 39          | K8     | SuperSpeed transmit minus  |

| NC    | DS3_DP    | I/O      | 65          | C4     | USB 2.0 data plus          |

| NC    | DS3_DM    | I/O      | 64          | C5     | USB 2.0 data minus         |

|       | -         |          |             | DS4 P  | ort                        |

| NC    | DS4_RXP   | Ι        | 15          | K4     | SuperSpeed receive plus    |

| NC    | DS4_RXM   | Ι        | 14          | K5     | SuperSpeed receive minus   |

| NC    | DS4_TXP   | 0        | 11          | K1     | SuperSpeed transmit plus   |

| NC    | DS4_TXM   | 0<br>I/O | 12          | K2     | SuperSpeed transmit minus  |

| NC    | NC DS4_DP |          | 67          | A3     | USB 2.0 data plus          |

| NC    | DS4_DM    | I/O      | 68          | A2     | USB 2.0 data minus         |

|       | CURR      | I        | 30          | F6     | Ganged overcurrent input   |

|       | R_EN      | I/O      | 29          | G7     | Ganged power enable output |

| N     | 1C        | I/O      | 25          | NA     | NC                         |

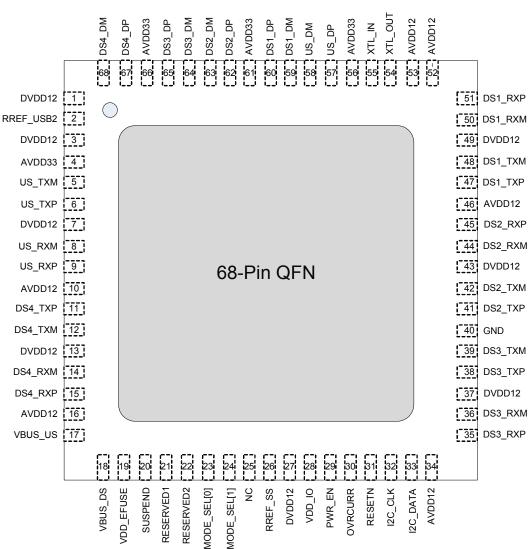

### Table 2. 68-Pin QFN, 100-Ball BGA Pinout for CYUSB3302 and CYUSB3304

### Table 4. 88-Pin QFN, 100-Ball BGA Pinout for CYUSB331X and CYUSB332X (continued)

| Pin N     | Name                                |               |      |       |                                                                                                                                          |

|-----------|-------------------------------------|---------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| CYUSB3312 | CYUSB3314<br>CYUSB3324<br>CYUSB3326 | Туре          | Pin# | Ball# | Description                                                                                                                              |

|           | CYUSB3328                           |               |      |       |                                                                                                                                          |

|           |                                     |               | -    |       | DS2 Port                                                                                                                                 |

| DS2       | RXP                                 | I             | 55   | F10   | SuperSpeed receive plus                                                                                                                  |

| DS2       | RXM                                 | Ι             | 54   | G10   | SuperSpeed receive minus                                                                                                                 |

| DS2       | TXP                                 | 0             | 51   | H8    | SuperSpeed transmit plus                                                                                                                 |

| DS2_      | TXM                                 | 0             | 52   | H7    | SuperSpeed transmit minus                                                                                                                |

| DS2       | _DP                                 | I/O           | 76   | A6    | USB 2.0 data plus                                                                                                                        |

| DS2       | _DM                                 | I/O           | 77   | A5    | USB 2.0 data minus                                                                                                                       |

| DS2_OV    | /RCURR                              | Ι             | 1    | B1    | Overcurrent detect input for DS2 port                                                                                                    |

| DS2_PV    | WREN <sup>[7]</sup>                 | I/O           | 86   | B2    | VBUS power enable output for DS2 port. When the port is disabled, this pin is in tristate.                                               |

| DS2_CE    | DP_EN <sup>[8]</sup>                | 1/0           | 00   | DZ    | This pin is called DS2_CDP_EN in the pin-strap configuration mode.                                                                       |

| DS2_AM    | MBER <sup>[7]</sup>                 |               |      |       | LED_AMBER output for DS2 port                                                                                                            |

| _         | OVABLE[0] <sup>[8]</sup>            | I/O           | 5    | E4    | This pin is called NON_REMOVABLE[0] in the pin-strap configuration mode.                                                                 |

| _         | REEN <sup>[7]</sup>                 |               |      |       | CYUSB3312/3314/3324: LED_GREEN output for DS2 port                                                                                       |

| DS2_VBU   | SEN_SL <sup>[7]</sup>               | I/O           | 6    | E3    | CYUSB3326/3328: VBUS power enable output for SS port 2                                                                                   |

| _         | OVABLE[1] <sup>[8]</sup>            |               |      |       | This pin is called NON_REMOVABLE[1] in the pin-strap configuration mode.                                                                 |

| _         | D_SS <sup>[7]</sup>                 | I/O 84        |      | C3    | LED_SS output for DS2 port                                                                                                               |

| PWR_EI    | N_SEL <sup>[8]</sup>                |               | •    |       | This pin is called PWR_EN_SEL in the pin-strap configuration mode.                                                                       |

|           | 1                                   | r – – – – – T |      | r     | DS3 Port                                                                                                                                 |

| NC        | DS3_RXP                             | I             | 45   | K10   | SuperSpeed receive plus                                                                                                                  |

| NC        | DS3_RXM                             | I             | 46   | J10   | SuperSpeed receive minus                                                                                                                 |

| NC        | DS3_TXP                             | 0             | 48   | K7    | SuperSpeed transmit plus                                                                                                                 |

| NC        | DS3_TXM                             | 0             | 49   | K8    | SuperSpeed transmit minus                                                                                                                |

| NC        | DS3_DP                              | I/O           | 79   | C4    | USB 2.0 data plus                                                                                                                        |

| NC        | DS3_DM                              | I/O           | 78   | C5    | USB 2.0 data minus                                                                                                                       |

| DS3_OV    | /RCURR                              | I             | 65   | B7    | CYUSB3314/3324/3326/3328: Overcurrent detect input for DS3 port CYUSB3312: This pin must be pulled HIGH using a 10 k $\Omega$ to VDD_IO. |

| DS3_PV    | DS3_PWREN <sup>[7]</sup>            |               | 87   | A1    | VBUS power enable output for DS3 port. When the port is disabled, this pin is in tristate.                                               |

| DS3_CE    | DP_EN <sup>[8]</sup>                |               |      |       | This pin is called DS3_CDP_EN in the pin-strap configuration mode.                                                                       |

|           | VBER <sup>[7]</sup>                 | I/O           | 85   | B3    | LED_AMBER output for DS3 port                                                                                                            |

| VID_SI    | EL[2] <sup>[8]</sup>                | -             | -    | -     | This pin is called VID_SEL[2] in the pin-strap configuration mode.                                                                       |

Notes

7. This pin can be configured as a GPIO using custom firmware. For information contact www.cypress.com/support.

8. For pin-strap configuration details, refer to Table 6 on page 25.

### Table 4. 88-Pin QFN, 100-Ball BGA Pinout for CYUSB331X and CYUSB332X (continued)

| Pin Name    |                        |      |      |         |                                                                                                                                                                                                           |

|-------------|------------------------|------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | CYUSB3314              |      |      |         |                                                                                                                                                                                                           |

| CYUSB3312   | CYUSB3324              | Туре | Pin# | Ball#   | Description                                                                                                                                                                                               |

| 010000012   | CYUSB3326              |      |      |         |                                                                                                                                                                                                           |

|             | CYUSB3328              |      |      |         |                                                                                                                                                                                                           |

|             | REEN <sup>[9]</sup>    |      |      |         | CYUSB3312/3314/3324: LED_GREEN output for DS3 port                                                                                                                                                        |

| DS3_VBU     | JSEN_SL <sup>[9]</sup> | I/O  | 64   | B8      | CYUSB3328: VBUS power enable output for SS port 3                                                                                                                                                         |

| _           | EL[1] <sup>[10]</sup>  |      |      |         | This pin is called VID_SEL[1] in the pin-strap configuration mode. For pin-strap configuration details, refer to Table 6 on page 25.                                                                      |

| DS3_LE      | ED_SS <sup>[9]</sup>   |      |      |         | LED_SS output for DS3 port                                                                                                                                                                                |

| PIN_S1      | [RAP <sup>[10]</sup>   | I/O  | 63   | B9      | This pin is called PIN_STRAP in pin-strap configuration mode. When connected to VDD_IO through a 10-k $\Omega$ resistor, this pin enables pin-strap configuration mode for HX3.                           |

|             |                        |      |      |         | DS4 Port                                                                                                                                                                                                  |

| NC          | DS4_RXP                | Ι    | 20   | K4      | SuperSpeed receive plus                                                                                                                                                                                   |

| NC          | DS4_RXM                | Ι    | 19   | K5      | SuperSpeed receive minus                                                                                                                                                                                  |

| NC          | DS4_TXP                | 0    | 16   | K1      | SuperSpeed transmit plus                                                                                                                                                                                  |

| NC          | DS4_TXM                | 0    | 17   | K2      | SuperSpeed transmit minus                                                                                                                                                                                 |

| NC          | DS4_DP                 | I/O  | 81   | A3      | USB 2.0 data plus                                                                                                                                                                                         |

| NC          | DS4_DM                 | I/O  | 82   | A2      | USB 2.0 data minus                                                                                                                                                                                        |

| DS4_O       | VRCURR                 | Ι    | 36   | F6      | CYUSB3314/3324/3326/3328: Overcurrent detect input for DS4 port. CYUSB3312: This pin must be pulled HIGH using a 10 k $\Omega$ to VDD_IO.                                                                 |

| DS4_PWRE    | N/PWR_EN4              | I/O  | 35   | G7      | VBUS power enable output for DS4 port. This pin is also used as power enable output when configured in ganged power mode using the Blaster Plus tool. When the port is disabled, this pin is in tristate. |

| DS4_CD      | DP_EN <sup>[10]</sup>  |      |      |         | This pin is called DS4_CDP_EN in the pin-strap configuration mode.                                                                                                                                        |

| DS4_A       | MBER <sup>[9]</sup>    | 1/0  | 30   | J4      | LED_AMBER output for DS4 port                                                                                                                                                                             |

| I2C_DE      | EV_ID <sup>[10]</sup>  | I/O  | 30   |         | This pin is called I2C_DEV_ID in the pin-strap configuration mode.                                                                                                                                        |

| DS4_G       | REEN <sup>[9]</sup>    |      |      |         | CYUSB3312/3314/3324: LED_GREEN output for DS4 port                                                                                                                                                        |

| DS4_VB      | USEN_SL                | I/O  | 43   | Н9      | CYUSB3328: VBUS power enable output for SS port 4                                                                                                                                                         |

| VID_SI      | EL[0] <sup>[10]</sup>  |      |      |         | This pin is called VID_SEL[0] in the pin-strap configuration mode.                                                                                                                                        |

| DS4_L       | ED_SS                  | I/O  | 26   | H4      | LED_SS output for DS4 port. The LED must be connected to GND as shown in Figure 16 on page 25. If LED is not used, this pin must be pulled HIGH using a 10 k $\Omega$ to VDD_IO.                          |

| RESE        | RVED1                  | Ι    | 27   | G4      | This pin must be pulled HIGH using a 10 k $\Omega$ to VDD_IO.                                                                                                                                             |

|             |                        |      |      | Mode Se | elect, Clock, and Reset                                                                                                                                                                                   |

| MODE        | MODE_SEL[0]            |      | 28   | G5      | Device operation mode select bit 0; refer to Table 5 on page 24                                                                                                                                           |

| MODE_SEL[1] |                        | Ι    | 29   | F4      | Device operation mode select bit 1; refer to Table 5 on page 24                                                                                                                                           |

| XTL_        | XTL_OUT                |      | 68   | E6      | Crystal out                                                                                                                                                                                               |

| XTI         | XTL_IN                 |      | 69   | E5      | Crystal in                                                                                                                                                                                                |

| RES         | SETN                   | Ι    | 37   | F7      | Active LOW reset input                                                                                                                                                                                    |

| I2C         | CLK                    | I/O  | 40   | J6      | I <sup>2</sup> C clock                                                                                                                                                                                    |

| I2C_        | DATA                   | I/O  | 41   | G8      | I <sup>2</sup> C data                                                                                                                                                                                     |

#### Notes

This pin can be configured as a GPIO using custom firmware. For information contact www.cypress.com/support.

For pin-strap configuration details, refer to Table 6 on page 25.

### Table 4. 88-Pin QFN, 100-Ball BGA Pinout for CYUSB331X and CYUSB332X (continued)

| Pin Name  |           |      |                                        |                                                               |                                                                                                                                                                                                                                                                      |

|-----------|-----------|------|----------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | CYUSB3314 |      |                                        |                                                               |                                                                                                                                                                                                                                                                      |

| CYUSB3312 | CYUSB3324 | Туре | Pin#                                   | Ball#                                                         | Description                                                                                                                                                                                                                                                          |

| C103B3312 | CYUSB3326 |      |                                        |                                                               |                                                                                                                                                                                                                                                                      |

|           | CYUSB3328 |      |                                        |                                                               |                                                                                                                                                                                                                                                                      |

| SUSI      | PEND      | I/O  | 25                                     | G3                                                            | Hub suspend status indicator. This pin is asserted if both the SS and USB 2.0 hubs are in the suspend state and is de-asserted when either of the hubs comes out of the suspend state.                                                                               |

|           |           |      |                                        | Po                                                            | wer and Ground                                                                                                                                                                                                                                                       |

| VDD_I     | EFUSE     | PWR  | 24                                     | H3                                                            | 1.2 V normal operation, 2.5 V for programming. Customers should connect to 1.2 V                                                                                                                                                                                     |

| AVE       | D12       | PWR  | 15, 21,<br>44, 56,<br>62, 67           | A10, C9,<br>F9, H1,<br>H10, J2                                | 1.2 V analog supply                                                                                                                                                                                                                                                  |

| GI        | ND        | PWR  | 50                                     | B5, C6,<br>D5, D7,<br>D9, E9,<br>F2, G9,<br>H6, J1,<br>J3, J9 | GND pin                                                                                                                                                                                                                                                              |

| DVE       | DD12      | PWR  | 8, 12,<br>18, 33,<br>47, 53,<br>59, 83 | B10, D4,<br>D6, D8,<br>E1, E10,<br>F5, K3,<br>K9              | 1.2 V core supply                                                                                                                                                                                                                                                    |

| VBUS      | S_US      | PWR  | 22                                     | H2                                                            | CYUSB3324/3328: Connect the VBUS_US pin to the local 5 V supply.<br>If ACA-Dock mode is disabled using Configuration Options on page 24,<br>this pin must be connected to VBUS from US port.<br>Other part numbers: This pin must be connected to VBUS from US port. |

| VBU       | S_DS      | PWR  | 23                                     | G2                                                            | This pin is used to power the Apple-charging circuit in HX3.<br>For BC v1.2 compliance testing, connect pin to GND. For normal<br>operation, connect pin to local 5 V supply.                                                                                        |

| AVE       | D33       | PWR  | 9, 70,<br>75, 80                       | A4, A7,<br>B6, F3                                             | 3.3 V analog supply                                                                                                                                                                                                                                                  |

| VDD_IO    |           | PWR  | 34, 66,<br>88                          | B4, E7,<br>G6                                                 | 3.3 V I/O supply                                                                                                                                                                                                                                                     |

|           |           |      |                                        | USB F                                                         | Precision Resistors                                                                                                                                                                                                                                                  |

| RREF      | USB2      | А    | 7                                      | E2                                                            | Connect pin to a precision resistor (6.04 k $\Omega \pm 1\%$ ) to generate a current reference for USB 2.0 PHY.                                                                                                                                                      |

| RRE       | F_SS      | А    | 32                                     | H5                                                            | Connect pin to a precision resistor (200 $\Omega \pm 1\%$ ) for SS PHY termination impedance calibration.                                                                                                                                                            |

## System Interfaces

#### Upstream Port (US)

This port is compliant with the USB 3.0 specification and includes an integrated 1.5 k $\Omega$  pull-up and termination resistors. It also supports ACA-Dock to enable charging an OTG host connected on the US port.

#### Downstream Ports (DS1, 2, 3, 4)

DS ports are compliant with the USB 3.0 specification and integrate 15 k $\Omega$  pull-down and termination resistors. Ports can be disabled or enabled, and can be set to removable or non-removable options. BC v1.2 charging is enabled by default and can be disabled on each DS port using the configuration options (see Configuration Options).

#### Communication Interfaces (I<sup>2</sup>C)

The interface follows the Inter-IC Bus specification, version 3.0, with support for the standard mode (100 kHz) and the fast mode (400 kHz) frequencies. HX3 supports I<sup>2</sup>C in the slave and master modes. The I<sup>2</sup>C interface supports the multi-master mode of operation. Both the SCL and SDA signals require external pull-up resistors based on the specification. VDD\_IO for HX3 is 3.3 V and it is expected that the I<sup>2</sup>C pull-up resistors will be connected to the same supply.

#### Oscillator

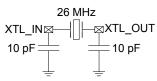

HX3 requires an external crystal with a frequency of 26 MHz and an accuracy of  $\pm$ 150 ppm in parallel resonant, fundamental mode. The crystal drive circuit is capable of a low-power drive level (<200  $\mu$ W). The crystal connection to the XTL\_OUT and XTL\_IN pins is shown in Figure 14.

#### Figure 14. Crystal Connection

### GPIOs

HX3 GPIOs are used for overcurrent sensing, controlling external power switches, and driving LEDs. These pins can sink up to 4 mA current each. GPIOs also enable pin-straps for input configuration. Refer to Table 6 for more details.

#### **Power Control**

The PWR\_EN[1-4] and OV\_CURR[1-4] pins interface HX3 to external power switches. These pins are used to control power switches for DS port power and monitor overcurrent conditions. The power switch polarity and the power control mode (individual and ganged) can be changed using the configuration options.

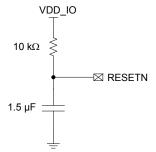

#### Reset

HX3 operates with two external power supplies, 3.3 V and 1.2 V. There is no power sequencing requirement between these two supplies. However, the RESETN pin should be held LOW until both these supplies become stable. The RESETN pin can be tied to VDD\_IO through an external resistor and to ground (GND) through an external capacitor (minimum 5 ms time constant), as shown in Figure 15. This creates a clean reset signal for power-on reset (POR).

HX3 does not support internal brown-out detection. If the system requires this feature, an external reset should be provided on the RESETN pin when supplies are below their valid operating ranges.

#### Figure 15. Reset Connection

#### **Configuration Mode Select**

Configuration options are selected through the MODE\_SEL pins and the pin-strap enable pin (PIN\_STRAP). After power-up, these pins are sampled by an on-chip bootloader to determine the configuration options (see Table 5).

#### Table 5. HX3 Boot Sequence

| MODE<br>SEL[1] | MODE<br>SEL[0] | HX3 Configuration Modes                                                               |  |  |  |  |  |

|----------------|----------------|---------------------------------------------------------------------------------------|--|--|--|--|--|

| 0              | 0              | Reserved. Do not use this mode.                                                       |  |  |  |  |  |

| 1              | 1              | Internal ROM configuration                                                            |  |  |  |  |  |

| 0              | 1              | I <sup>2</sup> C Master, read configuration from I <sup>2</sup> C EEPROM <sup>*</sup> |  |  |  |  |  |

| 1              | 0              | I <sup>2</sup> C Slave, configure from an external I <sup>2</sup> C Master*           |  |  |  |  |  |

\* Download Cypress-provided firmware from www.cypress.com/hx3.

### **Configuration Options**

HX3 can be configured by using one of the following:

- eFuse (one-time programmable memory)

- Pin-Strap (read configuration from dedicated pins at power on)

- External I<sup>2</sup>C slave such as an EEPROM

- External I<sup>2</sup>C master

The I<sup>2</sup>C master/slave configuration overrides the pin-strap configuration. Pin-straps override the eFuse configuration, and the eFuse configuration overrides the internal ROM configuration.

#### eFuse Configuration

HX3 contains eFuses, which are OTP elements on the chip that can be electrically blown. The eFuses are read by the bootloader to determine the customer-specific configurations. eFuse programming is supported only at factory and distributor locations where programming conditions can be controlled. eFuse programming is supported under the following conditions:

Temperature range of 25  $^\circ\text{C}\text{--}70$   $^\circ\text{C}$  and programming voltage of 2.5 V–2.7 V.

#### Pin-Strap Configuration

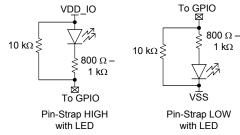

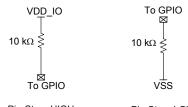

Table 6. Pin-Strap Configuration

Pin-straps are supported for select product options (see Table 1 on page 5) to provide reconfigurability without an additional EEPROM. The pin-strap configuration is enabled by pulling the Pin #63 of 88-pin QFN HIGH. Table 6 on page 25 shows the configuration options supported through pin-straps and the GPIOs used for this purpose. Figure 16 and Figure 17 show how the GPIOs need to be connected if pin-strap and LED connection are required or only pin-strap is required.

HX3 samples pin-strap GPIOs at power-up. Floating straps are considered as invalid and the default configuration is used. If PIN\_STRAP (Pin #63 of 88-pin QFN) is floating, all strap inputs are considered invalid. A GPIO is considered strapped "1" or "0" when connected with a weak pull-up (10 k $\Omega$ ) or pull-down (10 k $\Omega$ ) respectively. After the initial sampling at power-up and reset, the GPIOs are used in their normal functions.

## Figure 16. Pin-Strap With LED or LED-Only Connection

#### Figure 17. Pin-Strap Connection

Pin-Strap HIGH

Pin-Strap LOW

| 88-QFN<br>Pin # | Pin-Strap Name                   | Strappo                                                                                | ed '0' <sup>[11]</sup>                                                                          | Strapped '1' <sup>[11]</sup>                              |                          |  |  |  |  |

|-----------------|----------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------|--|--|--|--|

| 30              | I2C_DEV_ID <sup>[12]</sup>       | ID 0: HX3 I <sup>2</sup> C slave ac<br>This is also the defaul<br>the 68-pin QFN packa | ddress (7 bits) is 0x60.<br>t I <sup>2</sup> C slave address for<br>ge.                         | ID 1: HX3 I <sup>2</sup> C slave address (7 bits) is 0x58 |                          |  |  |  |  |

| 31              | PWR_SW_POL                       | Power enable and ove                                                                   | ercurrent will be active                                                                        | Power enable and ove<br>HIGH                              | ercurrent will be active |  |  |  |  |

| 2               | ACA_DOCK                         | Disa                                                                                   | abled                                                                                           | Ena                                                       | bled                     |  |  |  |  |

| 84              | PWR_EN_SEL                       | Indiv                                                                                  | vidual                                                                                          | Ga                                                        | ang                      |  |  |  |  |

| 63              | PIN_STRAP <sup>[13]</sup>        | No pin-s                                                                               | strapping                                                                                       | Pin-strapping con                                         | figuration enabled       |  |  |  |  |

| 4               | PORT_DISABLE[1]                  | PORT_DISABLE[1:0]                                                                      |                                                                                                 | •                                                         |                          |  |  |  |  |

| 3               | PORT_DISABLE[0]                  | b'01: DS1, DS2, DS3<br>b'10: DS1, DS2 active<br>b'11: DS1 active                       |                                                                                                 |                                                           |                          |  |  |  |  |

| 6               | NON_REMOVABLE[1] <sup>[14]</sup> |                                                                                        | NON_REMOVABLE[1:0] =                                                                            |                                                           |                          |  |  |  |  |

| 5               | NON_REMOVABLE[0] <sup>[14]</sup> | b'01: DS1, DS2, DS3                                                                    | b'00: DS1, DS2, DS3, DS4 removable<br>b'01: DS1, DS2, DS3 removable<br>b'10: DS1, DS2 removable |                                                           |                          |  |  |  |  |

| 85              | VID[2]                           |                                                                                        |                                                                                                 |                                                           |                          |  |  |  |  |

| 64              | VID[1]                           | Reserved. If PIN_STR                                                                   | AP is enabled and CY                                                                            | VID is required, strap V                                  | 'ID[2:0] to '1'.         |  |  |  |  |

| 43              | VID[0]                           |                                                                                        |                                                                                                 |                                                           |                          |  |  |  |  |

| 38              | DS1 CDP EN <sup>[15]</sup>       | strapped '0'                                                                           | strapped '1'                                                                                    | strapped '0'                                              | strapped '1'             |  |  |  |  |

| 38              | DSI_CDP_EN <sup>103</sup>        | DS1 CDP enabled                                                                        | DS1 CDP disabled                                                                                | DS1 CDP disabled                                          | DS1 CDP enabled          |  |  |  |  |

| 86              | DS2_CDP_EN <sup>[15]</sup>       | DS2 CDP enabled                                                                        | DS2 CDP disabled                                                                                | DS2 CDP disabled                                          | DS2 CDP enabled          |  |  |  |  |

| 87              | DS3_CDP_EN <sup>[15]</sup>       | DS3 CDP enabled                                                                        | DS3 CDP disabled                                                                                | DS3 CDP disabled                                          | DS3 CDP enabled          |  |  |  |  |

| 35              | DS4_CDP_EN <sup>[15]</sup>       | DS4 CDP enabled                                                                        | DS4 CDP disabled                                                                                | DS4 CDP disabled                                          | DS4 CDP enabled          |  |  |  |  |

| Notes           |                                  | 1                                                                                      | 1                                                                                               | 1                                                         | ·]                       |  |  |  |  |

Notes

11. See Figure 16 and Figure 17.

13. VID, PORT\_DISABLE, NON\_REMOVABLE are group straps. If one of the pins in a group strap is floating (INVALID), that group input will be INVALID and the default will not be overwritten.

14. These DS ports are exposed ports and the connected devices can be removed.

15. DSx\_CDP\_EN will be active LOW input when PWR\_SW\_POL is set to active LOW; similarly DSx\_CDP\_EN will be active HIGH input when PWR\_SW\_POL is set to active HIGH.

<sup>12.</sup> I2C\_DEV\_ID is valid only when HX3 is in I<sup>2</sup>C slave mode.

### I<sup>2</sup>C Configuration

When enabled for  $I^2C$  configuration through the MODE\_SEL pins (See Table 5 on page 24), HX3 can be configured as an  $I^2C$  master or as an  $I^2C$  slave. HX3's configuration data is a maximum of 197 bytes and HX3's firmware is 10 KB. Note that HX3's firmware also includes configuration settings.

### HX3 as I<sup>2</sup>C Master

HX3 reads configurations from an external I<sup>2</sup>C EEPROM with sizes ranging from 16 to 64 KB. An example of a supported EEPROM is 24LC128. Based on the contents of the bSignature and bImageType fields in Table 7 on page 26, HX3 performs one of the following actions:

- Loads custom configuration settings from the EEPROM when bSignature is "CY" and bImageType is 0xD4.

- Loads the Cypress-provided firmware from the EEPROM when bSignature is "CY" and bImageType is 0xB0. This firmware also includes configuration settings.

- If bSignature ≠ "CY", HX3 enumerates in the vendor-specific mode.

The contents of the EEPROM can be updated with the easy-to-use Cypress Blaster Plus tool. Blaster Plus is a

GUI-based tool to configure HX3. This tool allows to do the following:

- Download the Cypress-provided firmware from a PC via HX3's US port and store it on an EEPROM connected to HX3's I<sup>2</sup>C port.

- Read the configuration settings from the EEPROM. These settings are displayed in the Blaster Plus GUI. Modify settings as required.

- Write back the updated settings on to the EEPROM. In addition, an image file can be created for external use.

The Blaster Plus tool, user guide, and the Cypress-provided firmware are available at www.cypress.com/hx3.

#### HX3 as I<sup>2</sup>C Slave

An external I<sup>2</sup>C master can program the configuration settings into HX3 according to the EEPROM map in Table 7 on page 26. Alternatively, the HX3 firmware (<10 KB), which includes configuration settings, can also be programmed. It is recommended to use the Blaster Plus tool to create the HX3 firmware or configuration image file. HX3's I<sup>2</sup>C slave address needs to be provided while creating the image file. Refer to Table 6 for HX3's I<sup>2</sup>C slave address.

| I <sup>2</sup> C Offset | Bits | Name                   | Default                                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-------------------------|------|------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0                       | 7:0  | bSignature LSB ("C")   | 0x43                                                                                       | The first byte of the 2-byte signature initialized with "CY" ASCII text.<br>When the signature is not valid, the hub enumerates as a vendor-specific device.                                                                                                                                                                                                                        |  |  |  |

| 1                       | 7:0  | bSignature MSB ("Y")   | ASCII text. When the signature is not valid, the hub enume<br>as a vendor-specific device. |                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 2                       | 7:6  | bImageCTL              | b'00                                                                                       | Reserved                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                         | 5:4  | I <sup>2</sup> C Speed | b'11                                                                                       | b'01: 400 kHz<br>b'11: 100 kHz                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                         | 3:1  | bImageCTL              | b'000                                                                                      | Reserved                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                         | 0    | bImageCTL              | 0                                                                                          | 0: Execution binary file<br>1: Data file                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 3                       | 7:0  | bImageType             | 0xD4                                                                                       | 0xD4: Load only configuration<br>0xB0: Load firmware boot image<br>All other bImageType will return an error code.                                                                                                                                                                                                                                                                  |  |  |  |

| 4                       | 7:0  | bD4Length              | 40                                                                                         | bD4Length is defined in bytes as the length from offset 5.<br>I <sup>2</sup> C offset bytes 0–4 are the header bytes.<br>bD4Length = 6: Only update VID, PID, and DID<br>bD4Length = 18: Configuration options (no PHY trim)<br>bD4Length = 40: Configuration options with PHY trim options<br>bD4Length > 40: User must provide valid string descriptors<br>bD4Length > 192: Error |  |  |  |

| 5                       | 7:0  | VID [7:0]              | 0xB4                                                                                       | Custom Vendor ID - LSB                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 6                       | 7:0  | VID [15:8]             | 0x04                                                                                       | Custom Vendor ID - MSB                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 7                       | 7:0  | PID [7:0]              | 0x04                                                                                       | Custom Product ID (PID)                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 8                       | 7:0  | PID [15:8]             | 0x65                                                                                       | Default: 0x6504<br>If separate PID is used for USB 2.0, the USB 2.0 PID will be read<br>from offset 35 and 36.<br>Else, USB 2.0 PID = PID+2; Default: 0x6506                                                                                                                                                                                                                        |  |  |  |

#### Table 7. EEPROM Map

#### Table 7. EEPROM Map (continued)

| I <sup>2</sup> C Offset | Bits | Name                   | Default                                         | Description                                                                                                                                                                                                                                                                     |

|-------------------------|------|------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9                       | 7:0  | DID [7:0]              | 00 -<br>88-pin<br>QFN,<br>10 -<br>68-pin<br>QFN | Custom Device ID - revision - LSB                                                                                                                                                                                                                                               |

| 10                      | 7:0  | DID [15:8]             | 50                                              | Custom Device ID - revision - MSB                                                                                                                                                                                                                                               |

| 11                      | 7:0  | Reserved               | 0                                               | Reserved                                                                                                                                                                                                                                                                        |

| 12                      | 7:4  | SHARED_LINK_EN         | b'0000                                          | Enable Shared Link on DS port<br>bit[7:4]=DS4, DS3, DS2, DS1<br>0: Shared Link not enabled<br>1: Shared Link enabled                                                                                                                                                            |

|                         | 3:0  | SHC_ACTIVE_PORTS [3:0] | b'1111                                          | Indicates if a SuperSpeed port is active.<br>bit[3:0] = DS4, DS3, DS2, DS1<br>0: Not active<br>1: Active                                                                                                                                                                        |

| 13                      | 7:0  | POWER_ON_TIME          | 0x32                                            | Time (in 2-ms intervals) from the time the power-on sequence<br>begins on a port until power is good on that port<br>(bPwron2PwrGood)                                                                                                                                           |

| 14                      | 7:4  | REMOVABLE_PORTS [3:0]  | b'1111                                          | Indicates if the port is removable.<br>bit[7:4]=DS4, DS3, DS2, DS1<br>0: Non-removable<br>1: Removable                                                                                                                                                                          |

|                         | 3:0  | UHC_ACTIVE_PORTS [3:0] | b'1111                                          | Indicates if a USB 2.0 port is active.<br>bit[3:0]=DS4, DS3, DS2, DS1<br>0: Not active<br>1: Active                                                                                                                                                                             |

| 15                      | 7    | SS_LED_PIN_CONTROL     | 0                                               | Port 1–4: SS LED disable<br>0: DS[1:4]_LED_SS are LEDs. The LED glows when the SS port<br>is active and not in disabled state.<br>1: DS[1:4]_LED_SS are not LEDs                                                                                                                |

|                         | 6    | GREEN_LED_PIN_CONTROL  | 0                                               | Port 1–4: USB 2.0 Green LED disable<br>0: DS[1:4]_GREEN are LEDs<br>1: DS[1:4]_GREEN are not LEDs                                                                                                                                                                               |

|                         | 5    | AMBER_LED_PIN_CONTROL  | 0                                               | Port 1–4: USB 2.0 Amber LED disable<br>0: DS[1:4]_AMBER are LEDs<br>1: DS[1:4]_AMBER are not LEDs                                                                                                                                                                               |

|                         | 4    | PORT_INDICATORS        | 1                                               | Port indicators supported<br>0: Port indicators are not supported on its DS-facing ports and<br>the USB 2.0 PORT_INDICATOR request has no effect.<br>1: Port indicators are supported on its DS-facing ports and the<br>USB 2.0 PORT_INDICATOR request controls the indicators. |

|                         | 3    | COMPOUND_HUB           | 0                                               | Identifies a compound device.<br>0: Hub is not part of a compound device.<br>1: Hub is part of a compound device.                                                                                                                                                               |

|                         | 2:1  | Reserved               | 0                                               | Reserved                                                                                                                                                                                                                                                                        |

|                         | 0    | GANG                   | 0                                               | 1: Ganged power switch enable for all DS ports<br>0: Individual port power switch enable for each DS port                                                                                                                                                                       |

#### Table 7. EEPROM Map (continued)

| I <sup>2</sup> C Offset | Bits | Name                       | Default                                                                                             | Description                                                                                                                                                                       |

|-------------------------|------|----------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 51 + X                  | 7:0  | bString: Product           | 'C', 0,<br>'Y', 0, '-',<br>0, 'H', 0,<br>'X', 0, '3',<br>0, ' ', 0,<br>'H', 0,<br>'U', 0,<br>'B', 0 | Product string: UNICODE UTF-16LE per USB 2.0 specification:<br>"CY-HX3 HUB"                                                                                                       |

| 49 + X + Y              | 7:0  | bLength: Serial Number (Z) | 22                                                                                                  | Serial number string length ("bLength: LangID + bLength:<br>Manufacturer + bLength: Product + bLength: Serial Number"<br>should be less than or equal to 152 bytes). $Z \le 66$ . |

| 50 + X + Y              | 7:0  | DescType                   | 3                                                                                                   | String descriptor type (constant value)                                                                                                                                           |

| 51 + X + Y              | 7:0  | bString: Serial Number     | (1', 0, (2',<br>0, (3', 0,<br>(4', 0, (5',<br>0, (6', 0,<br>(7', 0, (8',<br>0, (9', 0,<br>(A', 0)   | Serial number string: UNICODE UTF-16LE per USB 2.0 speci-<br>fication: "123456789A"                                                                                               |

## EMI

ESD

HX3 meets the EMI requirements outlined by FCC 15B (USA) and EN55022 (Europe) for consumer electronics. HX3 tolerates EMI conducted by aggressors outlined by the above specifications and continues to function as expected.

HX3 has a built-in ESD protection on all pins. The ESD protection level provided on these ports is 2.2 kV Human Body Model (HBM) based on the JESD22-A114 specification.

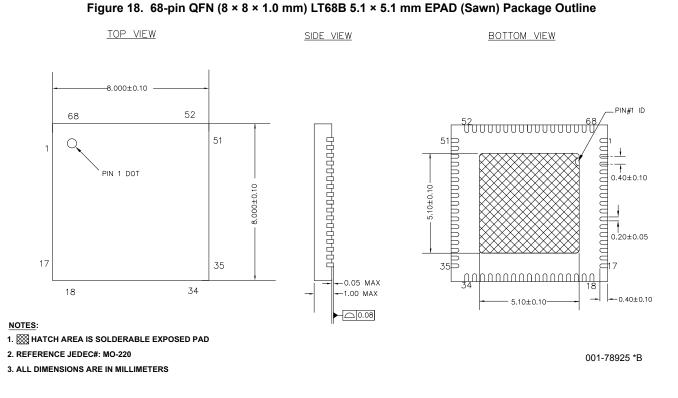

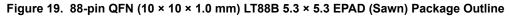

## Packaging

## Table 12. Package Characteristics

| Parameter       | Description                           | Min | Тур  | Max | Units |

|-----------------|---------------------------------------|-----|------|-----|-------|

| T <sub>A</sub>  | Operating ambient temperature         | -40 | -    | 85  | °C    |

| TJ              | Operating junction temperature        | -40 | -    | 125 | °C    |

| T <sub>JA</sub> | Package J <sub>A</sub> (68-pin QFN)   | -   | 16.2 | -   | °C/W  |

| T <sub>JA</sub> | Package J <sub>A</sub> (88-pin QFN)   | -   | 15.7 | _   | °C/W  |

| T <sub>JA</sub> | Package J <sub>A</sub> (100-ball BGA) | -   | 35   | -   | °C/W  |

| T <sub>JC</sub> | Package J <sub>C</sub> (68-pin QFN)   | -   | 23.8 | -   | °C/W  |

| T <sub>JC</sub> | Package J <sub>C</sub> (88-pin QFN)   | -   | 18.9 | -   | °C/W  |

| T <sub>JC</sub> | Package J <sub>C</sub> (100-ball BGA) | -   | 12   | -   | °C/W  |

### Table 13. Solder Reflow Peak Temperature

| Package      | Maximum Peak Temperature | Maximum Time at Peak Temperature |

|--------------|--------------------------|----------------------------------|

| 68-pin QFN   | 260 °C                   | 30 seconds                       |

| 88-pin QFN   | 260 °C                   | 30 seconds                       |

| 100-ball BGA | 260 °C                   | 30 seconds                       |

## Table 14. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 68-pin QFN   | MSL 3 |

| 88-pin QFN   | MSL 3 |

| 100-ball BGA | MSL 3 |

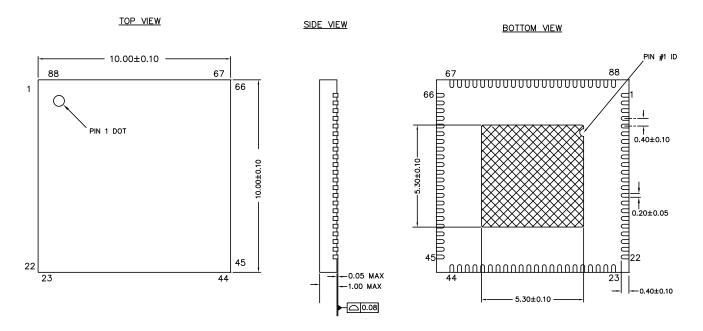

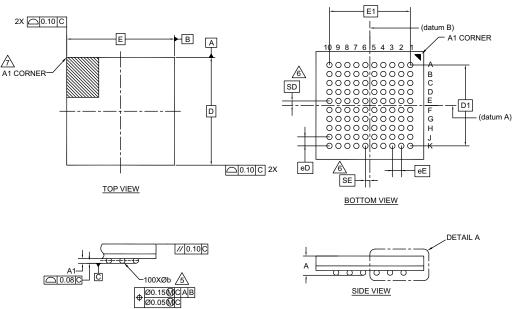

## **Package Diagrams**

001-76569 \*B

∕∕∖

#### Figure 20. 100-Ball BGA (6.0 × 6.0 × 1.0 mm) BZ100 Package Outline

| 0.445.01 | DIMENSIONS |      |      |  |

|----------|------------|------|------|--|

| SYMBOL   | MIN.       | NOM. | MAX. |  |

| А        | -          | -    | 1.00 |  |

| A1       | 0.16       | -    | -    |  |

| D        | 6.00 BSC   |      |      |  |

| E        | 6.00 BSC   |      |      |  |

| D1       | 4.50 BSC   |      |      |  |

| E1       | 4.50 BSC   |      |      |  |

| MD       | 10         |      |      |  |

| ME       | 10         |      |      |  |

| N        | 100        |      |      |  |

| Øb       | 0.25       | 0.30 | 0.35 |  |

| eD       | 0.50 BSC   |      |      |  |

| еE       | 0.50 BSC   |      |      |  |

| SD       | 0.25 BSC   |      |      |  |

| SE       | 0.25 BSC   |      |      |  |

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. SOLDER BALL POSITION DESIGNATION PER JEP95, SECTION 3, SPP-020.

- 3. "e" REPRESENTS THE SOLDER BALL GRID PITCH.

- 4. SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D" DIRECTION. SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE "E" DIRECTION. N IS THE NUMBER OF POPULATED SOLDER BALL POSITIONS FOR MATRIX SIZE MD X ME.

- 5 DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL DIAMETER IN A PLANE PARALLEL TO DATUM C.

- 6 "SD" AND "SE" ARE MEASURED WITH RESPECT TO DATUMS A AND B AND DEFINE THE POSITION OF THE CENTER SOLDER BALL IN THE OUTER ROW. WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN THE OUTER ROW "SD" OR "SE" = 0.

WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN THE OUTER ROW, "SD" = eD/2 AND "SE" = eE/2.

- A1 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK MARK METALIZED MARK, INDENTATION OR OTHER MEANS.

- 8. "+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED SOLDER BALLS.

- 9. JEDEC SPECIFICATION NO. REF. : MO-195C.

51-85209 \*F

## Acronyms

#### Table 15. Acronyms Used in this Document

| Acronym | Description                                            |

|---------|--------------------------------------------------------|

| ACA     | Accessory Charging Adapter                             |

| ASSP    | Application-Specific Standard Product                  |

| BC      | Battery Charging                                       |

| CDP     | Charging Downstream Port                               |

| DS      | DownStream                                             |

| DCP     | Dedicated Charging Port                                |

| DNU     | Do Not Use                                             |

| DWG     | Device Working Group                                   |

| EEPROM  | Electrically Erasable Programmable Read-Only<br>Memory |

| FS      | Full-Speed                                             |

| FW      | FirmWare                                               |

| GND     | GrouND                                                 |

| GPIO    | General-Purpose Input/Output                           |

| HS      | Hi-Speed                                               |

| ISP     | In-System Programming                                  |

| I/O     | Input/Output                                           |

| LS      | Low-Speed                                              |

| NC      | No Connect                                             |

| OTG     | On-The-Go                                              |

| PID     | Product ID                                             |

| POR     | Power-On Reset                                         |

| ROM     | Read-Only Memory                                       |

| SCL     | Serial CLock                                           |

| SDA     | Serial DAta                                            |

| SS      | SuperSpeed                                             |

| TT      | Transaction Translator                                 |

| US      | UpStream                                               |

| VID     | Vendor ID                                              |

## **Reference Documents**

USB 2.0 Specification USB 3.0 Specification Battery Charging Specification

## **Document Conventions**

## **Units of Measure**

| Table | 16. | Units | of | Measure |

|-------|-----|-------|----|---------|

|-------|-----|-------|----|---------|

| Symbol | Unit of Measure    |  |  |

|--------|--------------------|--|--|

| °C     | degree celsius     |  |  |

| Ω      | ohm                |  |  |

| Gbps   | gigabit per second |  |  |

| KB     | kilobyte           |  |  |

| kHz    | kilohertz          |  |  |

| kΩ     | kiloohm            |  |  |

| Mbps   | megabit per second |  |  |

| MHz    | megahertz          |  |  |

| μA     | microampere        |  |  |

| mA     | milliampere        |  |  |