Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | HC11                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 3MHz                                                                     |

| Connectivity               | SCI, SPI                                                                 |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 26                                                                       |

| Program Memory Size        | 4KB (4K x 8)                                                             |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc711d3cfne3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

## Chapter 3 Central Processor Unit (CPU)

|         | ` ,                                                             |    |

|---------|-----------------------------------------------------------------|----|

| 3.1     | Introduction                                                    | 33 |

| 3.2     | CPU Registers                                                   | 33 |

| 3.2.1   | Accumulators A, B, and D                                        |    |

| 3.2.2   | Index Register X (IX)                                           | 34 |

| 3.2.3   | Index Register Y (IY)                                           | 34 |

| 3.2.4   | Stack Pointer (SP)                                              | 34 |

| 3.2.5   | Program Counter (PC)                                            |    |

| 3.2.6   | Condition Code Register (CCR)                                   | 36 |

| 3.2.6.1 | Carry/Borrow (C)                                                |    |

| 3.2.6.2 |                                                                 |    |

| 3.2.6.3 |                                                                 |    |

| 3.2.6.4 |                                                                 |    |

| 3.2.6.5 |                                                                 |    |

| 3.2.6.6 |                                                                 |    |

| 3.2.6.7 |                                                                 |    |

| 3.2.6.8 |                                                                 |    |

| 3.3     | Data Types                                                      | 37 |

| 3.4     | Opcodes and Operands                                            | 38 |

| 3.5     | Addressing Modes                                                |    |

| 3.5.1   | Immediate                                                       |    |

| 3.5.2   | Direct                                                          |    |

| 3.5.3   | Extended                                                        |    |

| 3.5.4   | Indexed                                                         | 39 |

| 3.5.5   | Inherent                                                        |    |

| 3.5.6   | Relative                                                        | 39 |

| 3.6     | Instruction Set                                                 | 39 |

|         |                                                                 |    |

|         | Chapter 4                                                       |    |

|         | Resets, Interrupts, and Low-Power Modes                         |    |

| 4.1     | Introduction                                                    |    |

| 4.2     | Res <u>ets</u>                                                  |    |

| 4.2.1   | RESET Pin                                                       |    |

| 4.2.2   | Power-On Reset (POR)                                            | 47 |

| 4.2.3   | Computer Operating Properly (COP) Reset                         |    |

| 4.2.4   | Clock Monitor Reset                                             |    |

| 4.2.5   | System Configuration Options Register                           |    |

| 4.3     | Interrupts                                                      |    |

| 4.3.1   | Software Interrupt (SWI)                                        |    |

| 4.3.2   | Illegal Opcode Trap                                             |    |

| 4.3.3   | Real-Time Interrupt (RTI)                                       |    |

| 4.3.4   | Interrupt Mask Bits in the CCR                                  |    |

| 4.3.5   | Priority Structure                                              |    |

| 4.3.6   | Highest Priority I Interrupt and Miscellaneous Register (HPRIO) | 58 |

| 4.4            | Low-Power Operation                   | 60 |

|----------------|---------------------------------------|----|

| 4.4.1          | Stop Mode                             |    |

| 4.4.2          | Wait Mode                             | 60 |

|                | Chapter 5                             |    |

|                | Input/Output (I/O) Ports              |    |

| 5.1            | Introduction                          | 61 |

| 5.2            | Port A                                |    |

| _              |                                       |    |

| 5.3<br>5.3.1   | Port B                                |    |

| 5.3.1          | Port B Data Register                  |    |

| 5.4            | Port C                                |    |

| 5.4.1          | Port C Control Register               |    |

| 5.4.2          | Port C Data Register                  |    |

| 5.4.3          | Port C Data Direction Register        |    |

| 5.5            | Port D.                               |    |

| 5.5.1          | Port D Data Register                  |    |

| 5.5.2          | Port D Data Direction Register        |    |

|                |                                       |    |

|                | Chapter 6                             |    |

|                | Serial Communications Interface (SCI) |    |

| 6.1            | Introduction                          |    |

| 6.2            | Data Format                           |    |

| 6.3            | Transmit Operation                    | 65 |

| 6.4            | Receive Operation                     | 65 |

| 6.5            | Wakeup Feature                        |    |

| 6.5.1          | Idle-Line Wakeup                      |    |

| 6.5.2          | Address-Mark Wakeup                   |    |

| 6.6            | SCI Error Detection                   |    |

| 6.7            | SCI Registers                         |    |

| 6.7.1          | SCI Data Register                     |    |

| 6.7.2          | SCI Control Register 1                |    |

| 6.7.3<br>6.7.4 | SCI Control Register 2                |    |

| 6.7.5          | SCI Status Register                   |    |

| 6.8            | Status Flags and Interrupts           |    |

| 0.0            | Status Flags and Interrupts           | 75 |

|                | Chapter 7                             |    |

|                | Serial Peripheral Interface (SPI)     |    |

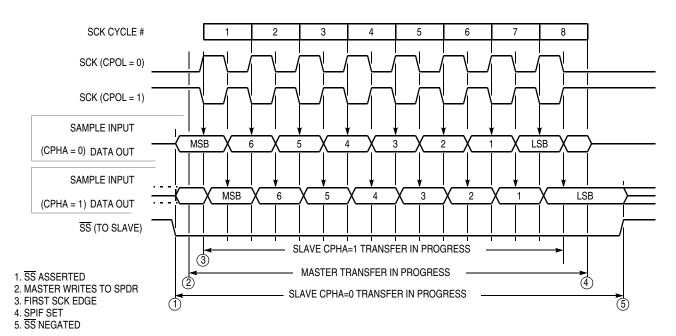

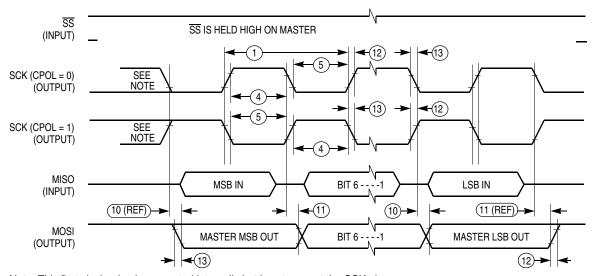

| 7.1            | Introduction                          | 77 |

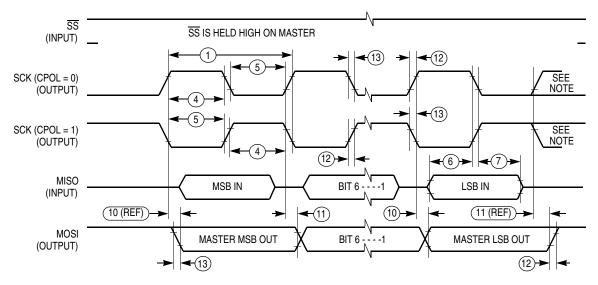

| 7.2            | Functional Description                | 77 |

| 7.3            | SPI Transfer Formats                  |    |

| 7.4            | Clock Phase and Polarity Controls     |    |

| 7.5            | SPI Signals                           |    |

| 7.5.1          | Master In/Slave Out (MISO).           |    |

| 7.5.2          | Master Out/Slave In (MOSI)            |    |

|                |                                       |    |

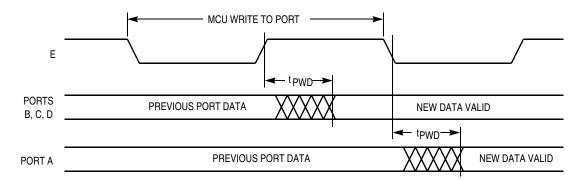

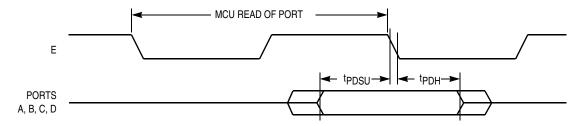

| 9.8            | Expansion Bus Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 115 |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 9.9            | Serial Peripheral Interface Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 117 |

|                | Chapter 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                | Ordering Information and Mechanical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 10.1           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 121 |

| 10.2           | Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 121 |

| 10.3           | 40-Pin DIP (Case 711-03)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 121 |

| 10.4           | 44-Pin PLCC (Case 777-02)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 122 |

| 10.5           | 44-Pin QFP (Case 824A-01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 123 |

|                | Appendix A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                | MC68HC11D3 and MC68HC11D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| <b>A.1</b>     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 125 |

| A.2            | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 126 |

| A.3            | Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 127 |

| A.4            | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 128 |

| A.5            | MC68HC11D3 and MC68HC11D0 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| A.5.1          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| A.5.2          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| A.6            | Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 129 |

|                | Appendix B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                | MC68L11D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| B.1            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| B.2            | MC68L11D0 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| B.2.1<br>B.2.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| B.2.3          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| B.2.4          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| B.2.5          | The state of the s |     |

| B.2.6          | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| B.3            | Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 136 |

#### **Operating Modes and Memory**

#### 2.4.2 Programming the EPROM with Downloaded Data

When using this method, the EPROM is programmed by software while in the special test or bootstrap modes. User-developed software can be uploaded through the SCI or a ROM-resident EPROM programming utility can be used. The 12-volt nominal programming voltage must be present on the XIRQ/V<sub>PP</sub> pin. To use the resident utility, bootload a 3-byte program consisting of a single jump instruction to \$BF00. \$BF00 is the starting address of a resident EPROM programming utility. The utility program sets the X and Y index registers to default values, then receives programming data from an external host, and puts it in EPROM. The value in IX determines programming delay time. The value in IY is a pointer to the first address in EPROM to be programmed (default = \$F000).

When the utility program is ready to receive programming data, it sends the host the \$FF character. Then it waits. When the host sees the \$FF character, the EPROM programming data is sent, starting with the first location in the EPROM array. After the last byte to be programmed is sent and the corresponding verification data is returned, the programming operation is terminated by resetting the MCU.

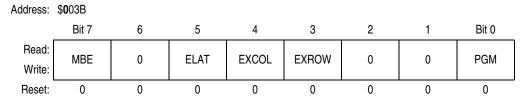

#### 2.4.3 PROM Programming Control Register

The PROM programming control register (PPROG) is used to control the programming of the OTPROM or EPROM. PPROG is cleared on reset so that the PROM is configured for normal read.

Figure 2-5. PROM Programming Control Register (PPROG)

#### MBE — Multiple Byte Program Enable Bit

This bit is reserved for testing.

#### Bit 6, 2, and 1 — Not implemented

Always read 0.

#### **ELAT — EPROM (OTPROM) Latch Control Bit**

- 1 = PROM address and data bus are configured for programming. Writes to PROM cause address and data to be latched. The PROM cannot be read.

- 0 = PROM address and data bus are configured for normal reads. PROM cannot be programmed.

#### **EXCOL** — Select Extra Columns Bit

This bit is reserved for testing.

#### **EXROW** — Select Extra Row Bit

This bit is reserved for testing.

#### PGM — EPROM (OTPROM) Program Command Bit

This bit may be written only when ELAT = 1.

- 1 = Programming power is switched on to PROM array.

- 0 = Programming power is switched off.

#### 3.5.3 Extended

In the extended addressing mode, the effective address of the argument is contained in two bytes following the opcode byte. These are 3-byte instructions (or 4-byte instructions if a prebyte is required). One or two bytes are needed for the opcode and two for the effective address.

#### 3.5.4 Indexed

In the indexed addressing mode, an 8-bit unsigned offset contained in the instruction is added to the value contained in an index register (IX or IY). The sum is the effective address. This addressing mode allows referencing any memory location in the 64-Kbyte address space. These are 2- to 5-byte instructions, depending on whether a prebyte is required.

#### 3.5.5 Inherent

In the inherent addressing mode, all the information necessary to execute the instruction is contained in the opcode. Operations that use only the index registers or accumulators, as well as control instructions with no arguments, are included in this addressing mode. These are 1- or 2-byte instructions.

#### 3.5.6 Relative

The relative addressing mode is used only for branch instructions. If the branch condition is true, an 8-bit signed offset included in the instruction is added to the contents of the program counter to form the effective branch address. Otherwise, control proceeds to the next instruction. These are usually 2-byte instructions.

#### 3.6 Instruction Set

Refer to Table 3-2, which shows all the M68HC11 instructions in all possible addressing modes. For each instruction, the table shows the operand construction, the number of machine code bytes, and execution time in CPU E-clock cycles.

| Maamania   | Onevetion              | Decemention               | Addressing                                    |    | Ir                         | ıstru                      | ction |                       |   |   | Co | onditio | n Cod | les |   |   |

|------------|------------------------|---------------------------|-----------------------------------------------|----|----------------------------|----------------------------|-------|-----------------------|---|---|----|---------|-------|-----|---|---|

| Mnemonic   | Operation              | Description               | Mode                                          | Op | ocode                      | Op                         | erand | Cycles                | S | Х | Н  | I       | N     | Z   | ٧ | С |

| ABA        | Add<br>Accumulators    | $A + B \Rightarrow A$     | INH                                           |    | 1B                         |                            | _     | 2                     | _ | _ | Δ  | -       | Δ     | Δ   | Δ | Δ |

| ABX        | Add B to X             | IX + (00 : B) ⇒ IX        | INH                                           |    | 3A                         |                            | _     | 3                     | _ | _ | _  | _       | _     | _   | _ | _ |

| ABY        | Add B to Y             | IY + (00 : B) ⇒ IY        | INH                                           | 18 | ЗА                         |                            | _     | 4                     | _ | _ | _  | _       | _     | _   | _ | _ |

| ADCA (opr) | Add with Carry<br>to A | $A + M + C \Rightarrow A$ | A IMM<br>A DIR<br>A EXT<br>A IND,X<br>A IND,Y | 18 | 89<br>99<br>B9<br>A9<br>A9 | ii<br>dd<br>hh<br>ff<br>ff | 11    | 2<br>3<br>4<br>4<br>5 | _ |   | Δ  | _       | Δ     | Δ   | Δ | Δ |

| ADCB (opr) | Add with Carry<br>to B | $B + M + C \Rightarrow B$ | B IMM B DIR B EXT B IND,X B IND,Y             | 18 | C9<br>D9<br>F9<br>E9       | ii<br>dd<br>hh<br>ff<br>ff | 11    | 2<br>3<br>4<br>4<br>5 | _ |   | Δ  | _       | Δ     | Δ   | Δ | Δ |

| ADDA (opr) | Add Memory to<br>A     | $A + M \Rightarrow A$     | A IMM A DIR A EXT A IND,X A IND,Y             | 18 | 8B<br>9B<br>BB<br>AB<br>AB | ii<br>dd<br>hh<br>ff<br>ff | 11    | 2<br>3<br>4<br>4<br>5 | _ |   | Δ  | _       | Δ     | Δ   | Δ | Δ |

Table 3-2. Instruction Set (Sheet 1 of 8)

MC68HC711D3 Data Sheet, Rev. 2.1

# **Chapter 4 Resets, Interrupts, and Low-Power Modes**

### 4.1 Introduction

This section describes the internal and external resets and interrupts of the MC68HC711D3 and its two low power-consumption modes.

### 4.2 Resets

The microcontroller unit (MCU) can be reset in any of these four ways:

- 1. An active-low input to the  $\overline{RESET}$  pin

- 2. A power-on reset (POR) function

- 3. A clock monitor failure

- 4. A computer operating properly (COP) watchdog timer timeout

The RESET input consists mainly of a Schmitt trigger that senses the RESET line logic level.

#### 4.2.1 RESET Pin

To request an external reset, the RESET pin must be held low for at least eight E-clock cycles, or for one E-clock cycle if no distinction is needed between internal and external resets.

#### 4.2.2 Power-On Reset (POR)

Power-on reset occurs when a positive transition is detected on  $V_{DD}$ . This reset is used strictly for power turn on conditions and should not be used to detect any drop in the power supply voltage. If the external  $\overline{RESET}$  pin is low at the end of the power-on delay time, the processor remains in the reset condition until  $\overline{RESET}$  goes high.

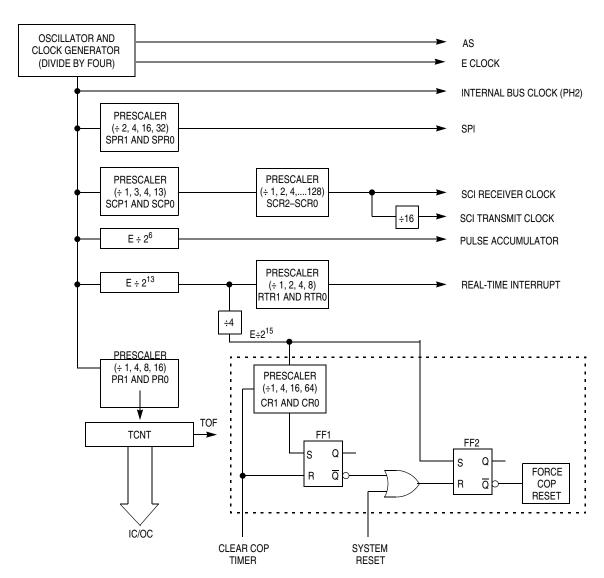

#### 4.2.3 Computer Operating Properly (COP) Reset

The MCU contains a watchdog timer that automatically times out unless it is serviced within a specific time by a program reset sequence. If the COP watchdog timer is allowed to timeout, a reset is generated, which drives the RESET pin low to reset the MCU and the external system.

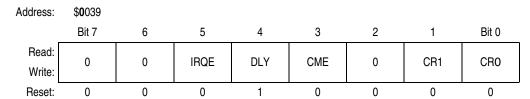

In the MC68HC711D3, the COP reset function is enabled out of reset in normal modes. If the user does not want the COP enabled, he must write a 1 to the NOCOP bit of the configuration control register (CONFIG) after reset. This bit is writable only once after reset in normal modes (see 2.3.3 Configuration Control Register for more information). Protected control bits (CR1 and CR0) in the configuration options register (OPTION) allow the user to select one of the four COP timeout rates. Table 4-1 shows the relationship between CR1 and CR0 and the COP timeout period for various system clock frequencies.

Figure 4-2. System Configuration Options Register (OPTION)

#### Bits 7, 6, and 2 — Not implemented

Always read 0.

#### IRQE — IRQ Edge/Level Sensitivity Select

This bit can be written only once during the first 64 E-clock cycles after reset in normal modes.

- $1 = \overline{IRQ}$  is configured to respond only to falling edges.

- $0 = \overline{IRQ}$  is configured for low-level wired-OR operation.