Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | HC11                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 2MHz                                                                     |

| Connectivity               | SCI, SPI                                                                 |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 26                                                                       |

| Program Memory Size        | 4KB (4K x 8)                                                             |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                |                                                                          |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            |                                                                          |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc711d3vfne2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **List of Chapters**

| Chapter 1 General Description                                 | 13  |

|---------------------------------------------------------------|-----|

| Chapter 2 Operating Modes and Memory                          | 21  |

| Chapter 3 Central Processor Unit (CPU)                        | 33  |

| Chapter 4 Resets, Interrupts, and Low-Power Modes             | 47  |

| Chapter 5 Input/Output (I/O) Ports                            | 61  |

| Chapter 6 Serial Communications Interface (SCI)               | 65  |

| Chapter 7 Serial Peripheral Interface (SPI)                   | 77  |

| Chapter 8 Programmable Timer                                  | 85  |

| Chapter 9 Electrical Characteristics                          | 105 |

| Chapter 10 Ordering Information and Mechanical Specifications | 121 |

| Appendix A MC68HC11D3 and MC68HC11D0                          | 125 |

| Appendix B MC68L11D0                                          | 131 |

#### **Table of Contents**

## Chapter 3 Central Processor Unit (CPU)

|         | ` ,                                                             |    |

|---------|-----------------------------------------------------------------|----|

| 3.1     | Introduction                                                    | 33 |

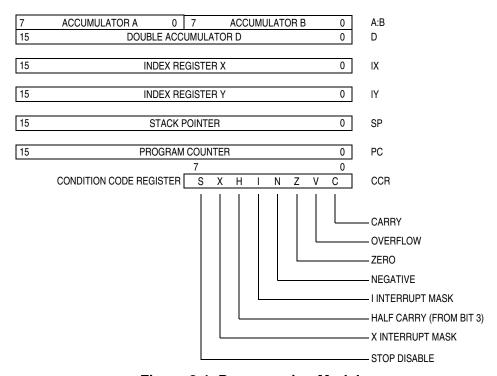

| 3.2     | CPU Registers                                                   | 33 |

| 3.2.1   | Accumulators A, B, and D                                        |    |

| 3.2.2   | Index Register X (IX)                                           | 34 |

| 3.2.3   | Index Register Y (IY)                                           | 34 |

| 3.2.4   | Stack Pointer (SP)                                              | 34 |

| 3.2.5   | Program Counter (PC)                                            |    |

| 3.2.6   | Condition Code Register (CCR)                                   | 36 |

| 3.2.6.1 | Carry/Borrow (C)                                                |    |

| 3.2.6.2 |                                                                 |    |

| 3.2.6.3 |                                                                 |    |

| 3.2.6.4 |                                                                 |    |

| 3.2.6.5 |                                                                 |    |

| 3.2.6.6 |                                                                 |    |

| 3.2.6.7 |                                                                 |    |

| 3.2.6.8 |                                                                 |    |

| 3.3     | Data Types                                                      | 37 |

| 3.4     | Opcodes and Operands                                            | 38 |

| 3.5     | Addressing Modes                                                |    |

| 3.5.1   | Immediate                                                       |    |

| 3.5.2   | Direct                                                          |    |

| 3.5.3   | Extended                                                        |    |

| 3.5.4   | Indexed                                                         | 39 |

| 3.5.5   | Inherent                                                        |    |

| 3.5.6   | Relative                                                        | 39 |

| 3.6     | Instruction Set                                                 | 39 |

|         |                                                                 |    |

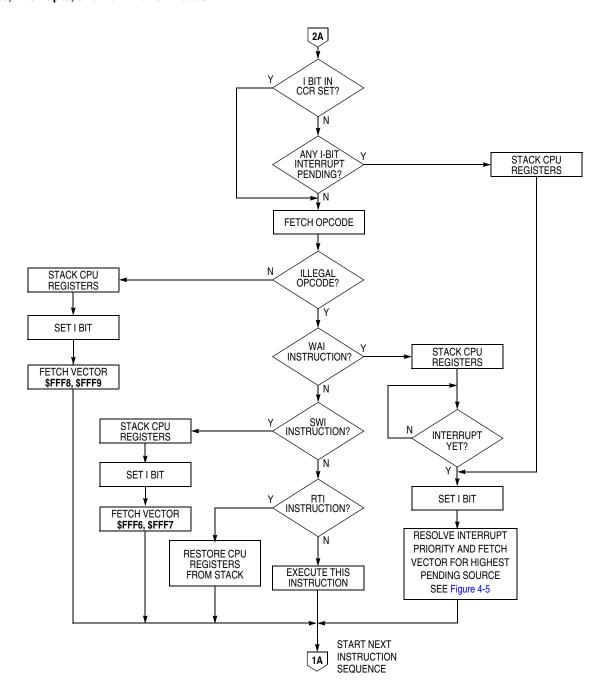

|         | Chapter 4                                                       |    |

|         | Resets, Interrupts, and Low-Power Modes                         |    |

| 4.1     | Introduction                                                    |    |

| 4.2     | Res <u>ets</u>                                                  |    |

| 4.2.1   | RESET Pin                                                       |    |

| 4.2.2   | Power-On Reset (POR)                                            | 47 |

| 4.2.3   | Computer Operating Properly (COP) Reset                         |    |

| 4.2.4   | Clock Monitor Reset                                             |    |

| 4.2.5   | System Configuration Options Register                           |    |

| 4.3     | Interrupts                                                      |    |

| 4.3.1   | Software Interrupt (SWI)                                        |    |

| 4.3.2   | Illegal Opcode Trap                                             |    |

| 4.3.3   | Real-Time Interrupt (RTI)                                       |    |

| 4.3.4   | Interrupt Mask Bits in the CCR                                  |    |

| 4.3.5   | Priority Structure                                              |    |

| 4.3.6   | Highest Priority I Interrupt and Miscellaneous Register (HPRIO) | 58 |

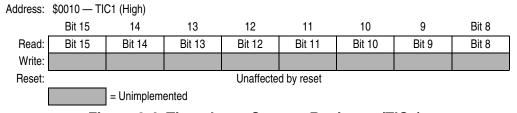

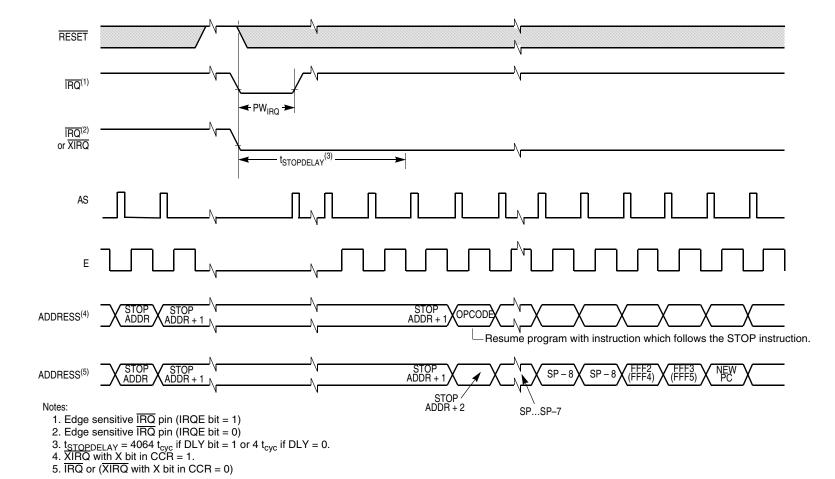

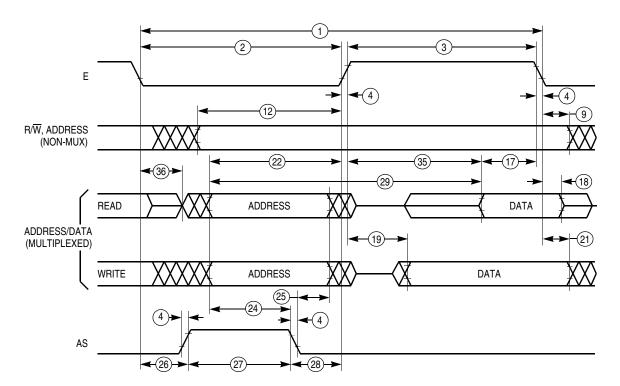

| 9.8            | Expansion Bus Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 115 |

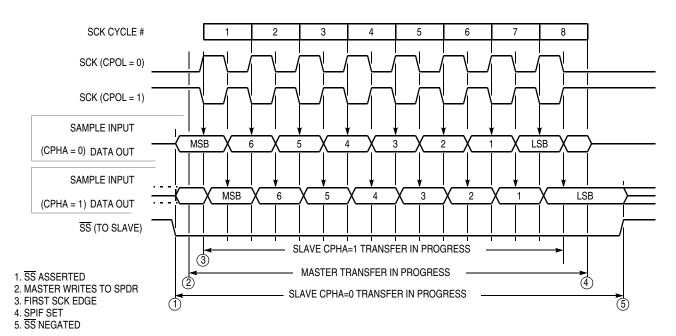

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 9.9            | Serial Peripheral Interface Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 117 |

|                | Chapter 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                | Ordering Information and Mechanical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 10.1           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 121 |

| 10.2           | Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 121 |

| 10.3           | 40-Pin DIP (Case 711-03)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 121 |

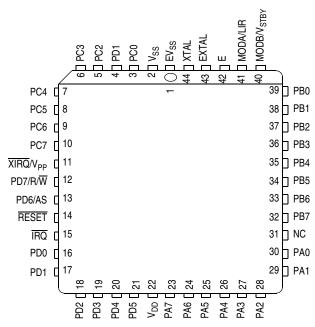

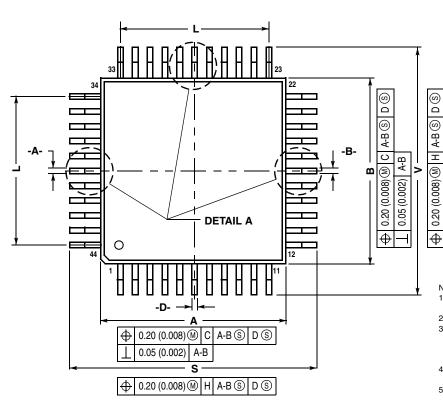

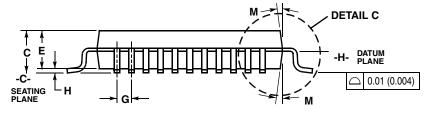

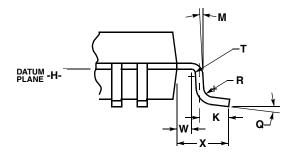

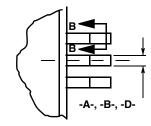

| 10.4           | 44-Pin PLCC (Case 777-02)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 122 |

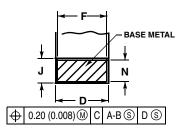

| 10.5           | 44-Pin QFP (Case 824A-01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 123 |

|                | Appendix A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                | MC68HC11D3 and MC68HC11D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| <b>A.1</b>     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 125 |

| A.2            | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 126 |

| A.3            | Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 127 |

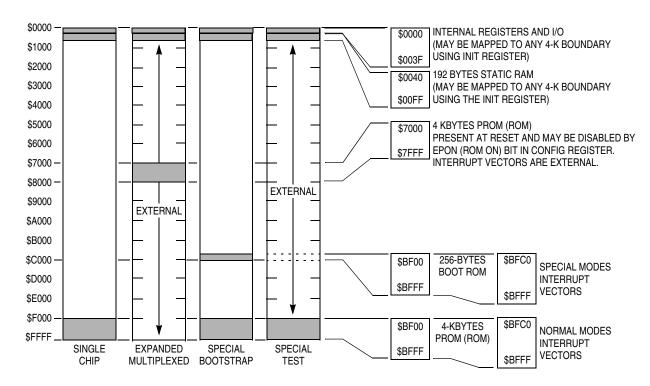

| A.4            | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 128 |

| A.5            | MC68HC11D3 and MC68HC11D0 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| A.5.1          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| A.5.2          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| A.6            | Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 129 |

|                | Appendix B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                | MC68L11D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| B.1            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| B.2            | MC68L11D0 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| B.2.1<br>B.2.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| B.2.3          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| B.2.4          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| B.2.5          | The state of the s |     |

| B.2.6          | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| B.3            | Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 136 |

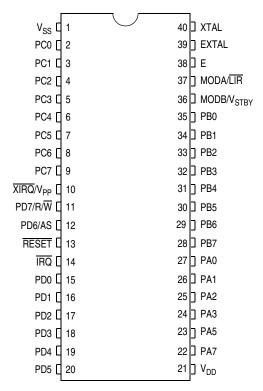

Figure 1-2. Pin Assignments for 40-Pin Plastic DIP

Figure 1-3. Pin Assignments for 44-Pin PLCC

#### **Operating Modes and Memory**

| MODB | MODA | Mode Selected                 |

|------|------|-------------------------------|

| 1    | 0    | Single-chip (mode 0)          |

| 1    | 1    | Expanded multiplexed (mode 1) |

| 0    | 0    | Special bootstrap             |

| 0    | 1    | Special test                  |

Figure 2-1. MC68HC711D3 Memory Map

#### **Operating Modes and Memory**

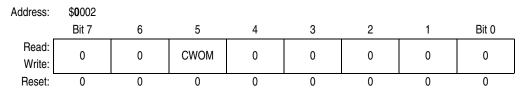

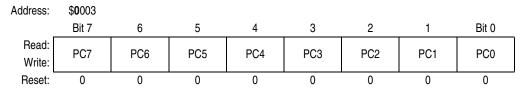

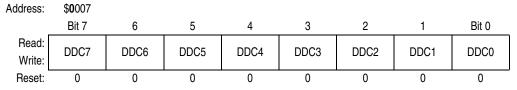

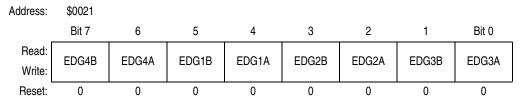

| Addr.                                   | Register Name                                     |                 | Bit 7 | 6          | 5      | 4         | 3          | 2     | 1           | Bit 0 |

|-----------------------------------------|---------------------------------------------------|-----------------|-------|------------|--------|-----------|------------|-------|-------------|-------|

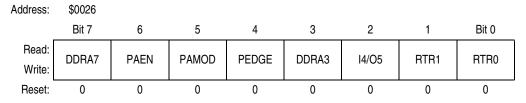

| \$ <b>0</b> 026                         | Pulse Accumulator Control<br>Register (PACTL)     | Read:<br>Write: | DDRA7 | PAEN       | PAMOD  | PEDGE     | DDRA3      | I4/O5 | RTR1        | RTR0  |

|                                         | See pages 99 and 102.                             | Reset:          | 0     | 0          | 0      | 0         | 0          | 0     | 0           | 0     |

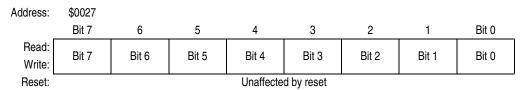

| \$ <b>0</b> 027                         | Pulse Accumulator Count Register (PACNT)          | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4     | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|                                         | See page 103.                                     | Reset:          |       |            |        | Unaffecte | d by reset |       |             |       |

| \$ <b>0</b> 028                         | SPI Control Register<br>(SPCR)                    | Read:<br>Write: | SPIE  | SPE        | DWOM   | MSTR      | CPOL       | СРНА  | SPR1        | SPR0  |

|                                         | See page 81.                                      | Reset:          | 0     | 0          | 0      | 0         | 0          | 1     | U           | U     |

| \$ <b>0</b> 029                         | SPI Status Register<br>(SPSR)                     | Read:<br>Write: | SPIF  | WCOL       | 0      | MODF      | 0          | 0     | 0           | 0     |

|                                         | See page 82.                                      | Reset:          | 0     | 0          | 0      | 0         | 0          | 0     | 0           | 0     |

| \$ <b>0</b> 02A                         | SPI Data I/O Register<br>(SPDR)                   | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4     | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|                                         | See page 83.                                      | Reset:          |       |            |        | Unaffecte | d by reset |       |             |       |

| \$ <b>0</b> 02B                         | Baud Rate Register<br>(BAUD)                      | Read:<br>Write: | TCLR  | 0          | SCP1   | SCP0      | RCKB       | SCR2  | SCR1        | SCR0  |

|                                         | See page 72.                                      | Reset:          | 0     | 0          | 0      | 0         | 0          | U     | U           | U     |

| \$ <b>0</b> 02C                         | SCI Control Register 1<br>(SCCR1)                 | Read:<br>Write: | R8    | Т8         | 0      | М         | WAKE       | 0     | 0           | 0     |

|                                         | See page 70.                                      | Reset:          | U     | U          | 0      | 0         | 0          | 0     | 0           | 0     |

| \$ <b>0</b> 02D                         | SCI Control Register 2<br>(SCCR2)                 | Read:<br>Write: | TIE   | TCIE       | RIE    | ILIE      | TE         | RE    | RWU         | SBK   |

|                                         | See page 70.                                      | Reset:          | 0     | 0          | 0      | 0         | 0          | 0     | 0           | 0     |

| \$ <b>0</b> 02E                         | SCI Status Register<br>(SCSR)<br>See page 71.     | Read:<br>Write: | TDRE  | TC         | RDRF   | IDLE      | OR         | NF    | FE          | 0     |

|                                         |                                                   | Reset:          | 1     | 1          | 0      | 0         | 0          | 0     | 0           | 0     |

| \$ <b>0</b> 02F                         | SCI Data Register<br>(SCDR)                       | Read:<br>Write: | R7/T7 | R6/T6      | R5/T5  | R4/T4     | R3/T3      | R2/T2 | R1/T1       | R0/T0 |

|                                         | See page 69. Res                                  |                 |       |            |        | Unaffecte | d by reset |       |             |       |

| \$ <b>0</b> 030<br>↓<br>\$ <b>0</b> 038 | Reserved                                          |                 | R     | R          | R      | R         | R          | R     | R           | R     |

| ,                                       |                                                   | ļ               |       |            |        |           |            |       |             |       |

| \$ <b>0</b> 039                         | System Configuration Options<br>Register (OPTION) | Read:<br>Write: | 0     | 0          | IRQE   | DLY       | CME        | 0     | CR1         | CR0   |

|                                         | See page 49.                                      | Reset:          | 0     | 0          | 0      | 1         | 0          | 0     | 0           | 0     |

|                                         |                                                   |                 |       | = Unimpler | mented | R         | = Reserved | d     | U = Unaffed | eted  |

Figure 2-2. Register and Control Bit Assignments (Sheet 4 of 5)

# **Chapter 3 Central Processor Unit (CPU)**

#### 3.1 Introduction

This section presents information on M68HC11 central processor unit (CPU):

- Architecture

- Data types

- Addressing modes

- Instruction set

- Special operations such as subroutine calls and interrupts

The CPU is designed to treat all peripheral, input/output (I/O), and memory locations identically as addresses in the 64-Kbyte memory map. This is referred to as memory-mapped I/O. I/O has no instructions separate from those used by memory. This architecture also allows accessing an operand from an external memory location with no execution time penalty.

## 3.2 CPU Registers

M68HC11 CPU registers are an integral part of the CPU and are not addressed as if they were memory locations. The seven registers, discussed in the following paragraphs, are shown in Figure 3-1.

Figure 3-1. Programming Model

MC68HC711D3 Data Sheet, Rev. 2.1

#### **Central Processor Unit (CPU)**

## Table 3-2. Instruction Set (Sheet 4 of 8)

|            | T                                |                                        | Addressing                          | li li                                     | nstruction                 |                       |   |   | Co | nditio | n Cod | es |   |   |

|------------|----------------------------------|----------------------------------------|-------------------------------------|-------------------------------------------|----------------------------|-----------------------|---|---|----|--------|-------|----|---|---|

| Mnemonic   | Operation                        | Description                            | Mode                                | Opcode                                    | Operand                    | Cycles                | S | Х | Н  | ı      | N     | Z  | ٧ | С |

| COMA       | Ones<br>Complement<br>A          | \$FF – A ⇒ A                           | A INH                               | 43                                        | _                          | 2                     | _ | _ | _  | _      | Δ     | Δ  | 0 | 1 |

| COMB       | Ones<br>Complement<br>B          | \$FF – B ⇒ B                           | B INH                               | 53                                        | _                          | 2                     | _ | _ | _  | -      | Δ     | Δ  | 0 | 1 |

| CPD (opr)  | Compare D to<br>Memory 16-Bit    | D – M : M + 1                          | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 1A 83<br>1A 93<br>1A B3<br>1A A3<br>CD A3 | jj kk<br>dd<br>hh 11<br>ff | 5<br>6<br>7<br>7<br>7 | _ | _ | _  | _      | Δ     | Δ  | Δ | Δ |

| CPX (opr)  | Compare X to<br>Memory 16-Bit    | IX – M : M + 1                         | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 8C<br>9C<br>BC<br>AC<br>CD AC             | jj kk<br>dd<br>hh 11<br>ff | 4<br>5<br>6<br>6<br>7 | _ | _ | _  | _      | Δ     | Δ  | Δ | Δ |

| CPY (opr)  | Compare Y to<br>Memory 16-Bit    | IY – M : M + 1                         | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18 8C<br>18 9C<br>18 BC<br>1A AC<br>18 AC | jj kk<br>dd<br>hh ll<br>ff | 5<br>6<br>7<br>7<br>7 | _ | _ | _  | _      | Δ     | Δ  | Δ | Δ |

| DAA        | Decimal Adjust<br>A              | Adjust Sum to BCD                      | INH                                 | 19                                        | _                          | 2                     | _ | - | _  | _      | Δ     | Δ  | Δ | Δ |

| DEC (opr)  | Decrement<br>Memory Byte         | $M-1 \Rightarrow M$                    | EXT<br>IND,X<br>IND,Y               | 7A<br>6A<br>18 6A                         | hh 11<br>ff<br>ff          | 6<br>6<br>7           | _ | _ | _  | _      | Δ     | Δ  | Δ | _ |

| DECA       | Decrement<br>Accumulator<br>A    | A − 1 ⇒ A                              | A INH                               | 4A                                        | _                          | 2                     | _ | _ | _  | _      | Δ     | Δ  | Δ | _ |

| DECB       | Decrement<br>Accumulator<br>B    | B − 1 ⇒ B                              | B INH                               | 5A                                        | _                          | 2                     | _ | _ | _  | _      | Δ     | Δ  | Δ | _ |

| DES        | Decrement<br>Stack Pointer       | SP − 1 ⇒ SP                            | INH                                 | 34                                        | _                          | 3                     | _ | _ | _  | _      | _     | _  | _ | _ |

| DEX        | Decrement<br>Index Register<br>X | $IX - 1 \Rightarrow IX$                | INH                                 | 09                                        | _                          | 3                     | _ | - | _  | _      | _     | Δ  | - | _ |

| DEY        | Decrement<br>Index Register<br>Y | IY − 1 ⇒ IY                            | INH                                 | 18 09                                     | _                          | 4                     | _ | _ | _  | _      | _     | Δ  | _ | _ |