Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC11                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 2MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 26                                                                      |

| Program Memory Size        | -                                                                       |

| Program Memory Type        | ROMIess                                                                 |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 192 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-QFP                                                                  |

| Supplier Device Package    | 44-QFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68l11d0cfbe2r |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **List of Chapters**

| Chapter 1 General Description                                 | 13  |

|---------------------------------------------------------------|-----|

| Chapter 2 Operating Modes and Memory                          | 21  |

| Chapter 3 Central Processor Unit (CPU)                        | 33  |

| Chapter 4 Resets, Interrupts, and Low-Power Modes             | 47  |

| Chapter 5 Input/Output (I/O) Ports                            | 61  |

| Chapter 6 Serial Communications Interface (SCI)               | 65  |

| Chapter 7 Serial Peripheral Interface (SPI)                   | 77  |

| Chapter 8 Programmable Timer                                  | 85  |

| Chapter 9 Electrical Characteristics                          | 105 |

| Chapter 10 Ordering Information and Mechanical Specifications | 121 |

| Appendix A MC68HC11D3 and MC68HC11D0                          | 125 |

| Appendix B MC68L11D0                                          | 131 |

|  |  |  | nts |

|--|--|--|-----|

|  |  |  |     |

|  |  |  |     |

| 7.5.3<br>7.5.4  | Serial Clock (SCK)                              |     |

|-----------------|-------------------------------------------------|-----|

| _               |                                                 |     |

| 7.6             | SPI System Errors                               |     |

| 7.7             | SPI Registers                                   |     |

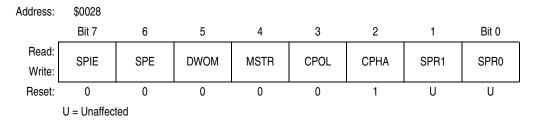

| 7.7.1           | SPI Control Register                            |     |

| 7.7.2           | SPI Status Register                             |     |

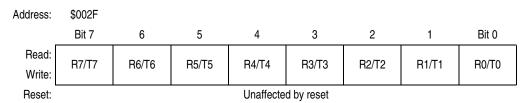

| 7.7.3           | SPI Data I/O Register                           | 83  |

|                 | Chapter 8 Programmable Timer                    |     |

| 8.1             | Introduction                                    | 85  |

| 8.2             | Timer Structure                                 | 87  |

| 8.3             | Input Capture                                   | 87  |

| 8.3.1           | Timer Control 2 Register                        |     |

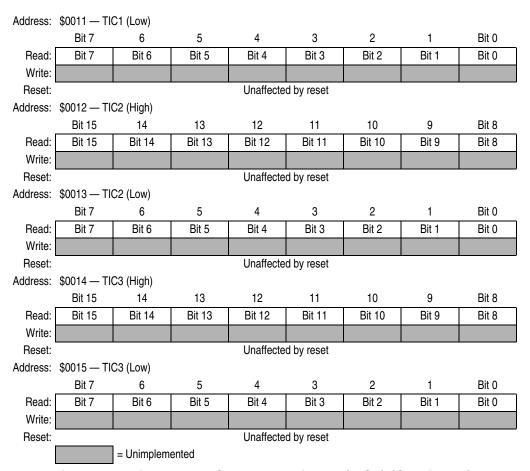

| 8.3.2           | Timer Input Capture Registers                   |     |

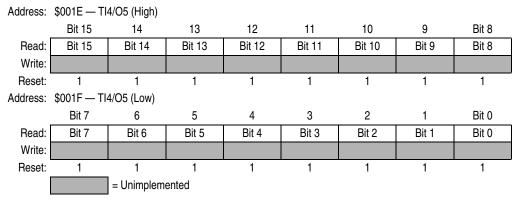

| 8.3.3           | Timer Input Capture 4/Output Compare 5 Register | 90  |

| 8.4             | Output Compare (OC)                             | 91  |

| 8.4.1           | Timer Output Compare Registers                  |     |

| 8.4.2           | Timer Compare Force Register                    | 93  |

| 8.4.3           | Output Compare 1 Mask Register                  | 93  |

| 8.4.4           | Output Compare 1 Data Register                  |     |

| 8.4.5           | Timer Counter Register                          |     |

| 8.4.6           | Timer Control 1 Register                        |     |

| 8.4.7           | Timer Interrupt Mask 1 Register                 |     |

| 8.4.8           | Timer Interrupt Flag 1 Register                 |     |

| 8.4.9<br>8.4.10 | Timer Interrupt Mask 2 Register                 |     |

|                 | Timer Interrupt Flag 2 Register                 |     |

| 8.5             | Real-Time Interrupt                             |     |

| 8.5.1<br>8.5.2  | Timer Interrupt Mask 2 Register                 |     |

| 8.5.3           | Timer Interrupt Flag 2 Register                 |     |

|                 | · · · · · · · · · · · · · · · · · · ·           |     |

| 8.6             | Computer Operating Properly Watchdog Function   |     |

| 8.7             | Pulse Accumulator                               |     |

| 8.7.1           | Pulse Accumulator Count Register                |     |

| 8.7.2<br>8.7.3  | Pulse Accumulator Count Register                |     |

| 0.7.3           | Fulse Accumulator Status and Interrupt bits     | 103 |

|                 | Chapter 9 Electrical Characteristics            |     |

| 9.1             | Introduction                                    | IOE |

| 9.2             |                                                 |     |

|                 | Maximum Ratings                                 |     |

| 9.3             | Functional Operating Temperature Range          |     |

| 9.4             | Thermal Characteristics                         |     |

| 9.5             | DC Electrical Characteristics                   |     |

| 9.6             | Control Timing                                  | 109 |

| 9.7             | Peripheral Port Timing                          | 114 |

MC68HC711D3 Data Sheet, Rev. 2.1

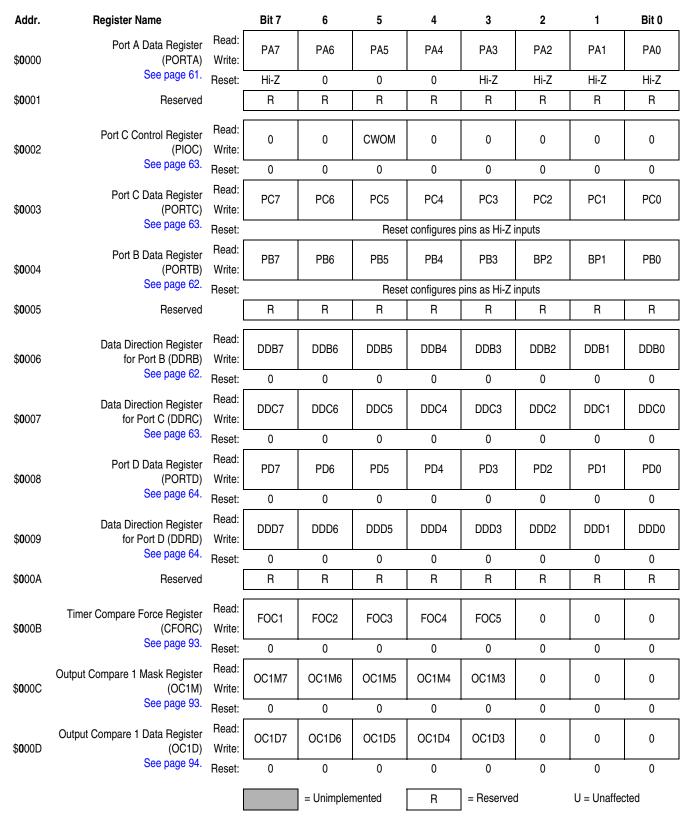

Figure 2-2. Register and Control Bit Assignments (Sheet 1 of 5)

MC68HC711D3 Data Sheet, Rev. 2.1

#### **Operating Modes and Memory**

RAM2–RAM0 (INIT bits 7–4) specify the starting address for the 192 bytes of static RAM. REG3–REG0 (INIT bits 3–0) specify the starting address for the control and status register block. In each case, the four RAM or REG bits become the four upper bits of the 16-bit address of the RAM or register. Since the INIT register is set to \$00 by reset, the internal registers begin at \$0000 and RAM begins at \$0040.

Throughout this document, control and status register addresses are displayed with the high-order digit shown as a bold **0**. This convention indicates that the register block may be relocated to any 4-K memory page, but that its default location is \$0000.

RAM and the control and status registers can be relocated independently. If the control and status registers are relocated in such a way as to conflict with PROM, then the register block takes priority, and the EPROM or OTPROM at those locations becomes inaccessible. No harmful conflicts result. Lower priority resources simply become inaccessible. Similarly, if an internal resource conflicts with an external device, no harmful conflict results, since data from the external device is not applied to the internal data bus. Thus, it cannot interfere with the internal read.

#### NOTE

There are unused register locations in the 64-byte control and status register block. Reads of these unused registers return data from the undriven internal data bus, not from another source that happens to be located at the same address.

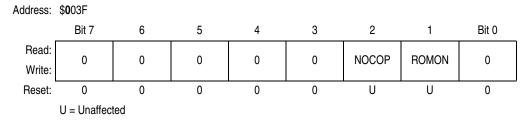

## 2.3.3 Configuration Control Register

The configuration control register (CONFIG) controls the presence of OTPROM or EPROM in the memory map and enables the computer operating properly (COP) watchdog system.

This register is writable only once in expanded and single-chip modes (SMOD = 0). In these mode, the COP watchdog timer is enabled out of reset. In all modes, except normal expanded, EPROM is enabled and located at \$F000–\$FFFF. In normal expanded mode, EPROM is enabled and located at \$7000–\$7FFF. Should the user wish to be in expanded mode, but with EPROM mapped at \$F000–\$FFFF, he must reset in single-chip mode, and write a 1 to the MDA bit in the HPRIO register.

Figure 2-4. Configuration Control Register (CONFIG)

#### Bits 7-3 and 0 — Not implemented

Always read 0.

#### NOCOP — Computer Operating Properly System Disable Bit

This bit is cleared out of reset in normal modes (single chip and expanded), enabling the COP system. It is writable only once after reset in these modes (SMOD = 0). In the special modes (test and bootstrap) (SMOD = 1), this bit comes out of reset set, and is writable any time.

1 = COP system is disabled.

0 = COP system is enabled, reset forced on timeout.

MC68HC711D3 Data Sheet, Rev. 2.1

#### **Central Processor Unit (CPU)**

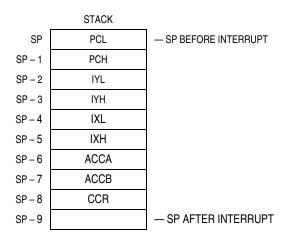

At the end of the interrupt service routine, a return-from interrupt (RTI) instruction is executed. The RTI instruction causes the saved registers to be pulled off the stack in reverse order. Program execution resumes at the return address.

Certain instructions push and pull the A and B accumulators and the X and Y index registers and are often used to preserve program context. For example, pushing accumulator A onto the stack when entering a subroutine that uses accumulator A and then pulling accumulator A off the stack just before leaving the subroutine ensures that the contents of a register will be the same after returning from the subroutine as it was before starting the subroutine.

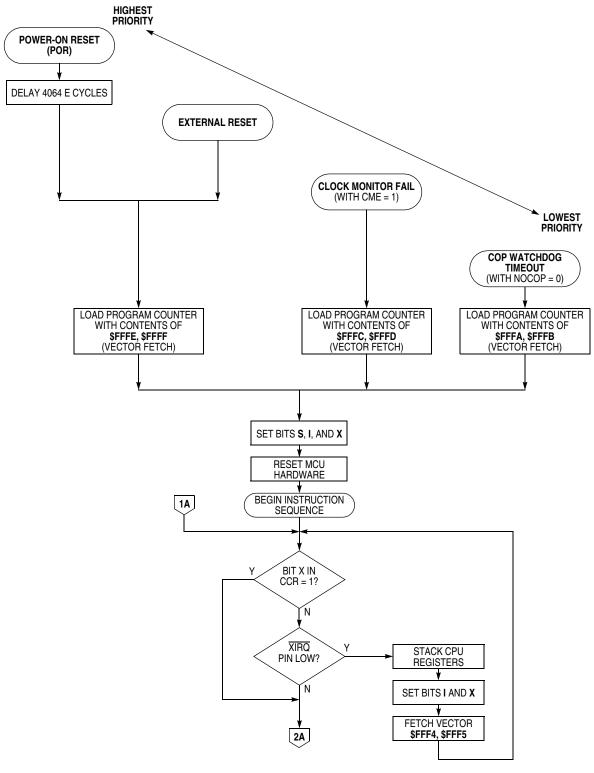

## 3.2.5 Program Counter (PC)

The program counter, a 16-bit register, contains the address of the next instruction to be executed. After reset, the program counter is initialized from one of six possible vectors, depending on operating mode and the cause of reset.

See Table 3-1.

| Mode         | POR or RESET Pin | Clock Monitor  | COP Watchdog   |

|--------------|------------------|----------------|----------------|

| Normal       | \$FFFE, \$FFFF   | \$FFFC, \$FFFD | \$FFFA, \$FFFB |

| Test or boot | \$BFFE, \$BFFF   | \$BFFC, \$FFFD | \$BFFA, \$FFFB |

**Table 3-1. Reset Vector Comparison**

## 3.2.6 Condition Code Register (CCR)

This 8-bit register contains:

- Five condition code indicators (C, V, Z, N, and H)

- Two interrupt masking bits (IRQ and XIRQ)

- One stop disable bit (S)

In the M68HC11 CPU, condition codes are updated automatically by most instructions. For example, load accumulator A (LDAA) and store accumulator A (STAA) instructions automatically set or clear the N, Z, and V condition code flags. Pushes, pulls, add B to X (ABX), add B to Y (ABY), and transfer/exchange instructions do not affect the condition codes. Refer to Table 3-2, which shows what condition codes are affected by a particular instruction.

#### 3.2.6.1 Carry/Borrow (C)

The C bit is set if the arithmetic logic unit (ALU) performs a carry or borrow during an arithmetic operation. The C bit also acts as an error flag for multiply and divide operations. Shift and rotate instructions operate with and through the carry bit to facilitate multiple-word shift operations.

#### 3.2.6.2 Overflow (V)

The overflow bit is set if an operation causes an arithmetic overflow. Otherwise, the V bit is cleared.

## 3.2.6.3 Zero (Z)

The Z bit is set if the result of an arithmetic, logic, or data manipulation operation is 0. Otherwise, the Z bit is cleared. Compare instructions do an internal implied subtraction and the condition codes, including Z, reflect the results of that subtraction. A few operations (INX, DEX, INY, and DEY) affect the Z bit and no other condition flags. For these operations, only = and  $\neq$  conditions can be determined.

#### MC68HC711D3 Data Sheet, Rev. 2.1

#### 3.5.3 Extended

In the extended addressing mode, the effective address of the argument is contained in two bytes following the opcode byte. These are 3-byte instructions (or 4-byte instructions if a prebyte is required). One or two bytes are needed for the opcode and two for the effective address.

#### 3.5.4 Indexed

In the indexed addressing mode, an 8-bit unsigned offset contained in the instruction is added to the value contained in an index register (IX or IY). The sum is the effective address. This addressing mode allows referencing any memory location in the 64-Kbyte address space. These are 2- to 5-byte instructions, depending on whether a prebyte is required.

#### 3.5.5 Inherent

In the inherent addressing mode, all the information necessary to execute the instruction is contained in the opcode. Operations that use only the index registers or accumulators, as well as control instructions with no arguments, are included in this addressing mode. These are 1- or 2-byte instructions.

#### 3.5.6 Relative

The relative addressing mode is used only for branch instructions. If the branch condition is true, an 8-bit signed offset included in the instruction is added to the contents of the program counter to form the effective branch address. Otherwise, control proceeds to the next instruction. These are usually 2-byte instructions.

## 3.6 Instruction Set

Refer to Table 3-2, which shows all the M68HC11 instructions in all possible addressing modes. For each instruction, the table shows the operand construction, the number of machine code bytes, and execution time in CPU E-clock cycles.

| Mnemonic           | Onevetion              | Decemention               | Addressing                                    |    | Ir                         | ıstru                      | ction |                       |   |   | Co | onditio | n Cod | les |   |   |

|--------------------|------------------------|---------------------------|-----------------------------------------------|----|----------------------------|----------------------------|-------|-----------------------|---|---|----|---------|-------|-----|---|---|

| Mnemonic Operation | willelilollic          | Description               | Mode                                          | Op | ocode                      | Op                         | erand | Cycles                | S | Х | Н  | I       | N     | Z   | ٧ | С |

| ABA                | Add<br>Accumulators    | $A + B \Rightarrow A$     | INH                                           |    | 1B                         |                            | _     | 2                     | _ | _ | Δ  | -       | Δ     | Δ   | Δ | Δ |

| ABX                | Add B to X             | IX + (00 : B) ⇒ IX        | INH                                           |    | 3A                         |                            | _     | 3                     | _ | _ | _  | _       | _     | _   | _ | _ |

| ABY                | Add B to Y             | IY + (00 : B) ⇒ IY        | INH                                           | 18 | ЗА                         |                            | _     | 4                     | _ | _ | _  | _       | _     | _   | _ | _ |

| ADCA (opr)         | Add with Carry<br>to A | $A + M + C \Rightarrow A$ | A IMM<br>A DIR<br>A EXT<br>A IND,X<br>A IND,Y | 18 | 89<br>99<br>B9<br>A9<br>A9 | ii<br>dd<br>hh<br>ff<br>ff | 11    | 2<br>3<br>4<br>4<br>5 | _ |   | Δ  | _       | Δ     | Δ   | Δ | Δ |

| ADCB (opr)         | Add with Carry<br>to B | $B + M + C \Rightarrow B$ | B IMM B DIR B EXT B IND,X B IND,Y             | 18 | C9<br>D9<br>F9<br>E9       | ii<br>dd<br>hh<br>ff<br>ff | 11    | 2<br>3<br>4<br>4<br>5 | _ |   | Δ  | _       | Δ     | Δ   | Δ | Δ |

| ADDA (opr)         | Add Memory to<br>A     | $A + M \Rightarrow A$     | A IMM A DIR A EXT A IND,X A IND,Y             | 18 | 8B<br>9B<br>BB<br>AB<br>AB | ii<br>dd<br>hh<br>ff<br>ff | 11    | 2<br>3<br>4<br>4<br>5 | _ |   | Δ  | _       | Δ     | Δ   | Δ | Δ |

Table 3-2. Instruction Set (Sheet 1 of 8)

MC68HC711D3 Data Sheet, Rev. 2.1

## Table 3-2. Instruction Set (Sheet 3 of 8)

|                              |                                   |                        | Addressing                                    |                               | Instruction                |                       |   |   | Co | nditio | n Coc | les |   |   |

|------------------------------|-----------------------------------|------------------------|-----------------------------------------------|-------------------------------|----------------------------|-----------------------|---|---|----|--------|-------|-----|---|---|

| Mnemonic                     | Operation                         | Description            | Mode                                          | Opcode                        | Operand                    | Cycles                | S | Х | Н  | 1      | N     | Z   | V | С |

| BITB (opr)                   | Bit(s) Test B<br>with Memory      | B • M                  | B IMM<br>B DIR<br>B EXT<br>B IND,X<br>B IND,Y | C5<br>D5<br>F5<br>E5<br>18 E5 | ii<br>dd<br>hh ll<br>ff    | 2<br>3<br>4<br>4<br>5 | _ | _ | _  | _      | Δ     | Δ   | 0 | _ |

| BLE (rel)                    | Branch if $\Delta$ Zero           | ? Z + (N ⊕ V) = 1      | REL                                           | 2F                            | rr                         | 3                     | _ | _ | _  | _      | _     | _   | _ | _ |

| BLO (rel)                    | Branch if Lower                   | ? C = 1                | REL                                           | 25                            | rr                         | 3                     | _ | _ | _  | _      | _     | _   | _ | _ |

| BLS (rel)                    | Branch if Lower or Same           | ? C + Z = 1            | REL                                           | 23                            | rr                         | 3                     | _ | _ | _  | _      | _     | _   | _ | _ |

| BLT (rel)                    | Branch if < Zero                  | ? N ⊕ V = 1            | REL                                           | 2D                            | rr                         | 3                     | _ | _ | _  | _      | _     | _   | _ | _ |

| BMI (rel)                    | Branch if Minus                   | ? N = 1                | REL                                           | 2B                            | rr                         | 3                     | _ | _ | _  | _      | _     | _   | _ | _ |

| BNE (rel)                    | Branch if not = Zero              | ? Z = 0                | REL                                           | 26                            | rr                         | 3                     | _ | _ | -  | -      | _     | _   | - | _ |

| BPL (rel)                    | Branch if Plus                    | ? N = 0                | REL                                           | 2A                            | rr                         | 3                     | _ | _ | _  | _      | _     | _   | _ | _ |

| BRA (rel)                    | Branch Always                     | ? 1 = 1                | REL                                           | 20                            | rr                         | 3                     | _ | _ | _  | _      | _     | _   | _ | _ |

| BRCLR(opr)<br>(msk)<br>(rel) | Branch if<br>Bit(s) Clear         | ? M • mm = 0           | DIR<br>IND,X<br>IND,Y                         | 13<br>1F<br>18 1F             | dd mm rr ff mm rr ff mm    | 6<br>7<br>8           | _ | _ | _  | _      | _     | _   | _ | _ |

| BRN (rel)                    | Branch Never                      | ? 1 = 0                | REL                                           | 21                            | rr                         | 3                     | _ | _ | _  | _      | _     | _   | _ |   |

| BRSET(opr)<br>(msk)<br>(rel) | Branch if Bit(s)<br>Set           | ? (M) • mm = 0         | DIR<br>IND,X<br>IND,Y                         | 12<br>1E<br>18 1E             | dd mm rr ff mm rr ff mm rr | 6<br>7<br>8           | _ | _ | _  | _      | _     | _   | _ | _ |

| BSET (opr)<br>(msk)          | Set Bit(s)                        | $M + mm \Rightarrow M$ | DIR<br>IND,X<br>IND,Y                         | 14<br>1C<br>18 1C             | dd mm<br>ff mm<br>ff mm    | 6<br>7<br>8           | _ | _ | _  | _      | Δ     | Δ   | 0 |   |

| BSR (rel)                    | Branch to<br>Subroutine           | See Figure 3-2         | REL                                           | 8D                            | rr                         | 6                     | _ | - | _  | _      | _     | _   | _ | _ |

| BVC (rel)                    | Branch if<br>Overflow Clear       | ? V = 0                | REL                                           | 28                            | rr                         | 3                     | _ | - | _  | -      | _     | -   | _ | _ |

| BVS (rel)                    | Branch if<br>Overflow Set         | ? V = 1                | REL                                           | 29                            | rr                         | 3                     | _ | - | _  | _      | _     | _   | _ | _ |

| CBA                          | Compare A to B                    | A – B                  | INH                                           | 11                            | _                          | 2                     | _ | _ | _  | _      | Δ     | Δ   | Δ | Δ |

| CLC                          | Clear Carry Bit                   | $0 \Rightarrow C$      | INH                                           | 0C                            | _                          | 2                     | _ | _ | _  | _      | _     | _   | _ | 0 |

| CLI                          | Clear Interrupt<br>Mask           | 0 ⇒ I                  | INH                                           | 0E                            | _                          | 2                     | _ | _ | _  | 0      | _     | _   | _ | _ |

| CLR (opr)                    | Clear Memory<br>Byte              | 0 ⇒ M                  | EXT<br>IND,X<br>IND,Y                         | 7F<br>6F<br>18 6F             | hh ll<br>ff<br>ff          | 6<br>6<br>7           | _ | _ | _  | _      | 0     | 1   | 0 | 0 |

| CLRA                         | Clear<br>Accumulator A            | $0\RightarrowA$        | A INH                                         | 4F                            | _                          | 2                     | _ | _ | _  | _      | 0     | 1   | 0 | 0 |

| CLRB                         | Clear<br>Accumulator B            | 0 ⇒ B                  | B INH                                         | 5F                            | _                          | 2                     | _ | _ | _  | _      | 0     | 1   | 0 | 0 |

| CLV                          | Clear Overflow<br>Flag            | 0 ⇒ V                  | INH                                           | 0A                            | _                          | 2                     | _ | - | _  | -      | _     | _   | 0 | _ |

| CMPA (opr)                   | Compare A to<br>Memory            | A – M                  | A IMM A DIR A EXT A IND,X A IND,Y             | 81<br>91<br>B1<br>A1<br>18 A1 | ii<br>dd<br>hh ll<br>ff    | 2<br>3<br>4<br>4<br>5 | _ | _ | _  | _      | Δ     | Δ   | Δ | Δ |

| CMPB (opr)                   | Compare B to<br>Memory            | B – M                  | B IMM B DIR B EXT B IND,X B IND,Y             | C1<br>D1<br>F1<br>E1<br>18 E1 | ii<br>dd<br>hh ll<br>ff    | 2<br>3<br>4<br>4<br>5 |   |   | _  | _      | Δ     | Δ   | Δ | Δ |

| COM (opr)                    | Ones<br>Complement<br>Memory Byte | \$FF − M ⇒ M           | EXT<br>IND,X<br>IND,Y                         | 73<br>63<br>18 63             | hh 11<br>ff<br>ff          | 6<br>6<br>7           | _ | _ | _  | _      | Δ     | Δ   | 0 | 1 |

MC68HC711D3 Data Sheet, Rev. 2.1

## Table 3-2. Instruction Set (Sheet 7 of 8)

|            |                               |                                        | Α                | ddressing                           |                      | Ir                         | stru                 | ction    |                       |   |          | Co | nditio | n Coc | les |   |   |

|------------|-------------------------------|----------------------------------------|------------------|-------------------------------------|----------------------|----------------------------|----------------------|----------|-----------------------|---|----------|----|--------|-------|-----|---|---|

| Mnemonic   | Operation                     | Description                            |                  | Mode                                | Op                   | ocode                      | Or                   | erand    | Cycles                | S | Х        | Н  | ı      | N     | Z   | ٧ | С |

| RTS        | Return from<br>Subroutine     | See Figure 3-2                         |                  | INH                                 |                      | 39                         |                      | _        | 5                     | _ | _        | _  | _      | _     | _   | _ | _ |

| SBA        | Subtract B from<br>A          | $A-B\RightarrowA$                      |                  | INH                                 |                      | 10                         |                      | _        | 2                     | _ | -        | -  | _      | Δ     | Δ   | Δ | Δ |

| SBCA (opr) | Subtract with<br>Carry from A | $A - M - C \Rightarrow A$              | A<br>A<br>A<br>A | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                   | 82<br>92<br>B2<br>A2<br>A2 | ii<br>dd<br>hh<br>ff | 11       | 2<br>3<br>4<br>4<br>5 | _ | _        | _  | _      | Δ     | Δ   | Δ | Δ |

| SBCB (opr) | Subtract with<br>Carry from B | $B-M-C\RightarrowB$                    | B<br>B<br>B<br>B | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                   | C2<br>D2<br>F2<br>E2<br>E2 | ii<br>dd<br>hh<br>ff | 11       | 2<br>3<br>4<br>4<br>5 | _ | _        | _  | _      | Δ     | Δ   | Δ | Δ |

| SEC        | Set Carry                     | 1 ⇒ C                                  |                  | INH                                 |                      | 0D                         |                      | _        | 2                     | _ | _        | _  | _      | _     | _   | _ | 1 |

| SEI        | Set Interrupt<br>Mask         | 1 ⇒ I                                  |                  | INH                                 |                      | 0F                         |                      | _        | 2                     | _ | _        | _  | 1      | _     | _   | _ | _ |

| SEV        | Set Overflow<br>Flag          | 1 ⇒ V                                  |                  | INH                                 |                      | 0B                         |                      | _        | 2                     | _ | _        | _  | _      | _     | _   | 1 | _ |

| STAA (opr) | Store<br>Accumulator<br>A     | $A\RightarrowM$                        | A<br>A<br>A      | DIR<br>EXT<br>IND,X<br>IND,Y        | 18                   | 97<br>B7<br>A7<br>A7       | dd<br>hh<br>ff<br>ff | 11       | 3<br>4<br>4<br>5      | _ | _        | _  | _      | Δ     | Δ   | 0 | _ |

| STAB (opr) | Store<br>Accumulator<br>B     | $B\RightarrowM$                        | B<br>B<br>B      | DIR<br>EXT<br>IND,X<br>IND,Y        | 18                   | D7<br>F7<br>E7<br>E7       | dd<br>hh<br>ff<br>ff | 11       | 3<br>4<br>4<br>5      | _ | _        | _  | _      | Δ     | Δ   | 0 | _ |

| STD (opr)  | Store<br>Accumulator<br>D     | $A \Rightarrow M, B \Rightarrow M + 1$ |                  | DIR<br>EXT<br>IND,X<br>IND,Y        | 18                   | DD<br>FD<br>ED<br>ED       | dd<br>hh<br>ff<br>ff | 11       | 4<br>5<br>5<br>6      | _ | _        | _  | _      | Δ     | Δ   | 0 | _ |

| STOP       | Stop Internal<br>Clocks       | _                                      |                  | INH                                 |                      | CF                         |                      | _        | 2                     | _ | -        | _  | -      | _     | _   | _ | _ |

| STS (opr)  | Store Stack<br>Pointer        | SP ⇒ M : M + 1                         |                  | DIR<br>EXT<br>IND,X<br>IND,Y        | 18                   | 9F<br>BF<br>AF<br>AF       | dd<br>hh<br>ff<br>ff | 11       | 4<br>5<br>5<br>6      | _ | _        | _  | _      | Δ     | Δ   | 0 | _ |

| STX (opr)  | Store Index<br>Register X     | $IX \Rightarrow M : M + 1$             |                  | DIR<br>EXT<br>IND,X<br>IND,Y        | CD                   | DF<br>FF<br>EF<br>EF       | dd<br>hh<br>ff       | 11       | 4<br>5<br>5<br>6      | _ | _        | _  | _      | Δ     | Δ   | 0 |   |

| STY (opr)  | Store Index<br>Register Y     | $IY \Rightarrow M : M + 1$             |                  | DIR<br>EXT<br>IND,X<br>IND,Y        | 18<br>18<br>1A<br>18 | DF<br>FF<br>EF<br>EF       | dd<br>hh<br>ff<br>ff | 11       | 5<br>6<br>6           | _ | _        | _  | _      | Δ     | Δ   | 0 | _ |

| SUBA (opr) | Subtract<br>Memory from<br>A  | $A-M\RightarrowA$                      | A<br>A<br>A<br>A | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                   | 80<br>90<br>B0<br>A0<br>A0 | ii<br>dd<br>hh<br>ff | 11       | 2<br>3<br>4<br>4<br>5 | _ | _        | _  | _      | Δ     | Δ   | Δ | Δ |

| SUBB (opr) | Subtract<br>Memory from<br>B  | $B-M\RightarrowB$                      | A<br>A<br>A<br>A | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                   | C0<br>D0<br>F0<br>E0<br>E0 | ii<br>dd<br>hh<br>ff | 11       | 2<br>3<br>4<br>4<br>5 | _ | _        | -  | -      | Δ     | Δ   | Δ | Δ |

| SUBD (opr) | Subtract<br>Memory from<br>D  | D − M : M + 1 ⇒ D                      |                  | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                   | 83<br>93<br>B3<br>A3<br>A3 | jj<br>dd<br>hh<br>ff | kk<br>11 | 4<br>5<br>6<br>6<br>7 | _ | _        | -  | -      | Δ     | Δ   | Δ | Δ |

| SWI        | Software<br>Interrupt         | See Figure 3-2                         |                  | INH                                 |                      | 3F                         |                      | _        | 14                    | _ | _        | _  | 1      | _     | _   | _ | _ |

| TAB        | Transfer A to B               | $A \Rightarrow B$                      |                  | INH                                 |                      | 16                         |                      | _        | 2                     | _ | _        | _  | _      | Δ     | Δ   | 0 | _ |

| TAP        | Transfer A to CC Register     | $A\RightarrowCCR$                      |                  | INH                                 |                      | 06                         |                      | _        | 2                     | Δ | <b>\</b> | Δ  | Δ      | Δ     | Δ   | Δ | Δ |

MC68HC711D3 Data Sheet, Rev. 2.1

Figure 4-3. Interrupt Stacking Order

## 4.3.1 Software Interrupt (SWI)

The SWI is executed the same as any other instruction and takes precedence over interrupts only if the other interrupts are masked (with I and X bits in the CCR set). SWI execution is similar to that of the maskable interrupts in that it sets the I bit, stacks the central processor unit (CPU) registers, etc.

#### NOTE

The SWI instruction cannot be executed as long as another interrupt is pending. However, once the SWI instruction has begun, no other interrupt can be honored until the first instruction in the SWI service routine is completed.

## 4.3.2 Illegal Opcode Trap

Since not all possible opcodes or opcode sequences are defined, an illegal opcode detection circuit has been included in the MCU. When an illegal opcode is detected, an interrupt is required to the illegal opcode vector. The illegal opcode vector should never be left uninitialized.

## 4.3.3 Real-Time Interrupt (RTI)

The real-time interrupt (RTI) provides a programmable periodic interrupt. This interrupt is maskable by either the I bit in the CCR or the RTI enable (RTII) bit of the timer interrupt mask register 2 (TMSK2). The rate is based on the MCU E clock and is software selectable to the E  $\div$  2<sup>13</sup>, E  $\div$  2<sup>14</sup>, E  $\div$  2<sup>15</sup>, or E  $\div$  2<sup>16</sup>. See PACTL, TMSK2, and TFLG2 register descriptions in Chapter 8 Programmable Timer for control and status bit information.

## 4.3.4 Interrupt Mask Bits in the CCR

Upon reset, both the X bit and I bit of the CCR are set to inhibit all maskable interrupts and XIRQ. After minimum system initialization, software may clear the X bit by a TAP instruction, thus enabling XIRQ interrupts. Thereafter software cannot set the X bit. So, an XIRQ interrupt is effectively a non-maskable interrupt. Since the operation of the I bit related interrupt structure has no effect on the X bit, the internal  $\overline{\text{XIRQ}}$  pin remains effectively non-masked. In the interrupt priority logic, the XIRQ interrupt is a higher priority than any source that is maskable by the I bit. All I bit related interrupts operate normally with their own priority relationship.

MC68HC711D3 Data Sheet, Rev. 2.1

Figure 4-4. Processing Flow Out of Reset (Sheet 1 of 2)

Serial Communications Interface (SCI)

## 6.5 Wakeup Feature

The wakeup feature reduces SCI service overhead in multiple receiver systems. Software for each receiver evaluates the first character of each message. The receiver is placed in wakeup mode by writing a 1 to the RWU bit in the SCCR2 register. While RWU is 1, all of the receiver-related status flags (RDRF, IDLE, OR, NF, and FE) are inhibited (cannot become set). Although RWU can be cleared by a software write to SCCR2, to do so would be unusual. Normally, RWU is set by software and is cleared automatically with hardware. Whenever a new message begins, logic alerts the sleeping receivers to wake up and evaluate the initial character of the new message.

Two methods of wakeup are available:

- Idle line wakeup

- Address mark wakeup

During idle line wakeup, a sleeping receiver awakens as soon as the RxD line becomes idle. In the address mark wakeup, logic 1 in the most significant bit (MSB) of a character wakes up all sleeping receivers.

## 6.5.1 Idle-Line Wakeup

To use the receiver wakeup method, establish a software addressing scheme to allow the transmitting devices to direct a message to individual receivers or to groups of receivers. This addressing scheme can take any form as long as all transmitting and receiving devices are programmed to understand the same scheme. Because the addressing information is usually the first frame(s) in a message, receivers that are not part of the current task do not become burdened with the entire set of addressing frames. All receivers are awake (RWU = 0) when each message begins. As soon as a receiver determines that the message is not intended for it, software sets the RWU bit (RWU = 1), which inhibits further flag setting until the RxD line goes idle at the end of the message. As soon as an idle line is detected by receiver logic, hardware automatically clears the RWU bit so that the first frame of the next message can be received. This type of receiver wakeup requires a minimum of one idle-line frame time between messages and no idle time between frames in a message.

#### 6.5.2 Address-Mark Wakeup

The serial characters in this type of wakeup consist of seven (eight if M = 1) information bits and an MSB, which indicates an address character (when set to 1 — mark). The first character of each message is an addressing character (MSB = 1). All receivers in the system evaluate this character to determine if the remainder of the message is directed toward this particular receiver. As soon as a receiver determines that a message is not intended for it, the receiver activates the RWU function by using a software write to set the RWU bit. Because setting RWU inhibits receiver-related flags, there is no further software overhead for the rest of this message. When the next message begins, its first character has its MSB set, which automatically clears the RWU bit and enables normal character reception. The first character whose MSB is set is also the first character to be received after wakeup because RWU gets cleared before the stop bit for that frame is serially received. This type of wakeup allows messages to include gaps of idle time, unlike the idle-line method, but there is a loss of efficiency because of the extra bit time for each character (address bit) required for all characters.

## 6.6 SCI Error Detection

Three error conditions can occur during generation of SCI system interrupts:

- Serial communications data register (SCDR) overrun

- · Received bit noise

- Framing

Three bits (OR, NF, and FE) in the serial communications status register (SCSR) indicate if one of these error conditions exists. The overrun error (OR) bit is set when the next byte is ready to be transferred from the receive shift register to the SCDR and the SCDR is already full (RDRF bit is set). When an overrun error occurs, the data that caused the overrun is lost and the data that was already in SCDR is not disturbed. The OR is cleared when the SCSR is read (with OR set), followed by a read of the SCDR.

The noise flag (NF) bit is set if there is noise on any of the received bits, including the start and stop bits. The NF bit is not set until the RDRF flag is set. The NF bit is cleared when the SCSR is read (with FE equal to 1) followed by a read of the SCDR.

When no stop bit is detected in the received data character, the framing error (FE) bit is set. FE is set at the same time as the RDRF. If the byte received causes both framing and overrun errors, the processor only recognizes the overrun error. The framing error flag inhibits further transfer of data into the SCDR until it is cleared. The FE bit is cleared when the SCSR is read (with FE equal to 1) followed by a read of the SCDR.

## 6.7 SCI Registers

This subsection describes the five addressable registers in the SCI.

## 6.7.1 SCI Data Register

The SCI data register (SCDR) is a parallel register that performs two functions. It is the receive data register when it is read, and the transmit data register when it is written. Reads access the receive data buffer and writes access the transmit data buffer. Receive and transmit are double buffered.

Figure 6-3. SCI Data Register (SCDR)

A write collision error occurs if the SPDR is written while a transfer is in progress. Because the SPDR is not double buffered in the transmit direction, writes to SPDR cause data to be written directly into the SPI shift register. Because this write corrupts any transfer in progress, a write collision error is generated. The transfer continues undisturbed, and the write data that caused the error is not written to the shifter.

A write collision is normally a slave error because a slave has no control over when a master initiates a transfer. A master knows when a transfer is in progress, so there is no reason for a master to generate a write-collision error, although the SPI logic can detect write collisions in both master and slave devices.

The SPI configuration determines the characteristics of a transfer in progress. For a master, a transfer begins when data is written to SPDR and ends when SPIF is set. For a slave with CPHA equal to zero, a transfer starts when  $\overline{SS}$  goes low and ends when  $\overline{SS}$  returns high. In this case, SPIF is set at the middle of the eighth SCK cycle when data is transferred from the shifter to the parallel data register, but the transfer is still in progress until  $\overline{SS}$  goes high. For a slave with CPHA equal to one, transfer begins when the SCK line goes to its active level, which is the edge at the beginning of the first SCK cycle. The transfer ends in a slave in which CPHA equals one when SPIF is set. For a slave, after a byte transfer, SCK must be in inactive state for at least 2 E-clock cycles before the next byte transfer begins.

## 7.7 SPI Registers

The three SPI registers, SPCR, SPSR, and SPDR, provide control, status, and data storage functions. This sub-section provides a description of how these registers are organized.

## 7.7.1 SPI Control Register

Figure 7-3. SPI Control Register (SPCR)

#### SPIE — Serial Peripheral Interrupt Enable Bit

0 = SPI interrupt disabled

1 = SPI interrupt enabled

## SPE — Serial Peripheral System Enable Bit

0 = SPI off

1 = SPI on

#### DWOM — Port D Wired-OR Mode Bit

DWOM affects all six port D pins.

0 = Normal CMOS outputs

1 = Open-drain outputs

#### MSTR — Master Mode Select Bit

0 = Slave mode

1 = Master mode

# **Chapter 8 Programmable Timer**

#### 8.1 Introduction

The M68HC11 timing system is composed of five clock divider chains. The main clock divider chain includes a 16-bit free-running counter, which is driven by a programmable prescaler. The main timer's programmable prescaler provides one of the four clocking rates to drive the 16-bit counter. Two prescaler control bits select the prescale rate.

The prescaler output divides the system clock by 1, 4, 8, or 16. Taps off of this main clocking chain drive circuitry that generates the slower clocks used by the pulse accumulator, the real-time interrupt (RTI), and the computer operating properly (COP) watchdog subsystems. Refer to Figure 8-1.

All main timer system activities are referenced to this free-running counter. The counter begins incrementing from \$0000 as the microcontroller unit (MCU) comes out of reset, and continues to the maximum count, \$FFFF. At the maximum count, the counter rolls over to \$0000, sets an overflow flag, and continues to increment. As long as the MCU is running in a normal operating mode, there is no way to reset, change, or interrupt the counting. The capture/compare subsystem features three input capture channels, four output compare channels, and one channel that can be selected to perform either input capture or output compare. Each of the three input capture functions has its own 16-bit input capture register (time capture latch) and each of the output compare functions has its own 16-bit compare register. All timer functions, including the timer overflow and RTI have their own interrupt controls and separate interrupt vectors.

The pulse accumulator contains an 8-bit counter and edge select logic. The pulse accumulator can operate in either event counting or gated time accumulation modes. During event counting mode, the pulse accumulator's 8-bit counter increments when a specified edge is detected on an input signal. During gated time accumulation mode, an internal clock source increments the 8-bit counter while an input signal has a predetermined logic level.

RTI is a programmable periodic interrupt circuit that permits pacing the execution of software routines by selecting one of four interrupt rates.

The COP watchdog clock input  $(E \div 2^{15})$  is tapped off of the free-running counter chain. The COP automatically times out unless it is serviced within a specific time by a program reset sequence. If the COP is allowed to time out, a reset is generated, which drives the  $\overline{RESET}$  pin low to reset the MCU and the external system. Refer to Table 8-1 for crystal related frequencies and periods.

#### **Programmable Timer**

Figure 8-4. Timer Input Capture Registers (TICx) (Continued)

## 8.3.3 Timer Input Capture 4/Output Compare 5 Register

Use timer input capture 4/output compare 5 (TI4/O5) as either an input capture register or an output compare register, depending on the function chosen for the I4/O5 pin. To enable it as an input capture pin, set the I4/O5 bit in the pulse accumulator control register (PACTL) to logic level 1. To use it as an output compare register, set the I4/O5 bit to a logic level 0. Refer to 8.7 Pulse Accumulator.

Figure 8-5. Timer Input Capture 4/Output Compare 5 Register (TI4/O5)

MC68HC711D3 Data Sheet, Rev. 2.1

91

## 8.4 Output Compare (OC)

Use the output compare (OC) function to program an action to occur at a specific time — when the 16-bit counter reaches a specified value. For each of the five output compare functions, there is a separate 16-bit compare register and a dedicated 16-bit comparator. The value in the compare register is compared to the value of the free-running counter on every bus cycle. When the compare register matches the counter value, an output compare status flag is set. The flag can be used to initiate the automatic actions for that output compare function.

To produce a pulse of a specific duration, write to the output compare register a value representing the time the leading edge of the pulse is to occur. The output compare circuit is configured to set the appropriate output either high or low, depending on the polarity of the pulse being produced. After a match occurs, the output compare register is reprogrammed to change the output pin back to its inactive level at the next match. A value representing the width of the pulse is added to the original value, and then is written to the output compare register. Because the pin state changes occur at specific values of the free-running counter, the pulse width can be controlled accurately at the resolution of the free-running counter, independent of software latencies. To generate an output signal of a specific frequency and duty cycle, repeat this pulse-generating procedure.

There are four 16-bit read/write output compare registers: TOC1, TOC2, TOC3, and TOC4, and the TI4/O5 register, which functions under software control as either IC4 or OC5. Each of the OC registers is set to \$FFFF on reset. A value written to an OC register is compared to the free-running counter value during each E-clock cycle. If a match is found, the particular output compare flag is set in timer interrupt flag register 1 (TFLG1). If that particular interrupt is enabled in the timer interrupt mask register 1 (TMSK1), an interrupt is generated. In addition to an interrupt, a specified action can be initiated at one or more timer output pins. For OC5–OC2, the pin action is controlled by pairs of bits (OMx and OLx) in the TCTL1 register. The output action is taken on each successful compare, regardless of whether the OCxF flag in the TFLG1 register was previously cleared.

OC1 is different from the other output compares in that a successful OC1 compare can affect any or all five of the OC pins. The OC1 output action taken when a match is found is controlled by two 8-bit registers with three bits unimplemented: the output compare 1 mask register, OC1M, and the output compare 1 data register, OC1D. OC1M specifies which port A outputs are to be used, and OC1D specifies what data is placed on these port pins.

## 8.4.1 Timer Output Compare Registers

All output compare registers are 16-bit read-write. Each is initialized to \$FFFF at reset. If an output compare register is not used for an output compare function, it can be used as a storage location. A write to the high-order byte of an output compare register pair inhibits the output compare function for one bus cycle. This inhibition prevents inappropriate subsequent comparisons. Coherency requires a complete 16-bit read or write. However, if coherency is not needed, byte accesses can be used.

For output compare functions, write a comparison value to output compare registers TOC1–TOC4 and TI4/O5. When TCNT value matches the comparison value, specified pin actions occur.

## **Chapter 9 Electrical Characteristics**

## 9.1 Introduction

This section contains electrical specifications.

## 9.2 Maximum Ratings

Maximum ratings are the extreme limits to which the microcontroller unit (MCU) can be exposed without permanently damaging it.

#### NOTE

This device is not guaranteed to operate properly at the maximum ratings. Refer to 9.5 DC Electrical Characteristics for guaranteed operating conditions.

| Rating                                                                               | Symbol           | Value        | Unit |

|--------------------------------------------------------------------------------------|------------------|--------------|------|

| Supply voltage                                                                       | $V_{DD}$         | -0.3 to +7.0 | V    |

| Input voltage                                                                        | V <sub>In</sub>  | -0.3 to +7.0 | V    |

| Current drain per $pin^{(1)}$ Excluding $V_{DD}$ , $V_{SS}$ , $V_{RH, and}$ $V_{RL}$ | I <sub>D</sub>   | 25           | mA   |

| Storage temperature                                                                  | T <sub>STG</sub> | -55 to +150  | °C   |

<sup>1.</sup> One pin at a time, observing maximum power dissipation limits

#### NOTE

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. For proper operation, it is recommended that  $V_{In}$  and  $V_{Out}$  be constrained to the range  $V_{SS} \leq (V_{In} \text{ or } V_{Out}) \leq V_{DD}$ . Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (for example, either  $V_{SS}$  or  $V_{DD}$ ).

#### **Electrical Characteristics**

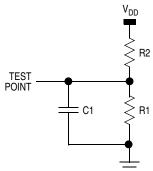

#### EQUIVALENT TEST LOAD(1)

| Pins                                               | R1     | R2     | C1     |

|----------------------------------------------------|--------|--------|--------|

| PA3-PA7<br>PB0-PB7<br>PC0-PC7<br>PD0, PD5-PD7<br>E | 3.26 K | 2.38 K | 90 pF  |

| PD1—PD4                                            | 3.26 K | 2.38 K | 200 pF |

Note:

1. Full test loads are applied during all ac electrical timing measurements.

Figure 9-1. Equivalent Test Load

#### Note:

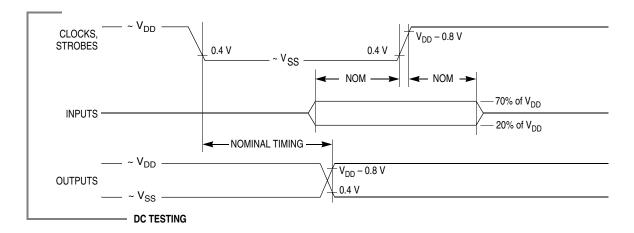

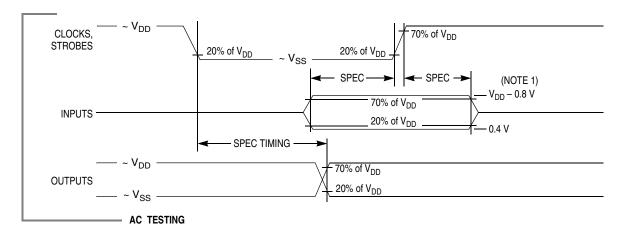

1. During ac timing measurements, inputs are driven to 0.4 volts and  $V_{DD}$  – 0.8 volts while timing measurements are taken at the 20% and 70% of  $V_{DD}$  points.

Figure 9-2. Test Methods

## MC68HC711D3 Data Sheet, Rev. 2.1

#### **Ordering Information and Mechanical Specifications**

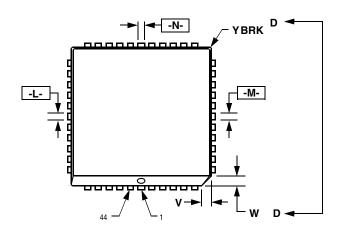

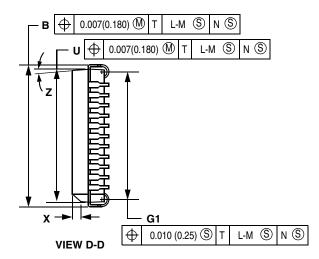

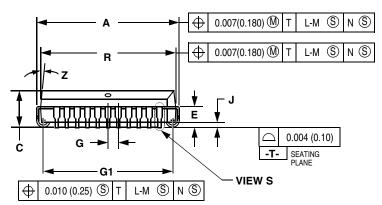

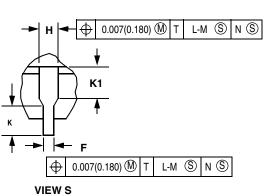

## 10.4 44-Pin PLCC (Case 777-02)

- NOTES: 1. DATUMS -L-, -M-, AND -N- ARE DETERMINED WHERE TOP OF LEAD SHOLDERS EXITS

- PLASTIC BODY AT MOLD PARTING LINE.

2. DIMENSION G1, TRUE POSITION TO BE MEASURED AT DATUM -T-, SEATING PLANE.

- 3. DIMENSION R AND U DO NOT INCLUDE MOLD FLASH. ALLOWABLE MOLD FLASH IS 0.010 (0.25) PER SIDE.

- 4. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 5. CONTROLLING DIMENSION: INCH.

- 6. THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM BY UP TO 0.012 (0.300). DIMENSIONS R AND U ARE DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF THE MOLD FLASH, TIE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

7. DIMINSION H DOES NOT INCLUDE DAMBAR

- PROTRUSION OR INTRUSION. THE DAMBAR PROTUSION(S) SHALL NOT CAUSE THE H DIMINSION TO BE GREATER THAN 0.037 (0.940124). THE DAMBAR INTRUSION(S) SHALL NOT CAUSE THE H DIMINISION TO SMALLER THAN 0.025 (0.635).

|     | INC   | HES   | MILLIN | METERS |

|-----|-------|-------|--------|--------|

| DIM | MIN   | MAX   | MIN    | MAX    |

| Α   | 0.685 | 0.695 | 17.40  | 17.65  |

| В   | 0.685 | 0.695 | 17.40  | 17.65  |

| С   | 0.165 | 0.180 | 4.20   | 4.57   |

| E   | 0.090 | 0.110 | 2.29   | 2.79   |

| F   | 0.013 | 0.019 | 0.33   | 0.48   |

| G   | 0.050 | BSC   | 1.27   | BSC    |

| Н   | 0.026 | 0.032 | 0.66   | 0.81   |

| J   | 0.020 | _     | 0.51   | _      |

| K   | 0.025 | ı     | 0.64   | -      |

| R   | 0.650 | 0.656 | 16.51  | 16.66  |

| U   | 0.650 | 0.656 | 16.51  | 16.66  |

| ٧   | 0.042 | 0.048 | 1.07   | 1.21   |

| W   | 0.042 | 0.048 | 1.07   | 1.21   |

| Х   | 0.042 | 0.056 | 1.07   | 1.42   |

| Υ   | ı     | 0.020 | 1      | 0.50   |

| Z   | 2°    | 10°   | 2°     | 10°    |

| G1  | 0.610 | 0.630 | 15.50  | 16.00  |

| K1  | 0.040 | _     | 1.02   | _      |