Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                       |                                                                                                          |

|-------------------------------|----------------------------------------------------------------------------------------------------------|

| Product Status                | Active                                                                                                   |

| Core Processor                | ARM® Cortex®-M4/M0                                                                                       |

| Core Size                     | 32-Bit Dual-Core                                                                                         |

| Speed                         | 204MHz                                                                                                   |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I²C, IrDA, Microwire, MMC/SD, QEI, SPI, SSI, SSP, UART/USART, USB, USB<br>OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                        |

| Number of I/O                 | 164                                                                                                      |

| Program Memory Size           | -                                                                                                        |

| Program Memory Type           | ROMIess                                                                                                  |

| EEPROM Size                   | -                                                                                                        |

| RAM Size                      | 282K x 8                                                                                                 |

| Voltage - Supply<br>(Vcc/Vdd) | 2.2V ~ 3.6V                                                                                              |

| Data Converters               | A/D 3x12b; D/A 1x10b                                                                                     |

| Oscillator Type               | Internal                                                                                                 |

| Operating Temperature         | -40°C ~ 85°C (TA)                                                                                        |

| Mounting Type                 | Surface Mount                                                                                            |

| Package / Case                | 256-LBGA                                                                                                 |

| Supplier Device Package       | 256-LBGA (17x17)                                                                                         |

| Purchase URL                  | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc43s70fet256e                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

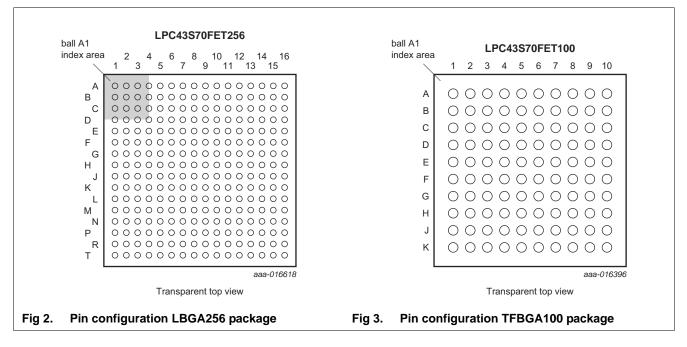

### 6. Pinning information

### 6.1 Pinning

### 6.2 Pin description

On the LPC43S70, digital pins are grouped into 16 ports, named P0 to P9 and PA to PF, with up to 20 pins used per port. Each digital pin can support up to eight different digital functions, including General Purpose I/O (GPIO), selectable through the System Configuration Unit (SCU) registers. The pin name is not indicative of the GPIO port assigned to it.

Not all functions listed in <u>Table 3</u> are available on all packages. See <u>Table 2</u> for availability of USB0, USB1, Ethernet, and LCD functions.

#### 32-bit ARM Cortex-M4/M0 microcontroller

|        | 0360,      | _        | 5011 |                    | is are | e not available on all parts. See <u>Table 2</u> .                                                                                            |

|--------|------------|----------|------|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol | LBGA256    | TFBGA100 |      | Reset state<br>[2] | Type   | Description                                                                                                                                   |

| P4_2   | <b>D</b> 3 | -        | [3]  | I; PU              |        | GPIO2[2] — General purpose digital input/output pin.                                                                                          |

|        |            |          |      |                    | 0      | <b>CTOUT_0</b> — SCT output 0. Match output 0 of timer 0.                                                                                     |

|        |            |          |      |                    | 0      | LCD_VD3 — LCD data.                                                                                                                           |

|        |            |          |      |                    | -      | R — Function reserved.                                                                                                                        |

|        |            |          |      |                    | -      | R — Function reserved.                                                                                                                        |

|        |            |          |      |                    | 0      | LCD_VD12 — LCD data.                                                                                                                          |

|        |            |          |      |                    | Ι      | U3_RXD — Receiver input for USART3.                                                                                                           |

|        |            |          |      |                    | I/O    | SGPIO8 — General purpose digital input/output pin.                                                                                            |

| P4_3   | C2         | -        | [6]  | I; PU              | I/O    | GPIO2[3] — General purpose digital input/output pin.                                                                                          |

|        |            |          | [13] |                    | 0      | CTOUT_3 — SCT output 3. Match output 3 of timer 0.                                                                                            |

|        |            |          |      |                    | 0      | LCD_VD2 — LCD data.                                                                                                                           |

|        |            |          |      |                    | -      | R — Function reserved.                                                                                                                        |

|        |            |          |      |                    | -      | R — Function reserved.                                                                                                                        |

|        |            |          |      |                    | 0      | LCD_VD21 — LCD data.                                                                                                                          |

|        |            |          |      |                    | I/O    | U3_BAUD — Baud pin for USART3.                                                                                                                |

|        |            |          |      |                    | I/O    | SGPIO9 — General purpose digital input/output pin.                                                                                            |

|        |            |          |      |                    | AI     | <b>ADC0_0</b> — ADC0, input channel 0. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |

| P4_4   | B1         | -        | [6]  | I; PU              | I/O    | GPIO2[4] — General purpose digital input/output pin.                                                                                          |

|        |            |          |      |                    | 0      | CTOUT_2 — SCT output 2. Match output 2 of timer 0.                                                                                            |

|        |            |          |      |                    | 0      | LCD_VD1 — LCD data.                                                                                                                           |

|        |            |          |      |                    | -      | R — Function reserved.                                                                                                                        |

|        |            |          |      |                    | -      | R — Function reserved.                                                                                                                        |

|        |            |          |      |                    | 0      | LCD_VD20 — LCD data.                                                                                                                          |

|        |            |          |      |                    | I/O    | U3_DIR — RS-485/EIA-485 output enable/direction control for USART3.                                                                           |

|        |            |          |      |                    | I/O    | SGPIO10 — General purpose digital input/output pin.                                                                                           |

|        |            |          |      |                    | 0      | <b>DAC</b> — DAC output. Configure the pin as GPIO input and use the analog function select register in the SCU to select the DAC.            |

| P4_5   | D2         | -        | [3]  | I; PU              | I/O    | GPIO2[5] — General purpose digital input/output pin.                                                                                          |

|        |            |          |      |                    | 0      | CTOUT_5 — SCT output 5. Match output 1 of timer 1.                                                                                            |

|        |            |          |      |                    | 0      | LCD_FP — Frame pulse (STN). Vertical synchronization pulse (TFT).                                                                             |

|        |            |          |      |                    | -      | R — Function reserved.                                                                                                                        |

|        |            |          |      |                    | -      | R — Function reserved.                                                                                                                        |

|        |            |          |      |                    | -      | R — Function reserved.                                                                                                                        |

|        |            |          |      |                    | -      | R — Function reserved.                                                                                                                        |

|        |            |          |      |                    | I/O    | SGPIO11 — General purpose digital input/output pin.                                                                                           |

|        |            |          |      |                    |        |                                                                                                                                               |

#### Table 3. Pin description ... continued

#### 32-bit ARM Cortex-M4/M0 microcontroller

| P6_3       P15 - II       I; PU       I/O       GPIO3[2] — General purpose digital input/output pin.         I       USB0_PWR_EN — VBUS drive signal (towards external ch power management unit); indicates that the VBUS signal m (active HIGH).         I/O       SGPIO4 — General purpose digital input/output pin.         O       EMC_CS1 — LOW active Chip Select 1 signal.         -       R — Function reserved.         I       T2_CAP2 — Capture input 2 of timer 2.         -       R — Function reserved.         -       R — Function reserved. |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <ul> <li>power management unit); indicates that the VBUS signal m (active HIGH).</li> <li>I/O SGPI04 — General purpose digital input/output pin.</li> <li>O EMC_CS1 — LOW active Chip Select 1 signal.</li> <li>R — Function reserved.</li> <li>I T2_CAP2 — Capture input 2 of timer 2.</li> <li>R — Function reserved.</li> <li>R — Function reserved.</li> <li>R — Function reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| <ul> <li>EMC_CS1 — LOW active Chip Select 1 signal.</li> <li>R — Function reserved.</li> <li>T2_CAP2 — Capture input 2 of timer 2.</li> <li>R — Function reserved.</li> <li>R — Function reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| <ul> <li>R — Function reserved.</li> <li>T2_CAP2 — Capture input 2 of timer 2.</li> <li>R — Function reserved.</li> <li>R — Function reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| <ul> <li>T2_CAP2 — Capture input 2 of timer 2.</li> <li>R — Function reserved.</li> <li>R — Function reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| <ul> <li>R — Function reserved.</li> <li>R — Function reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| - <b>R</b> — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| P6 4 R16 F6 3 I; PU I/O GPIO3I31 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| _ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| I <b>CTIN_6</b> — SCT input 6. Capture input 1 of timer 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| O <b>U0_TXD</b> — Transmitter output for USART0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| O <b>EMC_CAS</b> — LOW active SDRAM Column Address Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ). |

| - <b>R</b> — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| P6_5 P16 F9 [3] I; PU I/O <b>GPIO3[4]</b> — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| O <b>CTOUT_6</b> — SCT output 6. Match output 2 of timer 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| <b>U0_RXD</b> — Receiver input for USART0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| O <b>EMC_RAS</b> — LOW active SDRAM Row Address Strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| - <b>R</b> — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| P6_6 L14 - <u>I</u> I; PU <u>I/O</u> <b>GPIO0[5]</b> — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| O <b>EMC_BLS1</b> — LOW active Byte Lane select signal 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| I/O <b>SGPI05</b> — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| I <b>USB0_PWR_FAULT</b> — Port power fault signal indicating or<br>tion; this signal monitors over-current on the USB bus (exter<br>required to detect over-current condition).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| - <b>R</b> — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| I <b>T2_CAP3</b> — Capture input 3 of timer 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| - <b>R</b> — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| - <b>R</b> — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

#### Table 3. Pin description ... continued

#### 32-bit ARM Cortex-M4/M0 microcontroller

|      | LBGA256 | TFBGA100 |     | Reset state<br>[2] | Type | Description                                                 |

|------|---------|----------|-----|--------------------|------|-------------------------------------------------------------|

| PA_2 | K15     | -        | [4] | I; PU              |      | GPIO4[9] — General purpose digital input/output pin.        |

|      |         |          |     |                    | I    | QEI_PHB — Quadrature Encoder Interface PHB input.           |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | I    | U2_RXD — Receiver input for USART2.                         |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

| PA_3 | H11     | -        | [4] | I; PU              | I/O  | GPIO4[10] — General purpose digital input/output pin.       |

|      |         |          |     |                    | I    | QEI_PHA — Quadrature Encoder Interface PHA input.           |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

| PA_4 | G13     | -        | [3] | I; PU              | -    | R — Function reserved.                                      |

|      |         |          |     |                    | 0    | <b>CTOUT_9</b> — SCT output 9. Match output 1 of timer 2.   |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | I/O  | EMC_A23 — External memory address line 23.                  |

|      |         |          |     |                    | I/O  | GPIO5[19] — General purpose digital input/output pin.       |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

| PB_0 | B15     | -        | [3] | I; PU              | -    | R — Function reserved.                                      |

|      |         |          |     |                    | 0    | <b>CTOUT_10</b> — SCT output 10. Match output 2 of timer 2. |

|      |         |          |     |                    | 0    | LCD_VD23 — LCD data.                                        |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | I/O  | GPIO5[20] — General purpose digital input/output pin.       |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

|      |         |          |     |                    | -    | R — Function reserved.                                      |

#### Table 3. Pin description ... continued

#### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA100 |     | Reset state<br>[2] | Type | Description                                                                                                                                                      |

|--------|---------|----------|-----|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC_10  | M5      | -        | [3] | I; PU              | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |     |                    | 0    | <b>USB1_ULPI_STP</b> — ULPI link STP signal. Asserted to end or interrupt transfers to the PHY.                                                                  |

|        |         |          |     |                    | Ι    | U1_DSR — Data Set Ready input for UART 1.                                                                                                                        |

|        |         |          |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |     |                    | I/O  | GPIO6[9] — General purpose digital input/output pin.                                                                                                             |

|        |         |          |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |     |                    | 0    | T3_MAT3 — Match output 3 of timer 3.                                                                                                                             |

|        |         |          |     |                    | I/O  | SD_CMD — SD/MMC command signal.                                                                                                                                  |

| PC_11  | L5      | -        | [3] | I; PU              | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |     |                    | I    | <b>USB1_ULPI_DIR</b> — ULPI link DIR signal. Controls the ULPI data line direction.                                                                              |

|        |         |          |     |                    | I    | U1_DCD — Data Carrier Detect input for UART 1.                                                                                                                   |

|        |         |          |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |     |                    | I/O  | GPIO6[10] — General purpose digital input/output pin.                                                                                                            |

|        |         |          |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |     |                    | I/O  | SD_DAT4 — SD/MMC data bus line 4.                                                                                                                                |

| PC_12  | L6      | -        | [3] | I; PU              | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |     |                    | 0    | <b>U1_DTR</b> — Data Terminal Ready output for UART 1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART 1.                           |

|        |         |          |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |     |                    | I/O  | GPIO6[11] — General purpose digital input/output pin.                                                                                                            |

|        |         |          |     |                    | I/O  | SGPI011 — General purpose digital input/output pin.                                                                                                              |

|        |         |          |     |                    | I/O  | <b>I2S0_TX_SDA</b> — I2S transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $l^2S$ -bus specification. |

|        |         |          |     |                    | I/O  | SD_DAT5 — SD/MMC data bus line 5.                                                                                                                                |

| PC_13  | M1      | -        | [3] | I; PU              | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |     |                    | 0    | U1_TXD — Transmitter output for UART 1.                                                                                                                          |

|        |         |          |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |     |                    | I/O  | GPIO6[12] — General purpose digital input/output pin.                                                                                                            |

|        |         |          |     |                    | I/O  | SGPI012 — General purpose digital input/output pin.                                                                                                              |

|        |         |          |     |                    | I/O  | <b>I2S0_TX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $l^2S$ -bus specification.   |

|        |         |          |     |                    | I/O  | <b>SD_DAT6</b> — SD/MMC data bus line 6.                                                                                                                         |

#### Table 3. Pin description ...continued

LCD. Ethernet. USB0. and USB1 functions are not available on all parts. See Table 2

#### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol      | LBGA256                                                                                     | TFBGA100                              | Reset state<br>[2] | Type | Description                                                                                                                        |

|-------------|---------------------------------------------------------------------------------------------|---------------------------------------|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------|

| VDDIO       | D7,<br>E12,<br>F7,<br>F8,<br>G10,<br>H10,<br>J6,<br>J7,<br>K7,<br>L9,<br>L10,<br>N7,<br>N13 | F10,<br>K5                            | -                  | -    | I/O power supply. Tie the VDDREG and VDDIO pins to a common power supply to ensure the same ramp-up time for both supply voltages. |

| VDD         | -                                                                                           | -                                     |                    |      | Power supply for main regulator, I/O, and OTP.                                                                                     |

| VSS         | G9,<br>H7,<br>J10,<br>J11,<br>K8                                                            | -                                     | -                  | -    | Ground.                                                                                                                            |

| VSSIO       | C4,<br>D13,<br>G6,<br>G7,<br>G8,<br>H8,<br>H9,<br>J8,<br>J9,<br>K10,<br>M13,<br>P7,<br>P13  | C8,<br>D4,<br>D5,<br>G8,<br>J3,<br>J6 | -                  | -    | Ground.                                                                                                                            |

| VSSA        | B2                                                                                          | C2                                    | -                  | -    | Analog ground.                                                                                                                     |

| Not connect | ted                                                                                         |                                       |                    |      |                                                                                                                                    |

| -           | B9                                                                                          | -                                     | -                  | -    | n.c.                                                                                                                               |

### Table 3. Pin description ...continued I CD. Ethernet. USB0, and USB1 functions are not available on all parts. See Table 2

[1] - = not pinned out.

[2] I = input, O = output, AI/O analog input/output, IA = inactive; PU = pull-up enabled (weak pull-up resistor pulls up pin to V<sub>DD(IO)</sub>); F = floating. Reset state reflects the pin state at reset without boot code operation.

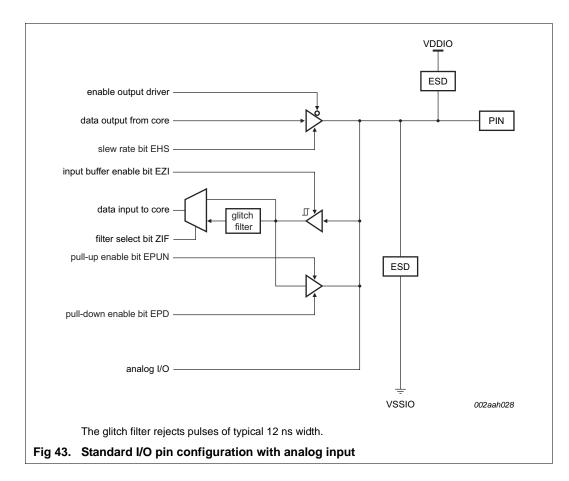

[3] 5 V tolerant pad with 15 ns glitch filter (5 V tolerant if V<sub>DD(IO)</sub> present; if V<sub>DD(IO)</sub> not present, do not exceed 3.3 V); provides digital I/O functions with TTL levels and hysteresis; normal drive strength.

[4] 5 V tolerant pad with 15 ns glitch filter (5 V tolerant if V<sub>DD(IO)</sub> present; if V<sub>DD(IO)</sub> not present, do not exceed 3.3 V) providing digital I/O functions with TTL levels, and hysteresis; high drive strength.

[5] 5 V tolerant pad with 15 ns glitch filter (5 V tolerant if V<sub>DD(IO)</sub> present; if V<sub>DD(IO)</sub> not present, do not exceed 3.3 V) providing high-speed digital I/O functions with TTL levels and hysteresis.

#### **NXP Semiconductors**

# LPC43S70

#### 32-bit ARM Cortex-M4/M0 microcontroller

- [6] 5 V tolerant pad providing digital I/O functions (with TTL levels and hysteresis) and analog input or output (5 V tolerant if V<sub>DD(IO)</sub> present; if V<sub>DD(IO)</sub> not present, do not exceed 3.3 V). When configured as a ADC input or DAC output, the pin is not 5 V tolerant and the digital section of the pad must be disabled by setting the pin to an input function and disabling the pull-up resistor through the pin's SFSP register.

- [7] 5 V tolerant transparent analog pad.

- [8] For maximum load  $C_L = 6.5 \,\mu$ F and maximum resistance  $R_{pd} = 80 \,k\Omega$ , the VBUS signal takes about 2 s to fall from VBUS = 5 V to VBUS = 0.2 V when it is no longer driven.

- [9] Transparent analog pad. Not 5 V tolerant.

- [10] Pad provides USB functions (5 V tolerant if V<sub>DD(IO)</sub> present; if V<sub>DD(IO)</sub> not present, do not exceed 3.3 V). It is designed in accordance with the USB specification, revision 2.0 (Full-speed and Low-speed mode only).

- [11] Open-drain 5 V tolerant digital I/O pad, compatible with I<sup>2</sup>C-bus Fast Mode Plus specification. This pad requires an external pull-up to provide output functionality. When power is switched off, this pin connected to the I<sup>2</sup>C-bus is floating and does not disturb the I<sup>2</sup>C lines.

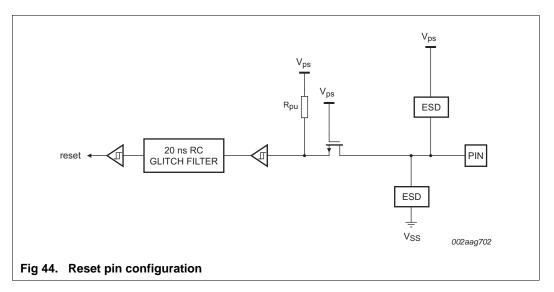

- [12] 5 V tolerant pad with 20 ns glitch filter; provides digital I/O functions with open-drain output with weak pull-up resistor and hysteresis.

- [13] To minimize interference on the 12-bit ADC signal lines, do not configure the digital signal as output when using the 12-bit ADC. See <u>Table 45</u>.

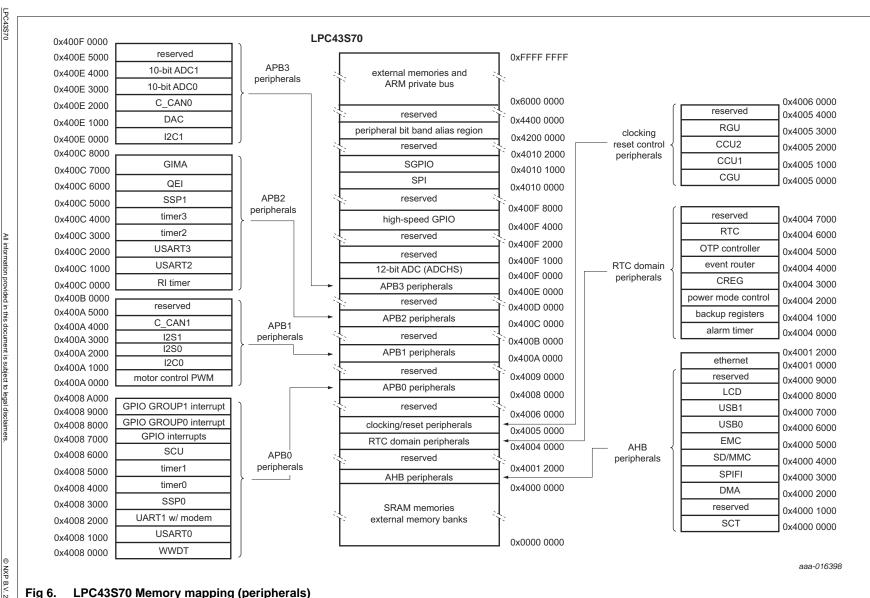

### 7. Functional description

#### 7.1 Architectural overview

The ARM Cortex-M4 includes three AHB-Lite buses: the system bus, the I-code bus, and the D-code bus. The I-code and D-code core buses allow for concurrent code and data accesses from different slave ports.

The LPC43S70 use a multi-layer AHB matrix to connect the ARM Cortex-M4 buses and other bus masters to peripherals in a flexible manner that optimizes performance by allowing peripherals that are on different slaves ports of the matrix to be accessed simultaneously by different bus masters.

An ARM Cortex-M0 coprocessor is included in the LPC43S70, capable of off-loading the main ARM Cortex-M4 application processor. Most peripheral interrupts are connected to both processors. The processors communicate with each other via an interprocessor communication protocol.

### 7.2 ARM Cortex-M4 processor

The ARM Cortex-M4 CPU incorporates a 3-stage pipeline, uses a Harvard architecture with separate local instruction and data buses as well as a third bus for peripherals, and includes an internal prefetch unit that supports speculative branching. The ARM Cortex-M4 supports single-cycle digital signal processing and SIMD instructions. A hardware floating-point processor is integrated in the core. The processor includes a NVIC with up to 53 interrupts.

### 7.3 ARM Cortex-M0 processors

The ARM Cortex-M0 processors are general purpose, 32-bit microprocessors, which offer high performance and very low power consumption. The ARM Cortex-M0 processor uses a 3-stage pipeline von Neumann architecture and a small but powerful instruction set providing high-end processing hardware. The processors each incorporate an NVIC with 32 interrupts.

#### 7.3.1 ARM Cortex-M0 coprocessor

The M0 coprocessor resides on the same AHB multi-layer matrix as the main Cortex-M0 core. The coprocessor can be used to off-load multiple tasks from the main Cortex-M4 processor.

#### 7.3.2 ARM Cortex-M0 subsytem

The Cortex-M0 subsystem can be used to manage the SGPIO and SPI peripherals on the M0 subsystem multilayer matrix but any other peripheral as well. The M0 subsystem is separated by a bridge from the main AHB matrix. The M0 subsystem AHB matrix has two SRAM blocks which allows to run the Cortex-M0 subsystem at full speed independently from the main matrix.

One application of using the subsystem is to reduce power, for example when the main matrix runs at a very low speed and the M0 subsystem monitors activity and increases the main matrix speed when needed.

Product data sheet

information provided in this document is subject to legal disciain Rev. 1.2 — 15 March 2016

LPC43S70 Cortex-M4/M0 microcontroller

32-bit ARM

- Up to four external outputs corresponding to match registers, with the following capabilities:

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

- Up to two match registers can be used to generate timed DMA requests.

#### 7.19.2 Motor control PWM

The motor control PWM is a specialized PWM supporting 3-phase motors and other combinations. Feedback inputs are provided to automatically sense rotor position and use that information to ramp speed up or down. An abort input is also provided that causes the PWM to immediately release all motor drive outputs. At the same time, the motor control PWM is highly configurable for other generalized timing, counting, capture, and compare applications.

#### 7.19.3 Quadrature Encoder Interface (QEI)

A quadrature encoder, also known as a 2-channel incremental encoder, converts angular displacement into two pulse signals. By monitoring both the number of pulses and the relative phase of the two signals, the user can track the position, direction of rotation, and velocity. In addition, a third channel, or index signal, can be used to reset the position counter. The quadrature encoder interface decodes the digital pulses from a quadrature encoder wheel to integrate position over time and determine direction of rotation. In addition, the QEI can capture the velocity of the encoder wheel.

#### 7.19.3.1 Features

- Tracks encoder position.

- Increments/decrements depending on direction.

- Programmable for 2× or 4× position counting.

- Velocity capture using built-in timer.

- Velocity compare function with "less than" interrupt.

- Uses 32-bit registers for position and velocity.

- Three position compare registers with interrupts.

- Index counter for revolution counting.

- Index compare register with interrupts.

- Can combine index and position interrupts to produce an interrupt for whole and partial revolution displacement.

- Digital filter with programmable delays for encoder input signals.

- Can accept decoded signal inputs (clk and direction).

- Measurement range of 0 V to 1.2 V.

- 12-bit conversion rate of 80 MSamples/s.

- Conversion on transition on input pin or various internal signals.

- Output FIFO with DMA support.

#### 7.20.2 10-bit Analog-to-Digital Converter (ADC0/1)

#### 7.20.2.1 Features

- 10-bit successive approximation analog to digital converter.

- Input multiplexing among 8 pins per ADC for a total of 16 individual channels.

- Power-down mode.

- Measurement range 0 to VDDA.

- Sampling frequency up to 400 kSamples/s.

- Burst conversion mode for single or multiple inputs.

- Optional conversion on transition on ADCTRIG0 or ADCTRIG1 pins, combined timer outputs 8 or 15, or the PWM output MCOA2.

- Individual result registers for each A/D channel to reduce interrupt overhead.

- DMA support.

#### 7.20.3 Digital-to-Analog Converter (DAC)

#### 7.20.3.1 Features

- 10-bit resolution

- Monotonic by design (resistor string architecture)

- Controllable conversion speed

- Low power consumption

### 7.21 Peripherals in the RTC power domain

#### 7.21.1 RTC

The Real Time Clock (RTC) is a set of counters for measuring time when system power is on, and optionally when it is off. It uses very little power when its registers are not being accessed by the CPU, especially reduced power modes. The RTC is clocked by a separate 32 kHz oscillator that produces a 1 Hz internal time reference. The RTC is powered by its own power supply pin, VBAT.

#### 7.21.1.1 Features

- Measures the passage of time to maintain a calendar and clock. Provides seconds, minutes, hours, day of month, month, year, day of week, and day of year.

- Ultra-low power design to support battery powered systems. Uses power from the CPU power supply when it is present.

- Dedicated battery power supply pin.

- RTC power supply is isolated from the rest of the chip.

- Calibration counter allows adjustment to better than  $\pm 1$  sec/day with 1 sec resolution.

LPC43S70

© NXP B.V. 2016. All rights reserved.

#### 32-bit ARM Cortex-M4/M0 microcontroller

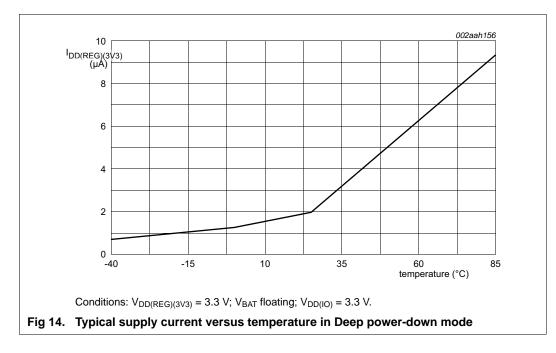

### Table 10. Static characteristics ...continued

$T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ , unless otherwise specified.

| Symbol                | Parameter                                                      | Conditions                                                                                                                                                                                                                                        |      | Min                                                        | Typ <u>[1]</u>        | Max                         | Uni         |

|-----------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------|-----------------------|-----------------------------|-------------|

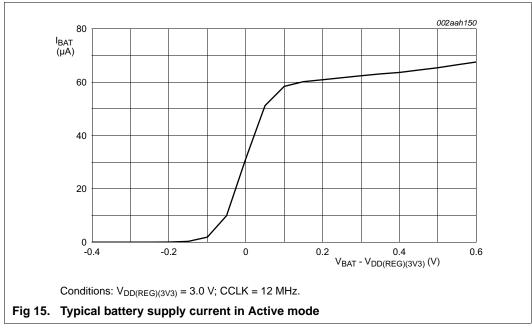

| BAT                   | battery supply current                                         | V <sub>DD(REG)(3V3)</sub> = 3.3 V;<br>V <sub>BAT</sub> = 3.6 V                                                                                                                                                                                    | [8]  |                                                            |                       |                             |             |

|                       |                                                                | deep-sleep mode                                                                                                                                                                                                                                   |      | -                                                          | 2                     | -                           | μΑ          |

|                       |                                                                | power-down mode                                                                                                                                                                                                                                   | [8]  | -                                                          | 2                     | -                           | μΑ          |

|                       |                                                                | deep power-down<br>mode                                                                                                                                                                                                                           | [8]  | -                                                          | 2                     | -                           | μA          |

| DD(IO)                | I/O supply current                                             | deep sleep mode                                                                                                                                                                                                                                   |      | -                                                          | 1                     | -                           | μA          |

| ~ /                   |                                                                | power-down mode                                                                                                                                                                                                                                   |      | -                                                          | 1                     | -                           | μA          |

|                       |                                                                | deep power-down mode                                                                                                                                                                                                                              | [9]  | -                                                          | 0.05                  | -                           | μA          |

| DDA                   | Analog supply current                                          | on pin VDDA;                                                                                                                                                                                                                                      | [11] | -                                                          | 0.4                   | -                           |             |

|                       |                                                                | deep sleep mode                                                                                                                                                                                                                                   |      |                                                            |                       |                             | μA          |

|                       |                                                                | power-down mode                                                                                                                                                                                                                                   | [11] | -                                                          | 0.4                   | -                           | μΑ          |

|                       |                                                                | deep power-down<br>mode                                                                                                                                                                                                                           | [11] | -                                                          | 0.007                 | -                           | μA          |

| RESET,RTC             | _ALARM, WAKEUPn pins                                           |                                                                                                                                                                                                                                                   |      |                                                            |                       |                             |             |

| V <sub>IH</sub>       | HIGH-level input voltage                                       |                                                                                                                                                                                                                                                   | [10] | 0.8 × (V <sub>ps</sub> – 0.35)                             | -                     | 5.5                         | V           |

| V <sub>IL</sub>       | LOW-level input voltage                                        |                                                                                                                                                                                                                                                   | [10] | 0                                                          | -                     | $0.3 \times (V_{ps} - 0.1)$ | V           |

| V <sub>hys</sub>      | hysteresis voltage                                             |                                                                                                                                                                                                                                                   | [10] | $\begin{array}{c} 0.05\times(V_{ps}\\-\ 0.35) \end{array}$ | -                     | -                           | V           |

| Vo                    | output voltage                                                 |                                                                                                                                                                                                                                                   | [10] | -                                                          | V <sub>ps</sub> - 0.2 | -                           | V           |

| Standard I/C          | ) pins - normal drive streng                                   | th                                                                                                                                                                                                                                                |      |                                                            |                       |                             |             |

| CI                    | input capacitance                                              |                                                                                                                                                                                                                                                   |      | -                                                          | -                     | 5.2                         | pF          |

| LL                    | LOW-level leakage<br>current                                   | V <sub>I</sub> = 0 V; on-chip pull-up resistor disabled                                                                                                                                                                                           |      | -                                                          | 3                     | -                           | nA          |

| ILH                   | HIGH-level leakage<br>current                                  | $V_I = V_{DD(IO)}$ ; on-chip<br>pull-down resistor<br>disabled                                                                                                                                                                                    |      | -                                                          | 3                     | -                           | nA          |

|                       |                                                                | $V_{I} = 5 V$                                                                                                                                                                                                                                     |      | -                                                          | -                     | 20                          | nA          |

|                       |                                                                | 1 = 0 1                                                                                                                                                                                                                                           |      |                                                            |                       |                             |             |

| loz                   | OFF-state output current                                       | $V_O = 0 V$ to $V_{DD(IO)}$ ;<br>on-chip pull-up/down<br>resistors disabled;<br>absolute value                                                                                                                                                    |      | -                                                          | 3                     | -                           | nA          |

| loz<br>V <sub>I</sub> |                                                                | $V_{O} = 0 V$ to $V_{DD(IO)}$ ;<br>on-chip pull-up/down<br>resistors disabled;<br>absolute value<br>pin configured to provide<br>a digital function;                                                                                              |      | - 0                                                        | 3                     | -<br>5.5                    | nA<br>V     |

|                       | current                                                        | $\begin{split} V_{O} &= 0 \ V \ to \ V_{DD(IO)}; \\ \text{on-chip pull-up/down} \\ \text{resistors disabled;} \\ \text{absolute value} \\ \text{pin configured to provide} \\ \text{a digital function;} \\ V_{DD(IO)} &\geq 2.2 \ V \end{split}$ |      | -                                                          | -                     |                             |             |

|                       | current                                                        | $V_{O} = 0 \text{ V to } V_{DD(IO)};$<br>on-chip pull-up/down<br>resistors disabled;<br>absolute value<br>pin configured to provide<br>a digital function;<br>$V_{DD(IO)} \ge 2.2 \text{ V}$<br>$V_{DD(IO)} = 0 \text{ V}$                        |      | -                                                          | 3<br>-<br>-           | -<br>5.5<br>3.6             |             |

| Vı                    | current<br>input voltage<br>output voltage                     | $\begin{split} V_{O} &= 0 \ V \ to \ V_{DD(IO)}; \\ \text{on-chip pull-up/down} \\ \text{resistors disabled;} \\ \text{absolute value} \\ \text{pin configured to provide} \\ \text{a digital function;} \\ V_{DD(IO)} &\geq 2.2 \ V \end{split}$ |      | -<br>0<br>0<br>0                                           | 3<br>-<br>-           |                             | V           |

|                       | current<br>input voltage                                       | $V_{O} = 0 \text{ V to } V_{DD(IO)};$<br>on-chip pull-up/down<br>resistors disabled;<br>absolute value<br>pin configured to provide<br>a digital function;<br>$V_{DD(IO)} \ge 2.2 \text{ V}$<br>$V_{DD(IO)} = 0 \text{ V}$                        |      | -<br>0<br>0                                                | 3                     | 3.6                         | V           |

| V <sub>I</sub>        | current<br>input voltage<br>output voltage<br>HIGH-level input | $V_{O} = 0 \text{ V to } V_{DD(IO)};$<br>on-chip pull-up/down<br>resistors disabled;<br>absolute value<br>pin configured to provide<br>a digital function;<br>$V_{DD(IO)} \ge 2.2 \text{ V}$<br>$V_{DD(IO)} = 0 \text{ V}$                        |      | -<br>0<br>0<br>0<br>0.7 ×                                  | 3                     | 3.6<br>V <sub>DD(IO)</sub>  | V<br>V<br>V |

#### 32-bit ARM Cortex-M4/M0 microcontroller

#### 32-bit ARM Cortex-M4/M0 microcontroller

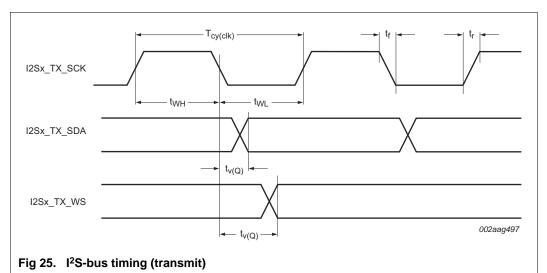

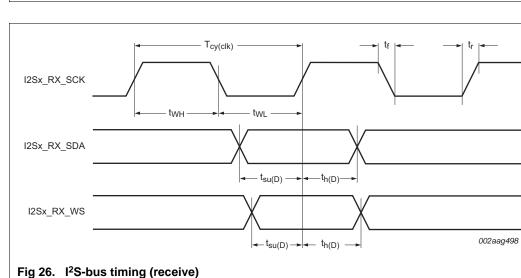

[1] Clock to the I<sup>2</sup>S-bus interface BASE\_APB1\_CLK = 150 MHz; peripheral clock to the I<sup>2</sup>S-bus interface PCLK = BASE\_APB1\_CLK / 12. I<sup>2</sup>S clock cycle time  $T_{cy(clk)}$  = 79.2 ns; corresponds to the SCK signal in the I<sup>2</sup>S-bus specification.

### 11.10 USART interface

#### Table 24. USART dynamic characteristics

$T_{amb} = -40$  °C to 85 °C; 2.2 V  $\leq V_{DD(REG)(3V3)} \leq 3.6$  V; 2.7 V  $\leq V_{DD(IO)} \leq 3.6$  V;  $C_L = 20$  pF. EHS = 1 for all pins. Simulated values.

| Symbol                             | Parameter              | Min | Max | Unit |  |

|------------------------------------|------------------------|-----|-----|------|--|

| USART master (in synchronous mode) |                        |     |     |      |  |

| t <sub>su(D)</sub>                 | data input set-up time | ns  |     |      |  |

| t <sub>h(D)</sub>                  | data input hold time   | 0   | -   | ns   |  |

| t <sub>v(Q)</sub>                  | data output valid time | 0   | 8.8 | ns   |  |

111 of 157

#### **NXP Semiconductors**

# LPC43S70

#### 32-bit ARM Cortex-M4/M0 microcontroller

#### 32-bit ARM Cortex-M4/M0 microcontroller

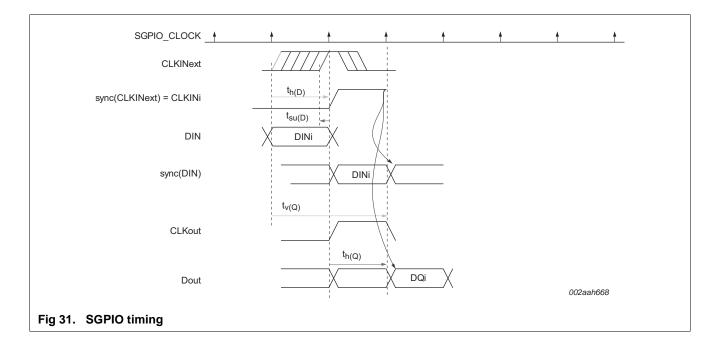

| Symbol             | Parameter              | Conditions                |     | Min                    | Тур | Мах                    | Unit |

|--------------------|------------------------|---------------------------|-----|------------------------|-----|------------------------|------|

| t <sub>su(D)</sub> | data input set-up time |                           |     | 2                      | -   | -                      | ns   |

| t <sub>h(D)</sub>  | data input hold time   |                           | [1] | T <sub>SGPIO</sub> + 2 | -   | -                      | ns   |

| t <sub>su(D)</sub> | data input set-up time | sampled by<br>SGPIO_CLOCK | [1] | T <sub>SGPIO</sub> + 2 | -   | -                      | ns   |

| t <sub>h(D)</sub>  | data input hold time   | sampled by<br>SGPIO_CLOCK | [1] | T <sub>SGPIO</sub> + 2 | -   | -                      | ns   |

| t <sub>v(Q)</sub>  | data output valid time |                           | [1] | -                      | -   | 2 x T <sub>SGPIO</sub> | ns   |

| t <sub>h(Q)</sub>  | data output hold time  |                           | [1] | T <sub>SGPIO</sub>     | -   |                        | ns   |

| t <sub>v(Q)</sub>  | data output valid time | sampled by<br>SGPIO_CLOCK | [1] | -3                     | -   | 3                      | ns   |

| t <sub>h(Q)</sub>  | data output hold time  | sampled by<br>SGPIO_CLOCK | [1] | -3                     | -   | 3                      | ns   |

#### Table 28. Dynamic characteristics: SGPIO

[1] SGPIO\_CLOCK is the internally generated SGPIO clock.  $T_{SGPIO} = 1/f_{SGPIO_CLOCK}$ .

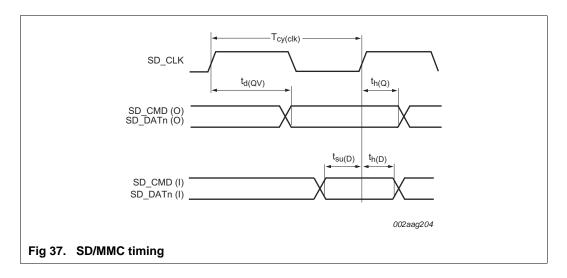

#### 11.19 SD/MMC

#### Table 35. Dynamic characteristics: SD/MMC

$T_{amb} = -40 \ ^{\circ}C$  to 85  $\ ^{\circ}C$ , 2.2 V  $\leq V_{DD(REG)(3V3)} \leq 3.6 \ V$ ; 2.7 V  $\leq V_{DD(IO)} \leq 3.6 \ V$ ,  $C_L = 20 \ pF$ . SAMPLE\_DELAY = 0x9, DRV\_DELAY = 0xD in the SDDELAY register sampled at 90 % and 10 % of the signal level, EHS = 1 for SD\_CLK pin, EHS = 1 for SD\_DATn and SD\_CMD pins. Simulated values.

| Symbol                                    | Parameter               | Conditions                        | Min | Max  | Unit |

|-------------------------------------------|-------------------------|-----------------------------------|-----|------|------|

| f <sub>clk</sub>                          | clock frequency         | on pin SD_CLK; data transfer mode |     | 52   | MHz  |

| t <sub>su(D)</sub> data input set-up time |                         | on pins SD_DATn as inputs         | 3.9 | -    | ns   |

|                                           |                         | on pins SD_CMD as inputs          | 5.2 | -    | ns   |

| t <sub>h(D)</sub>                         | data input hold time    | on pins SD_DATn as inputs         | 0.4 | -    | ns   |

|                                           |                         | on pins SD_CMD as inputs          | 0   |      | ns   |

| t <sub>d(QV)</sub>                        | data output valid delay | on pins SD_DATn as outputs        | -   | 15.3 | ns   |