Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                               |

|                            | Not For New Designs                                                               |

| Core Processor             | C166SV2                                                                           |

| Core Size                  | 16/32-Bit                                                                         |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI              |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                   |

| Number of I/O              | 76                                                                                |

| Program Memory Size        | 320KB (320K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 42K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                         |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-100-8                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2268n40f80lrabkxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Summary of Features**

- On-Chip Peripheral Modules

- Two synchronizable A/D Converters with up to 16 channels, 10-bit resolution, conversion time below 1 μs, optional data preprocessing (data reduction, range check), broken wire detection

- 16-channel general purpose capture/compare unit (CC2)

- Two capture/compare units for flexible PWM signal generation (CCU6x)

- Multi-functional general purpose timer unit with 5 timers

- Up to 6 serial interface channels to be used as UART, LIN, high-speed synchronous channel (SPI/QSPI), IIC bus interface (10-bit addressing, 400 kbit/s), IIS interface

- On-chip MultiCAN interface (Rev. 2.0B active) with up to 256 message objects (Full CAN/Basic CAN) on up to 6 CAN nodes and gateway functionality

- On-chip system timer and on-chip real time clock

- Up to 12 Mbytes external address space for code and data

- Programmable external bus characteristics for different address ranges

- Multiplexed or demultiplexed external address/data buses

- Selectable address bus width

- 16-bit or 8-bit data bus width

- Four programmable chip-select signals

- Single power supply from 3.0 V to 5.5 V

- Power reduction and wake-up modes with flexible power management

- Programmable watchdog timer and oscillator watchdog

- Up to 76 general purpose I/O lines

- On-chip bootstrap loaders

- Supported by a full range of development tools including C compilers, macroassembler packages, emulators, evaluation boards, HLL debuggers, simulators, logic analyzer disassemblers, programming boards

- On-chip debug support via Device Access Port (DAP) or JTAG interface

- 100-pin Green LQFP package, 0.5 mm (19.7 mil) pitch

#### **General Device Information**

## 2 General Device Information

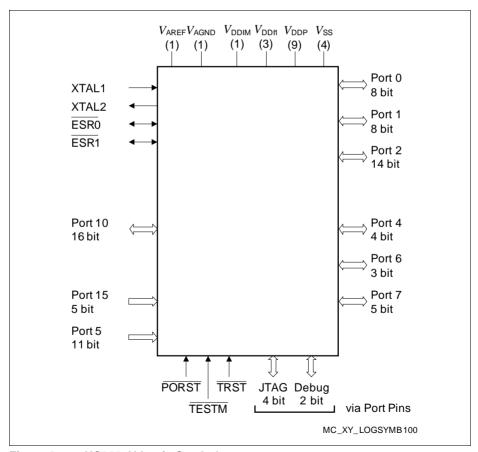

The XC226xN series (16/32-Bit Single-Chip Microcontroller with 32-Bit Performance) is a part of the Infineon XC2000 Family of full-feature single-chip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 80 million instructions per second) with extended peripheral functionality and enhanced IO capabilities. Optimized peripherals can be adapted flexibly to meet the application requirements. These derivatives utilize clock generation via PLL and internal or external clock sources. On-chip memory modules include program Flash, program RAM, and data RAM.

Figure 2 XC226xN Logic Symbol

Data Sheet 13 V1.6, 2014-06

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl. | Туре | Function                                       |

|-----|------------------|-------|------|------------------------------------------------|

| 24  | P5.3             | I     | In/A | Bit 3 of Port 5, General Purpose Input         |

|     | ADC0_CH3         | I     | In/A | Analog Input Channel 3 for ADC0                |

|     | T3INA            | I     | In/A | GPT12E Timer T3 Count/Gate Input               |

| 28  | P5.4             | I     | In/A | Bit 4 of Port 5, General Purpose Input         |

|     | ADC0_CH4         | I     | In/A | Analog Input Channel 4 for ADC0                |

|     | T3EUDA           | I     | In/A | GPT12E Timer T3 External Up/Down Control Input |

|     | TMS_A            | I     | In/A | JTAG Test Mode Selection Input                 |

| 29  | P5.5             | I     | In/A | Bit 5 of Port 5, General Purpose Input         |

|     | ADC0_CH5         | I     | In/A | Analog Input Channel 5 for ADC0                |

|     | CCU60_T12<br>HRB | I     | In/A | External Run Control Input for T12 of CCU60    |

| 30  | P5.8             | I     | In/A | Bit 8 of Port 5, General Purpose Input         |

|     | ADC0_CH8         | I     | In/A | Analog Input Channel 8 for ADC0                |

|     | ADC1_CH8         | I     | In/A | Analog Input Channel 8 for ADC1                |

|     | CCU6x_T12H<br>RC | I     | In/A | External Run Control Input for T12 of CCU60/1  |

|     | CCU6x_T13H<br>RC | I     | In/A | External Run Control Input for T13 of CCU60/1  |

|     | U2C0_DX0F        | I     | In/A | USIC2 Channel 0 Shift Data Input               |

| 31  | P5.9             | I     | In/A | Bit 9 of Port 5, General Purpose Input         |

|     | ADC0_CH9         | I     | In/A | Analog Input Channel 9 for ADC0                |

|     | ADC1_CH9         | I     | In/A | Analog Input Channel 9 for ADC1                |

|     | CC2_T7IN         | I     | In/A | CAPCOM2 Timer T7 Count Input                   |

| 32  | P5.10            | I     | In/A | Bit 10 of Port 5, General Purpose Input        |

|     | ADC0_CH10        | I     | In/A | Analog Input Channel 10 for ADC0               |

|     | ADC1_CH10        | I     | In/A | Analog Input Channel 10 for ADC1               |

|     | BRKIN_A          | I     | In/A | OCDS Break Signal Input                        |

|     | U2C1_DX0F        | I     | In/A | USIC2 Channel 1 Shift Data Input               |

|     | CCU61_T13<br>HRA | I     | In/A | External Run Control Input for T13 of CCU61    |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                      |

|-----|------------------|--------|------|-----------------------------------------------|

| 45  | P2.4             | O0 / I | St/B | Bit 4 of Port 2, General Purpose Input/Output |

|     | U0C1_DOUT        | 01     | St/B | USIC0 Channel 1 Shift Data Output             |

|     | TxDC0            | O2     | St/B | CAN Node 0 Transmit Data Output               |

|     | CC2_CC17         | O3 / I | St/B | CAPCOM2 CC17IO Capture Inp./ Compare Out.     |

|     | A17              | ОН     | St/B | External Bus Interface Address Line 17        |

|     | ESR1_0           | I      | St/B | ESR1 Trigger Input 0                          |

|     | U0C0_DX0F        | I      | St/B | USIC0 Channel 0 Shift Data Input              |

|     | RxDC1A           | I      | St/B | CAN Node 1 Receive Data Input                 |

| 46  | P2.5             | O0 / I | St/B | Bit 5 of Port 2, General Purpose Input/Output |

|     | U0C0_SCLK<br>OUT | O1     | St/B | USIC0 Channel 0 Shift Clock Output            |

|     | TxDC0            | O2     | St/B | CAN Node 0 Transmit Data Output               |

|     | CC2_CC18         | O3 / I | St/B | CAPCOM2 CC18IO Capture Inp./ Compare Out.     |

|     | A18              | ОН     | St/B | External Bus Interface Address Line 18        |

|     | U0C0_DX1D        | I      | St/B | USIC0 Channel 0 Shift Clock Input             |

|     | ESR1_10          | I      | St/B | ESR1 Trigger Input 10                         |

| 47  | P4.2             | O0 / I | St/B | Bit 2 of Port 4, General Purpose Input/Output |

|     | TxDC2            | O2     | St/B | CAN Node 2 Transmit Data Output               |

|     | CC2_CC26         | O3 / I | St/B | CAPCOM2 CC26IO Capture Inp./ Compare Out.     |

|     | CS2              | ОН     | St/B | External Bus Interface Chip Select 2 Output   |

|     | T2INA            | I      | St/B | GPT12E Timer T2 Count/Gate Input              |

| 48  | P2.6             | O0 / I | St/B | Bit 6 of Port 2, General Purpose Input/Output |

|     | U0C0_SELO<br>0   | O1     | St/B | USIC0 Channel 0 Select/Control 0 Output       |

|     | U0C1_SELO<br>1   | O2     | St/B | USIC0 Channel 1 Select/Control 1 Output       |

|     | CC2_CC19         | O3 / I | St/B | CAPCOM2 CC19IO Capture Inp./ Compare Out.     |

|     | A19              | ОН     | St/B | External Bus Interface Address Line 19        |

|     | U0C0_DX2D        | I      | St/B | USIC0 Channel 0 Shift Control Input           |

|     | RxDC0D           | I      | St/B | CAN Node 0 Receive Data Input                 |

|     | ESR2_6           | I      | St/B | ESR2 Trigger Input 6                          |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.      | Туре | Function                                       |

|-----|-------------------|------------|------|------------------------------------------------|

| 58  | P0.2              | O0 / I     | St/B | Bit 2 of Port 0, General Purpose Input/Output  |

|     | U1C0_SCLK<br>OUT  | O1         | St/B | USIC1 Channel 0 Shift Clock Output             |

|     | TxDC0             | 02         | St/B | CAN Node 0 Transmit Data Output                |

|     | CCU61_CC6<br>2    | О3         | St/B | CCU61 Channel 2 Output                         |

|     | A2                | ОН         | St/B | External Bus Interface Address Line 2          |

|     | U1C0_DX1B         | I          | St/B | USIC1 Channel 0 Shift Clock Input              |

|     | CCU61_CC6<br>2INA | I          | St/B | CCU61 Channel 2 Input                          |

| 59  | P10.0             | O0 / I     | St/B | Bit 0 of Port 10, General Purpose Input/Output |

|     | U0C1_DOUT         | 01         | St/B | USIC0 Channel 1 Shift Data Output              |

|     | CCU60_CC6         | O2         | St/B | CCU60 Channel 0 Output                         |

|     | AD0               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 0     |

|     | CCU60_CC6<br>0INA | I          | St/B | CCU60 Channel 0 Input                          |

|     | ESR1_2            | I          | St/B | ESR1 Trigger Input 2                           |

|     | U0C0_DX0A         | I          | St/B | USIC0 Channel 0 Shift Data Input               |

|     | U0C1_DX0A         | I          | St/B | USIC0 Channel 1 Shift Data Input               |

| 60  | P10.1             | O0 / I     | St/B | Bit 1 of Port 10, General Purpose Input/Output |

|     | U0C0_DOUT         | 01         | St/B | USIC0 Channel 0 Shift Data Output              |

|     | CCU60_CC6         | O2         | St/B | CCU60 Channel 1 Output                         |

|     | AD1               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 1     |

|     | CCU60_CC6<br>1INA | I          | St/B | CCU60 Channel 1 Input                          |

|     | U0C0_DX1A         | I          | St/B | USIC0 Channel 0 Shift Clock Input              |

|     | U0C0_DX0B         | I          | St/B | USIC0 Channel 0 Shift Data Input               |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.      | Туре | Function                                       |

|-----|------------------|------------|------|------------------------------------------------|

| 65  | P2.13            | O0 / I     | St/B | Bit 13 of Port 2, General Purpose Input/Output |

|     | U2C1_SELO<br>2   | O1         | St/B | USIC2 Channel 1 Select/Control 2 Output        |

|     | RxDC2D           | I          | St/B | CAN Node 2 Receive Data Input                  |

| 66  | P2.10            | O0 / I     | St/B | Bit 10 of Port 2, General Purpose Input/Output |

|     | U0C1_DOUT        | O1         | St/B | USIC0 Channel 1 Shift Data Output              |

|     | U0C0_SELO<br>3   | O2         | St/B | USIC0 Channel 0 Select/Control 3 Output        |

|     | CC2_CC23         | O3 / I     | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |

|     | A23              | ОН         | St/B | External Bus Interface Address Line 23         |

|     | U0C1_DX0E        | I          | St/B | USIC0 Channel 1 Shift Data Input               |

|     | CAPINA           | I          | St/B | GPT12E Register CAPREL Capture Input           |

| 67  | P10.3            | O0 / I     | St/B | Bit 3 of Port 10, General Purpose Input/Output |

|     | CCU60_COU<br>T60 | O2         | St/B | CCU60 Channel 0 Output                         |

|     | AD3              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 3     |

|     | U0C0_DX2A        | I          | St/B | USIC0 Channel 0 Shift Control Input            |

|     | U0C1_DX2A        | I          | St/B | USIC0 Channel 1 Shift Control Input            |

| 68  | P0.5             | O0 / I     | St/B | Bit 5 of Port 0, General Purpose Input/Output  |

|     | U1C1_SCLK<br>OUT | O1         | St/B | USIC1 Channel 1 Shift Clock Output             |

|     | U1C0_SELO<br>2   | O2         | St/B | USIC1 Channel 0 Select/Control 2 Output        |

|     | CCU61_COU<br>T62 | О3         | St/B | CCU61 Channel 2 Output                         |

|     | A5               | ОН         | St/B | External Bus Interface Address Line 5          |

|     | U1C1_DX1A        | I          | St/B | USIC1 Channel 1 Shift Clock Input              |

|     | U1C0_DX1C        | I          | St/B | USIC1 Channel 0 Shift Clock Input              |

|     | RXDC3E           | I          | St/B | CAN Node 3 Receive Data Input                  |

### **Functional Description**

## **Memory Content Protection**

The contents of on-chip memories can be protected against soft errors (induced e.g. by radiation) by activating the parity mechanism or the Error Correction Code (ECC).

The parity mechanism can detect a single-bit error and prevent the software from using incorrect data or executing incorrect instructions.

The ECC mechanism can detect and automatically correct single-bit errors. This supports the stable operation of the system.

It is strongly recommended to activate the ECC mechanism wherever possible because this dramatically increases the robustness of an application against such soft errors.

### **Functional Description**

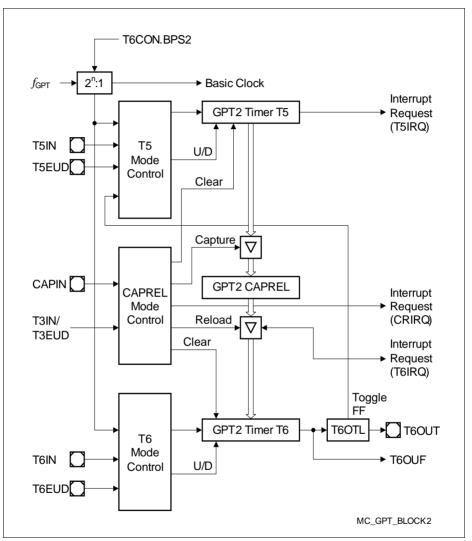

Figure 9 Block Diagram of GPT2

### **Functional Description**

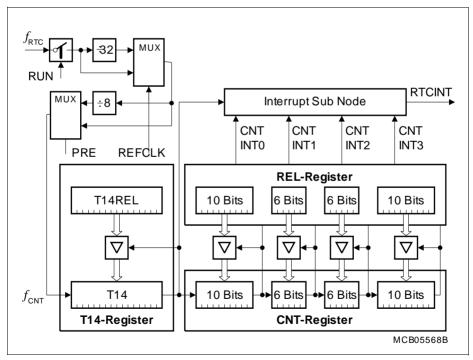

### 3.11 Real Time Clock

The Real Time Clock (RTC) module of the XC226xN can be clocked with a clock signal selected from internal sources or external sources (pins).

The RTC basically consists of a chain of divider blocks:

- Selectable 32:1 and 8:1 dividers (on off)

- The reloadable 16-bit timer T14

- The 32-bit RTC timer block (accessible via registers RTCH and RTCL) consisting of:

- a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

Figure 10 RTC Block Diagram

Note: The registers associated with the RTC are only affected by a power reset.

### **Functional Description**

### 3.17 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XC226xN from a number of external or internal clock sources:

- External clock signals with pad voltage or core voltage levels

- External crystal or resonator using the on-chip oscillator

- · On-chip clock source for operation without crystal/resonator

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals, a clock input signal, or from the on-chip clock source. See also **Section 4.7.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

#### **Electrical Parameters**

### 4.3 DC Parameters

These parameters are static or average values that may be exceeded during switching transitions (e.g. output current).

The XC226xN can operate within a wide supply voltage range from 3.0 V to 5.5 V. However, during operation this supply voltage must remain within 10 percent of the selected nominal supply voltage. It cannot vary across the full operating voltage range.

Because of the supply voltage restriction and because electrical behavior depends on the supply voltage, the parameters are specified separately for the upper and the lower voltage range.

During operation, the supply voltages may only change with a maximum speed of dV/dt < 1 V/ms.

Leakage current is strongly dependent on the operating temperature and the voltage level at the respective pin. The maximum values in the following tables apply under worst case conditions, i.e. maximum temperature and an input level equal to the supply voltage.

The value for the leakage current in an application can be determined by using the respective leakage derating formula (see tables) with values from that application.

The pads of the XC226xN are designed to operate in various driver modes. The DC parameter specifications refer to the pad current limits specified in **Section 4.7.4**.

#### **Electrical Parameters**

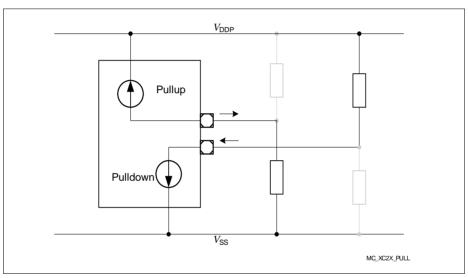

### Pullup/Pulldown Device Behavior

Most pins of the XC226xN feature pullup or pulldown devices. For some special pins these are fixed; for the port pins they can be selected by the application.

The specified current values indicate how to load the respective pin depending on the intended signal level. **Figure 13** shows the current paths.

The shaded resistors shown in the figure may be required to compensate system pull currents that do not match the given limit values.

Figure 13 Pullup/Pulldown Current Definition

#### **Electrical Parameters**

## 4.4 Analog/Digital Converter Parameters

These parameters describe the conditions for optimum ADC performance.

Note: Operating Conditions apply.

Table 20 ADC Parameters

| Parameter                                       | Symbol                     |      | Value | S    | Unit     | Note /<br>Test Condition       |

|-------------------------------------------------|----------------------------|------|-------|------|----------|--------------------------------|

|                                                 |                            | Min. | Тур.  | Max. |          |                                |

| Switched capacitance at an analog input         | $C_{AINSW}$                | -    | -     | 4    | pF       | not subject to production test |

| Total capacitance at an analog input            | $C_{AINT}$                 | -    | -     | 10   | pF       | not subject to production test |

| Switched capacitance at the reference input     | $C_{AREFSW}$               | -    | -     | 7    | pF       | not subject to production test |

| Total capacitance at the reference input        | $C_{AREFT}$                | _    | -     | 15   | pF       | not subject to production test |

| Differential Non-Linearity<br>Error             | EA <sub>DNL</sub>  <br>CC  | _    | 0.8   | 1    | LSB      |                                |

| Gain Error                                      | EA <sub>GAIN</sub>  <br>CC | _    | 0.4   | 0.8  | LSB      |                                |

| Integral Non-Linearity                          | EA <sub>INL</sub>  <br>CC  | _    | 0.8   | 1.2  | LSB      |                                |

| Offset Error                                    | EA <sub>OFF</sub>  <br>CC  | _    | 0.5   | 0.8  | LSB      |                                |

| Analog clock frequency                          | $f_{ADCI}SR$               | 0.5  | _     | 16.5 | MHz      | voltage_range=<br>lower        |

|                                                 |                            | 0.5  | _     | 20   | MHz      | voltage_range=<br>upper        |

| Input resistance of the selected analog channel | R <sub>AIN</sub> CC        | -    | -     | 2    | kOh<br>m | not subject to production test |

| Input resistance of the reference input         | R <sub>AREF</sub><br>CC    | _    | -     | 2    | kOh<br>m | not subject to production test |

#### **Electrical Parameters**

## 4.6 Flash Memory Parameters

The XC226xN is delivered with all Flash sectors erased and with no protection installed. The data retention time of the XC226xN's Flash memory (i.e. the time after which stored

The data retention time of the XC226xN's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

Table 25 Flash Parameters

| Parameter                                                  | Symbol                       |      | Values          | S               | Unit   | Note /                                                                            |

|------------------------------------------------------------|------------------------------|------|-----------------|-----------------|--------|-----------------------------------------------------------------------------------|

|                                                            |                              | Min. | Тур.            | Max.            |        | Test Condition                                                                    |

| Parallel Flash module                                      | $N_{PP}SR$                   | _    | _               | 2 <sup>1)</sup> |        | $N_{FL\_RD} \le 1$                                                                |

| program/erase limit<br>depending on Flash read<br>activity |                              | _    | _               | 1 <sup>2)</sup> |        | N <sub>FL_RD</sub> > 1                                                            |

| Flash erase endurance for security pages                   | $N_{\rm SEC}{ m SR}$         | 10   | -               | _               | cycles | t <sub>RET</sub> ≥ 20 years                                                       |

| Flash wait states <sup>3)</sup>                            | $N_{\mathrm{WSFLAS}}$        | 1    | _               | _               |        | f <sub>SYS</sub> ≤ 8 MHz                                                          |

|                                                            | <sub>H</sub> SR              | 2    | _               | _               |        | $f_{\rm SYS} \le$ 13 MHz                                                          |

|                                                            |                              | 3    | _               | _               |        | $f_{\rm SYS} \leq$ 17 MHz                                                         |

|                                                            |                              | 4    | _               | _               |        | $f_{\rm SYS}$ > 17 MHz                                                            |

| Erase time per sector/page                                 | $t_{\sf ER}$ CC              | _    | 7 <sup>4)</sup> | 8.0             | ms     |                                                                                   |

| Programming time per page                                  | $t_{PR}CC$                   | _    | 3 <sup>4)</sup> | 3.5             | ms     |                                                                                   |

| Data retention time                                        | $t_{RET}CC$                  | 20   | -               | _               | years  | $N_{\rm ER} \le$ 1,000 cycl es                                                    |

| Drain disturb limit                                        | $N_{\mathrm{DD}}\mathrm{SR}$ | 32   | _               | _               | cycles |                                                                                   |

| Number of erase cycles                                     | N <sub>ER</sub> SR           | _    | _               | 15.000          | cycles | $t_{\text{RET}} \ge 5$ years;<br>Valid for Flash<br>module 1 (up to<br>64 kbytes) |

|                                                            |                              | _    | _               | 1.000           | cycles | t <sub>RET</sub> ≥ 20 years                                                       |

The unused Flash module(s) can be erased/programmed while code is executed and/or data is read from only

one Flash module or from PSRAM. The Flash module that delivers code/data can, of course, not be

erased/programmed.

## **Electrical Parameters**

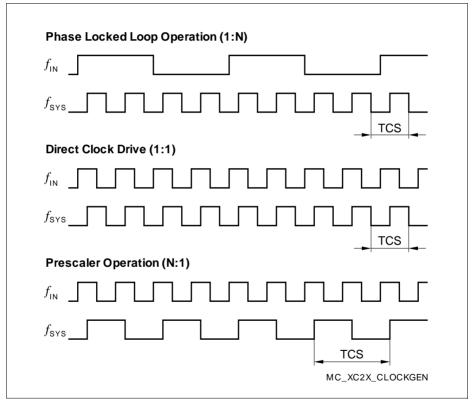

## 4.7.2 Definition of Internal Timing

The internal operation of the XC226xN is controlled by the internal system clock  $f_{\rm SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XC226xN.

Figure 19 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in Figure 19 uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

#### **Electrical Parameters**

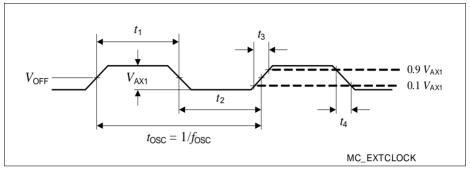

- 1) The amplitude voltage  $V_{\rm AX1}$  refers to the offset voltage  $V_{\rm OFF}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{\rm IX1}$ .

- 2) Overload conditions must not occur on pin XTAL1.

Figure 21 External Clock Drive XTAL1

Note: For crystal or ceramic resonator operation, it is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for oscillator operation.

The manufacturers of crystals and ceramic resonators offer an oscillator evaluation service. This evaluation checks the crystal/resonator specification limits to ensure a reliable oscillator operation.

#### **Electrical Parameters**

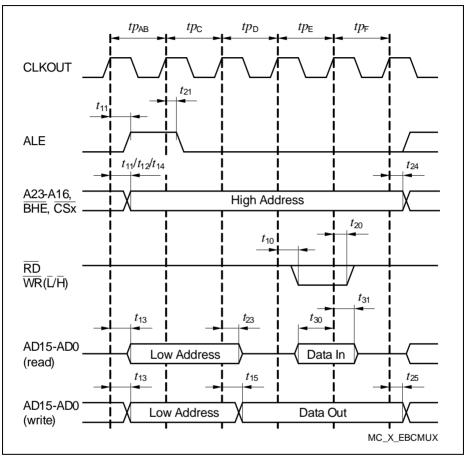

Figure 23 Multiplexed Bus Cycle

#### **Electrical Parameters**

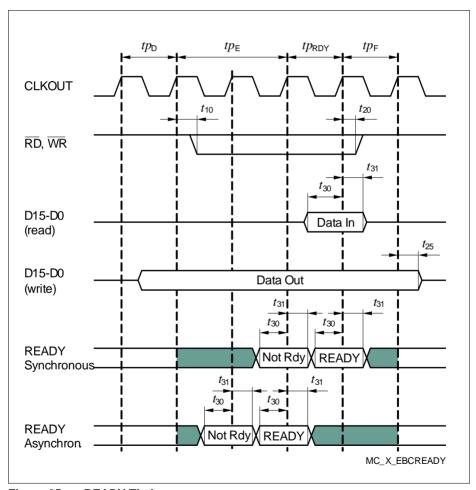

duration of an asynchronous READY signal for safe synchronization is one CLKOUT period plus the input setup time.

An active READY signal can be deactivated in response to the trailing (rising) edge of the corresponding command ( $\overline{RD}$  or  $\overline{WR}$ ).

If the next bus cycle is controlled by READY, an active READY signal must be disabled before the first valid sample point in the next bus cycle. This sample point depends on the programmed phases of the next cycle.

Figure 25 READY Timing

#### **Electrical Parameters**

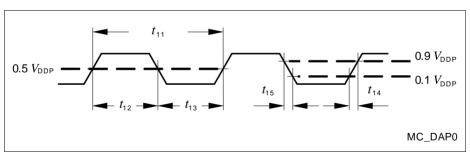

Table 39 DAP Interface Timing for Lower Voltage Range

| Parameter                                      | Symbol             |           | Values | S | Unit           | Note / |

|------------------------------------------------|--------------------|-----------|--------|---|----------------|--------|

|                                                |                    | Min. Typ. | Max.   |   | Test Condition |        |

| DAP0 clock period <sup>1)</sup>                | t <sub>11</sub> SR | 25        | -      | _ | ns             |        |

| DAP0 high time                                 | t <sub>12</sub> SR | 8         | _      | _ | ns             |        |

| DAP0 low time <sup>1)</sup>                    | t <sub>13</sub> SR | 8         | -      | _ | ns             |        |

| DAP0 clock rise time                           | t <sub>14</sub> SR | -         | _      | 4 | ns             |        |

| DAP0 clock fall time                           | t <sub>15</sub> SR | -         | _      | 4 | ns             |        |

| DAP1 setup to DAP0 rising edge                 | t <sub>16</sub> SR | 6         | _      | _ | ns             |        |

| DAP1 hold after DAP0 rising edge               | t <sub>17</sub> SR | 6         | _      | _ | ns             |        |

| DAP1 valid per DAP0 clock period <sup>2)</sup> | t <sub>19</sub> CC | 12        | 17     | - | ns             |        |

<sup>1)</sup> See the DAP chapter for clock rate restrictions in the Active::IDLE protocol state.

<sup>2)</sup> The Host has to find a suitable sampling point by analyzing the sync telegram response.

Figure 27 Test Clock Timing (DAP0)

Data Sheet 121 V1.6, 2014-06

#### **Electrical Parameters**

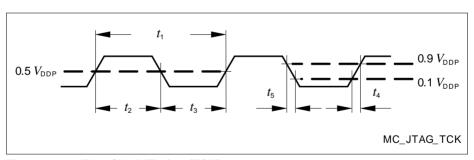

Table 41 JTAG Interface Timing for Lower Voltage Range (cont'd)

| Parameter                                                                | Symbol             |      | Values |      | Unit | Note /         |

|--------------------------------------------------------------------------|--------------------|------|--------|------|------|----------------|

|                                                                          |                    | Min. | Тур.   | Max. |      | Test Condition |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR  | 6    | -      | _    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>1)</sup>        | t <sub>8</sub> CC  | _    | 32     | 36   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>2)1)</sup> | t <sub>9</sub> CC  | -    | 32     | 36   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>1)</sup>   | t <sub>10</sub> CC | -    | 32     | 36   | ns   |                |

| TDO hold after TCK falling edge <sup>1)</sup>                            | t <sub>18</sub> CC | 5    | -      | -    | ns   |                |

<sup>1)</sup> The falling edge on TCK is used to generate the TDO timing.

<sup>2)</sup> The setup time for TDO is given implicitly by the TCK cycle time.

Figure 30 Test Clock Timing (TCK)

Data Sheet 124 V1.6, 2014-06