Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16/32-Bit                                                                        |

| Speed                      | 40MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 38                                                                               |

| Program Memory Size        | 192KB (192K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 26K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 9x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-64-6                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xc2236n-24f40l-aa |

16/32-Bit

**Architecture**

XC2232N, XC2234N, XC2236N, XC2238N

16/32-Bit Single-Chip Microcontroller with 32-Bit Performance XC2000 Family / Value Line

Data Sheet V1.5 2013-02

Microcontrollers

### **Table of Contents**

| 4.7     | AC Parameters                                  | 84 |

|---------|------------------------------------------------|----|

| 4.7.1   | Testing Waveforms                              | 84 |

| 4.7.2   | Definition of Internal Timing                  | 85 |

| 4.7.2.1 | Phase Locked Loop (PLL)                        | 86 |

| 4.7.2.2 | Wakeup Clock                                   | 89 |

| 4.7.2.3 | Selecting and Changing the Operating Frequency | 89 |

| 4.7.3   | External Clock Input Parameters                | 90 |

| 4.7.4   | Pad Properties                                 | 92 |

| 4.7.5   | Synchronous Serial Interface Timing            | 96 |

| 4.7.6   | Debug Interface Timing                         | 00 |

| 5       | Package and Reliability                        | 06 |

| 5.1     | Packaging 1                                    | 06 |

| 5.2     | Thermal Considerations                         | 80 |

| 5.3     | Quality Declarations                           | 09 |

### **Summary of Features**

Table 5 Interface Channel Association (cont'd)

| Total Number      | Available Channels / Message Objects                      | Available Channels / Message Objects |  |  |  |  |  |

|-------------------|-----------------------------------------------------------|--------------------------------------|--|--|--|--|--|

| 3 CAN nodes       | CAN0, CAN1, CAN2<br>64 message objects                    |                                      |  |  |  |  |  |

| 6 CAN nodes       | CAN0, CAN1, CAN2, CAN3, CAN4, CAN5<br>256 message objects |                                      |  |  |  |  |  |

| 2 serial channels | U0C0, U0C1                                                |                                      |  |  |  |  |  |

| 4 serial channels | U0C0, U0C1, U1C0, U1C1                                    |                                      |  |  |  |  |  |

| 6 serial channels | U0C0, U0C1, U1C0, U1C1, U2C0, U2C1                        |                                      |  |  |  |  |  |

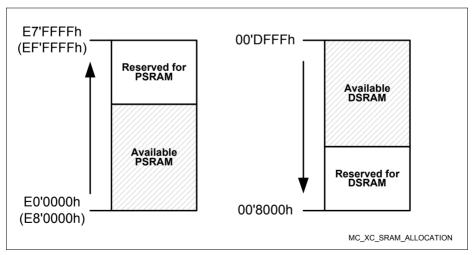

The XC223xN types are offered with several SRAM memory sizes. Figure 1 shows the allocation rules for PSRAM and DSRAM. Note that the rules differ:

- PSRAM allocation starts from the lower address

- · DSRAM allocation starts from the higher address

For example 8 Kbytes of PSRAM will be allocated at E0'0000h-E0'1FFFh and 8 Kbytes of DSRAM will be at 00'C000h-00'DFFFh.

Figure 1 SRAM Allocation

### **General Device Information**

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                       |

|-----|------------------|--------|------|------------------------------------------------|

| 26  | P2.1             | O0 / I | St/B | Bit 1 of Port 2, General Purpose Input/Output  |

|     | TxDC0            | 01     | St/B | CAN Node 0 Transmit Data Output                |

|     | RxDC5C           | I      | St/B | CAN Node 5 Receive Data Input                  |

|     | T5EUDB           | I      | St/B | GPT12E Timer T5 External Up/Down Control Input |

|     | ESR1_5           | I      | St/B | ESR1 Trigger Input 5                           |

| 27  | P2.2             | O0 / I | St/B | Bit 2 of Port 2, General Purpose Input/Output  |

|     | TxDC1            | 01     | St/B | CAN Node 1 Transmit Data Output                |

|     | ESR2_5           | I      | St/B | ESR2 Trigger Input 5                           |

| 28  | P2.3             | O0 / I | St/B | Bit 3 of Port 2, General Purpose Input/Output  |

|     | U0C0_DOUT        | 01     | St/B | USIC0 Channel 0 Shift Data Output              |

|     | CC2_CC16         | O3 / I | St/B | CAPCOM2 CC16IO Capture Inp./ Compare Out.      |

|     | ESR2_0           | I      | St/B | ESR2 Trigger Input 0                           |

|     | U0C0_DX0E        | I      | St/B | USIC0 Channel 0 Shift Data Input               |

|     | U0C1_DX0D        | I      | St/B | USIC0 Channel 1 Shift Data Input               |

|     | RxDC0A           | I      | St/B | CAN Node 0 Receive Data Input                  |

| 29  | P2.4             | O0 / I | St/B | Bit 4 of Port 2, General Purpose Input/Output  |

|     | U0C1_DOUT        | 01     | St/B | USIC0 Channel 1 Shift Data Output              |

|     | TxDC0            | O2     | St/B | CAN Node 0 Transmit Data Output                |

|     | CC2_CC17         | O3 / I | St/B | CAPCOM2 CC17IO Capture Inp./ Compare Out.      |

|     | ESR1_0           | I      | St/B | ESR1 Trigger Input 0                           |

|     | U0C0_DX0F        | I      | St/B | USIC0 Channel 0 Shift Data Input               |

|     | RxDC1A           | I      | St/B | CAN Node 1 Receive Data Input                  |

| 30  | P2.5             | O0 / I | St/B | Bit 5 of Port 2, General Purpose Input/Output  |

|     | U0C0_SCLK<br>OUT | 01     | St/B | USIC0 Channel 0 Shift Clock Output             |

|     | TxDC0            | O2     | St/B | CAN Node 0 Transmit Data Output                |

|     | CC2_CC18         | O3 / I | St/B | CAPCOM2 CC18IO Capture Inp./ Compare Out.      |

|     | U0C0_DX1D        | I      | St/B | USIC0 Channel 0 Shift Clock Input              |

|     | ESR1_10          | I      | St/B | ESR1 Trigger Input 10                          |

**Functional Description**

# 3 Functional Description

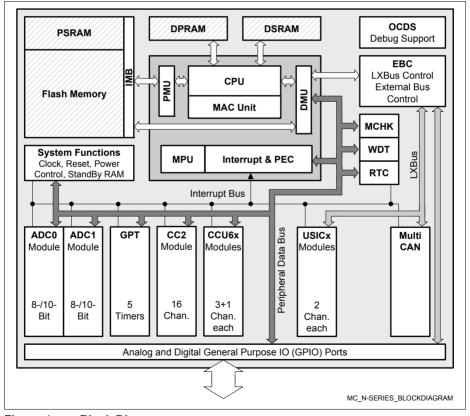

The architecture of the XC223xN combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources. This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XC223xN.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XC223xN.

Figure 4 Block Diagram

### **Functional Description**

With this hardware most XC223xN instructions are executed in a single machine cycle of 12.5 ns @ 80-MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle, no matter how many bits are shifted. Also, multiplication and most MAC instructions execute in one cycle. All multiple-cycle instructions have been optimized so that they can be executed very fast; for example, a 32-/16-bit division is started within 4 cycles while the remaining cycles are executed in the background. Another pipeline optimization, the branch target prediction, eliminates the execution time of branch instructions if the prediction was correct.

The CPU has a register context consisting of up to three register banks with 16 word-wide GPRs each at its disposal. One of these register banks is physically allocated within the on-chip DPRAM area. A Context Pointer (CP) register determines the base address of the active register bank accessed by the CPU at any time. The number of these register bank copies is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 32 Kwords is provided for storage of temporary data. The system stack can be allocated to any location within the address space (preferably in the on-chip RAM area); it is accessed by the CPU with the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared with the stack pointer value during each stack access to detect stack overflow or underflow.

The high performance of the CPU hardware implementation can be best utilized by the programmer with the highly efficient XC223xN instruction set. This includes the following instruction classes:

- Standard Arithmetic Instructions

- DSP-Oriented Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- · Shift and Rotate Instructions

- · Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- · System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

### **Functional Description**

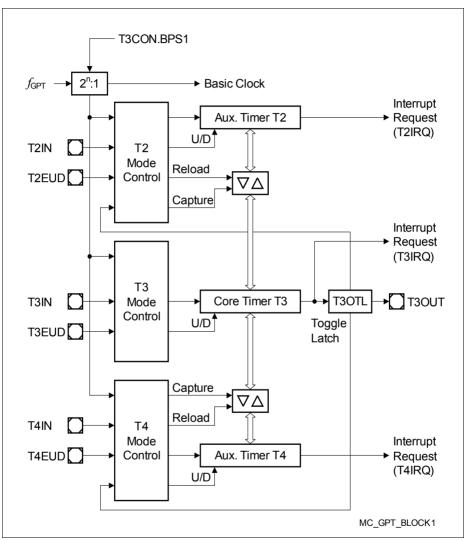

### 3.9 General Purpose Timer (GPT12E) Unit

The GPT12E unit is a very flexible multifunctional timer/counter structure which can be used for many different timing tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT12E unit incorporates five 16-bit timers organized in two separate modules, GPT1 and GPT2. Each timer in each module may either operate independently in a number of different modes or be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation: Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the system clock and divided by a programmable prescaler. Counter Mode allows timer clocking in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes each timer has one associated port pin (TxIN) which serves as a gate or clock input. The maximum resolution of the timers in module GPT1 is 4 system clock cycles.

The counting direction (up/down) for each timer can be programmed by software or altered dynamically by an external signal on a port pin (TxEUD), e.g. to facilitate position tracking.

In Incremental Interface Mode the GPT1 timers can be directly connected to the incremental position sensor signals A and B through their respective inputs TxIN and TxEUD. Direction and counting signals are internally derived from these two input signals, so that the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components. It may also be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to the basic operating modes, T2 and T4 may be configured as reload or capture register for timer T3. A timer used as capture or reload register is stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at the associated input pin (TxIN). Timer T3 is reloaded with the contents of T2 or T4, triggered either by an external signal or a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be continuously generated without software intervention.

Note: Signals T2IN, T2EUD, T4EUD, and T6EUD are not connected to pins.

Data Sheet 43 V1.5, 2013-02

### **Functional Description**

Figure 8 Block Diagram of GPT1

**Functional Description**

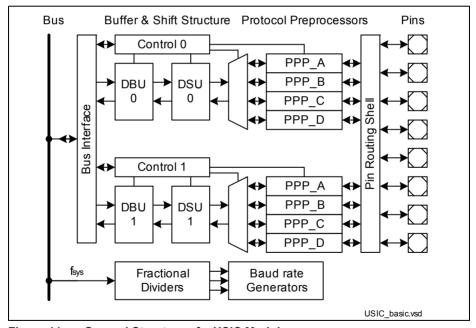

## 3.12 Universal Serial Interface Channel Modules (USIC)

The XC223xN features the USIC modules USIC0, USIC1, USIC2. Each module provides two serial communication channels.

The Universal Serial Interface Channel (USIC) module is based on a generic data shift and data storage structure which is identical for all supported serial communication protocols. Each channel supports complete full-duplex operation with a basic data buffer structure (one transmit buffer and two receive buffer stages). In addition, the data handling software can use FIFOs.

The protocol part (generation of shift clock/data/control signals) is independent of the general part and is handled by protocol-specific preprocessors (PPPs).

The USIC's input/output lines are connected to pins by a pin routing unit. The inputs and outputs of each USIC channel can be assigned to different interface pins, providing great flexibility to the application software. All assignments can be made during runtime.

Figure 11 General Structure of a USIC Module

The regular structure of the USIC module brings the following advantages:

- · Higher flexibility through configuration with same look-and-feel for data management

- · Reduced complexity for low-level drivers serving different protocols

- Wide range of protocols with improved performances (baud rate, buffer handling)

### **Functional Description**

#### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Independent CAN nodes

- Set of independent message objects (shared by the CAN nodes)

- Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

### 3.14 System Timer

The System Timer consists of a programmable prescaler and two concatenated timers (10 bits and 6 bits). Both timers can generate interrupt requests. The clock source can be selected and the timers can also run during power reduction modes.

Therefore, the System Timer enables the software to maintain the current time for scheduling functions or for the implementation of a clock.

# 3.15 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2 μs and 13.4 s can be monitored (@ 80 MHz).

The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

#### **Electrical Parameters**

# 4.3.1 DC Parameters for Upper Voltage Area

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{\rm OV}$ .

Note: Operating Conditions apply.

**Table 16** is valid under the following conditions:  $V_{\text{DDP}} \le 5.5 \text{ V}$ ;  $V_{\text{DDP}} \text{typ. 5 V}$ ;  $V_{\text{DDP}} \ge 4.5 \text{ V}$

Table 16 DC Characteristics for Upper Voltage Range

| Parameter                                                                        | Symbol                   | Values                           |      |                                  | Unit | Note /                                                                                                                                                      |

|----------------------------------------------------------------------------------|--------------------------|----------------------------------|------|----------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                  |                          | Min.                             | Тур. | Max.                             |      | Test Condition                                                                                                                                              |

| Pin capacitance (digital inputs/outputs). To be doubled for double bond pins. 1) | C <sub>IO</sub> CC       | _                                | _    | 10                               | pF   | not subject to production test                                                                                                                              |

| Input Hysteresis <sup>2)</sup>                                                   | HYS CC                   | $V_{\rm DDP}$                    | _    | _                                | V    | R <sub>S</sub> = 0 Ohm                                                                                                                                      |

| Absolute input leakage current on pins of analog ports <sup>3)</sup>             | I <sub>OZ1</sub>  <br>CC | _                                | 10   | 200                              | nA   | $\begin{array}{c} V_{\rm IN} \!\!> V_{\rm SS} \; ; \\ V_{\rm IN} \!\!< V_{\rm DDP} \end{array} \label{eq:VIN}$                                              |

| Absolute input leakage current for all other pins. To be doubled for double      | ins. CC                  | _                                | 0.2  | 5                                | μА   | $T_{\rm J} \le$ 110 °C;<br>$V_{\rm IN} > V_{\rm SS}$ ;<br>$V_{\rm IN} < V_{\rm DDP}$                                                                        |

| bond pins. <sup>3)1)4)</sup>                                                     |                          | _                                | 0.2  | 15                               | μА   | $T_{\rm J} \le$ 150 °C;<br>$V_{\rm IN} > V_{\rm SS}$ ;<br>$V_{\rm IN} < V_{\rm DDP}$                                                                        |

| Pull Level Force Current <sup>5)</sup>                                           | $ I_{\rm PLF} $ SR       | 250                              | _    | _                                | μА   | $ \begin{aligned} V_{\text{IN}} &\geq V_{\text{IHmin}}(pull\\ down\_enabled);\\ V_{\text{IN}} &\leq V_{\text{ILmax}}(pull\\ up\_enabled) \end{aligned} $    |

| Pull Level Keep Current <sup>6)</sup>                                            | I <sub>PLK</sub>  <br>SR | _                                | _    | 30                               | μА   | $ \begin{aligned} V_{\text{IN}} &\geq V_{\text{IHmin}}(pull \\ up\_enabled); \\ V_{\text{IN}} &\leq V_{\text{ILmax}}(pull \\ down\_enabled) \end{aligned} $ |

| Input high voltage (all except XTAL1)                                            | $V_{IH}SR$               | $0.7 \text{ x}$ $V_{\text{DDP}}$ | _    | <i>V</i> <sub>DDP</sub> + 0.3    | V    |                                                                                                                                                             |

| Input low voltage (all except XTAL1)                                             | $V_{IL}SR$               | -0.3                             | _    | $0.3 \text{ x}$ $V_{\text{DDP}}$ | V    |                                                                                                                                                             |

#### **Electrical Parameters**

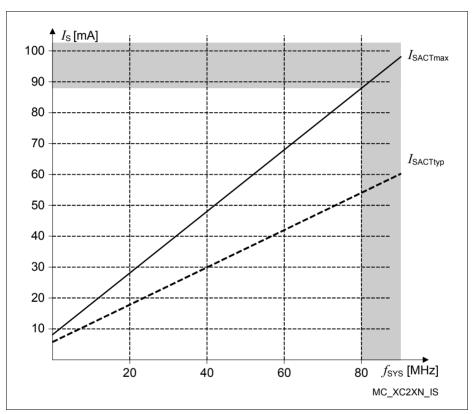

During operation domain A draws a maximum current of 1.5 mA for each active A/D converter module from  $V_{\rm DDPA}$ .

In Fast Startup Mode (with the Flash modules deactivated), the typical current is reduced to  $3 + 0.6 \times f_{\rm SYS}$  mA.

Figure 14 Supply Current in Active Mode as a Function of Frequency

Note: Operating Conditions apply.

#### **Electrical Parameters**

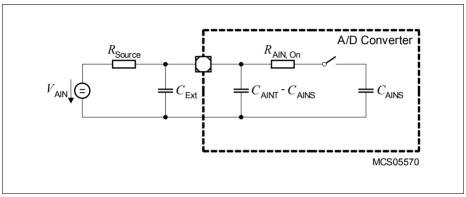

# 4.4 Analog/Digital Converter Parameters

These parameters describe the conditions for optimum ADC performance.

Note: Operating Conditions apply.

Table 20 ADC Parameters

| Parameter                                       | Symbol                                          |      | Values | 3    | Unit     | Note /<br>Test Condition       |

|-------------------------------------------------|-------------------------------------------------|------|--------|------|----------|--------------------------------|

|                                                 |                                                 | Min. | Тур.   | Max. |          |                                |

| Switched capacitance at an analog input         | $C_{AINSW}$                                     | -    | -      | 4    | pF       | not subject to production test |

| Total capacitance at an analog input            | $C_{AINT}$                                      | -    | -      | 10   | pF       | not subject to production test |

| Switched capacitance at the reference input     | $\begin{array}{c} C_{AREFSW} \\ CC \end{array}$ | -    | -      | 7    | pF       | not subject to production test |

| Total capacitance at the reference input        | $C_{AREFT}$                                     | _    | -      | 15   | pF       | not subject to production test |

| Differential Non-Linearity<br>Error             | $ EA_{DNL} $                                    | _    | 0.8    | 1    | LSB      |                                |

| Gain Error                                      | $ EA_{GAIN} $                                   | _    | 0.4    | 0.8  | LSB      |                                |

| Integral Non-Linearity                          | $ EA_{INL} $                                    | _    | 0.8    | 1.2  | LSB      |                                |

| Offset Error                                    | $ EA_{OFF} $                                    | _    | 0.5    | 0.8  | LSB      |                                |

| Analog clock frequency                          | $f_{ADCI}SR$                                    | 0.5  | _      | 16.5 | MHz      | voltage_range=<br>lower        |

|                                                 |                                                 | 0.5  | _      | 20   | MHz      | voltage_range=<br>upper        |

| Input resistance of the selected analog channel | R <sub>AIN</sub> CC                             | _    | -      | 2    | kOh<br>m | not subject to production test |

| Input resistance of the reference input         | R <sub>AREF</sub><br>CC                         | _    | -      | 2    | kOh<br>m | not subject to production test |

#### **Electrical Parameters**

- 4) The broken wire detection delay against V<sub>AREF</sub> is measured in numbers of consecutive precharge cycles at a conversion rate of not more than 10 μs. This function is influenced by leakage current, in particular at high temperature. Result above 80% (332μ)

- 5) TUE is tested at V<sub>AREF</sub> = V<sub>DDPA</sub> = 5.0 V, V<sub>AGND</sub> = 0 V. It is verified by design for all other voltages within the defined voltage range. The specified TUE is valid only if the absolute sum of input overload currents on analog port pins (see I<sub>OV</sub> specification) does not exceed 10 mA, and if V<sub>AREF</sub> and V<sub>AGND</sub> remain stable during the measurement time.

- 6)  $V_{\text{AIN}}$  may exceed  $V_{\text{AGND}}$  or  $V_{\text{AREF}}$  up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

Figure 16 Equivalent Circuitry for Analog Inputs

#### **Electrical Parameters**

### Coding of bit fields LEVxV in SWD Configuration Registers

After power-on the supply watch dog is preconfigured to operate in the lower voltage range.

Table 23 Coding of bit fields LEVxV in Register SWDCON0

| Code                                  | Voltage Level | Notes <sup>1)</sup>          |

|---------------------------------------|---------------|------------------------------|

| 0000 <sub>B</sub>                     | -             | out of valid operation range |

| 0001 <sub>B</sub>                     | 3.0 V         | LEV1V: reset request         |

| 0010 <sub>B</sub> - 0101 <sub>B</sub> | 3.1 V- 3.4 V  | step width is 0.1 V          |

| 0110 <sub>B</sub>                     | 3.6 V         |                              |

| 0111 <sub>B</sub>                     | 4.0 V         |                              |

| 1000 <sub>B</sub>                     | 4.2 V         |                              |

| 1001 <sub>B</sub>                     | 4.5 V         | LEV2V: no request            |

| 1010 <sub>B</sub> - 1110 <sub>B</sub> | 4.6 V - 5.0 V | step width is 0.1 V          |

| 1111 <sub>B</sub>                     | 5.5 V         |                              |

<sup>1)</sup> The indicated default levels for LEV1V and LEV2V are selected automatically after a power-on reset.

### Coding of bit fields LEVxV in PVC Configuration Registers

The core voltages are controlled internally to the nominal value of 1.5 V; a variation of  $\pm 10$  % is allowed. These operation conditions limit the possible PVC monitoring values to the predefined reset values shown in **Table 24**.

Table 24 Coding of bit fields LEVxV in Registers PVCyCONz

| Code                                | Voltage Level | Notes <sup>1)</sup>                    |

|-------------------------------------|---------------|----------------------------------------|

| 000 <sub>B</sub> -011 <sub>B</sub>  | -             | out of valid operation range           |

| 100 <sub>B</sub>                    | 1.35 V        | LEV1V: reset request                   |

| 101 <sub>B</sub>                    | 1.45 V        | LEV2V: interrupt request <sup>2)</sup> |

| 110 <sub>B</sub> - 111 <sub>B</sub> | -             | out of valid operation range           |

<sup>1)</sup> The indicated default levels for LEV1V and LEV2V are selected automatically after a power-on reset.

<sup>2)</sup> Due to variations of the tolerance of both the Embedded Voltage Regulators (EVR) and the PVC levels, this interrupt can be triggered inadvertently, even though the core voltage is within the normal range. It is, therefore, recommended not to use this warning level.

### **Electrical Parameters**

### 4.7 AC Parameters

These parameters describe the dynamic behavior of the XC223xN.

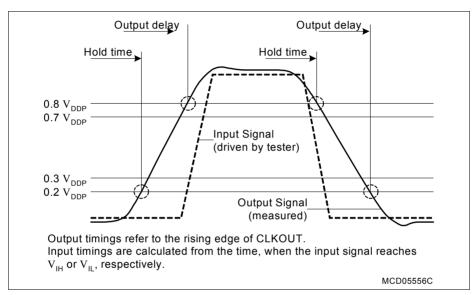

# 4.7.1 Testing Waveforms

These values are used for characterization and production testing (except pin XTAL1).

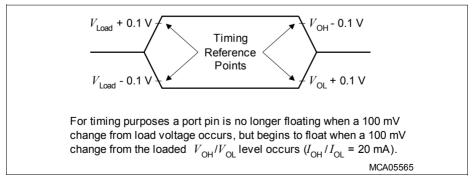

Figure 17 Input Output Waveforms

Figure 18 Floating Waveforms

#### **Electrical Parameters**

Table 26 System PLL Parameters

| Parameter            | Symbol                   | Values |      |      | Unit | Note /                                   |

|----------------------|--------------------------|--------|------|------|------|------------------------------------------|

|                      |                          | Min.   | Тур. | Max. |      | Test Condition                           |

| VCO output frequency | ency f <sub>VCO</sub> CC | 50     | -    | 110  | MHz  | VCOSEL= 00b;<br>VCOmode=<br>controlled   |

|                      |                          | 10     | _    | 40   | MHz  | VCOSEL= 00b;<br>VCOmode=<br>free running |

|                      |                          | 100    | -    | 160  | MHz  | VCOSEL= 01b;<br>VCOmode=<br>controlled   |

|                      |                          | 20     | -    | 80   | MHz  | VCOSEL= 01b;<br>VCOmode=<br>free running |

### 4.7.2.2 Wakeup Clock

When wakeup operation is selected (SYSCON0.CLKSEL = 00<sub>B</sub>), the system clock is derived from the low-frequency wakeup clock source:

$$f_{SYS} = f_{WU}$$

.

In this mode, a basic functionality can be maintained without requiring an external clock source and while minimizing the power consumption.

# 4.7.2.3 Selecting and Changing the Operating Frequency

When selecting a clock source and the clock generation method, the required parameters must be carefully written to the respective bit fields, to avoid unintended intermediate states.

Many applications change the frequency of the system clock ( $f_{SYS}$ ) during operation in order to optimize system performance and power consumption. Changing the operating frequency also changes the switching currents, which influences the power supply.

To ensure proper operation of the on-chip EVRs while they generate the core voltage, the operating frequency shall only be changed in certain steps. This prevents overshoots and undershoots of the supply voltage.

To avoid the indicated problems, recommended sequences are provided which ensure the intended operation of the clock system interacting with the power system. Please refer to the Programmer's Guide.

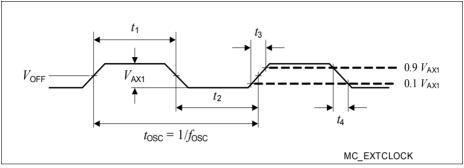

#### **Electrical Parameters**

- 1) The amplitude voltage  $V_{\rm AX1}$  refers to the offset voltage  $V_{\rm OFF}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{\rm IX1}$ .

- 2) Overload conditions must not occur on pin XTAL1.

Figure 21 External Clock Drive XTAL1

Note: For crystal or ceramic resonator operation, it is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for oscillator operation.

The manufacturers of crystals and ceramic resonators offer an oscillator evaluation service. This evaluation checks the crystal/resonator specification limits to ensure a reliable oscillator operation.

#### **Electrical Parameters**

Table 29 Standard Pad Parameters for Lower Voltage Range (cont'd)

| Parameter                       | Symbol                 |      | Values |                                  |    | Note /                                                                                                          |    |                                                                                                                                  |

|---------------------------------|------------------------|------|--------|----------------------------------|----|-----------------------------------------------------------------------------------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------|

|                                 |                        | Min. | Тур.   | Max.                             |    | Test Condition                                                                                                  |    |                                                                                                                                  |

| Rise and Fall times (10% - 90%) | - t <sub>RF</sub> CC - | _    | _      | 37 +<br>0.65 x<br>C <sub>L</sub> | ns | $C_{\rm L} \ge 20~{\rm pF};$<br>$C_{\rm L} \le 100~{\rm pF};$<br>Driver_Strength<br>= Medium                    |    |                                                                                                                                  |

|                                 |                        | _    | _      | 24 +<br>0.3 x<br>C <sub>L</sub>  | ns | $C_{\rm L}{\geq}$ 20 pF;<br>$C_{\rm L}{\leq}$ 100 pF;<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Medium |    |                                                                                                                                  |

|                                 |                        |      |        | _                                | -  | 6.2 +<br>0.24 x<br>$C_{L}$                                                                                      | ns | $C_{\text{L}} \ge 20 \text{ pF};$<br>$C_{\text{L}} \le 100 \text{ pF};$<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Sharp |

|                                 |                        |      |        |                                  |    | _                                                                                                               | _  | 34 +<br>0.3 x<br>C <sub>L</sub>                                                                                                  |

|                                 |                        | _    | _      | 500 +<br>2.5 x<br>$C_{L}$        | ns | $C_{\rm L} \ge 20 \ \rm pF;$<br>$C_{\rm L} \le 100 \ \rm pF;$<br>Driver_Strength<br>= Weak                      |    |                                                                                                                                  |

An output current above |I<sub>OXnom</sub>| may be drawn from up to three pins at the same time. For any group of 16 neighboring output pins, the total output current in each direction (\(\Sigma I\_{OL}\) and \(\Sigma - I\_{OH}\)) must remain below 50 mA.

www.infineon.com

Published by Infineon Technologies AG