#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product StatusObsoleteCore ProcessorC166SV2Core Size6/32-BitSpeed80MHzConnectivityCANbus, EBI/EMI, I*C, LINbus, SPI, SSC, UART/USART, USIPreipheralsI*S, POR, PWM, WDTNumber of I/O38Program Memory Size202K (320K x 8)Program Memory TypeFLASHEEPROM Size-Valdage - Supply (Vcc/Vd)3V - S.5VPotage - Supply (Vcc/Vd)SV - S.5VData ConvertersAlo SuppleOperating Temperature40°C ~ 125°C (TA)Mounting TypeSuface MountProkage / Case6-LQFP Exposed PadPackage / Case6-LQFP Exposed PadSuppler Device PackageBitp://www.esfl.com/product-detail/infineon-technologies/xc223840f80baksxumal | Details                    |                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------|

| Core Size16/32-BitSpeed80MHzConnectivityCANbus, EBI/EMI, I*C, LINbus, SPI, SSC, UART/USART, USIPeripherals1*S, POR, PWM, WDTNumber of I/O38Program Memory Size320KB (320K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size42K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP Exposed PadSuppler Device Package-                                                                                                                                                                     | Product Status             | Obsolete                                                                         |

| Speed80MHzConnectivityCANbus, EBI/EMI, I²C, LINbus, SPI, SSC, UART/USART, USIPeripheralsI²S, POR, PWM, WDTNumber of I/O38Program Memory Size320KB (320K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size42K × 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP Exposed PadSupplier Device PackageFG-LQFP-64-6                                                                                                                                                    | Core Processor             | C166SV2                                                                          |

| ConnectivityCANbus, EBI/EMI, I²C, LINbus, SPI, SSC, UART/USART, USIPeripheralsI²S, POR, PWM, WDTNumber of I/O38Program Memory Size320KB (320K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size42K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP Exposed PadSupplier Device PackagePG-LQFP-64-6                                                                                                                                                              | Core Size                  | 16/32-Bit                                                                        |

| PeripheralsI²S, POR, PWM, WDTNumber of I/O38Program Memory Size320KB (320K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size42K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP Exposed PadSupplier Device PackagePG-LQFP-64-6                                                                                                                                                                                                                                 | Speed                      | 80MHz                                                                            |

| Number of I/O38Program Memory Size320KB (320K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size42K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP Exposed PadSupplier Device PackagePG-LQFP-64-6                                                                                                                                                                                                                                                              | Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Program Memory Size320KB (320K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size42K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP Exposed PadSupplier Device PackagePG-LQFP-64-6                                                                                                                                                                                                                                                                             | Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Program Memory TypeFLASHEEPROM Size-RAM Size42K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP Exposed PadSupplier Device PackagePG-LQFP-64-6                                                                                                                                                                                                                                                                                                                | Number of I/O              | 38                                                                               |

| EEPROM Size-RAM Size42K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP Exposed PadSupplier Device PackagePG-LQFP-64-6                                                                                                                                                                                                                                                                                                                                        | Program Memory Size        | 320KB (320K x 8)                                                                 |

| RAM Size42K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP Exposed PadSupplier Device PackagePG-LQFP-64-6                                                                                                                                                                                                                                                                                                                                                    | Program Memory Type        | FLASH                                                                            |

| Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP Exposed PadSupplier Device PackagePG-LQFP-64-6                                                                                                                                                                                                                                                                                                                                                                   | EEPROM Size                | -                                                                                |

| Data ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP Exposed PadSupplier Device PackagePG-LQFP-64-6                                                                                                                                                                                                                                                                                                                                                                                                      | RAM Size                   | 42K x 8                                                                          |

| Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP Exposed PadSupplier Device PackagePG-LQFP-64-6                                                                                                                                                                                                                                                                                                                                                                                                                              | Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Operating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP Exposed PadSupplier Device PackagePG-LQFP-64-6                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Data Converters            | A/D 9x10b                                                                        |

| Mounting Type     Surface Mount       Package / Case     64-LQFP Exposed Pad       Supplier Device Package     PG-LQFP-64-6                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Oscillator Type            | Internal                                                                         |

| Package / Case     64-LQFP Exposed Pad       Supplier Device Package     PG-LQFP-64-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Supplier Device Package PG-LQFP-64-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Mounting Type              | Surface Mount                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Package / Case             | 64-LQFP Exposed Pad                                                              |

| Purchase URL https://www.e-xfl.com/product-detail/infineon-technologies/xc2238n40f80laakxuma1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Supplier Device Package    | PG-LQFP-64-6                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2238n40f80laakxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|           | N Data Sheet<br>n History: V1.5 2013-02                                                                                                           |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Previous  | Versions:                                                                                                                                         |

| V1.4, 201 | 11-07                                                                                                                                             |

| V1.3, 20  | 10-04                                                                                                                                             |

| V1.2, 200 | )9-12                                                                                                                                             |

| V1.1, 200 | 09-07                                                                                                                                             |

| V1.0, 200 | 09-03 Preliminary                                                                                                                                 |

| Page      | Subjects (major changes since last revision)                                                                                                      |

| 27        | Added AB step marking.                                                                                                                            |

| 79        | Errata SWD_X.P002 implemented: $V_{SWD}$ tolerance boundaries for 5.5 V are changed.                                                              |

| 81        | Clarified "Coding of bit fields LEVxV" descriptions. Matched with Operating Conditions: marked some coding values "out of valid operation range". |

| 82        | Errata FLASH_X.P001 implemented: Test Condition for Flash parameter $N_{\rm ER}$ corrected                                                        |

### Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

### mcdocu.comments@infineon.com

#### Summary of Features

- On-Chip Peripheral Modules

- Two synchronizable A/D Converters with up to 9 channels, 10-bit resolution, conversion time below 1  $\mu$ s, optional data preprocessing (data reduction, range check), broken wire detection

- 16-channel general purpose capture/compare unit (CC2)

- Two capture/compare units for flexible PWM signal generation (CCU6x)

- Multi-functional general purpose timer unit with 5 timers

- Up to 6 serial interface channels to be used as UART, LIN, high-speed synchronous channel (SPI/QSPI), IIC bus interface (10-bit addressing, 400 kbit/s), IIS interface

- On-chip MultiCAN interface (Rev. 2.0B active) with up to 256 message objects (Full CAN/Basic CAN) on 6 CAN node

- On-chip system timer and on-chip real time clock

- Single power supply from 3.0 V to 5.5 V

- · Power reduction and wake-up modes with flexible power management

- Programmable watchdog timer and oscillator watchdog

- Up to 40 general purpose I/O lines

- On-chip bootstrap loaders

- Supported by a full range of development tools including C compilers, macroassembler packages, emulators, evaluation boards, HLL debuggers, simulators, logic analyzer disassemblers, programming boards

- · On-chip debug support via Device Access Port (DAP) or JTAG interface

- 64-pin Green LQFP package, 0.5 mm (19.7 mil) pitch

## **Ordering Information**

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. This ordering code identifies:

- the derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the temperature range:

- SAF-...: -40°C to 85°C

- SAH-...: -40°C to 110°C

- SAK-...: -40°C to 125°C

- the package and the type of delivery.

For ordering codes for the XC223xN please contact your sales representative or local distributor.

This document describes several derivatives of the XC223xN group:

Basic Device Types are readily available and

Special Device Types are only available on request.

As this document refers to all of these derivatives, some descriptions may not apply to a specific product, in particular to the special device types.

For simplicity the term XC223xN is used for all derivatives throughout this document.

#### Summary of Features

## 1.2 Special Device Types

Special device types are only available for high-volume applications on request.

| Derivative <sup>1)</sup> | Flash<br>Memory <sup>2)</sup> | PSRAM<br>DSRAM <sup>3)</sup> | Capt./Comp.<br>Modules <sup>4)</sup> | ADC <sup>5)</sup><br>Chan. | Interfaces <sup>5)</sup>       |

|--------------------------|-------------------------------|------------------------------|--------------------------------------|----------------------------|--------------------------------|

| XC2232N-40FxL            | 320 Kbytes                    | 16 Kbytes<br>16 Kbytes       | CC2<br>CCU60/1                       | 7 + 2                      | 3 CAN Nodes,<br>6 Serial Chan. |

| XC2232N-24FxL            | 192 Kbytes                    | 8 Kbytes<br>8 Kbytes         | CC2<br>CCU60/1                       | 7 + 2                      | 3 CAN Nodes,<br>6 Serial Chan. |

| XC2232N-8FxL             | 64 Kbytes                     | 4 Kbytes<br>4 Kbytes         | CC2<br>CCU60/1                       | 7 + 2                      | 3 CAN Nodes,<br>6 Serial Chan. |

| XC2234N-40FxL            | 320 Kbytes                    | 16 Kbytes<br>16 Kbytes       | CC2<br>CCU60/1                       | 7 + 2                      | 1 CAN Node,<br>2 Serial Chan.  |

| XC2234N-24FxL            | 192 Kbytes                    | 8 Kbytes<br>8 Kbytes         | CC2<br>CCU60/1                       | 7 + 2                      | 1 CAN Node,<br>2 Serial Chan.  |

| XC2234N-16FxL            | 128 Kbytes                    | 4 Kbytes<br>4 Kbytes         | CC2<br>CCU60/1                       | 7 + 2                      | 1 CAN Node,<br>2 Serial Chan.  |

| XC2236N-40FxL            | 320 Kbytes                    | 16 Kbytes<br>16 Kbytes       | CC2<br>CCU60/1                       | 7 + 2                      | 1 CAN Node,<br>4 Serial Chan.  |

| XC2236N-24FxL            | 192 Kbytes                    | 8 Kbytes<br>8 Kbytes         | CC2<br>CCU60/1                       | 7 + 2                      | 1 CAN Node,<br>4 Serial Chan.  |

| XC2236N-16FxL            | 128 Kbytes                    | 4 Kbytes<br>4 Kbytes         | CC2<br>CCU60/1                       | 7 + 2                      | 1 CAN Node,<br>4 Serial Chan.  |

## Table 2 Synopsis of XC223xN Special Device Types

1) x is a placeholder for available speed grade in MHz. Can be 20, 40, 66 or 80.

2) Specific information about the on-chip Flash memory in Table 3.

3) All derivatives additionally provide 8 Kbytes SBRAM and 2 Kbytes DPRAM.

4) Due to bonding limitations in the XC223xN devices only a subset of the CCU61 features can be used. The module has the T12 and T13 timer inputs and no outputs connected. Therefore only CCU61 timers can be triggered from external. This can typically be used for periodic triggering of ADCs.

Specific information about the available channels in Table 5. Analog input channels are listed for each Analog/Digital Converter module separately (ADC0 + ADC1).

#### **General Device Information**

| Table | Table 6         Pin Definitions and Functions (cont'd) |        |      |                                               |  |  |  |

|-------|--------------------------------------------------------|--------|------|-----------------------------------------------|--|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                      |  |  |  |

| 31    | P2.6                                                   | O0 / I | St/B | Bit 6 of Port 2, General Purpose Input/Output |  |  |  |

|       | U0C0_SELO<br>0                                         | 01     | St/B | USIC0 Channel 0 Select/Control 0 Output       |  |  |  |

|       | U0C1_SELO<br>1                                         | O2     | St/B | USIC0 Channel 1 Select/Control 1 Output       |  |  |  |

|       | CC2_CC19                                               | O3 / I | St/B | CAPCOM2 CC19IO Capture Inp./ Compare Out.     |  |  |  |

|       | U0C0_DX2D                                              | I      | St/B | USIC0 Channel 0 Shift Control Input           |  |  |  |

|       | RxDC0D                                                 | I      | St/B | CAN Node 0 Receive Data Input                 |  |  |  |

|       | ESR2_6                                                 | I      | St/B | ESR2 Trigger Input 6                          |  |  |  |

| 35    | P2.7                                                   | O0 / I | St/B | Bit 7 of Port 2, General Purpose Input/Output |  |  |  |

|       | U0C1_SELO<br>0                                         | 01     | St/B | USIC0 Channel 1 Select/Control 0 Output       |  |  |  |

|       | U0C0_SELO<br>1                                         | O2     | St/B | USIC0 Channel 0 Select/Control 1 Output       |  |  |  |

|       | CC2_CC20                                               | O3 / I | St/B | CAPCOM2 CC20IO Capture Inp./ Compare Out.     |  |  |  |

|       | U0C1_DX2C                                              | I      | St/B | USIC0 Channel 1 Shift Control Input           |  |  |  |

|       | RxDC1C                                                 | I      | St/B | CAN Node 1 Receive Data Input                 |  |  |  |

|       | ESR2_7                                                 | I      | St/B | ESR2 Trigger Input 7                          |  |  |  |

| 36    | P2.8                                                   | O0 / I | DP/B | Bit 8 of Port 2, General Purpose Input/Output |  |  |  |

|       | U0C1_SCLK<br>OUT                                       | 01     | DP/B | USIC0 Channel 1 Shift Clock Output            |  |  |  |

|       | EXTCLK                                                 | 02     | DP/B | Programmable Clock Signal Output              |  |  |  |

|       | CC2_CC21                                               | O3 / I | DP/B | CAPCOM2 CC21IO Capture Inp./ Compare Out.     |  |  |  |

|       | U0C1_DX1D                                              | I      | DP/B | USIC0 Channel 1 Shift Clock Input             |  |  |  |

## XC2232N, XC2234N, XC2236N, XC2238N XC2000 Family / Value Line

#### **General Device Information**

| Table | Table 6         Pin Definitions and Functions (cont'd) |        |      |                                                |  |  |  |  |

|-------|--------------------------------------------------------|--------|------|------------------------------------------------|--|--|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                       |  |  |  |  |

| 40    | P10.2                                                  | O0 / I | St/B | Bit 2 of Port 10, General Purpose Input/Output |  |  |  |  |

|       | U0C0_SCLK<br>OUT                                       | 01     | St/B | USIC0 Channel 0 Shift Clock Output             |  |  |  |  |

|       | CCU60_CC6<br>2                                         | O2     | St/B | CCU60 Channel 2 Output                         |  |  |  |  |

|       | CCU60_CC6<br>2INA                                      | I      | St/B | CCU60 Channel 2 Input                          |  |  |  |  |

|       | U0C0_DX1B                                              | I      | St/B | USIC0 Channel 0 Shift Clock Input              |  |  |  |  |

| 42    | P2.10                                                  | O0 / I | St/B | Bit 10 of Port 2, General Purpose Input/Output |  |  |  |  |

|       | U0C1_DOUT                                              | 01     | St/B | USIC0 Channel 1 Shift Data Output              |  |  |  |  |

|       | U0C0_SELO<br>3                                         | O2     | St/B | USIC0 Channel 0 Select/Control 3 Output        |  |  |  |  |

|       | CC2_CC23                                               | O3 / I | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |  |  |  |  |

|       | U0C1_DX0E                                              | I      | St/B | USIC0 Channel 1 Shift Data Input               |  |  |  |  |

|       | CAPINA                                                 | I      | St/B | GPT12E Register CAPREL Capture Input           |  |  |  |  |

| 43    | P10.3                                                  | 00 / I | St/B | Bit 3 of Port 10, General Purpose Input/Output |  |  |  |  |

|       | CCU60_COU<br>T60                                       | O2     | St/B | CCU60 Channel 0 Output                         |  |  |  |  |

|       | U0C0_DX2A                                              | I      | St/B | USIC0 Channel 0 Shift Control Input            |  |  |  |  |

|       | U0C1_DX2A                                              | I      | St/B | USIC0 Channel 1 Shift Control Input            |  |  |  |  |

| 44    | P10.4                                                  | O0 / I | St/B | Bit 4 of Port 10, General Purpose Input/Output |  |  |  |  |

|       | U0C0_SELO<br>3                                         | 01     | St/B | USIC0 Channel 0 Select/Control 3 Output        |  |  |  |  |

|       | CCU60_COU<br>T61                                       | O2     | St/B | CCU60 Channel 1 Output                         |  |  |  |  |

|       | U0C0_DX2B                                              | I      | St/B | USIC0 Channel 0 Shift Control Input            |  |  |  |  |

|       | U0C1_DX2B                                              | I      | St/B | USIC0 Channel 1 Shift Control Input            |  |  |  |  |

|       | ESR1_9                                                 | I      | St/B | ESR1 Trigger Input 9                           |  |  |  |  |

## XC2232N, XC2234N, XC2236N, XC2238N XC2000 Family / Value Line

## **General Device Information**

| Pin | Symbol         | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                         |

|-----|----------------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 56  | P10.13         | 00 / 1 |      | Bit 13 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                                                                  |

|     | U1C0_DOUT      | 01     | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                                                                                                                                                                                                                |

|     | TxDC3          | O2     | St/B | CAN Node 3 Transmit Data Output                                                                                                                                                                                                                                                                                                                  |

|     | U1C0_SELO<br>3 | O3     | St/B | USIC1 Channel 0 Select/Control 3 Output                                                                                                                                                                                                                                                                                                          |

|     | U1C0_DX0D      | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                                 |

| 58  | P10.14         | O0 / I | St/B | Bit 14 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                                                                  |

|     | U1C0_SELO<br>1 | 01     | St/B | USIC1 Channel 0 Select/Control 1 Output                                                                                                                                                                                                                                                                                                          |

|     | U0C1_DOUT      | O2     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                                                                |

|     | ESR2_2         | I      | St/B | ESR2 Trigger Input 2                                                                                                                                                                                                                                                                                                                             |

|     | U0C1_DX0C      | I      | St/B | USIC0 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                                                                 |

|     | RxDC3C         | I      | St/B | CAN Node 3 Receive Data Input                                                                                                                                                                                                                                                                                                                    |

| 59  | P10.15         | O0 / I | St/B | Bit 15 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                                                                  |

|     | U1C0_SELO<br>2 | 01     | St/B | USIC1 Channel 0 Select/Control 2 Output                                                                                                                                                                                                                                                                                                          |

|     | U0C1_DOUT      | 02     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                                                                |

|     | U1C0_DOUT      | O3     | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                                                                                                                                                                                                                |

|     | U0C1_DX1C      | I      | St/B | USIC0 Channel 1 Shift Clock Input                                                                                                                                                                                                                                                                                                                |

| 60  | XTAL2          | 0      | Sp/M | Crystal Oscillator Amplifier Output                                                                                                                                                                                                                                                                                                              |

| 61  | XTAL1          | 1      | Sp/M | <b>Crystal Oscillator Amplifier Input</b><br>To clock the device from an external source, drive XTAL1, while leaving XTAL2 unconnected. Voltages on XTAL1 must comply to the core supply voltage $V_{\text{DDIM}}$ .                                                                                                                             |

|     | ESR2_9         | I      | St/B | ESR2 Trigger Input 9                                                                                                                                                                                                                                                                                                                             |

| 62  | PORST          | 1      | In/B | <b>Power On Reset Input</b><br>A low level at this pin resets the XC223xN<br>completely. A spike filter suppresses input pulses<br><10 ns. Input pulses >100 ns safely pass the filter.<br>The minimum duration for a safe recognition<br>should be 120 ns.<br>An internal pull-up device will hold this pin high<br>when nothing is driving it. |

| Address Area         | Start Loc.           | End Loc.             | Area Size <sup>2)</sup> | Notes |

|----------------------|----------------------|----------------------|-------------------------|-------|

| Reserved for DSRAM   | 00'8000 <sub>H</sub> | 00'9FFF <sub>H</sub> | 8 Kbytes                |       |

| External memory area | 00'000 <sub>H</sub>  | 00'7FFF <sub>H</sub> | 32 Kbytes               |       |

### Table 8XC223xN Memory Map (cont'd)<sup>1)</sup>

Accesses to the shaded areas are reserved. In devices with external bus interface these accesses generate external bus accesses.

- 2) The areas marked with "<" are slightly smaller than indicated, see column "Notes".

- 3) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

- 4) Several pipeline optimizations are not active within the external IO area. This is necessary to control external peripherals properly.

This common memory space consists of 16 Mbytes organized as 256 segments of 64 Kbytes; each segment contains four data pages of 16 Kbytes. The entire memory space can be accessed bytewise or wordwise. Portions of the on-chip DPRAM and the register spaces (ESFR/SFR) additionally are directly bit addressable.

The internal data memory areas and the Special Function Register areas (SFR and ESFR) are mapped into segment 0, the system segment.

The Program Management Unit (PMU) handles all code fetches and, therefore, controls access to the program memories such as Flash memory and PSRAM.

The Data Management Unit (DMU) handles all data transfers and, therefore, controls access to the DSRAM and the on-chip peripherals.

Both units (PMU and DMU) are connected to the high-speed system bus so that they can exchange data. This is required if operands are read from program memory, code or data is written to the PSRAM, code is fetched from external memory, or data is read from or written to external resources. These include peripherals on the LXBus such as USIC or MultiCAN. The system bus allows concurrent two-way communication for maximum transfer performance.

**Up to 16 Kbytes of on-chip Program SRAM (PSRAM)** are provided to store user code or data. The PSRAM is accessed via the PMU and is optimized for code fetches. A section of the PSRAM with programmable size can be write-protected.

Note: The actual size of the PSRAM depends on the quoted device type.

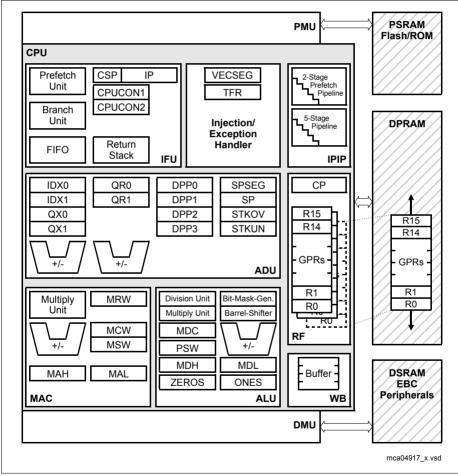

# 3.2 Central Processing Unit (CPU)

The core of the CPU consists of a 5-stage execution pipeline with a 2-stage instructionfetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply-and-divide unit, a bit-mask generator, and a barrel shifter.

Figure 5 CPU Block Diagram

to a dedicated vector table location). The occurrence of a hardware trap is also indicated by a single bit in the trap flag register (TFR). Unless another higher-priority trap service is in progress, a hardware trap will interrupt any ongoing program execution. In turn, hardware trap services can normally not be interrupted by standard or PEC interrupts.

Depending on the package option up to 3 External Service Request (ESR) pins are provided. The ESR unit processes their input values and allows to implement user controlled trap functions (System Requests SR0 and SR1). In this way reset, wakeup and power control can be efficiently realized.

Software interrupts are supported by the 'TRAP' instruction in combination with an individual trap (interrupt) number. Alternatively to emulate an interrupt by software a program can trigger interrupt requests by writing the Interrupt Request (IR) bit of an interrupt control register.

## 3.6 On-Chip Debug Support (OCDS)

The On-Chip Debug Support system built into the XC223xN provides a broad range of debug and emulation features. User software running on the XC223xN can be debugged within the target system environment.

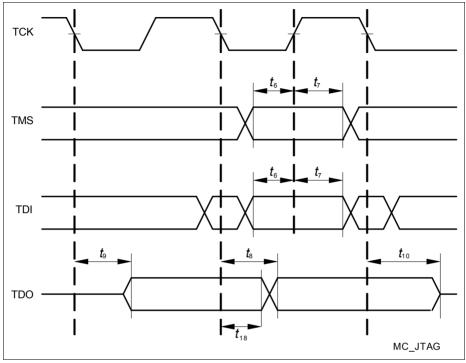

The OCDS is controlled by an external debugging device via the debug interface. This either consists of the 2-pin Device Access Port (DAP) or of the JTAG port conforming to IEEE-1149. The debug interface can be completed with an optional break interface.

The debugger controls the OCDS with a set of dedicated registers accessible via the debug interface (DAP or JTAG). In addition the OCDS system can be controlled by the CPU, e.g. by a monitor program. An injection interface allows the execution of OCDS-generated instructions by the CPU.

Multiple breakpoints can be triggered by on-chip hardware, by software, or by an external trigger input. Single stepping is supported, as is the injection of arbitrary instructions and read/write access to the complete internal address space. A breakpoint trigger can be answered with a CPU halt, a monitor call, a data transfer, or/and the activation of an external signal.

Tracing of data can be obtained via the debug interface, or via the external bus interface for increased performance.

Tracing of program execution is supported by the XC2000 Family emulation device. With this device the DAP can operate on clock rates of up to 20 MHz.

The DAP interface uses two interface signals, the JTAG interface uses four interface signals, to communicate with external circuitry. The debug interface can be amended with two optional break lines.

| Compare Modes           | Function                                                                                                                        |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Mode 2                  | Interrupt-only compare mode;<br>Only one compare interrupt per timer period is generated                                        |

| Mode 3                  | Pin set '1' on match; pin reset '0' on compare timer overflow;<br>Only one compare event per timer period is generated          |

| Double Register<br>Mode | Two registers operate on one pin;<br>Pin toggles on each compare match;<br>Several compare events per timer period are possible |

| Single Event Mode       | Generates single edges or pulses;<br>Can be used with any compare mode                                                          |

#### Table 9Compare Modes (cont'd)

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the compare mode selected.

With its maximum resolution of 2 system clock cycles, the **GPT2 module** provides precise event control and time measurement. It includes two timers (T5, T6) and a capture/reload register (CAPREL). Both timers can be clocked with an input clock which is derived from the CPU clock via a programmable prescaler or with external signals. The counting direction (up/down) for each timer can be programmed by software or altered dynamically with an external signal on a port pin (TxEUD). Concatenation of the timers is supported with the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can also be used to clock the CAPCOM2 timers and to initiate a reload from the CAPREL register.

The CAPREL register can capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN); timer T5 may optionally be cleared after the capture procedure. This allows the XC223xN to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) can also be generated upon transitions of GPT1 timer T3 inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

## **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- UART (asynchronous serial channel)

- module capability: maximum baud rate =  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- module capability: maximum baud rate =  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI (synchronous serial channel with or without data buffer)

- module capability: maximum baud rate =  $f_{SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- IIS (Inter-IC Sound Bus)

- module capability: maximum baud rate =  $f_{SYS}$  / 2

- Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

## 4.3.3 Power Consumption

The power consumed by the XC223xN depends on several factors such as supply voltage, operating frequency, active circuits, and operating temperature. The power consumption specified here consists of two components:

- The switching current  $I_{\rm S}$  depends on the device activity

- The leakage current I<sub>LK</sub> depends on the device temperature

To determine the actual power consumption, always both components, switching current  $I_{\rm S}$  and leakage current  $I_{\rm LK}$  must be added:

$I_{\text{DDP}} = I_{\text{S}} + I_{\text{LK}}.$

Note: The power consumption values are not subject to production test. They are verified by design/characterization.

To determine the total power consumption for dimensioning the external power supply, also the pad driver currents must be considered.

The given power consumption parameters and their values refer to specific operating conditions:

Active mode:

Regular operation, i.e. peripherals are active, code execution out of Flash.

Stopover mode:

Crystal oscillator and PLL stopped, Flash switched off, clock in domain DMP\_1 stopped.

Standby mode:

Voltage domain DMP\_1 switched off completely, power supply control switched off. DMP\_M domain is supplied by ultra low power electronic voltage regulator (ULPEVR). The alternate regulator EVR\_M is switched off.

Note: The maximum values cover the complete specified operating range of all manufactured devices.

The typical values refer to average devices under typical conditions, such as nominal supply voltage, room temperature, application-oriented activity.

After a power reset, the decoupling capacitors for  $V_{\rm DDIM}$  and  $V_{\rm DDI1}$  are charged with the maximum possible current.

For additional information, please refer to **Section 5.2**, **Thermal Considerations**.

Note: Operating Conditions apply.

### Table 18Switching Power Consumption

| Parameter                                                                    | Symbol                  | Values |                             |                                           | Unit | Note /                                                              |

|------------------------------------------------------------------------------|-------------------------|--------|-----------------------------|-------------------------------------------|------|---------------------------------------------------------------------|

|                                                                              |                         | Min.   | Тур.                        | Max.                                      |      | Test Condition                                                      |

| Power supply current<br>(active) with all peripherals<br>active and EVVRs on | I <sub>SACT</sub><br>CC | -      | $6 + 0.6 \\ x f_{SYS}^{1)}$ | 8+1.0<br>x f <sub>SYS</sub> <sup>1)</sup> | mA   | power_mode=<br>active ;<br>voltage_range=<br>both <sup>2)3)4)</sup> |

| Power supply current in standby mode                                         | I <sub>SSB</sub> CC     | -      | 45                          | 125                                       | μA   | power_mode=<br>standby ;<br>voltage_range=<br>lower <sup>5)</sup>   |

|                                                                              |                         | -      | 70                          | 220                                       | μA   | power_mode=<br>standby ;<br>voltage_range=<br>upper <sup>5)</sup>   |

| Power supply current in stopover mode, EVVRs on                              | I <sub>SSO</sub> CC     | -      | 0.7                         | 2.0                                       | mA   | power_mode=<br>stopover ;<br>voltage_range=<br>both <sup>4)</sup>   |

1)  $f_{\rm SYS}$  in MHz

2) The pad supply voltage pins (V<sub>DDPB</sub>) provide the input current for the on-chip EVVRs and the current consumed by the pin output drivers. A small current is consumed because the drivers input stages are switched. In Fast Startup Mode (with the Flash modules deactivated), the typical current is reduced to 3 + 0.6 x f<sub>SVS</sub>.

- 3) Please consider the additional conditions described in section "Active Mode Power Supply Current".

- 4) The pad supply voltage has only a minor influence on this parameter.

- These values are valid if the voltage validation circuits for V<sub>DDPB</sub> (SWD) and V<sub>DDIM</sub> (PVC\_M) are off. Leaving SWD and PVC\_M active adds another 90 μA.

#### Active Mode Power Supply Current

The actual power supply current in active mode not only depends on the system frequency but also on the configuration of the XC223xN's subsystem.

Besides the power consumed by the device logic the power supply pins also provide the current that flows through the pin output drivers.

A small current is consumed because the drivers' input stages are switched.

The IO power domains can be supplied separately. Power domain A ( $V_{\rm DDPA}$ ) supplies the A/D converters and Port 6. Power domain B ( $V_{\rm DDPB}$ ) supplies the on-chip EVVRs and all other ports.

| Parameter                                            | Symbol              | Values |      |       | Unit | Note /                                       |

|------------------------------------------------------|---------------------|--------|------|-------|------|----------------------------------------------|

|                                                      |                     | Min.   | Тур. | Max.  | 1    | Test Condition                               |

| Leakage supply current<br>(DMP_1 off) <sup>1)</sup>  | I <sub>LK0</sub> CC | -      | 20   | 35    | μA   | <i>T</i> <sub>J</sub> = 25 °C <sup>2)</sup>  |

|                                                      |                     | -      | 115  | 330   | μA   | <i>T</i> <sub>J</sub> = 85 °C <sup>2)</sup>  |

|                                                      |                     | -      | 270  | 880   | μA   | <i>T</i> <sub>J</sub> = 125 °C <sup>2)</sup> |

|                                                      |                     | -      | 420  | 1,450 | μA   | <i>T</i> <sub>J</sub> = 150 °C <sup>2)</sup> |

| Leakage supply current (DMP_1 powered) <sup>1)</sup> | I <sub>LK1</sub> CC | -      | 0.03 | 0.04  | mA   | $T_{\rm J}$ = 25 °C <sup>2)</sup>            |

|                                                      |                     | -      | 0.5  | 1.2   | mA   | <i>T</i> <sub>J</sub> = 85 °C <sup>2)</sup>  |

|                                                      |                     | -      | 1.9  | 5.5   | mA   | <i>T</i> <sub>J</sub> = 125 °C <sup>2)</sup> |

|                                                      |                     | -      | 3.9  | 12.2  | mA   | <i>T</i> <sub>J</sub> = 150 °C <sup>2)</sup> |

### Table 19 Leakage Power Consumption

1) The supply current caused by leakage depends mainly on the junction temperature and the supply voltage. The temperature difference between the junction temperature  $T_J$  and the ambient temperature  $T_A$  must be taken into account. As this fraction of the supply current does not depend on device activity, it must be added to other power consumption values.

All inputs (including pins configured as inputs) are set at 0 V to 0.1 V or at V<sub>DDP</sub> - 0.1 V to V<sub>DDP</sub> and all outputs (including pins configured as outputs) are disconnected.

Note: A fraction of the leakage current flows through domain DMP\_A (pin  $V_{DDPA}$ ). This current can be calculated as 7,000 × e<sup>- $\alpha$ </sup>, with  $\alpha$  = 5000 / (273 + 1.3 ×  $T_{J}$ ). For  $T_{J}$  = 150°C, this results in a current of 160  $\mu$ A.

### Leakage Power Consumption Calculation

The leakage power consumption can be calculated according to the following formulas:

$I_{LK0}$  = 500,000 ×  $e^{-\alpha}$  with  $\alpha$  = 3000 / (273 + B ×  $T_{J}$ )

Parameter B must be replaced by

- 1.0 for typical values

- 1.6 for maximum values

$I_{IK1} = 530,000 \times e^{-\alpha}$  with  $\alpha = 5000 / (273 + B \times T_{J})$

Parameter B must be replaced by

- 1.0 for typical values

- 1.3 for maximum values

- 4) The broken wire detection delay against V<sub>AREF</sub> is measured in numbers of consecutive precharge cycles at a conversion rate of not more than 10 μs. This function is influenced by leakage current, in particular at high temperature. Result above 80% (332<sub>µ</sub>)

- 5) TUE is tested at V<sub>AREF</sub> = V<sub>DDPA</sub> = 5.0 V, V<sub>AGND</sub> = 0 V. It is verified by design for all other voltages within the defined voltage range. The specified TUE is valid only if the absolute sum of input overload currents on analog port pins (see I<sub>OV</sub> specification) does not exceed 10 mA, and if V<sub>AREF</sub> and V<sub>AGND</sub> remain stable during the measurement time.

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

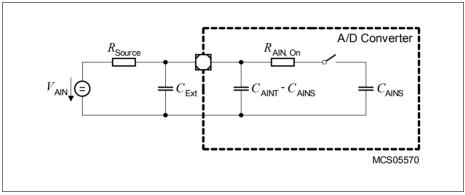

Figure 16 Equivalent Circuitry for Analog Inputs

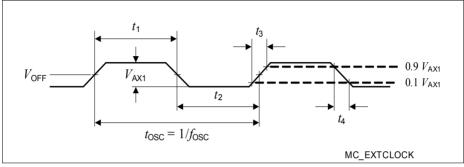

- 1) The amplitude voltage  $V_{AX1}$  refers to the offset voltage  $V_{OFF}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{IX1}$ .

- 2) Overload conditions must not occur on pin XTAL1.

#### Figure 21 External Clock Drive XTAL1

Note: For crystal or ceramic resonator operation, it is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for oscillator operation.

The manufacturers of crystals and ceramic resonators offer an oscillator evaluation service. This evaluation checks the crystal/resonator specification limits to ensure a reliable oscillator operation.

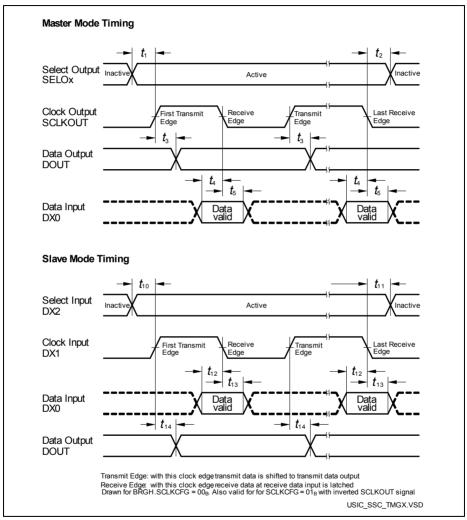

Figure 22 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration where the slave select signal is low-active and the serial clock signal is not shifted and not inverted.

Figure 27 JTAG Timing

## XC2232N, XC2234N, XC2236N, XC2238N XC2000 Family / Value Line

### Package and Reliability

## Package Outlines

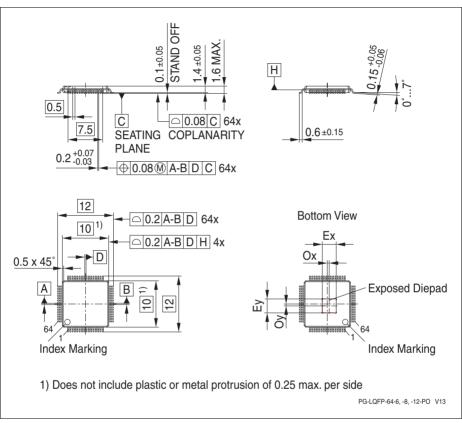

Figure 28 PG-LQFP-64-6 (Plastic Green Thin Quad Flat Package)

All dimensions in mm.

You can find complete information about Infineon packages, packing and marking in our Infineon Internet Page "Packages": http://www.infineon.com/packages