Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | 8051                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 36                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LCC (J-Lead)                                                       |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89v664fa-512 |

|                            |                                                                       |

■ Idle mode

# 2.3 Comparison to the P89C660/662/664 devices

- **SPI interface**. The P89V660/662/664 devices include an SPI interface that was not present on the P89C660/662/664 devices.

- **Dual I2C-bus interfaces**. The P89V660/662/664 devices have two I<sup>2</sup>C-bus interfaces. The P89C660/662/664 devices have one.

- More I/O pins. The P89V660/662/664 devices have an additional four-bit I/O port, Port 4.

- The **6x/12x mode** on the P89V660/662/664 devices is **programmable** and erasable **using ISP** and IAP as well as parallel programmer mode. The P89C660/662/664 devices could only be switched using parallel programmer mode.

- Smaller block sizes. The smallest block size on the P89C660/662/664 devices was 8 kB. The P89V660/662/664 devices have a page size of 128 B. These small pages can be erased and reprogrammed using IAP function calls making use of the code memory for non-volatile data storage practical. Each page erase is 30 ms or less. The IAP and ISP code in P89V660/662/664 devices support these 128-byte page operations. In addition, the IAP and ISP code uses multiple page erase operations to emulate the erasing of the larger block sizes (8 kB and 16 kB to maintain firmware compatibility).

- Status bit versus Status byte. The P89V660/662/664 devices used a Status byte to control the automatic entry into ISP mode following a reset. On the P89V660/662/664 devices this has changed to a single Status bit. Since the ISP entry was based on the zero/non-zero value of the Status byte this is an almost identical operation on the P89V660/662/664 devices.

- Faster block erase. The erase time for the entire user code memory of the P89V660/662/664 devices is 150 ms.

# 3. Ordering information

Table 1. Ordering information

| Type number | Package |                                                                                     |          |  |  |  |  |  |  |

|-------------|---------|-------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|

|             | Name    | Description                                                                         | Version  |  |  |  |  |  |  |

| P89V662FA   | PLCC44  | plastic leaded chip carrier; 44 leads                                               | SOT187-2 |  |  |  |  |  |  |

| P89V662FBC  | TQFP44  | plastic thin quad flat package; 44 leads; body $10 \times 10 \times 1.0 \text{ mm}$ | SOT376-1 |  |  |  |  |  |  |

| P89V664FA   | PLCC44  | plastic leaded chip carrier; 44 leads                                               | SOT187-2 |  |  |  |  |  |  |

| P89V664FBC  | TQFP44  | plastic thin quad flat package; 44 leads; body $10 \times 10 \times 1.0 \text{ mm}$ | SOT376-1 |  |  |  |  |  |  |

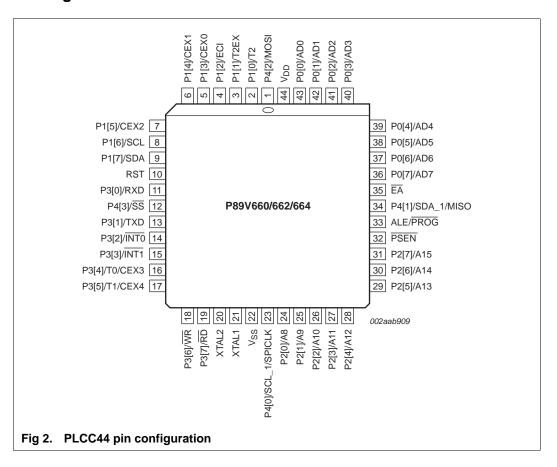

# 5. Pinning information

# 5.1 Pinning

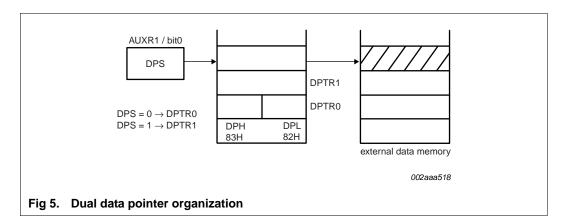

Table 8. AUXR1 - Auxiliary register 1 (address A2H) bit allocation Not bit addressable: Reset value 00H

| Bit    | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0   |

|--------|---|---|---|---|-----|---|---|-----|

| Symbol | - | - | - | - | GF2 | 0 | - | DPS |

Table 9. AUXR1 - Auxiliary register 1 (address A2H) bit description

|        |        | , 9                                                                                                                                            |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Symbol | Description                                                                                                                                    |

| 7 to 4 | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                |

| 3      | GF2    | General purpose user-defined flag.                                                                                                             |

| 2      | 0      | This bit contains a hard-wired '0'. Allows toggling of the DPS bit by incrementing AUXR1, without interfering with other bits in the register. |

| 1      | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                |

| 0      | DPS    | Data pointer select. Chooses one of two Data Pointers for use by the program. See text for details.                                            |

#### 6.2.3 Reset

At initial power-up, the port pins will be in a random state until the oscillator has started and the internal reset algorithm has weakly pulled all pins high. Powering up the device without a valid reset could cause the MCU to start executing instructions from an indeterminate location. Such undefined states may inadvertently corrupt the code in the flash. A system reset will not affect the on-chip RAM while the device is running, however, the contents of the on-chip RAM during power-up are indeterminate.

When power is applied to the device, the RST pin must be held high long enough for the oscillator to start-up (usually several milliseconds for a low frequency crystal), in addition to two machine cycles for a valid power-on reset. An example of a method to extend the RST signal is to implement a RC circuit by connecting the RST pin to  $V_{DD}$  through a 10  $\mu F$  capacitor and to  $V_{SS}$  through an 8.2  $k\Omega$  resistor as shown in Figure 6.

During initial power the POF flag in the PCON register is set to indicate an initial power-up condition. The POF flag will remain active until cleared by software.

Following a reset condition, under normal conditions, the MCU will start executing code from address 0000H in the user's code memory. However if either the PSEN pin was low when reset was exited, or the Status Bit was set = 1, the MCU will start executing code from the boot address. The boot address is formed using the value of the boot vector as the high byte of the address and 00H as the low byte.

P89V660\_662\_664

All information provided in this document is subject to legal disclaimers.

based on the oscillator frequency. The ISP feature requires that an initial character (an uppercase U) be sent to the P89V660/662/664 to establish the baud rate. The ISP firmware provides auto-echo of received characters. Once baud rate initialization has been performed, the ISP firmware will only accept Intel Hex-type records. Intel Hex records consist of ASCII characters used to represent hexadecimal values and are summarized below:

#### :NNAAAARRDD..DDCC<crlf>

In the Intel Hex record, the 'NN' represents the number of data bytes in the record. The P89V660/662/664 will accept up to 32 data bytes. The 'AAAA' string represents the address of the first byte in the record. If there are zero bytes in the record, this field is often set to 0000. The 'RR' string indicates the record type. A record type of '00' is a data record. A record type of '01' indicates the end-of-file mark. In this application, additional record types will be added to indicate either commands or data for the ISP facility.

The maximum number of data bytes in a record is limited to 32 (decimal). ISP commands are summarized in <u>Table 11</u>. As a record is received by the P89V660/662/664, the information in the record is stored internally and a checksum calculation is performed. The operation indicated by the record type is not performed until the entire record has been received. Should an error occur in the checksum, the P89V660/662/664 will send an 'X' out the serial port indicating a checksum error. If the checksum calculation is found to match the checksum in the record, then the command will be executed. In most cases, successful reception of the record will be indicated by transmitting a '.' character out the serial port.

Table 11. ISP hex record formats

| Record type | Command/data function                               |

|-------------|-----------------------------------------------------|

| 00          | Program User Code Memory                            |

|             | :nnaaaa00ddddcc                                     |

|             | Where:                                              |

|             | nn = number of bytes to program                     |

|             | aaaa = address                                      |

|             | dddd = data bytes                                   |

|             | cc = checksum                                       |

|             | Example:                                            |

|             | :0900000010203040506070809CA                        |

| 01          | End of File (EOF), no operation                     |

|             | :xxxxxx01cc                                         |

|             | Where:                                              |

|             | xxxxxx = required field but value is a 'don't care' |

|             | cc = checksum                                       |

|             | Example:                                            |

|             | :0000001FF                                          |

| 02          | not used                                            |

# 6.4.1 I<sup>2</sup>C-bus data register

S1DAT register contains the data to be transmitted or the data received. The CPU can read and write to this 8-bit register while it is not in the process of shifting a byte. Thus this register should only be accessed when the SI bit is set. Data in S1DAT remains stable as long as the SI bit is set. Data in S1DAT is always shifted from right to left: the first bit to be transmitted is the MSB (bit 7), and after a byte has been received, the first bit of received data is located at the MSB of S1DAT.

## 6.4.2 I<sup>2</sup>C-bus slave address register

The S1ADR register is readable and writable, and is only used when the I<sup>2</sup>C-bus interface is set to slave mode. In master mode, this register has no effect. The LSB of S1ADR is general call bit. When this bit is set, the general call address (00H) is recognized.

Table 13. I<sup>2</sup>C-bus slave address register (S1ADR - address DBH) bit allocation

| Bit    | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0    |

|--------|---------|---------|---------|---------|---------|---------|---------|------|

| Symbol | S1ADR.6 | S1ADR.5 | S1ADR.4 | S1ADR.3 | S1ADR.2 | S1ADR.1 | S1ADR.0 | S1GC |

| Reset  | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0    |

Table 14. I<sup>2</sup>C-bus slave address register (S1ADR - address DBH) bit description

| Bit | Symbol   | Description                                                                                        |

|-----|----------|----------------------------------------------------------------------------------------------------|

| 7:1 | S1ADR7:1 | 7 bit own slave address. When in master mode, the contents of this register has no effect.         |

| 0   | S1GC     | General call bit. When set, the general call address (00H) is recognized, otherwise it is ignored. |

#### 6.4.3 I<sup>2</sup>C-bus control register

The CPU can read and write this register. There are two bits are affected by hardware: the SI bit and the STO bit. The SI bit is set by hardware and the STO bit is cleared by hardware.

CR2:0 determines the SCL source and frequency when the I<sup>2</sup>C-bus is in master mode. In slave mode these bits are ignored and the bus will automatically synchronize with any clock frequency up to 100 kHz from the master I<sup>2</sup>C-bus device. Timer 1 should be programmed by the user in 8 bit auto-reload mode (Mode 2) when used as the SCL source. See Table 17.

The STA bit is START flag. Setting this bit causes the I<sup>2</sup>C-bus interface to enter master mode and attempt transmitting a START condition or transmitting a repeated START condition when it is already in master mode.

The STO bit is STOP flag. Setting this bit causes the I<sup>2</sup>C-bus interface to transmit a STOP condition in master mode, or recovering from an error condition in slave mode.

If the STA and STO are both set, then a STOP condition is transmitted to the I<sup>2</sup>C-bus if it is in master mode, and transmits a START condition afterwards. If it is in slave mode, an internal STOP condition will be generated, but it is not transmitted to the bus.

Table 17. I<sup>2</sup>C-bus clock rates ...continued

| CR2:0 |              | Bit freq    |               |             |                             |                       |

|-------|--------------|-------------|---------------|-------------|-----------------------------|-----------------------|

|       | 6-clock mode |             | 12-clock mode | е           | f <sub>osc</sub> divided by |                       |

|       | 6 MHz        | 12 MHZ      | 6 MHz         | 12 MHz      | 6X                          | 12X                   |

| 101   | 100          | 200         | 50            | 100         | 60                          | 120                   |

| 110   | 200          | 400         | 100           | 200         | 30                          | 60                    |

| 111   | 0.49 < 62.5  | 0.98 < 50.0 | 0.24 < 62.5   | 0.49 < 62.5 | 48 x (Timer 1 reload)       | 96 x (Timer 1 reload) |

# 6.4.4 I<sup>2</sup>C-bus status register

This is a read-only register. It contains the status code of the  $I^2C$ -bus interface. The least three bits are always 0. There are 26 possible status codes. When the code is F8H, there is no relevant information available and SI bit is not set. All other 25 status codes correspond to defined  $I^2C$ -bus states. When any of these states entered, the SI bit will be set. Refer to Table 22 to Table 25 for details.

Table 18. I<sup>2</sup>C-bus status register (S1STA - address D9H) bit allocation

| Bit    | 7    | 6    | 5    | 4    | 3    | 2 | 1 | 0 |

|--------|------|------|------|------|------|---|---|---|

| Symbol | SC.4 | SC.3 | SC.2 | SC.1 | SC.0 | 0 | 0 | 0 |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0 | 0 | 0 |

Table 19. I<sup>2</sup>C-bus status register (S1STA - address D9H) bit description

| Bit | Symbol  | Description                       |

|-----|---------|-----------------------------------|

| 7:3 | SC[4:0] | l <sup>2</sup> C-bus Status code. |

| 2:0 | -       | Reserved, are always set to 0.    |

### 6.4.5 I<sup>2</sup>C-bus operation modes

#### 6.4.5.1 Master transmitter mode

In this mode data is transmitted from master to slave. Before the Master Transmitter mode can be entered, S1CON must be initialized as follows:

Table 20. I<sup>2</sup>C-bus control register (S1CON - address D8H)

| Bit    | 7        | 6    | 5   | 4   | 3  | 2  | 1        | 0        |

|--------|----------|------|-----|-----|----|----|----------|----------|

| Symbol | CR2      | ENS1 | STA | STO | SI | AA | CR1      | CR0      |

| Value  | bit rate | 1    | 0   | 0   | 0  | Х  | bit rate | bit rate |

CR2:0 define the bit rate (See <u>Table 17</u>). ENS1 must be set to 1 to enable the I<sup>2</sup>C-bus function. If the AA bit is 0, it will not acknowledge its own slave address or the general call address in the event of another device becoming master of the bus and it can not enter slave mode. STA, STO, and SI bits must be cleared to 0.

The first byte transmitted contains the slave address of the receiving device (7 bits) and the data direction bit. In this case, the data direction bit (R/W) will be logic 0 indicating a write. Data is transmitted 8 bits at a time. After each byte is transmitted, an acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

Table 25. Slave transmitter mode ...continued

| Status code | Status of the                                      | Application softw  | are re   | sponse | Next action taken by I <sup>2</sup> C-bus |    |                                                                                                                                                                                                    |

|-------------|----------------------------------------------------|--------------------|----------|--------|-------------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (S1STA)     | I <sup>2</sup> C-bus<br>hardware                   | to/from S1DAT      | to S1CON |        |                                           |    | hardware                                                                                                                                                                                           |

|             | naraware                                           |                    | STA      | STO    | SI                                        | AA |                                                                                                                                                                                                    |

| СОН         | Data byte in<br>S1DAT has been<br>transmitted; NOT | No S1DAT action or | 0        | 0      | 0                                         | 0  | Switched to not addressed SLA mode; no recognition of own SLA or General call address.                                                                                                             |

|             | ACK has been received.                             | no S1DAT action or | 0        | 0      | 0                                         | 1  | Switched to not addressed SLA mode; Own slave address will be recognized; General call address will be recognized if S1ADR.0 = 1.                                                                  |

|             |                                                    | no S1DAT action or | 1        | 0      | 0                                         | 0  | Switched to not addressed SLA mode; no recognition of own SLA or General call address. A START condition will be transmitted when the bus becomes free.                                            |

|             |                                                    | no S1DAT action    | 1        | 0      | 0                                         | 1  | Switched to not addressed SLA mode; Own slave address will be recognized; General call address will be recognized if S1ADR.0 = 1. A START condition will be transmitted when the bus becomes free. |

| C8H         | Last data byte in S1DAT has been transmitted       | No S1DAT action or | 0        | 0      | 0                                         | 0  | Switched to not addressed SLA mode; no recognition of own SLA or General call address.                                                                                                             |

|             | (AA = 0); ACK<br>has been<br>received.             | no S1DAT action or | 0        | 0      | 0                                         | 1  | Switched to not addressed SLA mode; Own slave address will be recognized; General call address will be recognized if S1ADR.0 = 1.                                                                  |

|             |                                                    | no S1DAT action or | 1        | 0      | 0                                         | 0  | Switched to not addressed SLA mode; no recognition of own SLA or General call address. A START condition will be transmitted when the bus becomes free.                                            |

|             |                                                    | no S1DAT action    | 1        | 0      | 0                                         | 1  | Switched to not addressed SLA mode; Own slave address will be recognized; General call address will be recognized if S1ADR.0 = 1. A START condition will be transmitted when the bus becomes free. |

# 6.5 Timers/counters 0 and 1

The two 16-bit Timer/Counter registers: Timer 0 and Timer 1 can be configured to operate either as timers or event counters (see Table 26 and Table 27).

In the 'Timer' function, the register is incremented every machine cycle. Thus, one can think of it as counting machine cycles. Since a machine cycle consists of six oscillator periods, the count rate is  $\frac{1}{6}$  of the oscillator frequency.

Table 38. SCON - Serial port control register (address 98H) bit description ...continued

| Bit | Symbol | Description                                                                                                                                                                                                     |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | TB8    | The 9th data bit that will be transmitted in Modes 2 and 3. Set or clear by software as desired.                                                                                                                |

| 2   | RB8    | In Modes 2 and 3, is the 9th data bit that was received. In Mode 1, it $SM2 = 0$ , RB8 is the stop bit that was received. In Mode 0, RB8 is undefined.                                                          |

| 1   | TI     | Transmit interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or at the stop bit in the other modes, in any serial transmission. Must be cleared by software.                              |

| 0   | RI     | Receive interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or approximately halfway through the stop bit time in all other modes. (See SM2 for exceptions). Must be cleared by software. |

Table 39. SCON - Serial port control register (address 98H) SM0/SM1 mode definition

| SM0, SM1 | UART mode         | Baud rate                        |

|----------|-------------------|----------------------------------|

| 0 0      | 0: shift register | CPU clock / 6                    |

| 0 1      | 1: 8-bit UART     | variable                         |

| 1 0      | 2: 9-bit UART     | CPU clock / 32 or CPU clock / 16 |

| 11       | 3: 9-bit UART     | variable                         |

# 6.7.5 Framing error

Framing error (FE) is reported in the SCON.7 bit if SMOD0 (PCON.6) = 1. If SMOD0 = 0, SCON.7 is the SM0 bit for the UART, it is recommended that SM0 is set up before SMOD0 is set to '1'.

## 6.7.6 More about UART mode 1

Reception is initiated by a detected 1-to-0 transition at RXD. For this purpose RXD is sampled at a rate of 16 times whatever baud rate has been established. When a transition is detected, the divide-by-16 counter is immediately reset to align its rollovers with the boundaries of the incoming bit times.

The 16 states of the counter divide each bit time into 16ths. At the 7th, 8th, and 9th counter states of each bit time, the bit detector samples the value of RXD. The value accepted is the value that was seen in at least 2 of the 3 samples. This is done for noise rejection. If the value accepted during the first bit time is not 0, the receive circuits are reset and the unit goes back to looking for another 1-to-0 transition. This is to provide rejection of false start bits. If the start bit proves valid, it is shifted into the input shift register, and reception of the rest of the frame will proceed.

The signal to load SBUF and RB8, and to set RI, will be generated if, and only if, the following conditions are met at the time the final shift pulse is generated: (a) RI = 0, and (b) Either SM2 = 0, or the received stop bit = 1.

If either of these two conditions is not met, the received frame is irretrievably lost. If both conditions are met, the stop bit goes into RB8, the 8 data bits go into SBUF, and RI is activated.

#### 6.7.7 More about UART modes 2 and 3

Reception is performed in the same manner as in mode 1.

50 of 90

In a more complex system the following could be used to select slaves 1 and 2 while excluding slave 0:

Example 1, slave 0:

$SADDR = 1100\ 0000$

$$\frac{\text{SADEN} = 1111\ 1001}{\text{Given} = 1100\ 0\text{XX}0} \tag{6}$$

Example 2, slave 1:

SADDR = 11100000

$$\frac{\text{SADEN} = 1111\ 1010}{\text{Given} = 1110\ 0X0X} \tag{7}$$

Example 2, slave 2:

SADDR = 11000000

$$\frac{\text{SADEN} = 1111\ 1100}{\text{Given} = 1100\ 00XX}$$

(8)

In the above example the differentiation among the 3 slaves is in the lower 3 address bits. Slave 0 requires that bit 0 = 0 and it can be uniquely addressed by 1110 0110. Slave 1 requires that bit 1 = 0 and it can be uniquely addressed by 1110 0101. Slave 2 requires that bit 2 = 0 and its unique address is 1110 0011. To select Slaves 0 and 1 and exclude Slave 2 use address 1110 0100, since it is necessary to make bit 2 = 1 to exclude slave 2. The Broadcast Address for each slave is created by taking the logical OR of SADDR and SADEN. Zeros in this result are treated as don't-cares. In most cases, interpreting the don't-cares as ones, the broadcast address will be FF hexadecimal. Upon reset SADDR and SADEN are loaded with 0s. This produces a given address of all 'don't cares' as well as a Broadcast address of all 'don't cares'. This effectively disables the Automatic Addressing mode and allows the microcontroller to use standard UART drivers which do not make use of this feature.

# 6.8 Serial Peripheral Interface (SPI)

#### 6.8.1 SPI features

- Master or slave operation

- 10 MHz bit frequency (max)

- · LSB first or MSB first data transfer

- Four programmable bit rates

- End of transmission (SPIF)

- Write collision flag protection (WCOL)

- Wake-up from Idle mode (slave mode only)

### 6.8.2 SPI description

The serial peripheral interface allows high-speed synchronous data transfer between the P89V660/662/664 and peripheral devices or between several P89V660/662/664 devices. Figure 23 shows the correspondence between master and slave SPI devices. The

P89V660\_662\_664

All information provided in this document is subject to legal disclaimers.

Table 41. SPCR - SPI control register (address D5H) bit description ...continued

| Bit | Symbol | Description                                                                                                                                                         |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | СРНА   | Clock Phase control bit. $1 = \text{shift triggered on the trailing edge of the clock}$ ; $0 = \text{shift triggered on the leading edge of the clock}$ .           |

| 1   | SPR1   | SPI Clock Rate Select bit 1. Along with SPR0 controls the SPICLK rate of the device when a master. SPR1 and SPR0 have no effect on the slave. See <u>Table 42</u> . |

| 0   | SPR0   | SPI Clock Rate Select bit 0. Along with SPR1 controls the SPICLK rate of the device when a master. SPR1 and SPR0 have no effect on the slave. See <u>Table 42</u> . |

Table 42. SPCR - SPI control register (address D5H) clock rate selection

|      | _    |                                      |               |  |

|------|------|--------------------------------------|---------------|--|

| SPR1 | SPR0 | SPICLK = f <sub>osc</sub> divided by |               |  |

|      |      | 6-clock mode                         | 12-clock mode |  |

| 0    | 0    | 2                                    | 4             |  |

| 0    | 1    | 8                                    | 16            |  |

| 1    | 0    | 32                                   | 64            |  |

| 1    | 1    | 64                                   | 128           |  |

Table 43. SPSR - SPI status register (address AAH) bit allocation

Bit addressable; Reset source(s): any reset; Reset value: 0000 0000B

| Bit    | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|------|------|---|---|---|---|---|---|

| Symbol | SPIF | WCOL | - | - | - | - | - | - |

Table 44. SPSR - SPI status register (address AAH) bit description

| Bit    | Symbol | Description                                                                                                                                                             |

|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | SPIF   | SPI interrupt flag. Upon completion of data transfer, this bit is set to '1'. If SPIE = 1 and ES3 = 1, an interrupt is then generated. This bit is cleared by software. |

| 6      | WCOL   | Write Collision Flag. Set if the SPI data register is written to during data transfer. This bit is cleared by software.                                                 |

| 5 to 0 | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                                         |

P89V660\_662\_664

All information provided in this document is subject to legal disclaimers.

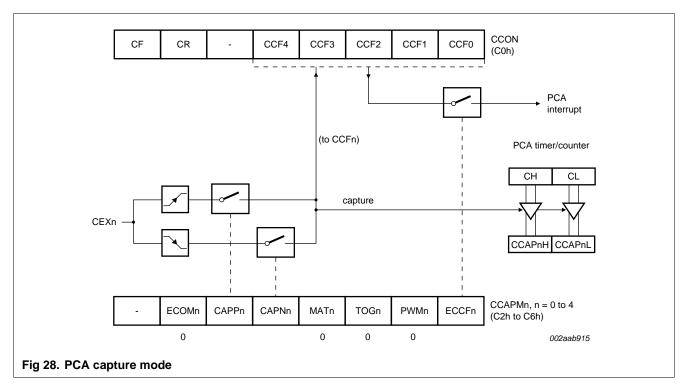

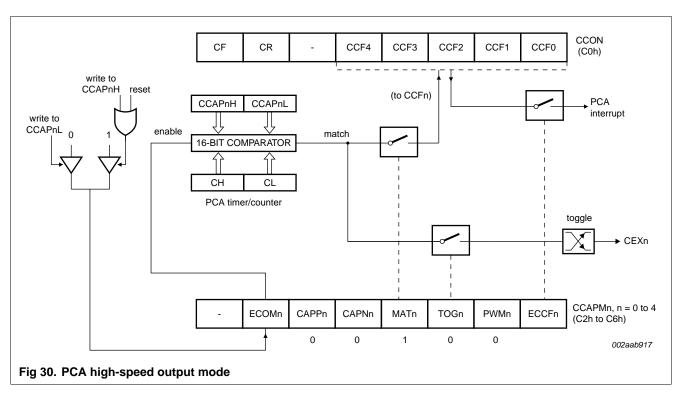

If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated.

#### 6.10.2 16-bit software timer mode

The PCA modules can be used as software timers (<u>Figure 29</u>) by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set.

#### 6.10.4 Pulse width modulator mode

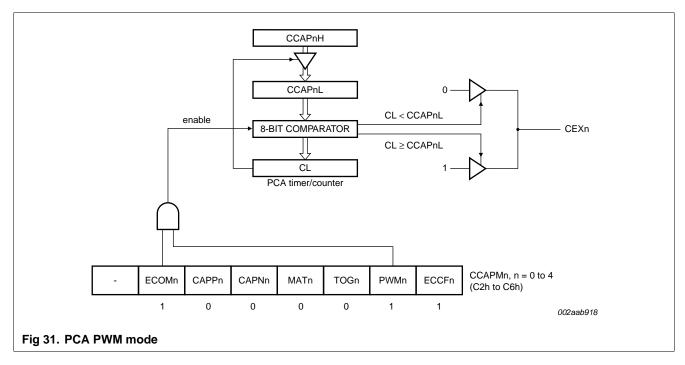

All of the PCA modules can be used as PWM outputs (<u>Figure 31</u>). Output frequency depends on the source for the PCA timer.

All of the modules will have the same frequency of output because they all share one and only PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPnL. When the value of the PCA CL SFR is less than the

P89V660\_662\_664

All information provided in this document is subject to legal disclaimers.

# 7. Limiting values

### Table 69. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to  $V_{SS}$  unless otherwise noted.

| Symbol                 | Parameter                                     | Conditions                                                         | Min  | Max                   | Unit |

|------------------------|-----------------------------------------------|--------------------------------------------------------------------|------|-----------------------|------|

| T <sub>amb(bias)</sub> | bias ambient temperature                      |                                                                    | -55  | +125                  | °C   |

| T <sub>stg</sub>       | storage temperature                           |                                                                    | -65  | +150                  | °C   |

| V <sub>I</sub>         | input voltage                                 | on EA pin to V <sub>SS</sub>                                       | -0.5 | 14                    | V    |

| V <sub>n</sub>         | voltage on any other pin                      | except $V_{SS}$ , with respect to $V_{DD}$                         | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| I <sub>OL(I/O)</sub>   | LOW-level output current per input/output pin |                                                                    | -    | 15                    | mA   |

| P <sub>tot(pack)</sub> | total power dissipation (per package)         | based on package heat<br>transfer, not device power<br>consumption | -    | 1.5                   | W    |

# 8. Static characteristics

Table 70. Static characteristics

$T_{amb} = -40$  °C to +85 °C;  $V_{DD} = 4.5$  V to 5.5 V;  $V_{SS} = 0$  V

| Symbol                                   | Parameter                   | Conditions                                                               |                 | Min                      | Тур | Max                   | Unit         |

|------------------------------------------|-----------------------------|--------------------------------------------------------------------------|-----------------|--------------------------|-----|-----------------------|--------------|

| n <sub>endu(fl)</sub>                    | endurance of flash memory   | JEDEC Standard A117                                                      | [1]             | 10000                    | -   | -                     | cycles       |

| t <sub>ret(fl)</sub>                     | flash memory retention time | JEDEC Standard A103                                                      | [1]             | 100                      | -   | -                     | years        |

| I <sub>latch</sub>                       | I/O latch-up current        | JEDEC Standard 78                                                        | [1]             | 100 + I <sub>DD</sub>    | -   | -                     | mA           |

| $V_{th(HL)}$                             | HIGH-LOW threshold voltage  | except SCL, SDA                                                          |                 | -0.5                     | -   | $0.2V_{DD} - 0.1$     | V            |

| $V_{IL}$                                 | LOW-level input voltage     | SCL, SDA                                                                 |                 | -0.5                     | -   | $0.3V_{DD}$           | V            |

| $V_{\text{th(LH)}}$                      | LOW-HIGH threshold voltage  | except SCL, SDA, XTAL1, RST                                              |                 | 0.2V <sub>DD</sub> + 0.9 | -   | V <sub>DD</sub> + 0.5 | V            |

| V <sub>IH</sub>                          | HIGH-level input voltage    | SCL, SDA                                                                 |                 | $0.7V_{DD}$              | -   | $V_{DD} + 0.5$        | V            |

|                                          |                             | XTAL1, RST                                                               |                 | $0.7V_{DD}$              | -   | 6.0                   | V            |

| V <sub>OL</sub> LOW-level output voltage |                             | $V_{DD} = 4.5 \text{ V, except, } \overline{\text{PSEN}},$ ALE, SCL, SDA | [2][3][4]       |                          |     |                       |              |

|                                          |                             | I <sub>OL</sub> = 1.6 mA                                                 |                 | -                        | -   | 0.4                   | V            |

|                                          |                             | V <sub>DD</sub> = 4.5 V, ALE, PSEN                                       |                 |                          |     |                       |              |

|                                          |                             | I <sub>OL</sub> = 3.2 mA                                                 |                 | -                        | -   | 0.45                  | V            |

|                                          |                             | V <sub>DD</sub> = 4.5 V, SCL, SDA                                        |                 |                          |     |                       |              |

|                                          |                             | $I_{OL} = 3.0 \text{ mA}$                                                |                 | -                        | -   | 0.4                   | V            |

| V <sub>OH</sub>                          | HIGH-level output voltage   | V <sub>DD</sub> = 4.5 V, ports 1, 2, 3, 4                                | [5]             |                          |     |                       |              |

|                                          |                             | $I_{OH} = -30 \mu A$                                                     |                 | $V_{DD}-0.7$             | -   | -                     | V            |

|                                          |                             | V <sub>DD</sub> = 4.5 V, Port 0 in<br>External Bus mode, ALE,<br>PSEN    |                 |                          |     |                       |              |

|                                          |                             | $I_{OH} = -3.2 \text{ mA}$                                               |                 | V <sub>DD</sub> - 0.7    | -   | -                     | V            |

| I <sub>IL</sub>                          | LOW-level input current     | V <sub>I</sub> = 0.4 V, ports 1, 2, 3, 4                                 |                 | -1                       | -   | -75                   | μΑ           |

| P89V660_662_664                          | 4                           | All information provided in this document is subject to                  | legal disclaime | rs.                      |     | © NXP B.V. 2011. Al   | rights reser |

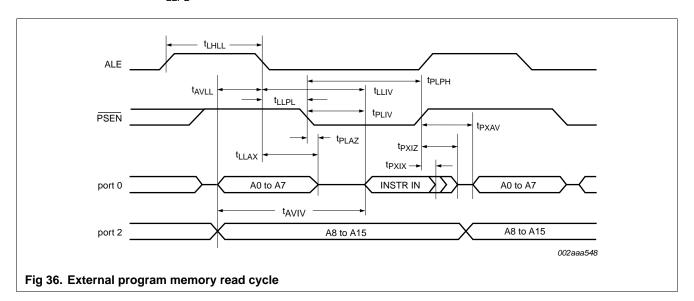

# 9.1 Explanation of symbols

Each timing symbol has 5 characters. The first character is always a 'T' (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

A — Address

C — Clock

D — Input data

H — Logic level HIGH

I — Instruction (program memory contents)

L — Logic level LOW or ALE

P - PSEN

Q — Output data

R — RD signal

T — Time

V — Valid

$W - \overline{WR}$  signal

X — No longer a valid logic level

**Z** — High impedance (Float)

# Example:

t<sub>AVII</sub> = Address valid to ALE LOW time

$t_{LLPL}$  = ALE LOW to  $\overline{PSEN}$  LOW time

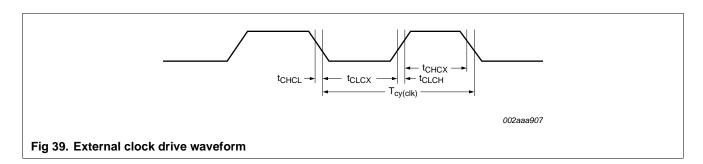

Table 72. External clock drive

| Symbol               | Parameter            | Oscilla | Oscillator |                          |                          |     |  |  |

|----------------------|----------------------|---------|------------|--------------------------|--------------------------|-----|--|--|

|                      |                      | 40 MHz  | 40 MHz     |                          | Variable                 |     |  |  |

|                      |                      | Min     | Max        | Min                      | Max                      |     |  |  |

| f <sub>osc</sub>     | oscillator frequency | -       | -          | 0                        | 40                       | MHz |  |  |

| T <sub>cy(clk)</sub> | clock cycle time     | 25      | -          | -                        | -                        | ns  |  |  |

| t <sub>CHCX</sub>    | clock HIGH time      | 8.75    | -          | 0.35T <sub>cy(clk)</sub> | 0.65T <sub>cy(clk)</sub> | ns  |  |  |

| t <sub>CLCX</sub>    | clock LOW time       | 8.75    | -          | 0.35T <sub>cy(clk)</sub> | 0.65T <sub>cy(clk)</sub> | ns  |  |  |

| t <sub>CLCH</sub>    | clock rise time      | -       | 10         | -                        | -                        | ns  |  |  |

| t <sub>CHCL</sub>    | clock fall time      | -       | 10         | -                        | -                        | ns  |  |  |

Table 73. Serial port timing

| Symbol            | Parameter                                     | Oscillator |     |                              |                     |    |

|-------------------|-----------------------------------------------|------------|-----|------------------------------|---------------------|----|

|                   |                                               | 40 MHz     |     | Variable                     |                     |    |

|                   |                                               | Min        | Max | Min                          | Max                 |    |

| T <sub>XLXL</sub> | serial port clock cycle time                  | 0.3        | ·-  | 12T <sub>cy(clk)</sub>       | -                   | μS |

| t <sub>QVXH</sub> | output data set-up to clock rising edge time  | 117        | -   | 10T <sub>cy(clk)</sub> – 133 | -                   | ns |

| t <sub>XHQX</sub> | output data hold after clock rising edge time | 0          | -   | $2T_{cy(clk)} - 50$          | -                   | ns |

| t <sub>XHDX</sub> | input data hold after clock rising edge time  | 0          | -   | 0                            | -                   | ns |

| t <sub>XHDV</sub> | input data valid to clock rising edge time    | -          | 117 | -                            | $10T_{cy(clk)}-133$ | ns |

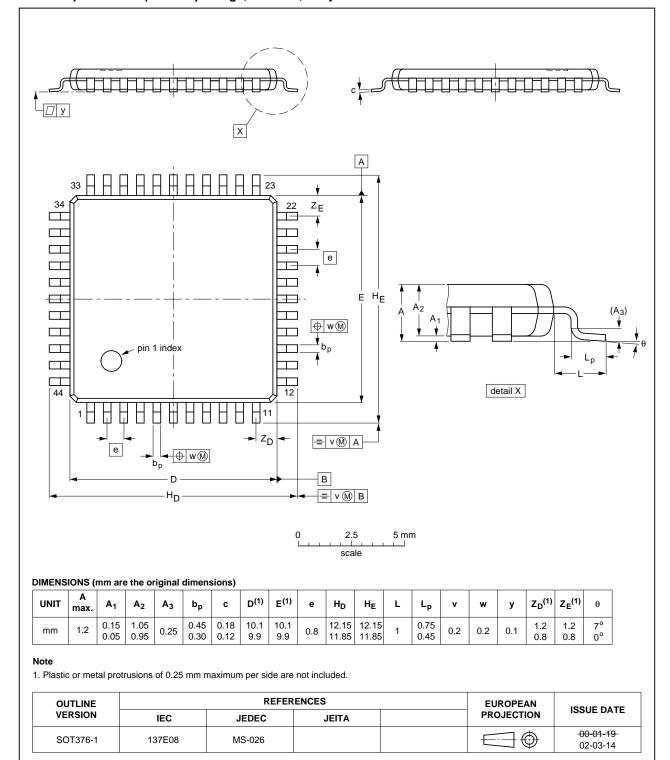

# 10. Package outline

TQFP44: plastic thin quad flat package; 44 leads; body 10 x 10 x 1.0 mm

SOT376-1

Fig 50. Package outline SOT376-1 (TQFP44)

P89V660\_662\_664

All information provided in this document is subject to legal disclaimers.

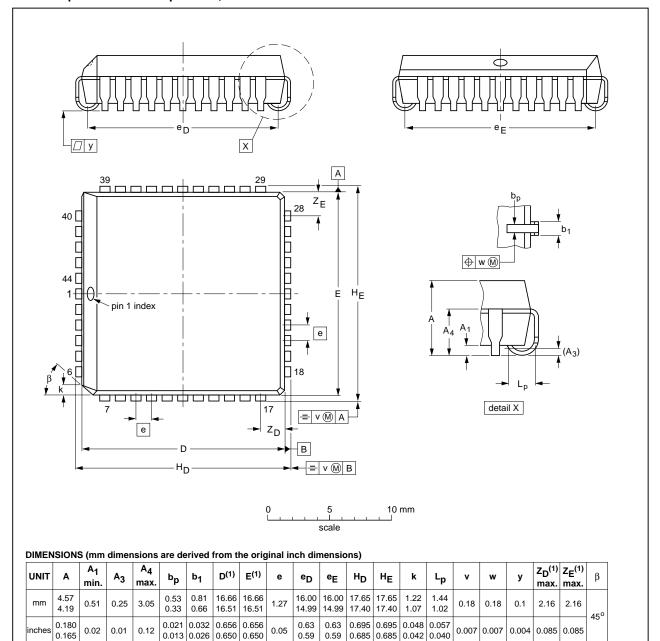

### PLCC44: plastic leaded chip carrier; 44 leads

#### SOT187-2

#### Note

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| OUTLINE REFERENCES |        |        |          |  | EUROPEAN   | ISSUE DATE                      |

|--------------------|--------|--------|----------|--|------------|---------------------------------|

| VERSION            | IEC    | JEDEC  | JEITA    |  | PROJECTION | ISSUE DATE                      |

| SOT187-2           | 112E10 | MS-018 | EDR-7319 |  |            | <del>99-12-27</del><br>01-11-14 |

Fig 51. Package outline SOT187-2 (PLCC44)

P89V660\_662\_664 All information provided in this document is subject to legal disclaimers.

# 11. Abbreviations

Table 76. Acronym list

| Acronym | Description                                 |

|---------|---------------------------------------------|

| ALE     | Address Latch Enabled                       |

| CPU     | Central Processing Unit                     |

| DUT     | Device Under Test                           |

| EPROM   | Erasable Programmable Read-Only Memory      |

| EMI     | Electro-Magnetic Interference               |

| MCU     | Microcontroller Unit                        |

| PWM     | Pulse Width Modulator                       |

| RAM     | Random Access Memory                        |

| RC      | Resistance-Capacitance                      |

| SFR     | Special Function Register                   |

| SPI     | Serial Peripheral Interface                 |

| UART    | Universal Asynchronous Receiver/Transmitter |

# 13. Legal information

#### 13.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

## 13.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 13.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or

malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

P89V660\_662\_664

All information provided in this document is subject to legal disclaimers.