Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                               |

| Core Processor             | CIP-51 8051                                                            |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 50MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SMBus, SPI, UART/USART, USB                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 22                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2.25K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 5.25V                                                           |

| Data Converters            | A/D 20x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 28-WFQFN Exposed Pad                                                   |

| Supplier Device Package    | 28-QFN (5x5)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm8ub10f16g-b-qfn28 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.7 Analog

#### 12-Bit Analog-to-Digital Converter (ADC0)

The ADC is a successive-approximation-register (SAR) ADC with 12-, 10-, and 8-bit modes, integrated track-and hold and a programmable window detector. The ADC is fully configurable under software control via several registers. The ADC may be configured to measure different signals using the analog multiplexer. The voltage reference for the ADC is selectable between internal and external reference sources.

- · Up to 20 external inputs.

- · Single-ended 12-bit and 10-bit modes.

- Supports an output update rate of 200 ksps samples per second in 12-bit mode or 800 ksps samples per second in 10-bit mode.

- Operation in low power modes at lower conversion speeds.

- Asynchronous hardware conversion trigger, selectable between software, external I/O and internal timer sources.

- Output data window comparator allows automatic range checking.

- Support for burst mode, which produces one set of accumulated data per conversion-start trigger with programmable power-on settling and tracking time.

- Conversion complete and window compare interrupts supported.

- · Flexible output data formatting.

- Includes an internal fast-settling reference with two levels (1.65 V and 2.4 V) and support for external reference and signal ground.

- · Integrated temperature sensor.

#### Low Current Comparators (CMP0, CMP1)

Analog comparators are used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. External input connections to device I/O pins and internal connections are available through separate multiplexers on the positive and negative inputs. Hysteresis, response time, and current consumption may be programmed to suit the specific needs of the application.

The comparator includes the following features:

- Up to 10 (CMP0) or 12 (CMP1) external positive inputs

- Up to 10 (CMP0) or 12 (CMP1) external negative inputs

- · Additional input options:

- · Internal connection to LDO output

- · Direct connection to GND

- · Direct connection to VDD

- · Dedicated 6-bit reference DAC

- · Synchronous and asynchronous outputs can be routed to pins via crossbar

- Programmable hysteresis between 0 and ±20 mV

- · Programmable response time

- · Interrupts generated on rising, falling, or both edges

- · PWM output kill feature

#### 3.10 Bootloader

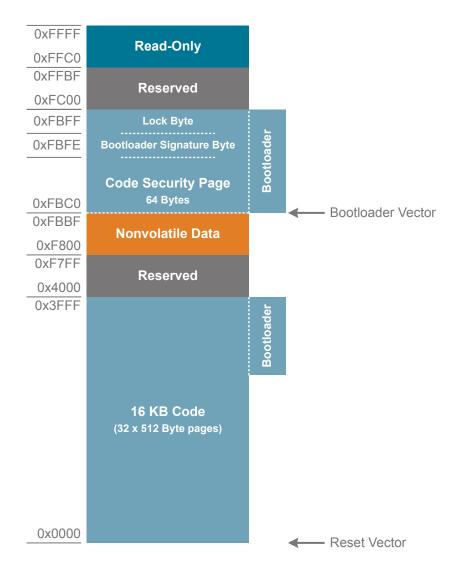

All devices come pre-programmed with a USB bootloader. This bootloader resides in the code security page and last pages of code flash; it can be erased if it is not needed.

The byte before the Lock Byte is the Bootloader Signature Byte. Setting this byte to a value of 0xA5 indicates the presence of the bootloader in the system. Any other value in this location indicates that the bootloader is not present in flash.

When a bootloader is present, the device will jump to the bootloader vector after any reset, allowing the bootloader to run. The bootloader then determines if the device should stay in bootload mode or jump to the reset vector located at 0x0000. When the bootloader is not present, the device will jump to the reset vector of 0x0000 after any reset.

Figure 3.2. Flash Memory Map with Bootloader—16 KB Devices

# 4.1.2 Power Consumption

**Table 4.2. Power Consumption**

| Parameter                                                                              | Symbol              | Test Condition                              | Min | Тур | Max | Unit |

|----------------------------------------------------------------------------------------|---------------------|---------------------------------------------|-----|-----|-----|------|

| Digital Core Supply Current                                                            |                     |                                             |     |     |     |      |

| Normal Mode-Full speed with code executing from flash                                  | I <sub>DD</sub>     | F <sub>SYSCLK</sub> = 48 MHz <sup>2</sup>   | _   | 8.9 | 9.8 | mA   |

| executing from hash                                                                    |                     | F <sub>SYSCLK</sub> = 24.5 MHz <sup>2</sup> | _   | 4.3 | 4.9 | mA   |

|                                                                                        |                     | F <sub>SYSCLK</sub> = 1.53 MHz <sup>2</sup> | _   | 600 | _   | μA   |

|                                                                                        |                     | F <sub>SYSCLK</sub> = 80 kHz <sup>3</sup>   | _   | 145 | _   | μA   |

| Idle Mode-Core halted with peripherals running                                         | I <sub>DD</sub>     | F <sub>SYSCLK</sub> = 48 MHz <sup>2</sup>   | _   | 6   | 6.6 | mA   |

| erais rummig                                                                           |                     | F <sub>SYSCLK</sub> = 24.5 MHz <sup>2</sup> | _   | 2.8 | 3.2 | mA   |

|                                                                                        |                     | F <sub>SYSCLK</sub> = 1.53 MHz <sup>2</sup> | _   | 440 | _   | μA   |

|                                                                                        |                     | F <sub>SYSCLK</sub> = 80 kHz <sup>3</sup>   | _   | 130 | _   | μA   |

| Suspend Mode-Core halted and                                                           | I <sub>DD</sub>     | LFO Running                                 | _   | 125 | _   | μA   |

| high frequency clocks stopped,<br>Supply monitor off.                                  |                     | LFO Stopped                                 | _   | 120 | _   | μA   |

| Snooze Mode-Core halted and                                                            | I <sub>DD</sub>     | LFO Running                                 | _   | 25  | _   | μA   |

| high frequency clocks stopped.<br>Regulator in low-power state, Supply monitor off.    |                     | LFO Stopped                                 | _   | 20  | _   | μA   |

| Stop Mode—Core halted and all clocks stopped,Internal LDO On, Supply monitor off.      | I <sub>DD</sub>     |                                             | _   | 120 | _   | μА   |

| Shutdown Mode—Core halted and all clocks stopped,Internal LDO Off, Supply monitor off. | I <sub>DD</sub>     |                                             | _   | 0.2 | _   | μА   |

| Analog Peripheral Supply Currents                                                      | 1                   |                                             | 1   | 1   |     |      |

| High-Frequency Oscillator 0                                                            | I <sub>HFOSC0</sub> | Operating at 24.5 MHz,                      | _   | 105 | _   | μA   |

|                                                                                        |                     | T <sub>A</sub> = 25 °C                      |     |     |     |      |

| High-Frequency Oscillator 1                                                            | I <sub>HFOSC1</sub> | Operating at 48 MHz,                        | _   | 850 | _   | μA   |

|                                                                                        |                     | T <sub>A</sub> = 25 °C                      |     |     |     |      |

| Low-Frequency Oscillator                                                               | I <sub>LFOSC</sub>  | Operating at 80 kHz,                        | _   | 4   | _   | μA   |

|                                                                                        |                     | T <sub>A</sub> = 25 °C                      |     |     |     |      |

| Parameter             | Symbol            | Test Condition                                          | Min | Тур | Max | Unit |

|-----------------------|-------------------|---------------------------------------------------------|-----|-----|-----|------|

| 5V Regulator          | I <sub>VREG</sub> | Normal Mode                                             | _   | 245 | 340 | μA   |

|                       |                   | (SUSEN = 0, BIASENB = 0)                                |     |     |     |      |

|                       |                   | Suspend Mode                                            | _   | 60  | 100 | μA   |

|                       |                   | (SUSEN = 1, BIASENB = 0)                                |     |     |     |      |

|                       |                   | Bias Disabled                                           | _   | 2.5 | 10  | μA   |

|                       |                   | (BIASENB = 1)                                           |     |     |     |      |

|                       |                   | Disabled                                                | _   | 2.5 | _   | nA   |

|                       |                   | (BIASENB = 1, REG1ENB = 1)                              |     |     |     |      |

| USB (USB0) Full-Speed | I <sub>USB</sub>  | Low Energy Mode, 64 byte 1ms IN Interrupt transfers     | _   | 850 | _   | μΑ   |

|                       |                   | Low Energy Mode, 64 byte 1ms<br>OUT Interrupt transfers | _   | 250 | _   | μА   |

|                       |                   | Low Energy Mode, Idle (SOF only)                        | _   | 50  | _   | μΑ   |

## Note:

- 1. Currents are additive. For example, where I<sub>DD</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 2. Includes supply current from internal LDO regulator, supply monitor, and High Frequency Oscillator.

- 3. Includes supply current from internal LDO regulator, supply monitor, and Low Frequency Oscillator.

- 4. ADC0 always-on power excludes internal reference supply current.

- 5. The internal reference is enabled as-needed when operating the ADC in burst mode to save power.

## 4.1.3 Reset and Supply Monitor

Table 4.3. Reset and Supply Monitor

| Parameter                                                            | Symbol            | Test Condition                                          | Min  | Тур   | Max  | Unit |

|----------------------------------------------------------------------|-------------------|---------------------------------------------------------|------|-------|------|------|

| VDD Supply Monitor Threshold V <sub>VDDM</sub>                       |                   |                                                         | 1.95 | 2.05  | 2.15 | V    |

| Power-On Reset (POR) Threshold                                       | V <sub>POR</sub>  | Rising Voltage on VDD                                   | _    | 1.2   | _    | V    |

|                                                                      |                   | Falling Voltage on VDD                                  | 0.75 | _     | 1.36 | V    |

| VDD Ramp Time                                                        | t <sub>RMP</sub>  | Time to V <sub>DD</sub> > 2.2 V                         | 10   | _     | _    | μs   |

| Reset Delay from POR                                                 | t <sub>POR</sub>  | Relative to V <sub>DD</sub> > V <sub>POR</sub>          | 3    | 10    | 31   | ms   |

| Reset Delay from non-POR source                                      | t <sub>RST</sub>  | Time between release of reset source and code execution | _    | 50    | _    | μs   |

| RST Low Time to Generate Reset                                       | t <sub>RSTL</sub> |                                                         | 15   | _     | _    | μs   |

| Missing Clock Detector Response<br>Time (final rising edge to reset) | t <sub>MCD</sub>  | F <sub>SYSCLK</sub> >1 MHz                              | _    | 0.625 | 1.2  | ms   |

| Missing Clock Detector Trigger Frequency                             | F <sub>MCD</sub>  |                                                         | _    | 7.5   | 13.5 | kHz  |

| VDD Supply Monitor Turn-On Time                                      | t <sub>MON</sub>  |                                                         | _    | 2     | _    | μs   |

### 4.1.4 Flash Memory

Table 4.4. Flash Memory

| Parameter                                               | Symbol             | Test Condition                 | Min | Тур  | Max | Units  |

|---------------------------------------------------------|--------------------|--------------------------------|-----|------|-----|--------|

| Write Time <sup>1 , 2</sup>                             | t <sub>WRITE</sub> | One Byte,                      | 19  | 20   | 21  | μs     |

|                                                         |                    | F <sub>SYSCLK</sub> = 24.5 MHz |     |      |     |        |

| Erase Time <sup>1, 2</sup>                              | t <sub>ERASE</sub> | One Page,                      | 5.2 | 5.35 | 5.5 | ms     |

|                                                         |                    | F <sub>SYSCLK</sub> = 24.5 MHz |     |      |     |        |

| V <sub>DD</sub> Voltage During Programming <sup>3</sup> | V <sub>PROG</sub>  |                                | 2.2 | _    | 3.6 | V      |

| Endurance (Write/Erase Cycles)                          | N <sub>WE</sub>    |                                | 20k | 100k | _   | Cycles |

### Note:

- 1. Does not include sequencing time before and after the write/erase operation, which may be multiple SYSCLK cycles.

- 2. The internal High-Frequency Oscillator 0 has a programmable output frequency, which is factory programmed to 24.5 MHz. If user firmware adjusts the oscillator speed, it must be between 22 and 25 MHz during any flash write or erase operation. It is recommended to write the HFO0CAL register back to its reset value when writing or erasing flash.

- 3. Flash can be safely programmed at any voltage above the supply monitor threshold (V<sub>VDDM</sub>).

- 4. Data Retention Information is published in the Quarterly Quality and Reliability Report.

#### 4.1.5 Power Management Timing

**Table 4.5. Power Management Timing**

| Parameter                 | Symbol                      | Test Condition                   | Min | Тур | Max | Units   |

|---------------------------|-----------------------------|----------------------------------|-----|-----|-----|---------|

| Idle Mode Wake-up Time    | t <sub>IDLEWK</sub>         |                                  | 2   | _   | 3   | SYSCLKs |

| Suspend Mode Wake-up Time | t <sub>SUS-</sub><br>PENDWK | SYSCLK = HFOSC0<br>CLKDIV = 0x00 | _   | 170 | _   | ns      |

| Snooze Mode Wake-up Time  | tsleepwk                    | SYSCLK = HFOSC0<br>CLKDIV = 0x00 | _   | 12  | _   | μs      |

# 4.1.8 ADC

Table 4.8. ADC

| Parameter                          | Symbol              | Test Condition                  | Min      | Тур   | Max                | Unit   |

|------------------------------------|---------------------|---------------------------------|----------|-------|--------------------|--------|

| Resolution                         | N <sub>bits</sub>   | 12 Bit Mode                     | 12       |       |                    | Bits   |

|                                    |                     | 10 Bit Mode                     |          | 10    |                    | Bits   |

| Throughput Rate                    | f <sub>S</sub>      | 12 Bit Mode                     | _        | _     | 200                | ksps   |

| (High Speed Mode)                  |                     | 10 Bit Mode                     | _        | _     | 800                | ksps   |

| Throughput Rate                    | f <sub>S</sub>      | 12 Bit Mode                     | _        | _     | 62.5               | ksps   |

| (Low Power Mode)                   |                     | 10 Bit Mode                     | _        | _     | 250                | ksps   |

| Tracking Time                      | t <sub>TRK</sub>    | High Speed Mode                 | 230      | _     | _                  | ns     |

|                                    |                     | Low Power Mode                  | 450      | _     | _                  | ns     |

| Power-On Time                      | t <sub>PWR</sub>    |                                 | 1.2      | _     | _                  | μs     |

| SAR Clock Frequency                | f <sub>SAR</sub>    | High Speed Mode,                | _        | _     | 6.25               | MHz    |

|                                    |                     | Reference is 2.4 V internal     |          |       |                    |        |

|                                    |                     | High Speed Mode,                | _        | _     | 12.5               | MHz    |

|                                    |                     | Reference is not 2.4 V internal |          |       |                    |        |

|                                    |                     | Low Power Mode                  | _        | _     | 4                  | MHz    |

| Conversion Time                    | t <sub>CNV</sub>    | 10-Bit Conversion,              |          | 1.1   | 1                  | μs     |

|                                    |                     | SAR Clock = 12.25 MHz,          |          |       |                    |        |

|                                    |                     | System Clock = 24.5 MHz.        |          |       |                    |        |

| Sample/Hold Capacitor              | C <sub>SAR</sub>    | Gain = 1                        | _        | 5     | _                  | pF     |

|                                    |                     | Gain = 0.5                      | _        | 2.5   | _                  | pF     |

| Input Pin Capacitance              | C <sub>IN</sub>     |                                 | _        | 20    | _                  | pF     |

| Input Mux Impedance                | R <sub>MUX</sub>    |                                 | _        | 550   | _                  | Ω      |

| Voltage Reference Range            | V <sub>REF</sub>    |                                 | 1        | _     | V <sub>IO</sub>    | V      |

| Input Voltage Range <sup>1</sup>   | V <sub>IN</sub>     | Gain = 1                        | 0        | _     | V <sub>REF</sub>   | V      |

|                                    |                     | Gain = 0.5                      | 0        | _     | 2xV <sub>REF</sub> | V      |

| Power Supply Rejection Ratio       | PSRR <sub>ADC</sub> |                                 | _        | 70    | _                  | dB     |

| DC Performance                     |                     |                                 |          |       |                    |        |

| Integral Nonlinearity              | INL                 | 12 Bit Mode                     | _        | ±1    | ±2.3               | LSB    |

| · ·                                |                     | 10 Bit Mode                     | _        | ±0.2  | ±0.6               | LSB    |

| Differential Nonlinearity (Guaran- | DNL                 | 12 Bit Mode                     | -1       | ±0.7  | 1.9                | LSB    |

| teed Monotonic)                    |                     | 10 Bit Mode                     | _        | ±0.2  | ±0.6               | LSB    |

| Offset Error                       | E <sub>OFF</sub>    | 12 Bit Mode, VREF = 1.65 V      | -3       | 0     | 3                  | LSB    |

|                                    |                     | 10 Bit Mode, VREF = 1.65 V      | -2       | 0     | 2                  | LSB    |

| Offset Temperature Coefficient     | TC <sub>OFF</sub>   |                                 | <u> </u> | 0.004 | _                  | LSB/°C |

# 4.1.13 Port I/O

Table 4.13. Port I/O

| Parameter                                                        | Symbol          | Test Condition                                              | Min                   | Тур | Max                   | Unit |

|------------------------------------------------------------------|-----------------|-------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| Output High Voltage (High Drive)                                 | V <sub>OH</sub> | $I_{OH}$ = -7 mA, $V_{IO} \ge 3.0 \text{ V}$                | V <sub>IO</sub> - 0.7 | _   | _                     | V    |

|                                                                  |                 | $I_{OH}$ = -3.3 mA, 2.2 V $\leq$ V <sub>IO</sub> $<$ 3.0 V  | V <sub>IO</sub> x 0.8 | _   | _                     | V    |

|                                                                  |                 | $I_{OH}$ = -1.8 mA, 1.71 V $\leq$ V <sub>IO</sub> $<$ 2.2 V |                       |     |                       |      |

| Output Low Voltage (High Drive)                                  | V <sub>OL</sub> | I <sub>OL</sub> = 13.5 mA, V <sub>IO</sub> ≥ 3.0 V          | _                     | _   | 0.6                   | V    |

|                                                                  |                 | $I_{OL}$ = 7 mA, 2.2 V ≤ $V_{IO}$ < 3.0 V                   | _                     | _   | V <sub>IO</sub> x 0.2 | V    |

|                                                                  |                 | $I_{OL}$ = 3.6 mA, 1.71 V $\leq$ V <sub>IO</sub> $<$ 2.2 V  |                       |     |                       |      |

| Output High Voltage (Low Drive)                                  | V <sub>OH</sub> | I <sub>OH</sub> = -4.75 mA, V <sub>IO</sub> ≥ 3.0 V         | V <sub>IO</sub> - 0.7 | _   | _                     | V    |

|                                                                  |                 | $I_{OH}$ = -2.25 mA, 2.2 V $\leq$ V <sub>IO</sub> $<$ 3.0 V | V <sub>IO</sub> x 0.8 | _   | _                     | V    |

|                                                                  |                 | $I_{OH}$ = -1.2 mA, 1.71 V $\leq$ V <sub>IO</sub> $<$ 2.2 V |                       |     |                       |      |

| Output Low Voltage (Low Drive)                                   | V <sub>OL</sub> | $I_{OL}$ = 6.5 mA, $V_{IO} \ge 3.0 \text{ V}$               | _                     | _   | 0.6                   | V    |

|                                                                  |                 | $I_{OL}$ = 3.5 mA, 2.2 V ≤ $V_{IO}$ < 3.0 V                 | _                     | _   | V <sub>IO</sub> x 0.2 | V    |

|                                                                  |                 | $I_{OL}$ = 1.8 mA, 1.71 V $\leq$ V <sub>IO</sub> $<$ 2.2 V  |                       |     |                       |      |

| Input High Voltage                                               | V <sub>IH</sub> |                                                             | V <sub>IO</sub> - 0.6 | _   | _                     | V    |

| (all port pins including VBUS)                                   |                 |                                                             |                       |     |                       |      |

| Input Low Voltage                                                | V <sub>IL</sub> |                                                             | _                     | _   | 0.6                   | V    |

| (all port pins including VBUS)                                   |                 |                                                             |                       |     |                       |      |

| Pin Capacitance                                                  | C <sub>IO</sub> |                                                             | _                     | 7   | _                     | pF   |

| Weak Pull-Up Current                                             | I <sub>PU</sub> | V <sub>DD</sub> = 3.6                                       | -30                   | -20 | -10                   | μΑ   |

| (V <sub>IN</sub> = 0 V)                                          |                 |                                                             |                       |     |                       |      |

| Input Leakage (Pullups off or Analog)                            | I <sub>LK</sub> | GND < V <sub>IN</sub> < V <sub>IO</sub>                     | -1.1                  | _   | 1.1                   | μΑ   |

| Input Leakage Current with V <sub>IN</sub> above V <sub>IO</sub> | I <sub>LK</sub> | V <sub>IO</sub> < V <sub>IN</sub> < V <sub>IO</sub> +2.0 V  | 0                     | 5   | 150                   | μΑ   |

### 4.3 Absolute Maximum Ratings

Stresses above those listed in 4.3 Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at <a href="http://www.silabs.com/support/quality/pages/default.aspx">http://www.silabs.com/support/quality/pages/default.aspx</a>.

**Table 4.16. Absolute Maximum Ratings**

| Parameter                                         | Symbol             | Test Condition          | Min     | Max                  | Unit |

|---------------------------------------------------|--------------------|-------------------------|---------|----------------------|------|

| Ambient Temperature Under Bias                    | T <sub>BIAS</sub>  |                         | -55     | 125                  | °C   |

| Storage Temperature                               | T <sub>STG</sub>   |                         | -65     | 150                  | °C   |

| Voltage on VDD                                    | V <sub>DD</sub>    |                         | GND-0.3 | 4.2                  | V    |

| Voltage on VIO <sup>2</sup>                       | V <sub>IO</sub>    |                         | GND-0.3 | 4.2                  | V    |

| Voltage on VREGIN                                 | V <sub>REGIN</sub> |                         | GND-0.3 | 5.8                  | V    |

| Voltage on D+ or D-                               | V <sub>USBD</sub>  |                         | GND-0.3 | V <sub>DD</sub> +0.3 | V    |

| Voltage on I/O pins (including VBUS /             | V <sub>IN</sub>    | V <sub>IO</sub> > 3.3 V | GND-0.3 | 5.8                  | V    |

| P3.1) or RSTb                                     |                    | V <sub>IO</sub> < 3.3 V | GND-0.3 | V <sub>IO</sub> +2.5 | V    |

| Total Current Sunk into Supply Pin                | I <sub>VDD</sub>   |                         | _       | 400                  | mA   |

| Total Current Sourced out of Ground Pin           | I <sub>GND</sub>   |                         | 400     | _                    | mA   |

| Current Sourced or Sunk by any I/O<br>Pin or RSTb | I <sub>IO</sub>    |                         | -100    | 100                  | mA   |

| Operating Junction Temperature                    | TJ                 |                         | -40     | 105                  | °C   |

|                                                   | •                  | <u> </u>                |         | •                    | •    |

# Note:

- 1. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2. On devices without a VIO pin,  $V_{IO} = V_{DD}$

# 4.4 Typical Performance Curves

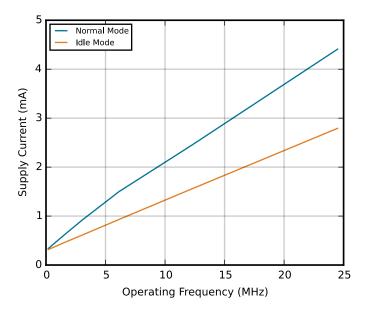

Figure 4.1. Typical Operating Supply Current using HFOSC0

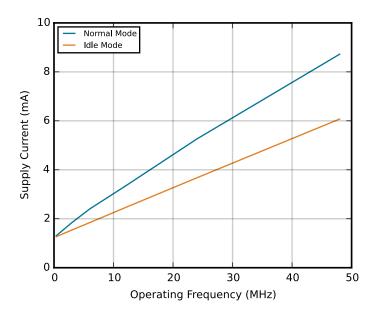

Figure 4.2. Typical Operating Supply Current using HFOSC1

Figure 4.3. Typical Operating Supply Current using LFOSC

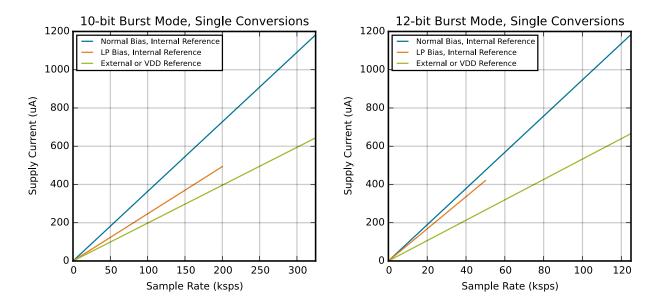

Figure 4.4. Typical ADC0 and Internal Reference Supply Current in Burst Mode

# 6. Pin Definitions

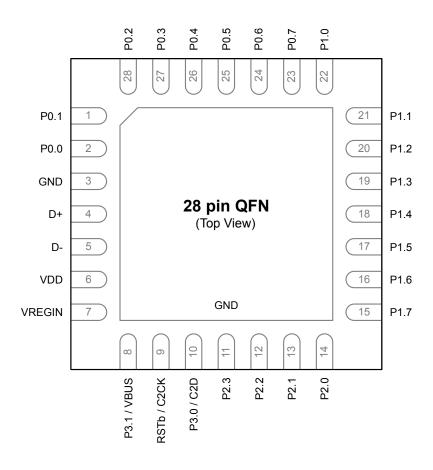

## 6.1 EFM8UB1x-QFN28 Pin Definitions

Figure 6.1. EFM8UB1x-QFN28 Pinout

Table 6.1. Pin Definitions for EFM8UB1x-QFN28

| Pin    | Pin Name | Description       | Crossbar Capability | Additional Digital Functions | Analog Functions |

|--------|----------|-------------------|---------------------|------------------------------|------------------|

| Number |          |                   |                     | Tulletions                   |                  |

| 1      | P0.1     | Multifunction I/O | Yes                 | P0MAT.1                      | ADC0.1           |

|        |          |                   |                     | INT0.1                       | CMP0P.1          |

|        |          |                   |                     | INT1.1                       | CMP0N.1          |

|        |          |                   |                     |                              | AGND             |

| Pin    | Pin Name | Description          | Crossbar Capability | Additional Digital | Analog Functions |

|--------|----------|----------------------|---------------------|--------------------|------------------|

| Number |          |                      |                     | Functions          |                  |

| 2      | P0.0     | Multifunction I/O    | Yes                 | P0MAT.0            | ADC0.0           |

|        |          |                      |                     | INT0.0             | CMP0P.0          |

|        |          |                      |                     | INT1.0             | CMP0N.0          |

|        |          |                      |                     |                    | VREF             |

| 3      | GND      | Ground               |                     |                    |                  |

| 4      | D+       | USB Data Positive    |                     |                    | ADC0.28          |

| 5      | D-       | USB Data Negative    |                     |                    | ADC0.29          |

| 6      | VDD      | Supply Power Input / |                     |                    |                  |

|        |          | 5V Regulator Output  |                     |                    |                  |

| 7      | VREGIN   | 5V Regulator Input   |                     |                    |                  |

| 8      | P3.1     | Multifunction I/O    |                     | VBUS               |                  |

| 9      | RST /    | Active-low Reset /   |                     |                    |                  |

|        | C2CK     | C2 Debug Clock       |                     |                    |                  |

| 10     | P3.0 /   | Multifunction I/O /  |                     |                    |                  |

|        | C2D      | C2 Debug Data        |                     |                    |                  |

| 11     | P2.3     | Multifunction I/O    | Yes                 | P2MAT.3            | ADC0.23          |

|        |          |                      |                     |                    | CMP1P.12         |

|        |          |                      |                     |                    | CMP1N.12         |

| 12     | P2.2     | Multifunction I/O    | Yes                 | P2MAT.2            | ADC0.22          |

|        |          |                      |                     |                    | CMP1P.11         |

|        |          |                      |                     |                    | CMP1N.11         |

| 13     | P2.1     | Multifunction I/O    | Yes                 | P2MAT.1            | ADC0.21          |

|        |          |                      |                     |                    | CMP1P.10         |

|        |          |                      |                     |                    | CMP1N.10         |

| 14     | P2.0     | Multifunction I/O    | Yes                 | P2MAT.0            | ADC0.20          |

|        |          |                      |                     |                    | CMP1P.9          |

|        |          |                      |                     |                    | CMP1N.9          |

| 15     | P1.7     | Multifunction I/O    | Yes                 | P1MAT.7            | ADC0.15          |

|        |          |                      |                     |                    | CMP1P.7          |

|        |          |                      |                     |                    | CMP1N.7          |

| 16     | P1.6     | Multifunction I/O    | Yes                 | P1MAT.6            | ADC0.14          |

|        |          |                      |                     | I2C0_SCL           | CMP1P.6          |

|        |          |                      |                     |                    | CMP1N.6          |

| 17     | P1.5     | Multifunction I/O    | Yes                 | P1MAT.5            | ADC0.13          |

|        |          |                      |                     | I2C0_SDA           | CMP1P.5          |

|        |          |                      |                     |                    | CMP1N.5          |

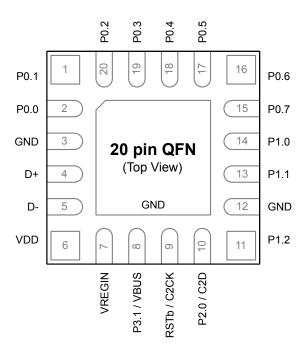

## 6.3 EFM8UB1x-QFN20 Pin Definitions

Figure 6.3. EFM8UB1x-QFN20 Pinout

Table 6.3. Pin Definitions for EFM8UB1x-QFN20

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|------------------------------|------------------|

| 1             | P0.1     | Multifunction I/O | Yes                 | P0MAT.1                      | ADC0.1           |

|               |          |                   |                     | INT0.1                       | CMP0P.1          |

|               |          |                   |                     | INT1.1                       | CMP0N.1          |

|               |          |                   |                     |                              | AGND             |

| 2             | P0.0     | Multifunction I/O | Yes                 | P0MAT.0                      | ADC0.0           |

|               |          |                   |                     | INT0.0                       | CMP0P.0          |

|               |          |                   |                     | INT1.0                       | CMP0N.0          |

|               |          |                   |                     |                              | VREF             |

| Pin    | Pin Name | Description          | Crossbar Capability | Additional Digital | Analog Functions |

|--------|----------|----------------------|---------------------|--------------------|------------------|

| Number |          |                      |                     | Functions          |                  |

| 3      | GND      | Ground               |                     |                    |                  |

| 4      | D+       | USB Data Positive    |                     |                    | ADC0.28          |

| 5      | D-       | USB Data Negative    |                     |                    | ADC0.29          |

| 6      | VDD      | Supply Power Input / |                     |                    |                  |

|        |          | 5V Regulator Output  |                     |                    |                  |

| 7      | VREGIN   | 5V Regulator Input   |                     |                    |                  |

| 8      | P3.1     | Multifunction I/O    |                     | VBUS               |                  |

| 9      | RST /    | Active-low Reset /   |                     |                    |                  |

|        | C2CK     | C2 Debug Clock       |                     |                    |                  |

| 10     | P2.0 /   | Multifunction I/O /  | Yes                 |                    |                  |

|        | C2D      | C2 Debug Data        |                     |                    |                  |

| 11     | P1.2     | Multifunction I/O    | Yes                 | P1MAT.2            | ADC0.10          |

|        |          |                      |                     | I2C0_SCL           | CMP1P.4          |

|        |          |                      |                     |                    | CMP1N.4          |

| 12     | GND      | Ground               |                     |                    |                  |

| 13     | P1.1     | Multifunction I/O    | Yes                 | P1MAT.1            | ADC0.9           |

|        |          |                      |                     | I2C0_SDA           | CMP1P.3          |

|        |          |                      |                     |                    | CMP1N.3          |

| 14     | P1.0     | Multifunction I/O    | Yes                 | P1MAT.0            | ADC0.8           |

|        |          |                      |                     |                    | CMP1P.2          |

|        |          |                      |                     |                    | CMP1N.2          |

| 15     | P0.7     | Multifunction I/O    | Yes                 | P0MAT.7            | ADC0.7           |

|        |          |                      |                     | INT0.7             | CMP1P.1          |

|        |          |                      |                     | INT1.7             | CMP1N.1          |

|        |          |                      |                     |                    | CMP0P.7          |

|        |          |                      |                     |                    | CMP0N.7          |

| 16     | P0.6     | Multifunction I/O    | Yes                 | P0MAT.6            | ADC0.6           |

|        |          |                      |                     | CNVSTR             | CMP1P.0          |

|        |          |                      |                     | INT0.6             | CMP1N.0          |

|        |          |                      |                     | INT1.6             | CMP0P.6          |

|        |          |                      |                     |                    | CMP0N.6          |

| 17     | P0.5     | Multifunction I/O    | Yes                 | P0MAT.5            | ADC0.5           |

|        |          |                      |                     | INT0.5             | CMP0P.5          |

|        |          |                      |                     | INT1.5             | CMP0N.5          |

|        |          |                      |                     | UART0_RX           |                  |

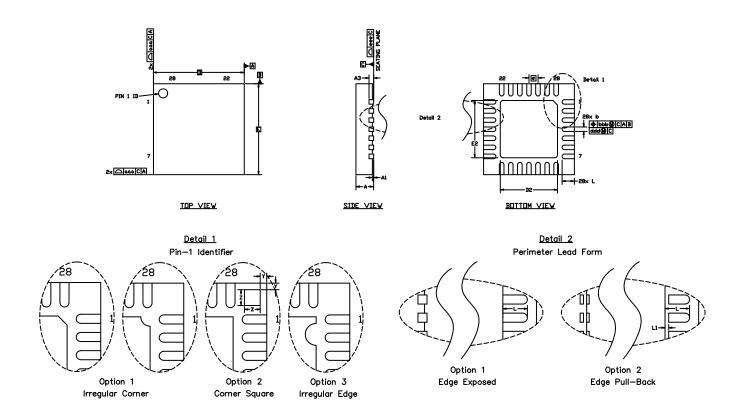

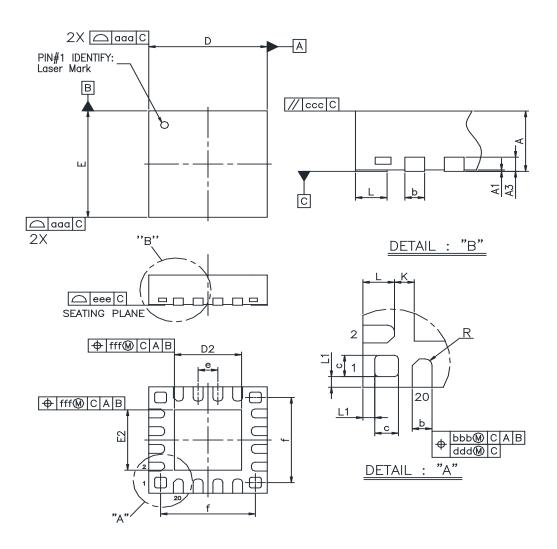

# 7. QFN28 Package Specifications

# 7.1 QFN28 Package Dimensions

Figure 7.1. QFN28 Package Drawing

Table 7.1. QFN28 Package Dimensions

| Dimension | Min      | Тур  | Max  |

|-----------|----------|------|------|

| A         | 0.70     | 0.75 | 0.80 |

| A1        | 0.00     | _    | 0.05 |

| A3        | 0.20 REF |      |      |

| b         | 0.20     | 0.25 | 0.30 |

| D         | 4.90     | 5.00 | 5.10 |

| D2        | 3.15     | 3.25 | 3.35 |

| е         | 0.50 BSC |      |      |

| Е         | 4.90     | 5.00 | 5.10 |

| E2        | 3.15     | 3.25 | 3.35 |

| L         | 0.45     | 0.55 | 0.65 |

| aaa       | 0.15     |      |      |

| bbb       | 0.10     |      |      |

| ddd       | 0.05     |      |      |

# 8. QSOP24 Package Specifications

# 8.1 QSOP24 Package Dimensions

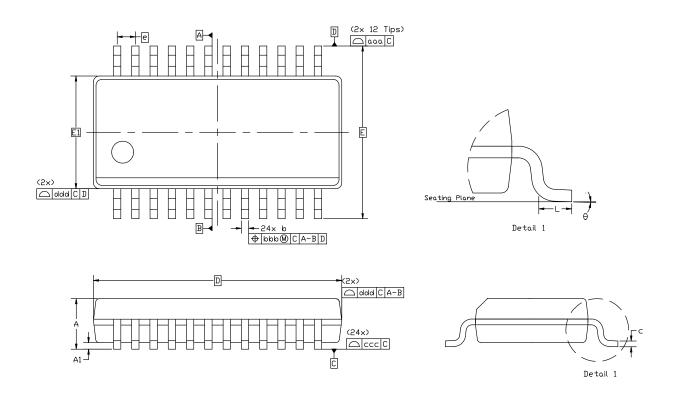

Figure 8.1. QSOP24 Package Drawing

Table 8.1. QSOP24 Package Dimensions

| Dimension | Min       | Тур | Max  |

|-----------|-----------|-----|------|

| A         | _         | _   | 1.75 |

| A1        | 0.10      | _   | 0.25 |

| b         | 0.20      | _   | 0.30 |

| С         | 0.10      | _   | 0.25 |

| D         | 8.65 BSC  |     |      |

| Е         | 6.00 BSC  |     |      |

| E1        | 3.90 BSC  |     |      |

| е         | 0.635 BSC |     |      |

| L         | 0.40      | _   | 1.27 |

| theta     | 0°        | _   | 8°   |

| Dimension | Min | Тур  | Max |

|-----------|-----|------|-----|

| aaa       |     | 0.20 |     |

| bbb       |     | 0.18 |     |

| ccc       |     | 0.10 |     |

| ddd       |     | 0.10 |     |

# Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-137, variation AE.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# 9. QFN20 Package Specifications

# 9.1 QFN20 Package Dimensions

Figure 9.1. QFN20 Package Drawing

Table 9.1. QFN20 Package Dimensions

| Dimension | Min      | Тур  | Max  |

|-----------|----------|------|------|

| А         | 0.70     | 0.75 | 0.80 |

| A1        | 0.00     | 0.02 | 0.05 |

| A3        | 0.20 REF |      |      |

| b         | 0.18     | 0.25 | 0.30 |

| С         | 0.25     | 0.30 | 0.35 |

| D         | 3.00 BSC |      |      |

| D2        | 1.6      | 1.70 | 1.80 |

| е         | 0.50 BSC |      |      |

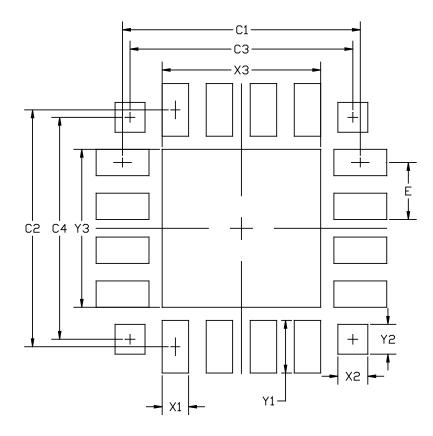

# 9.2 QFN20 PCB Land Pattern

Figure 9.2. QFN20 PCB Land Pattern Drawing

Table 9.2. QFN20 PCB Land Pattern Dimensions

| Dimension | Min  | Max  |  |

|-----------|------|------|--|

| C1        | 3.10 |      |  |

| C2        | 3.10 |      |  |

| С3        | 2.50 |      |  |

| C4        | 2.50 |      |  |

| E         | 0.50 |      |  |

| X1        | 0.30 |      |  |

| X2        | 0.25 | 0.35 |  |

| Х3        | 1.80 |      |  |

| Y1        | 0.90 |      |  |

| Y2        | 0.25 | 0.35 |  |

| Y3        | 1.80 |      |  |

## 10. Revision History

### 10.1 Revision 1.1

December 16, 2015

Updated 3.2 Power to properly reflect that a comparator falling edge wakes the device from Suspend and Snooze.

Added Note 4 to Table 4.1 Recommended Operating Conditions on page 12.

Added 5.3 Debug.

#### 10.2 Revision 1.0

Updated any TBD numbers in 4.1 Electrical Characteristics and adjusted various specifications.

Updated VOH and VOL graphs in Figure 4.6 Typical  $V_{OH}$  Curves on page 28 and Figure 4.7 Typical  $V_{OL}$  Curves on page 28 and updated the VOH and VOL specifications in Table 4.13 Port I/O on page 22.

Added more information to 3.10 Bootloader.

Updated part numbers to Revision C.

#### 10.3 Revision 0.3

Updated QFN20 packaging and landing diagram dimensions.

Updated QFN28 D and E minimum value.

Updated some characterization TBD values.

Added maximum allowable voltages on D+ and D- and added VBUS / P3.1 to the standard I/O row in Table 4.16 Absolute Maximum Ratings on page 24.

Added a diagram to 5.1 Power for cases when the internal 5 V-to-3.3 V regulator is not used.

Updated the 5 V-to-3.3 V regulator Electrical Characteristics table.

Added Stop mode to the Power Modes table in 3.2 Power.

#### 10.4 Revision 0.2

Initial release.