Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 50MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), CANbus, LINbus, SPI, UART/USART |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                       |

| Number of I/O              | 18                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 2.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                     |

| Data Converters            | A/D 18x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 24-WFQFN Exposed Pad                                             |

| Supplier Device Package    | 24-QFN (4x4)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f550-im   |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1. System Overview                                    | 16 |

|-------------------------------------------------------|----|

| 2. Ordering Information                               |    |

| 3. Pin Definitions                                    |    |

| 4. Package Specifications                             | 28 |

| 4.1. QFN-40 Package Specifications                    |    |

| 4.2. QFP-32 Package Specifications                    | 30 |

| 4.3. QFN-32 Package Specifications                    |    |

| 4.4. QFN-24 Package Specifications                    |    |

| 5. Electrical Characteristics                         | 36 |

| 5.1. Absolute Maximum Specifications                  | 36 |

| 5.2. Electrical Characteristics                       | 37 |

| 6. 12-Bit ADC (ADC0)                                  |    |

| 6.1. Modes of Operation                               | 48 |

| 6.1.1. Starting a Conversion                          |    |

| 6.1.2. Tracking Modes                                 |    |

| 6.1.3. Timing                                         |    |

| 6.1.4. Burst Mode                                     |    |

| 6.2. Output Code Formatting                           |    |

| 6.2.1. Settling Time Requirements                     | 52 |

| 6.3. Selectable Ğain                                  | 53 |

| 6.3.1. Calculating the Gain Value                     |    |

| 6.3.2. Setting the Gain Value                         |    |

| 6.4. Programmable Window Detector                     |    |

| 6.4.1. Window Detector In Single-Ended Mode           |    |

| 6.5. ADC0 Analog Multiplexer                          |    |

| 6.6. Temperature Sensor                               |    |

| 7. Voltage Reference                                  |    |

| 8. Comparators                                        |    |

| 8.1. Comparator Multiplexer                           |    |

| 9. Voltage Regulator (REG0)                           |    |

| 10. CIP-51 Microcontroller.                           |    |

| 10.1. Performance                                     | 81 |

| 10.2. Instruction Set                                 | 83 |

| 10.2.1. Instruction and CPU Timing                    | 83 |

| 10.3. CIP-51 Register Descriptions                    |    |

| 10.4. Serial Number Special Function Registers (SFRs) |    |

| 11. Memory Organization                               |    |

| 11.1. Program Memory                                  |    |

| 11.1.1. MOVX Instruction and Program Memory           |    |

| 11.2. Data Memory                                     |    |

| 11.2.1. Internal RAM                                  | 93 |

| 12. Special Function Registers                        |    |

| 12.1. SFR Paging                                      |    |

### Figure 5.1. Minimum VDD Monitor Threshold vs. System Clock Frequency

**Note:** With system clock frequencies greater than 25 MHz, the  $V_{DD}$  monitor level should be set to the high threshold (VDMLVL = 1b in SFR VDM0CN) to prevent undefined CPU operation. The high threshold should only be used with an external regulator powering  $V_{DD}$  directly. See Figure 9.2 on page 80 for the recommended power supply connections.

#### **Table 5.4. Reset Electrical Characteristics**

-40 to +125 °C unless otherwise specified.

| Parameter                                              | Conditions                                                                            | Min                   | Тур  | Max                   | Units |

|--------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| RST Output Low Voltage                                 | VIO = 5 V; IOL = 70 µA                                                                |                       | _    | 40                    | mV    |

| RST Input High Voltage                                 |                                                                                       | 0.7 x V <sub>IO</sub> |      | —                     |       |

| RST Input Low Voltage                                  |                                                                                       | —                     |      | 0.3 x V <sub>IO</sub> |       |

| RST Input Pullup Current                               | $\overline{\text{RST}}$ = 0.0 V, VIO = 5 V                                            |                       | 49   | 115                   | μA    |

| $V_{DD}$ RST Threshold ( $V_{RST-LOW}$ )               |                                                                                       | 1.65                  | 1.75 | 1.80                  | V     |

| V <sub>DD</sub> RST Threshold (V <sub>RST-HIGH</sub> ) |                                                                                       | 2.25                  | 2.30 | 2.45                  | V     |

| V <sub>REGIN</sub> Ramp Time for Power On              | V <sub>REGIN</sub> Ramp 0–1.8 V                                                       | _                     |      | 1                     | ms    |

|                                                        | Time from last system clock rising edge to reset initiation                           |                       |      |                       |       |

| Missing Clock Detector Timeout                         | V <sub>DD</sub> = 2.1 V                                                               | 200                   | 340  | 600                   | μs    |

|                                                        | V <sub>DD</sub> = 2.5 V                                                               | 200                   | 250  | 600                   |       |

| Reset Time Delay                                       | Delay between release of<br>any reset source and code<br>execution at location 0x0000 |                       | 155  | 175                   | μs    |

| Minimum RST Low Time to<br>Generate a System Reset     |                                                                                       | 6                     | _    | —                     | μs    |

| V <sub>DD</sub> Monitor Turn-on Time                   |                                                                                       | _                     | 60   | 100                   | μs    |

| V <sub>DD</sub> Monitor Supply Current                 |                                                                                       |                       | 1    | 2                     | μA    |

### **Table 5.5. Flash Electrical Characteristics**

$V_{DD}$  = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter                                                                                                                                                                 | Conditions                                    | Min                                | Тур   | Max          | Units       |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------|-------|--------------|-------------|--|--|--|

| Flash Size                                                                                                                                                                | C8051F550-3, 'F560-3,<br>'F568-9, and 'F570-1 | :                                  |       | Bytes        |             |  |  |  |

|                                                                                                                                                                           | C8051F554-7, 'F564-7, and<br>'F572-5          | 16384                              |       |              | bytes       |  |  |  |

| Endurance                                                                                                                                                                 |                                               | 20 k                               | 150 k |              | Erase/Write |  |  |  |

| Retention                                                                                                                                                                 | 125 °C                                        | 10                                 |       |              | Years       |  |  |  |

| Erase Cycle Time                                                                                                                                                          | 25 MHz System Clock                           | 28                                 | 30    | 45           | ms          |  |  |  |

| Write Cycle Time                                                                                                                                                          | 25 MHz System Clock                           | 79                                 | 84    | 125          | μs          |  |  |  |

| V <sub>DD</sub>                                                                                                                                                           | Write/Erase operations                        | V <sub>RST-HIGH</sub> <sup>2</sup> | _     | —            | V           |  |  |  |

| Temperature during<br>Programming Opera-<br>tions                                                                                                                         | –I Devices<br>–A Devices                      | 0<br>-40                           |       | +125<br>+125 | °C          |  |  |  |

| <ol> <li>On the 32 kB Flash devices, 1024 bytes at addresses 0x7C00 to 0x7FFF are reserved.</li> <li>See Table 5.4 for the V<sub>RST-HIGH</sub> specification.</li> </ol> |                                               |                                    |       |              |             |  |  |  |

#### 10.2. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 10.2.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 10.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

#### 13.1.1. Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IE, EIP1, or EIP2) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 13.1.

#### 13.1.2. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 5 system clock cycles: 1 clock cycle to detect the interrupt and 4 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 18 system clock cycles: 1 clock cycle to detect the interrupt, 5 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 4 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

### Table 13.1. Interrupt Summary

| Interrupt Source               | nterrupt Source Interrupt Priority Pending Fla<br>Vector Order |     | Pending Flag                                                               | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|--------------------------------|----------------------------------------------------------------|-----|----------------------------------------------------------------------------|------------------|----------------|--------------------|---------------------|

| Reset                          | 0x0000                                                         | Тор | None                                                                       | N/A              | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0<br>(INT0) | 0x0003                                                         | 0   | IE0 (TCON.1)                                                               | Y                | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow               | 0x000B                                                         | 1   | TF0 (TCON.5)                                                               | Y                | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1<br>(INT1) | 0x0013                                                         | 2   | IE1 (TCON.3)                                                               | Y                | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow               | 0x001B                                                         | 3   | TF1 (TCON.7)                                                               | Y                | Y              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                          | 0x0023                                                         | 4   | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y                | N              | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow               | 0x002B                                                         | 5   | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y                | N              | ET2 (IE.5)         | PT2 (IP.5)          |

| SPI0                           | 0x0033                                                         | 6   | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                | N              | ESPI0<br>(IE.6)    | PSPI0<br>(IP.6)     |

| SMB0                           | 0x003B                                                         | 7   | SI (SMB0CN.0)                                                              | Y                | Ν              | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| ADC0 Window Com-<br>pare       | 0x0043                                                         | 8   | ADOWINT<br>(ADC0CN.3)                                                      | Y                | N              | EWADC0<br>(EIE1.1) | PWADC0<br>(EIP1.1)  |

| ADC0 Conversion<br>Complete    | 0x004B                                                         | 9   | AD0INT (ADC0CN.5)                                                          | Y                | N              | EADC0<br>(EIE1.2)  | PADC0<br>(EIP1.2)   |

| Programmable<br>Counter Array  | 0x0053                                                         | 10  | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)<br>COVF (PCA0PWM.6)                       | Y                | N              | EPCA0<br>(EIE1.3)  | PPCA0<br>(EIP1.3)   |

| Comparator0                    | 0x005B                                                         | 11  | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | N                | N              | ECP0<br>(EIE1.4)   | PCP0<br>(EIP1.4)    |

| Comparator1                    | 0x0063                                                         | 12  | CP1FIF (CPT1CN.4)<br>CP1RIF (CPT1CN.5)                                     | N                | N              | ECP1<br>(EIE1.5)   | PCP1<br>(EIP1.5)    |

| Timer 3 Overflow               | 0x006B                                                         | 13  | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | N                | N              | ET3<br>(EIE1.6)    | PT3<br>(EIP1.6)     |

| LINO                           | 0x0073                                                         | 14  | LINOINT (LINST.3)                                                          | N                | N*             | ELIN0<br>(EIE1.7)  | PLIN0<br>(EIP1.7)   |

| Voltage Regulator<br>Dropout   | 0x007B                                                         | 15  | N/A                                                                        | N/A              | N/A            | EREG0<br>(EIE2.0)  | PREG0<br>(EIP2.0)   |

| CAN0                           | 0x0083                                                         | 16  | CAN0INT<br>(CAN0CN.7)                                                      | N                | Y              | ECAN0<br>(EIE2.1)  | PCAN0<br>(EIP2.1)   |

| Port Match                     | 0x008B                                                         | 17  | None                                                                       | N/A              | N/A            | EMAT<br>(EIE2.2)   | PMAT<br>(EIP2.2)    |

# SFR Definition 13.5. EIE2: Extended Interrupt Enable 2

| Bit   | 7 | 6 | 5 | 4 | 3 | 2    | 1     | 0     |

|-------|---|---|---|---|---|------|-------|-------|

| Name  |   |   |   |   |   | EMAT | ECAN0 | EREG0 |

| Туре  | R | R | R | R | R | R/W  | R/W   | R/W   |

| Reset | 0 | 0 | 0 | 0 | 0 | 0    | 0     | 0     |

#### SFR Address = 0xE7; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                                |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | Unused | Read = 00000b; Write = Don't Care.                                                                                                                                                                                                                                      |

| 2   | EMAT   | Enable Port Match Interrupt.<br>This bit sets the masking of the Port Match interrupt.<br>0: Disable all Port Match interrupts.<br>1: Enable interrupt requests generated by a Port Match                                                                               |

| 1   | ECAN0  | Enable CAN0 Interrupts.<br>This bit sets the masking of the CAN0 interrupt.<br>0: Disable all CAN0 interrupts.<br>1: Enable interrupt requests generated by CAN0.                                                                                                       |

| 0   | EREG0  | <ul> <li>Enable Voltage Regulator Dropout Interrupt.</li> <li>This bit sets the masking of the Voltage Regulator Dropout interrupt.</li> <li>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> </ul> |

# SFR Definition 13.7. IT01CF: INT0/INT1 Configuration

| Bit   | 7     | 6   | 5          | 4 | 3     | 2          | 1 | 0 |  |

|-------|-------|-----|------------|---|-------|------------|---|---|--|

| Name  | IN1PL |     | IN1SL[2:0] |   | IN0PL | INOSL[2:0] |   |   |  |

| Туре  | R/W   | R/W |            |   | R/W   | R/W        |   |   |  |

| Reset | 0     | 0   | 0          | 0 | 0     | 0 0 0      |   |   |  |

#### SFR Address = 0xE4; SFR Page = 0x0F

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IN1PL      | INT1 Polarity.<br>0: INT1 input is active low.<br>1: INT1 input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6:4 | IN1SL[2:0] | INT1 Port Pin Selection Bits.<br>These bits select which Port pin is assigned to INT1. Note that this pin assignment is<br>independent of the Crossbar; INT1 will monitor the assigned Port pin without disturb-<br>ing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar<br>will not assign the Port pin to a peripheral if it is configured to skip the selected pin.<br>000: Select P1.0<br>001: Select P1.1<br>010: Select P1.2<br>011: Select P1.3<br>100: Select P1.4<br>101: Select P1.5<br>110: Select P1.7                     |

| 3   | IN0PL      | INTO Polarity.<br>0: INTO input is active low.<br>1: INTO input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2:0 | IN0SL[2:0] | INTO Port Pin Selection Bits.<br>These bits select which Port pin is assigned to INTO. Note that this pin assignment is<br>independent of the Crossbar; INTO will monitor the assigned Port pin without disturb-<br>ing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar<br>will not assign the Port pin to a peripheral if it is configured to skip the selected pin.<br>000: Select P1.0<br>001: Select P1.1<br>010: Select P1.2<br>011: Select P1.3<br>100: Select P1.4<br>101: Select P1.5<br>110: Select P1.6<br>111: Select P1.7 |

# SFR Definition 14.1. PSCTL: Program Store R/W Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|-------|---|---|---|---|---|---|------|------|

| Name  |   |   |   |   |   |   | PSEE | PSWE |

| Туре  | R | R | R | R | R | R | R/W  | R/W  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0    |

#### SFR Address = 0x8F; SFR Page = 0x00

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b, Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1   | PSEE   | <ul> <li>Program Store Erase Enable.</li> <li>Setting this bit (in combination with PSWE) allows an entire page of Flash program memory to be erased. If this bit is logic 1 and Flash writes are enabled (PSWE is logic 1), a write to Flash memory using the MOVX instruction will erase the entire page that contains the location addressed by the MOVX instruction. The value of the data byte written does not matter.</li> <li>0: Flash program memory erasure disabled.</li> <li>1: Flash program memory erasure enabled.</li> </ul> |

| 0   | PSWE   | <ul> <li>Program Store Write Enable.</li> <li>Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.</li> <li>0: Writes to Flash program memory disabled.</li> <li>1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.</li> </ul>                                                                                                                                                     |

### 15.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the controller core to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the device performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100  $\mu$ s.

### 15.3. Suspend Mode

Setting the SUSPEND bit (OSCICN.5) causes the hardware to halt the CPU and the high-frequency internal oscillator, and go into Suspend mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. Most digital peripherals are not active in Suspend mode. The exception to this is the Port Match feature.

Suspend mode can be terminated by three types of events, a port match (described in Section "19.5. Port Match" on page 179), a Comparator low output (if enabled), or a device reset event. When Suspend mode is terminated, the device will continue execution on the instruction following the one that set the SUSPEND bit. If the wake event was configured to generate an interrupt, the interrupt will be serviced upon waking the device. If Suspend mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

Note: Before entering suspend mode, firmware must set the ZTCEN bit in REF0CN (SFR Definition 7.1).

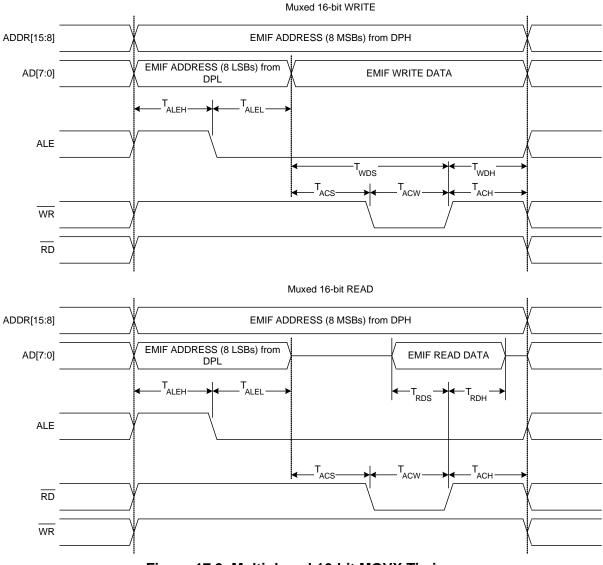

### 17.6.1. Multiplexed Mode 17.6.1.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011

Figure 17.3. Multiplexed 16-bit MOVX Timing

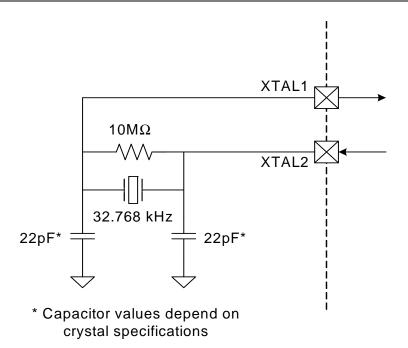

#### Figure 18.3. External 32.768 kHz Quartz Crystal Oscillator Connection Diagram

#### 18.4.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 18.1, Option 2. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation, according to Equation 18.1, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and R = the pull-up resistor value in k $\Omega$ .

$$f = 1.23 \times 10^3 / (R \times C)$$

### Equation 18.1. RC Mode Oscillator Frequency

For example: If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

f = 1.23(10<sup>3</sup>)/RC = 1.23(10<sup>3</sup>)/[246 x 50] = 0.1 MHz = 100 kHz

Referring to the table in SFR Definition 18.6, the required XFCN setting is 010b.

#### 18.4.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 18.1, Option 3. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation , where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and  $V_{DD}$  = the MCU power supply in Volts.

# SFR Definition 19.19. P1SKIP: Port 1 Skip

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|-------------|---|---|---|---|---|---|--|--|--|

| Name  |   | P1SKIP[7:0] |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W         |   |   |   |   |   |   |  |  |  |

| Reset | 0 | 0           | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

SFR Address = 0xD5; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                              |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1SKIP[7:0] | Port 1 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                     |

|     |             | These bits select Port 1 pins to be skipped by the Crossbar Decoder. Port pins<br>used for analog, special functions or GPIO should be skipped by the Crossbar.<br>0: Corresponding P1.n pin is not skipped by the Crossbar.<br>1: Corresponding P1.n pin is skipped by the Crossbar. |

### SFR Definition 19.20. P2: Port 2

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | P2[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W     |   |   |   |   |   |   |   |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Address = 0xA0; SFR Page = All Pages; Bit-Addressable

| Bit   | Name                                                         | Description                                                                                                                                  | Write                                                                         | Read                                                                    |  |  |  |

|-------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|

| 7:0   | P2[7:0]                                                      | <b>Port 2Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P2.n Port pin is logic<br>LOW.<br>1: P2.n Port pin is logic<br>HIGH. |  |  |  |

| Note: | Note: P2.2-P2.7 are available on 40-pin and 32-pin packages. |                                                                                                                                              |                                                                               |                                                                         |  |  |  |

#### 22.4.2. SMB0CN Control Register

SMB0CN is used to control the interface and to provide status information (see SFR Definition 22.2). The higher four bits of SMB0CN (MASTER, TXMODE, STA, and STO) form a status vector that can be used to jump to service routines. MASTER indicates whether a device is the master or slave during the current transfer. TXMODE indicates whether the device is transmitting or receiving data for the current byte.

STA and STO indicate that a START and/or STOP has been detected or generated since the last SMBus interrupt. STA and STO are also used to generate START and STOP conditions when operating as a master. Writing a 1 to STA will cause the SMBus interface to enter Master Mode and generate a START when the bus becomes free (STA is not cleared by hardware after the START is generated). Writing a 1 to STO while in Master Mode will cause the interface to generate a STOP and end the current transfer after the next ACK cycle. If STO and STA are both set (while in Master Mode), a STOP followed by a START will be generated.

As a receiver, writing the ACK bit defines the outgoing ACK value; as a transmitter, reading the ACK bit indicates the value received during the last ACK cycle. ACKRQ is set each time a byte is received, indicating that an outgoing ACK value is needed. When ACKRQ is set, software should write the desired outgoing value to the ACK bit before clearing SI. A NACK will be generated if software does not write the ACK bit before clearing SI. SDA will reflect the defined ACK value immediately following a write to the ACK bit; however SCL will remain low until SI is cleared. If a received slave address is not acknowledged, further slave events will be ignored until the next START is detected.

The ARBLOST bit indicates that the interface has lost an arbitration. This may occur anytime the interface is transmitting (master or slave). A lost arbitration while operating as a slave indicates a bus error condition. ARBLOST is cleared by hardware each time SI is cleared.

The SI bit (SMBus Interrupt Flag) is set at the beginning and end of each transfer, after each byte frame, or when an arbitration is lost; see Table 22.3 for more details.

**Important Note About the SI Bit:** The SMBus interface is stalled while SI is set; thus SCL is held low, and the bus is stalled until software clears SI.

### 24.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. Note that the NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 24.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPI0 with the SPIEN bit. Figure 24.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

### 24.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- 1. The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- 2. The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- 3. The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- 4. The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

# SFR Definition 24.2. SPI0CN: SPI0 Control

| Bit   | 7                                                                                                                                                                                 | 6                                                                                                                                                                                                                                                                               | 5                                                                                                                                                                                                                                                                                                                                                                                            | 4      | 3        | 2             | 1              | 0     |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|---------------|----------------|-------|--|--|

| Name  | s SPIF                                                                                                                                                                            | WCOL                                                                                                                                                                                                                                                                            | MODF                                                                                                                                                                                                                                                                                                                                                                                         | RXOVRN | NSSM     | D[1:0]        | TXBMT          | SPIEN |  |  |

| Туре  | R/W                                                                                                                                                                               | R/W                                                                                                                                                                                                                                                                             | R/W                                                                                                                                                                                                                                                                                                                                                                                          | R/W    | R/W      |               | R              | R/W   |  |  |

| Rese  | t 0                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                            | 0      | 0 1      |               | 1              | 0     |  |  |

| SFR A | ddress = 0xF8                                                                                                                                                                     | ; Bit-Addres                                                                                                                                                                                                                                                                    | Bit-Addressable; SFR Page = 0x00                                                                                                                                                                                                                                                                                                                                                             |        |          |               |                |       |  |  |

| Bit   | Name                                                                                                                                                                              |                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                              |        | Function | l             |                |       |  |  |

| 7     | SPIF                                                                                                                                                                              | This bit is<br>enabled, s<br>tine. This                                                                                                                                                                                                                                         | <b>SPI0 Interrupt Flag.</b><br>This bit is set to logic 1 by hardware at the end of a data transfer. If interrupts are enabled, setting this bit causes the CPU to vector to the SPI0 interrupt service routine. This bit is not automatically cleared by hardware. It must be cleared by soft-                                                                                              |        |          |               |                |       |  |  |

| 6     | 6 WCOL Write Collision Flag.<br>This bit is set to logic 1 by hardware (and generates a Swrite to the SPI0 data register was attempted while a da It must be cleared by software. |                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                              |        |          |               |                |       |  |  |

| 5     | MODF                                                                                                                                                                              | This bit is ter mode of                                                                                                                                                                                                                                                         | <b>Mode Fault Flag.</b><br>This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) when a master mode collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01).<br>This bit is not automatically cleared by hardware. It must be cleared by software.                                                                                                              |        |          |               | :0] = 01).     |       |  |  |

| 4     | RXOVRN                                                                                                                                                                            | N Receive Overrun Flag (valid in slave mode only).                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                              |        |          |               |                |       |  |  |

|       |                                                                                                                                                                                   | receive bu<br>current tra                                                                                                                                                                                                                                                       | This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) when the receive buffer still holds unread data from a previous transfer and the last bit of the current transfer is shifted into the SPI0 shift register. This bit is not automatically cleared by hardware. It must be cleared by software.                                                                        |        |          |               | ast bit of the |       |  |  |

| 3:2   | NSSMD[1:0]                                                                                                                                                                        | Slave Sel                                                                                                                                                                                                                                                                       | ect Mode.                                                                                                                                                                                                                                                                                                                                                                                    |        |          |               |                |       |  |  |

|       |                                                                                                                                                                                   | (See Sect<br>00: 3-Wire<br>01: 4-Wire<br>1x: 4-Wire                                                                                                                                                                                                                             | Selects between the following NSS operation modes:<br>(See Section 24.2 and Section 24.3).<br>00: 3-Wire Slave or 3-Wire Master Mode. NSS signal is not routed to a port pin.<br>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is an input to the device.<br>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the<br>device and will assume the value of NSSMD0. |        |          |               |                |       |  |  |

| 1     | TXBMT                                                                                                                                                                             | Transmit Buffer Empty.                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                              |        |          |               |                |       |  |  |

|       |                                                                                                                                                                                   | This bit will be set to logic 0 when new data has been written to the transmit buffer.<br>When data in the transmit buffer is transferred to the SPI shift register, this bit will<br>be set to logic 1, indicating that it is safe to write a new byte to the transmit buffer. |                                                                                                                                                                                                                                                                                                                                                                                              |        |          | this bit will |                |       |  |  |

| 0     | SPIEN                                                                                                                                                                             | SPI0 Enal<br>0: SPI disa<br>1: SPI ena                                                                                                                                                                                                                                          | abled.                                                                                                                                                                                                                                                                                                                                                                                       |        |          |               |                |       |  |  |

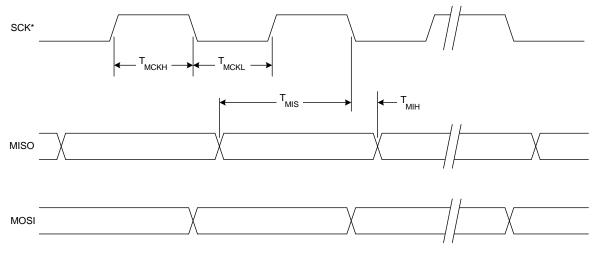

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

# Figure 24.9. SPI Master Timing (CKPHA = 1)

| Parameter                | Description                                                   | Min                          | Max                     | Units |  |

|--------------------------|---------------------------------------------------------------|------------------------------|-------------------------|-------|--|

| Master Mod               | <b>e Timing</b> <sup>*</sup> (See Figure 24.8 and Figure 24.9 | )                            |                         |       |  |

| т <sub>мскн</sub>        | SCK High Time                                                 | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |  |

| T <sub>MCKL</sub>        | SCK Low Time                                                  | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |  |

| T <sub>MIS</sub>         | MISO Valid to SCK Shift Edge                                  | 1 x T <sub>SYSCLK</sub> + 20 | —                       | ns    |  |

| Т <sub>МІН</sub>         | SCK Shift Edge to MISO Change                                 | 0                            | —                       | ns    |  |

| Slave Mode               | <b>Timing</b> <sup>*</sup> (See Figure 24.10 and Figure 24.1  | 1)                           |                         |       |  |

| T <sub>SE</sub>          | NSS Falling to First SCK Edge                                 | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |  |

| T <sub>SD</sub>          | Last SCK Edge to NSS Rising                                   | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |  |

| T <sub>SEZ</sub>         | NSS Falling to MISO Valid                                     | _                            | 4 x T <sub>SYSCLK</sub> | ns    |  |

| T <sub>SDZ</sub>         | NSS Rising to MISO High-Z                                     | _                            | 4 x T <sub>SYSCLK</sub> | ns    |  |

| т <sub>скн</sub>         | SCK High Time                                                 | 5 x T <sub>SYSCLK</sub>      | —                       | ns    |  |

| Т <sub>СКL</sub>         | SCK Low Time                                                  | 5 x T <sub>SYSCLK</sub>      | —                       | ns    |  |

| T <sub>SIS</sub>         | MOSI Valid to SCK Sample Edge                                 | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |  |

| T <sub>SIH</sub>         | SCK Sample Edge to MOSI Change                                | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |  |

| Т <sub>SOH</sub>         | SCK Shift Edge to MISO Change                                 | —                            | 4 x T <sub>SYSCLK</sub> | ns    |  |

| T <sub>SLH</sub>         | Last SCK Edge to MISO Change<br>(CKPHA = 1 ONLY)              | 6 x T <sub>SYSCLK</sub>      | 8 x T <sub>SYSCLK</sub> | ns    |  |

| *Note: T <sub>SYSC</sub> | LK is equal to one period of the device system cl             | ock (SYSCLK).                | 1                       |       |  |

# Table 24.1. SPI Slave Timing Parameters

# SFR Definition 25.1. CKCON: Clock Control

| Bit   | 7    | 6    | 5    | 4    | 3   | 2   | 1   | 0     |

|-------|------|------|------|------|-----|-----|-----|-------|

| Name  | ТЗМН | T3ML | T2MH | T2ML | T1M | ТОМ | SCA | [1:0] |

| Туре  | R/W  | R/W  | R/W  | R/W  | R/W | R/W | R/W |       |

| Reset | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0     |

#### SFR Address = 0x8E; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                          |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ТЗМН     | Timer 3 High Byte Clock Select.                                                                                                                                                                                                                                                                                   |

|     |          | Selects the clock supplied to the Timer 3 high byte (split 8-bit timer mode only).<br>0: Timer 3 high byte uses the clock defined by the T3XCLK bit in TMR3CN.<br>1: Timer 3 high byte uses the system clock.                                                                                                     |

| 6   | T3ML     | Timer 3 Low Byte Clock Select.                                                                                                                                                                                                                                                                                    |

|     |          | <ul><li>Selects the clock supplied to Timer 3. Selects the clock supplied to the lower 8-bit timer in split 8-bit timer mode.</li><li>0: Timer 3 low byte uses the clock defined by the T3XCLK bit in TMR3CN.</li><li>1: Timer 3 low byte uses the system clock.</li></ul>                                        |

|     | T2MH     |                                                                                                                                                                                                                                                                                                                   |

| 5   | 12MH     | <ul> <li>Timer 2 High Byte Clock Select.</li> <li>Selects the clock supplied to the Timer 2 high byte (split 8-bit timer mode only).</li> <li>0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 high byte uses the system clock.</li> </ul>                            |

| 4   | T2ML     | Timer 2 Low Byte Clock Select.                                                                                                                                                                                                                                                                                    |

|     |          | <ul> <li>Selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer mode, this bit selects the clock supplied to the lower 8-bit timer.</li> <li>0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 low byte uses the system clock.</li> </ul> |

| 3   | T1       | Timer 1 Clock Select.                                                                                                                                                                                                                                                                                             |

|     |          | Selects the clock source supplied to Timer 1. Ignored when C/T1 is set to 1.<br>0: Timer 1 uses the clock defined by the prescale bits SCA[1:0].<br>1: Timer 1 uses the system clock.                                                                                                                             |

| 2   | Т0       | Timer 0 Clock Select.                                                                                                                                                                                                                                                                                             |

|     |          | Selects the clock source supplied to Timer 0. Ignored when C/T0 is set to 1.<br>0: Counter/Timer 0 uses the clock defined by the prescale bits SCA[1:0].<br>1: Counter/Timer 0 uses the system clock.                                                                                                             |

| 1:0 | SCA[1:0] | Timer 0/1 Prescale Bits.                                                                                                                                                                                                                                                                                          |

|     |          | These bits control the Timer 0/1 Clock Prescaler:<br>00: System clock divided by 12<br>01: System clock divided by 4<br>10: System clock divided by 48<br>11: External clock divided by 8 (synchronized with the system clock)                                                                                    |

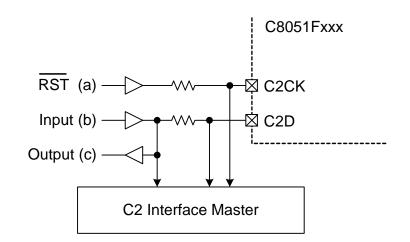

## 27.2. C2 Pin Sharing

The C2 protocol allows the C2 pins to be shared with user functions so that in-system debugging and Flash programming may be performed. This is possible because C2 communication is typically performed when the device is in the halt state, where all on-chip peripherals and user software are stalled. In this halted state, the C2 interface can safely 'borrow' the C2CK (RST) and C2D pins. In most applications, external resistors are required to isolate C2 interface traffic from the user application. A typical isolation configuration is shown in Figure 27.1.

Figure 27.1. Typical C2 Pin Sharing

The configuration in Figure 27.1 assumes the following:

- 1. The user input (b) cannot change state while the target device is halted.

- 2. The  $\overline{\text{RST}}$  pin on the target device is used as an input only.

Additional resistors may be necessary depending on the specific application.

303