Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), CANbus, SPI, UART/USART       |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 18                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 18x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-WFQFN Exposed Pad                                           |

| Supplier Device Package    | 24-QFN (4x4)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f551-im |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1. System Overview                                    | 16 |

|-------------------------------------------------------|----|

| 2. Ordering Information                               |    |

| 3. Pin Definitions                                    |    |

| 4. Package Specifications                             | 28 |

| 4.1. QFN-40 Package Specifications                    |    |

| 4.2. QFP-32 Package Specifications                    | 30 |

| 4.3. QFN-32 Package Specifications                    |    |

| 4.4. QFN-24 Package Specifications                    |    |

| 5. Electrical Characteristics                         | 36 |

| 5.1. Absolute Maximum Specifications                  | 36 |

| 5.2. Electrical Characteristics                       | 37 |

| 6. 12-Bit ADC (ADC0)                                  |    |

| 6.1. Modes of Operation                               | 48 |

| 6.1.1. Starting a Conversion                          |    |

| 6.1.2. Tracking Modes                                 |    |

| 6.1.3. Timing                                         |    |

| 6.1.4. Burst Mode                                     |    |

| 6.2. Output Code Formatting                           |    |

| 6.2.1. Settling Time Requirements                     | 52 |

| 6.3. Selectable Ğain                                  | 53 |

| 6.3.1. Calculating the Gain Value                     |    |

| 6.3.2. Setting the Gain Value                         |    |

| 6.4. Programmable Window Detector                     |    |

| 6.4.1. Window Detector In Single-Ended Mode           |    |

| 6.5. ADC0 Analog Multiplexer                          |    |

| 6.6. Temperature Sensor                               |    |

| 7. Voltage Reference                                  |    |

| 8. Comparators                                        |    |

| 8.1. Comparator Multiplexer                           |    |

| 9. Voltage Regulator (REG0)                           |    |

| 10. CIP-51 Microcontroller.                           |    |

| 10.1. Performance                                     | 81 |

| 10.2. Instruction Set                                 | 83 |

| 10.2.1. Instruction and CPU Timing                    | 83 |

| 10.3. CIP-51 Register Descriptions                    |    |

| 10.4. Serial Number Special Function Registers (SFRs) |    |

| 11. Memory Organization                               |    |

| 11.1. Program Memory                                  |    |

| 11.1.1. MOVX Instruction and Program Memory           |    |

| 11.2. Data Memory                                     |    |

| 11.2.1. Internal RAM                                  | 93 |

| 12. Special Function Registers                        |    |

| 12.1. SFR Paging                                      |    |

## 6.1. Modes of Operation

In a typical system, ADC0 is configured using the following steps:

- 1. If a gain adjustment is required, refer to Section "6.3. Selectable Gain" on page 53.

- 2. Choose the start of conversion source.

- 3. Choose Normal Mode or Burst Mode operation.

- 4. If Burst Mode, choose the ADC0 Idle Power State and set the Power-up Time.

- 5. Choose the tracking mode. Note that Pre-Tracking Mode can only be used with Normal Mode.

- 6. Calculate the required settling time and set the post convert-start tracking time using the AD0TK bits.

- 7. Choose the repeat count.

- 8. Choose the output word justification (Right-Justified or Left-Justified).

- 9. Enable or disable the End of Conversion and Window Comparator Interrupts.

#### 6.1.1. Starting a Conversion

A conversion can be initiated in one of four ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM1–0) in register ADC0CN. Conversions may be initiated by one of the following:

- Writing a 1 to the AD0BUSY bit of register ADC0CN

- A rising edge on the CNVSTR input signal (pin P0.1)

- A Timer 1 overflow (i.e., timed continuous conversions)

- A Timer 2 overflow (i.e., timed continuous conversions)

Writing a 1 to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand." During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). Note: When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. Note that when Timer 2 overflows are used as the conversion source, Low Byte overflows are used if Timer2 is in 8-bit mode; High byte overflows are used if Timer 2 is in 16-bit mode. See Section "25. Timers" on page 259 for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as Port pin P0.1. When the CNVSTR input is used as the ADC0 conversion source, Port pin P0.1 should be skipped by the Digital Crossbar. To configure the Crossbar to skip P0.1, set to 1 Bit1 in register P0SKIP. See Section "19. Port Input/Output" on page 169 for details on Port I/O configuration.

#### 6.1.2. Tracking Modes

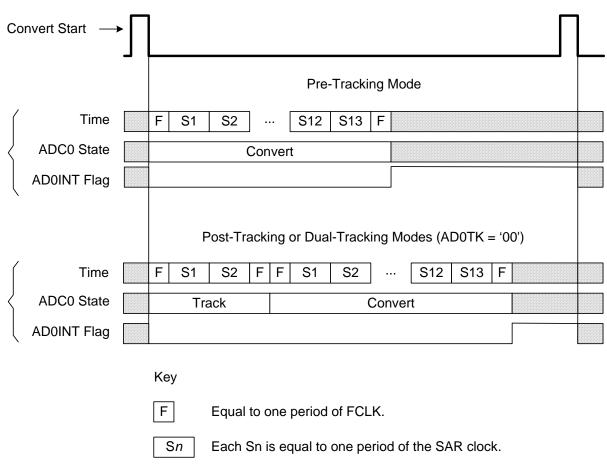

Each ADC0 conversion must be preceded by a minimum tracking time for the converted result to be accurate. ADC0 has three tracking modes: Pre-Tracking, Post-Tracking, and Dual-Tracking. Pre-Tracking Mode provides the minimum delay between the convert start signal and end of conversion by tracking continuously before the convert start signal. This mode requires software management in order to meet minimum tracking requirements. In Post-Tracking Mode, a programmable tracking time starts after the convert start signal and is managed by hardware. Dual-Tracking Mode maximizes tracking time by tracking before and after the convert start signal. Figure 6.2 shows examples of the three tracking modes.

Pre-Tracking Mode is selected when AD0TM is set to 10b. Conversions are started immediately following the convert start signal. ADC0 is tracking continuously when not performing a conversion. Software must allow at least the minimum tracking time between each end of conversion and the next convert start signal. The minimum tracking time must also be met prior to the first convert start signal after ADC0 is enabled.

# C8051F55x/56x/57x

Figure 6.3. 12-Bit ADC Tracking Mode Example

#### 6.1.4. Burst Mode

Burst Mode is a power saving feature that allows ADC0 to remain in a very low power state between conversions. When Burst Mode is enabled, ADC0 wakes from a very low power state, accumulates 1, 4, 8, or 16 samples using an internal Burst Mode clock (approximately 25 MHz), then re-enters a very low power state. Since the Burst Mode clock is independent of the system clock, ADC0 can perform multiple conversions then enter a very low power state within a single system clock cycle, even if the system clock is slow (e.g., 32.768 kHz), or suspended.

Burst Mode is enabled by setting BURSTEN to logic 1. When in Burst Mode, AD0EN controls the ADC0 idle power state (i.e. the state ADC0 enters when not tracking or performing conversions). If AD0EN is set to logic 0, ADC0 is powered down after each burst. If AD0EN is set to logic 1, ADC0 remains enabled after each burst. On each convert start signal, ADC0 is awakened from its Idle Power State. If AD0C0 is powered down, it will automatically power up and wait the programmable Power-up Time controlled by the AD0PWR bits. Otherwise, ADC0 will start tracking and converting immediately. Figure 6.4 shows an example of Burst Mode Operation with a slow system clock and a repeat count of 4.

Important Note: When Burst Mode is enabled, only Post-Tracking and Dual-Tracking modes can be used.

When Burst Mode is enabled, a single convert start will initiate a number of conversions equal to the repeat count. When Burst Mode is disabled, a convert start is required to initiate each conversion. In both modes, the ADC0 End of Conversion Interrupt Flag (AD0INT) will be set after "repeat count" conversions have

#### 6.3.2. Setting the Gain Value

The three programmable gain registers are accessed indirectly using the ADC0H and ADC0L registers when the GAINEN bit (ADC0CF.0) bit is set. ADC0H acts as the address register, and ADC0L is the data register. The programmable gain registers can only be written to and cannot be read. See Gain Register Definition 6.1, Gain Register Definition 6.2, and Gain Register Definition 6.3 for more information.

The gain is programmed using the following steps:

- 1. Set the GAINEN bit (ADC0CF.0)

- 2. Load the ADC0H with the ADC0GNH, ADC0GNL, or ADC0GNA address.

- 3. Load ADC0L with the desired value for the selected gain register.

- 4. Reset the GAINEN bit (ADC0CF.0)

#### Notes:

- 1. An ADC conversion should not be performed while the GAINEN bit is set.

- 2. Even with gain enabled, the maximum input voltage must be less than V<sub>REGIN</sub> and the maximum voltage of the signal after gain must be less than or equal to V<sub>REF</sub>.

In code, changing the value to 0.44 gain from the previous example looks like:

// in 'C':

MOV ADC0H,#07H MOV ADC0L,#0A0H

MOV ADC0H,#08H

MOV ADC0L,#01H

ANL ADCOCF,#0FEH

| ADC0CF  = 0x01;  | // GAINEN = 1                                |

|------------------|----------------------------------------------|

| ADC0H = 0x04;    | // Load the ADC0GNH address                  |

| ADC0L = 0x6C;    | // Load the upper byte of 0x6CA to ADC0GNH   |

| ADC0H = 0x07;    | // Load the ADC0GNL address                  |

| ADC0L = 0xA0;    | // Load the lower nibble of 0x6CA to ADC0GNL |

| ADC0H = 0x08;    | // Load the ADC0GNA address                  |

| ADC0L = 0x01;    | // Set the GAINADD bit                       |

| ADC0CF &= ~0x01; | // GAINEN = 0                                |

|                  |                                              |

| ; in assembly    |                                              |

| ORL ADC0CF,#01H  | ; GAINEN = 1                                 |

| MOV ADC0H,#04H   | ; Load the ADC0GNH address                   |

| MOV ADC0L,#06CH  | ; Load the upper byte of 0x6CA to ADC0GNH    |

- ; Load the upper byte of 0x6CA to ADC0GNH

- : Load the ADC0GNL address

- ; Load the lower nibble of 0x6CA to ADC0GNL

- : Load the ADC0GNA address

- : Set the GAINADD bit

- ; GAINEN = 0

## SFR Definition 6.5. ADC0H: ADC0 Data Word MSB

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|---|---|---|---|---|--|

| Name  | ADC0H[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xBE; SFR Page = 0x00

| Bit | Name       | Function                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0H[7:0] | ADC0 Data Word High-Order Bits.                                                                        |

|     |            | For AD0LJST = 0 and AD0RPT as follows:                                                                 |

|     |            | 00: Bits 3–0 are the upper 4 bits of the 12-bit result. Bits 7–4 are 0000b.                            |

|     |            | 01: Bits 4–0 are the upper 5 bits of the 14-bit result. Bits 7–5 are 000b.                             |

|     |            | 10: Bits 5–0 are the upper 6 bits of the 15-bit result. Bits 7–6 are 00b.                              |

|     |            | 11: Bits 7–0 are the upper 8 bits of the 16-bit result.                                                |

|     |            | For AD0LJST = 1 (AD0RPT must be 00): Bits 7–0 are the most-significant bits of the ADC0 12-bit result. |

## SFR Definition 6.6. ADC0L: ADC0 Data Word LSB

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|---|---|---|---|---|--|

| Name  | ADC0L[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xBD; SFR Page = 0x00

| Bit | Name | Function                                                                                                                                                                                                                              |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 |      | ADC0 Data Word Low-Order Bits.<br>For AD0LJST = 0: Bits 7–0 are the lower 8 bits of the ADC0 Accumulated Result.<br>For AD0LJST = 1 (AD0RPT must be '00'): Bits 7–4 are the lower 4 bits of the 12-bit<br>result. Bits 3–0 are 0000b. |

## 12.3. SFR Page Stack Example

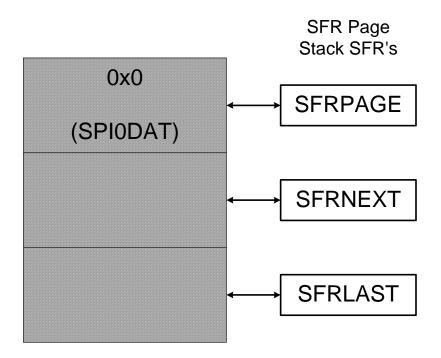

The following is an example that shows the operation of the SFR Page Stack during interrupts. In this example, the SFR Control register is left in the default enabled state (i.e., SFRPGEN = 1), and the CIP-51 is executing in-line code that is writing values to SPI Data Register (SFR "SPI0DAT", located at address 0xA3 on SFR Page 0x00). The device is also using the CAN peripheral (CAN0) and the Programmable Counter Array (PCA0) peripheral to generate a PWM output. The PCA is timing a critical control function in its interrupt service and so its associated ISR that is set to high priority. At this point, the SFR page is set to access the SPI0DAT SFR (SFRPAGE = 0x00). See Figure 12.2.

Figure 12.2. SFR Page Stack While Using SFR Page 0x0 To Access SPI0DAT

#### Table 13.1. Interrupt Summary

| Interrupt Source               | Vector Order |     | Bit addressable?                                                           | Cleared by HW? | Enable<br>Flag | Priority<br>Control |                    |

|--------------------------------|--------------|-----|----------------------------------------------------------------------------|----------------|----------------|---------------------|--------------------|

| Reset                          | 0x0000       | Тор | None                                                                       | N/A            | N/A            | Always<br>Enabled   | Always<br>Highest  |

| External Interrupt 0<br>(INT0) | 0x0003       | 0   | IE0 (TCON.1)                                                               | Y              | Y              | EX0 (IE.0)          | PX0 (IP.0)         |

| Timer 0 Overflow               | 0x000B       | 1   | TF0 (TCON.5)                                                               | Y              | Y              | ET0 (IE.1)          | PT0 (IP.1)         |

| External Interrupt 1<br>(INT1) | 0x0013       | 2   | IE1 (TCON.3)                                                               | Y              | Y              | EX1 (IE.2)          | PX1 (IP.2)         |

| Timer 1 Overflow               | 0x001B       | 3   | TF1 (TCON.7)                                                               | Y              | Y              | ET1 (IE.3)          | PT1 (IP.3)         |

| UART0                          | 0x0023       | 4   | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y              | N              | ES0 (IE.4)          | PS0 (IP.4)         |

| Timer 2 Overflow               | 0x002B       | 5   | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y              | N              | ET2 (IE.5)          | PT2 (IP.5)         |

| SPI0                           | 0x0033       | 6   | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y              | N              | ESPI0<br>(IE.6)     | PSPI0<br>(IP.6)    |

| SMB0                           | 0x003B       | 7   | SI (SMB0CN.0)                                                              | Y              | Ν              | ESMB0<br>(EIE1.0)   | PSMB0<br>(EIP1.0)  |

| ADC0 Window Com-<br>pare       | 0x0043       | 8   | ADOWINT<br>(ADC0CN.3)                                                      | Y              | N              | EWADC0<br>(EIE1.1)  | PWADC0<br>(EIP1.1) |

| ADC0 Conversion<br>Complete    | 0x004B       | 9   | AD0INT (ADC0CN.5)                                                          | Y              | N              | EADC0<br>(EIE1.2)   | PADC0<br>(EIP1.2)  |

| Programmable<br>Counter Array  | 0x0053       | 10  | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)<br>COVF (PCA0PWM.6)                       | Y              | N              | EPCA0<br>(EIE1.3)   | PPCA0<br>(EIP1.3)  |

| Comparator0                    | 0x005B       | 11  | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | N              | N              | ECP0<br>(EIE1.4)    | PCP0<br>(EIP1.4)   |

| Comparator1                    | 0x0063       | 12  | CP1FIF (CPT1CN.4)<br>CP1RIF (CPT1CN.5)                                     | N              | N              | ECP1<br>(EIE1.5)    | PCP1<br>(EIP1.5)   |

| Timer 3 Overflow               | 0x006B       | 13  | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | N              | N              | ET3<br>(EIE1.6)     | PT3<br>(EIP1.6)    |

| LINO                           | 0x0073       | 14  | LINOINT (LINST.3)                                                          | N              | N*             | ELIN0<br>(EIE1.7)   | PLIN0<br>(EIP1.7)  |

| Voltage Regulator<br>Dropout   | 0x007B       | 15  | N/A                                                                        | N/A            | N/A            | EREG0<br>(EIE2.0)   | PREG0<br>(EIP2.0)  |

| CAN0                           | 0x0083       | 16  | CAN0INT<br>(CAN0CN.7)                                                      | N              | Y              | ECAN0<br>(EIE2.1)   | PCAN0<br>(EIP2.1)  |

| Port Match                     | 0x008B       | 17  | None                                                                       | N/A            | N/A            | EMAT<br>(EIE2.2)    | PMAT<br>(EIP2.2)   |

### 14.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. Note: MOVX read instructions always target XRAM.

## 14.3. Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to 1 before software can modify the Flash memory; both PSWE and PSEE must be set to 1 before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

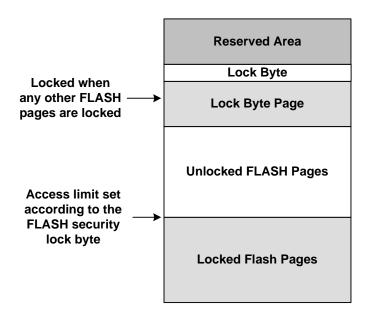

A Security Lock Byte located at the last byte of Flash user space offers protection of the Flash program memory from access (reads, writes, or erases) by unprotected code or the C2 interface. The Flash security mechanism allows the user to lock n 512-byte Flash pages, starting at page 0 (addresses 0x0000 to 0x01FF), where n is the ones complement number represented by the Security Lock Byte. Note that the page containing the Flash Security Lock Byte is unlocked when no other Flash pages are locked (all bits of the Lock Byte are 1) and locked when any other Flash pages are locked (any bit of the Lock Byte is 0). See example in Figure 14.1.

| Security Lock Byte: | 11111101b                                  |

|---------------------|--------------------------------------------|

| 1s Complement:      | 0000010b                                   |

| Flash pages locked: | 3 (First two Flash pages + Lock Byte Page) |

Figure 14.1. Flash Program Memory Map

## SFR Definition 14.3. FLSCL: Flash Scale

| Bit   | 7        | 6        | 5        | 4    | 3        | 2        | 1     | 0        |

|-------|----------|----------|----------|------|----------|----------|-------|----------|

| Name  | Reserved | Reserved | Reserved | FLRT | Reserved | Reserved | FLEWT | Reserved |

| Туре  | R/W      | R/W      | R/W      | R/W  | R/W      | R/W      | R/W   | R/W      |

| Reset | 0        | 0        | 0        | 0    | 0        | 0        | 0     | 0        |

## SFR Address = 0xB6; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                            |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Reserved | Must Write 000b.                                                                                                                                                                                                                                                    |

| 4   | FLRT     | Flash Read Time Control.                                                                                                                                                                                                                                            |

|     |          | <ul> <li>This bit should be programmed to the smallest allowed value, according to the system clock speed.</li> <li>0: SYSCLK ≤ 25 MHz (Flash read strobe is one system clock).</li> <li>1: SYSCLK &gt; 25 MHz (Flash read strobe is two system clocks).</li> </ul> |

| 3:2 | Reserved | Must Write 00b.                                                                                                                                                                                                                                                     |

| 1   | FLEWT    | Flash Erase Write Time Control.<br>This bit should be set to 1b before Writing or Erasing Flash.<br>0: Short Flash Erase / Write Timing.<br>1: Extended Flash Erase / Write Timing.                                                                                 |

| 0   | Reserved | Must Write 0b.                                                                                                                                                                                                                                                      |

## SFR Definition 15.1. PCON: Power Control

| Bit   | 7 | 6    | 5    | 4   | 3 | 2 | 1 | 0 |

|-------|---|------|------|-----|---|---|---|---|

| Name  |   | STOP | IDLE |     |   |   |   |   |

| Туре  |   |      | R/W  | R/W |   |   |   |   |

| Reset | 0 | 0    | 0    | 0   | 0 | 0 | 0 | 0 |

SFR Address = 0x87; SFR Page = All Pages

| Bit | Name    | Function                                                                                                                                                                                                                                                                   |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | GF[5:0] | General Purpose Flags 5–0.<br>These are general purpose flags for use under software control.                                                                                                                                                                              |

| 1   | STOP    | Stop Mode Select.Setting this bit will place the CIP-51 in Stop mode. This bit will always be read as 0.1: CPU goes into Stop mode (internal oscillator stopped).                                                                                                          |

| 0   | IDLE    | <b>IDLE: Idle Mode Select.</b><br>Setting this bit will place the CIP-51 in Idle mode. This bit will always be read as 0.<br>1: CPU goes into Idle mode. (Shuts off clock to CPU, but clock to Timers, Interrupts, Serial Ports, and Analog Peripherals are still active.) |

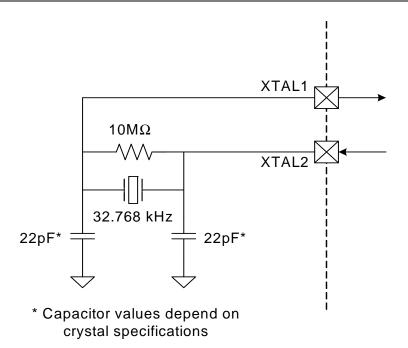

#### Figure 18.3. External 32.768 kHz Quartz Crystal Oscillator Connection Diagram

#### 18.4.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 18.1, Option 2. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation, according to Equation 18.1, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and R = the pull-up resistor value in k $\Omega$ .

$$f = 1.23 \times 10^3 / (R \times C)$$

#### Equation 18.1. RC Mode Oscillator Frequency

For example: If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

f = 1.23(10<sup>3</sup>)/RC = 1.23(10<sup>3</sup>)/[246 x 50] = 0.1 MHz = 100 kHz

Referring to the table in SFR Definition 18.6, the required XFCN setting is 010b.

#### 18.4.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 18.1, Option 3. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation , where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and  $V_{DD}$  = the MCU power supply in Volts.

## 21.2. CAN Registers

CAN registers are classified as follows:

- 1. CAN Controller Protocol Registers: CAN control, interrupt, error control, bus status, test modes.

- Message Object Interface Registers: Used to configure 32 Message Objects, send and receive data to and from Message Objects. The CIP-51 MCU accesses the CAN message RAM via the Message Object Interface Registers. Upon writing a message object number to an IF1 or IF2 Command Request Register, the contents of the associated Interface Registers (IF1 or IF2) will be transferred to or from the message object in CAN RAM.

- 3. **Message Handler Registers**: These read only registers are used to provide information to the CIP-51 MCU about the message objects (MSGVLD flags, Transmission Request Pending, New Data Flags) and Interrupts Pending (which Message Objects have caused an interrupt or status interrupt condition).

For the registers other than CAN0CFG, refer to the Bosch CAN User's Guide for information on the function and use of the CAN Control Protocol Registers.

#### 21.2.1. CAN Controller Protocol Registers

The CAN Control Protocol Registers are used to configure the CAN controller, process interrupts, monitor bus status, and place the controller in test modes.

The registers are: CAN Control Register (CAN0CN), CAN Clock Configuration (CAN0CFG), CAN Status Register (CAN0STA), CAN Test Register (CAN0TST), Error Counter Register, Bit Timing Register, and the Baud Rate Prescaler (BRP) Extension Register.

#### 21.2.2. Message Object Interface Registers

There are two sets of Message Object Interface Registers used to configure the 32 Message Objects that transmit and receive data to and from the CAN bus. Message objects can be configured for transmit or receive, and are assigned arbitration message identifiers for acceptance filtering by all CAN nodes.

Message Objects are stored in Message RAM, and are accessed and configured using the Message Object Interface Registers.

#### 21.2.3. Message Handler Registers

The Message Handler Registers are read only registers. The message handler registers provide interrupt, error, transmit/receive requests, and new data information.

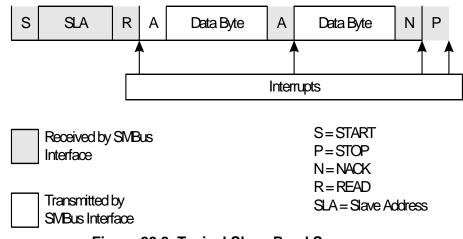

#### 22.5.4. Read Sequence (Slave)

During a read sequence, an SMBus master reads data from a slave device. The slave in this transfer will be a receiver during the address byte, and a transmitter during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode (to receive the slave address) when a START followed by a slave address and direction bit (READ in this case) is received. Upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. The interrupt will occur after the ACK cycle.

If the received slave address is ignored, slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are transmitted. If the received slave address is acknowledged, data should be written to SMB0DAT to be transmitted. The interface enters Slave Transmitter Mode, and transmits one or more bytes of data. After each byte is transmitted, the master sends an acknowledge bit; if the acknowledge bit is an ACK, SMB0DAT should be written with the next data byte. If the acknowledge bit is a NACK, SMB0DAT should not be written to before SI is cleared (Note: an error condition may be generated if SMB0DAT is written following a received NACK while in Slave Transmitter Mode). The interface exits Slave Transmitter Mode after receiving a STOP. Note that the interface will switch to Slave Receiver Mode if SMB0DAT is not written following a Slave Transmitter interrupt. Figure 22.8 shows a typical slave read sequence. Two transmitted data bytes are shown, though any number of bytes may be transmitted. Notice that all of the 'data byte transferred' interrupts occur **after** the ACK cycle in this mode.

#### 22.6. SMBus Status Decoding

The current SMBus status can be easily decoded using the SMB0CN register. In the tables, STATUS VECTOR refers to the four upper bits of SMB0CN: MASTER, TXMODE, STA, and STO. The shown response options are only the typical responses; application-specific procedures are allowed as long as they conform to the SMBus specification. Highlighted responses are allowed by hardware but do not conform to the SMBus specification.

# C8051F55x/56x/57x

|                    | Values Read      |   |   | ad      |     | Current SMbus State                             | Typical Response Options                                                                       | Values to<br>Write |     |     | ecte                           |

|--------------------|------------------|---|---|---------|-----|-------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------|-----|-----|--------------------------------|

| Mode               | Status<br>Vector |   |   | ARBLOST | ACK |                                                 |                                                                                                | STA                | STO | ACK | Next Status<br>Vector Expected |

|                    | 1110             | ( | 0 | 0       | Х   | A master START was gener-<br>ated.              | Load slave address + R/W into SMB0DAT.                                                         | 0                  | 0   | Х   | 1100                           |

|                    | 1100             | ( | 0 | 0       | 0   | A master data or address byte                   | Set STA to restart transfer.                                                                   | 1                  | 0   | Х   | 1110                           |

|                    |                  |   |   |         |     | was transmitted; NACK received.                 | Abort transfer.                                                                                | 0                  | 1   | Х   | _                              |

|                    |                  | ( | 0 | 0       | 1   | was transmitted; ACK                            | Load next data byte into SMB0-<br>DAT.                                                         | 0                  | 0   | Х   | 1100                           |

|                    |                  |   |   |         |     | received.                                       | End transfer with STOP.                                                                        | 0                  | 1   | Х   | _                              |

| smitter            |                  |   |   |         |     |                                                 | End transfer with STOP and start another transfer.                                             | 1                  | 1   | Х   | —                              |

| rans               |                  |   |   |         |     |                                                 | Send repeated START.                                                                           | 1                  | 0   | Х   | 1110                           |

| Master Transmitter |                  |   |   |         |     |                                                 | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT).           | 0                  | 0   | Х   | 1000                           |

|                    | 1000             |   | 1 | 0       | Х   | A master data byte was received; ACK requested. | Acknowledge received byte;<br>Read SMB0DAT.                                                    | 0                  | 0   | 1   | 1000                           |

|                    |                  |   |   |         |     |                                                 | Send NACK to indicate last byte, and send STOP.                                                | 0                  | 1   | 0   | —                              |

|                    |                  |   |   |         |     |                                                 | Send NACK to indicate last byte,<br>and send STOP followed by<br>START.                        | 1                  | 1   | 0   | 1110                           |

|                    |                  |   |   |         |     |                                                 | Send ACK followed by repeated START.                                                           | 1                  | 0   | 1   | 1110                           |

|                    |                  |   |   |         |     |                                                 | Send NACK to indicate last byte, and send repeated START.                                      | 1                  | 0   | 0   | 1110                           |

| eceiver            |                  |   |   |         |     |                                                 | Send ACK and switch to Master<br>Transmitter Mode (write to<br>SMB0DAT before clearing SI).    | 0                  | 0   | 1   | 1100                           |

| Master Receiver    |                  |   |   |         |     |                                                 | Send NACK and switch to Mas-<br>ter Transmitter Mode (write to<br>SMB0DAT before clearing SI). | 0                  | 0   | 0   | 1100                           |

Table 22.4. SMBus Status Decoding

## SFR Definition 24.2. SPI0CN: SPI0 Control

| Bit   | 7                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                                                                                                                                                                                                                                    | 5                                                                                                                                                                                                                                                                                               | 4             | 3                             | 2                            | 1                                                      | 0              |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------|------------------------------|--------------------------------------------------------|----------------|--|--|--|

| Name  | s SPIF                                                                                                                                                                                                                                                                                                                                                                                       | WCOL                                                                                                                                                                                                                                                                                 | MODF                                                                                                                                                                                                                                                                                            | RXOVRN        | NSSM                          | D[1:0]                       | TXBMT                                                  | SPIEN          |  |  |  |

| Туре  | R/W                                                                                                                                                                                                                                                                                                                                                                                          | R/W                                                                                                                                                                                                                                                                                  | R/W                                                                                                                                                                                                                                                                                             | R/W           | R/                            | R/W                          |                                                        | R/W            |  |  |  |

| Rese  | t 0                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                               | 0             | 0                             | 0 1                          |                                                        | 0              |  |  |  |

| SFR A | ddress = 0xF8                                                                                                                                                                                                                                                                                                                                                                                | ; Bit-Addres                                                                                                                                                                                                                                                                         | Bit-Addressable; SFR Page = 0x00                                                                                                                                                                                                                                                                |               |                               |                              |                                                        |                |  |  |  |

| Bit   | Name                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                      | Function                                                                                                                                                                                                                                                                                        |               |                               |                              |                                                        |                |  |  |  |

| 7     | SPIF                                                                                                                                                                                                                                                                                                                                                                                         | This bit is<br>enabled, s<br>tine. This                                                                                                                                                                                                                                              | <b>SPI0 Interrupt Flag.</b><br>This bit is set to logic 1 by hardware at the end of a data transfer. If interrupts are enabled, setting this bit causes the CPU to vector to the SPI0 interrupt service routine. This bit is not automatically cleared by hardware. It must be cleared by soft- |               |                               |                              |                                                        |                |  |  |  |

| 6     | WCOL                                                                                                                                                                                                                                                                                                                                                                                         | Write Col<br>This bit is<br>write to the                                                                                                                                                                                                                                             | ware.<br>Write Collision Flag.<br>This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) to indicate a<br>write to the SPI0 data register was attempted while a data transfer was in progress.<br>It must be cleared by software.                                              |               |                               |                              |                                                        |                |  |  |  |

| 5     | MODF                                                                                                                                                                                                                                                                                                                                                                                         | MODF <b>Mode Fault Flag.</b><br>This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) when a master mode collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01).<br>This bit is not automatically cleared by hardware. It must be cleared by software. |                                                                                                                                                                                                                                                                                                 |               |                               |                              |                                                        |                |  |  |  |

| 4     | RXOVRN                                                                                                                                                                                                                                                                                                                                                                                       | Receive C                                                                                                                                                                                                                                                                            | Overrun Fla                                                                                                                                                                                                                                                                                     | g (valid in s | lave mode                     | only).                       |                                                        |                |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                              | receive bu<br>current tra                                                                                                                                                                                                                                                            | uffer still hold<br>ansfer is shif                                                                                                                                                                                                                                                              | ds unread da  | ta from a pr<br>SPI0 shift re | evious trans<br>gister. This | Pl0 interrupt) v<br>sfer and the la<br>bit is not auto | ast bit of the |  |  |  |

| 3:2   | NSSMD[1:0]                                                                                                                                                                                                                                                                                                                                                                                   | Slave Sel                                                                                                                                                                                                                                                                            | ect Mode.                                                                                                                                                                                                                                                                                       |               |                               |                              |                                                        |                |  |  |  |

|       | Selects between the following NSS operation modes:<br>(See Section 24.2 and Section 24.3).<br>00: 3-Wire Slave or 3-Wire Master Mode. NSS signal is not routed to a port pin.<br>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is an input to the device.<br>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the<br>device and will assume the value of NSSMD0. |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                 |               |                               |                              |                                                        |                |  |  |  |

| 1     | TXBMT                                                                                                                                                                                                                                                                                                                                                                                        | Transmit                                                                                                                                                                                                                                                                             | Transmit Buffer Empty.                                                                                                                                                                                                                                                                          |               |                               |                              |                                                        |                |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                              | This bit will be set to logic 0 when new data has been written to the transmit buffer.<br>When data in the transmit buffer is transferred to the SPI shift register, this bit will<br>be set to logic 1, indicating that it is safe to write a new byte to the transmit buffer.      |                                                                                                                                                                                                                                                                                                 |               |                               |                              |                                                        |                |  |  |  |

| 0     | SPIEN     SPI0 Enable.       0: SPI disabled.       1: SPI enabled.                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                 |               |                               |                              |                                                        |                |  |  |  |

## SFR Definition 25.4. TL0: Timer 0 Low Byte

| Bit                                      | 7          | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|------------------------------------------|------------|----------|---|---|---|---|---|---|--|--|--|

| Name                                     | e          | TL0[7:0] |   |   |   |   |   |   |  |  |  |

| Туре                                     | •          | R/W      |   |   |   |   |   |   |  |  |  |

| Rese                                     | <b>t</b> 0 | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| SFR Address = 0x8A; SFR Page = All Pages |            |          |   |   |   |   |   |   |  |  |  |

| Bit                                      | Name       | Function |   |   |   |   |   |   |  |  |  |

|                                          |            |          |   |   |   |   |   |   |  |  |  |

| 7:0 | TL0[7:0] | Timer 0 Low Byte.                                       |

|-----|----------|---------------------------------------------------------|

|     |          | The TL0 register is the low byte of the 16-bit Timer 0. |

## SFR Definition 25.5. TL1: Timer 1 Low Byte

| Bit   | 7             | 6                                                       | 5           | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---------------|---------------------------------------------------------|-------------|---|---|---|---|---|--|--|--|

| Nam   | e             | TL1[7:0]                                                |             |   |   |   |   |   |  |  |  |

| Туре  | 9             | R/W                                                     |             |   |   |   |   |   |  |  |  |

| Rese  | et 0          | 0                                                       | 0           | 0 | 0 | 0 | 0 | 0 |  |  |  |

| SFR A | Address = 0x8 | B; SFR Page                                             | = All Pages | ; |   |   |   |   |  |  |  |

| Bit   | Name          | Name Function                                           |             |   |   |   |   |   |  |  |  |

| 7:0   | TL1[7:0]      | TL1[7:0] Timer 1 Low Byte.                              |             |   |   |   |   |   |  |  |  |

|       |               | The TL1 register is the low byte of the 16-bit Timer 1. |             |   |   |   |   |   |  |  |  |

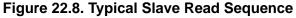

## 26. Programmable Counter Array

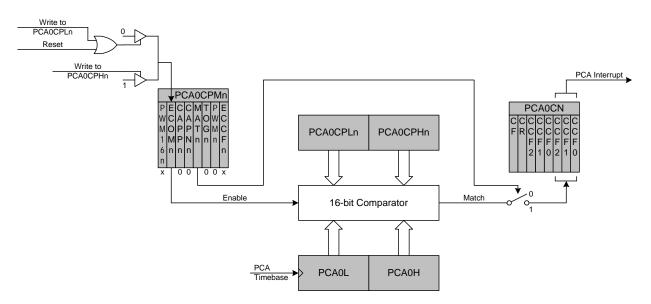

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and six 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled. The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, Timer 0 overflows, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8 to 11-Bit PWM, or 16-Bit PWM (each mode is described in Section "26.3. Capture/Compare Modules" on page 283). The external oscillator clock option is ideal for real-time clock (RTC) functionality, allowing the PCA to be clocked by a precision external oscillator while the internal oscillator drives the system clock. The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 26.1

**Important Note:** The PCA Module 5 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See Section 26.4 for details.

Figure 26.1. PCA Block Diagram

# C8051F55x/56x/57x

Figure 26.5. PCA Software Timer Mode Diagram

#### 26.3.3. High-Speed Output Mode

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode. If ECOMn is cleared, the associated pin will retain its state, and not toggle on the next match event.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

286