Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 18                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 18x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-WFQFN Exposed Pad                                           |

| Supplier Device Package    | 24-QFN (4x4)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f553-im |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 21.2.2. Magagag Object Interface Registers           | 211 |

|------------------------------------------------------|-----|

| 21.2.2. Message Object Interface Registers           |     |

| 21.2.3. Message Handler Registers                    |     |

| 21.2.4. CAN Register Assignment                      |     |

| 22. SMBus                                            |     |

| 22.1. Supporting Documents                           |     |

| 22.2. SMBus Configuration                            |     |

| 22.3. SMBus Operation                                |     |

| 22.3.1. Transmitter Vs. Receiver                     |     |

| 22.3.2. Arbitration                                  |     |

| 22.3.3. Clock Low Extension                          |     |

| 22.3.4. SCL Low Timeout                              |     |

| 22.3.5. SCL High (SMBus Free) Timeout                |     |

| 22.4. Using the SMBus                                |     |

| 22.4.1. SMBus Configuration Register                 |     |

| 22.4.2. SMB0CN Control Register                      |     |

| 22.4.3. Data Register                                |     |

| 22.5. SMBus Transfer Modes                           | -   |

| 22.5.1. Write Sequence (Master)                      |     |

| 22.5.2. Read Sequence (Master)                       |     |

| 22.5.3. Write Sequence (Slave)                       |     |

| 22.5.4. Read Sequence (Slave)                        |     |

| 22.6. SMBus Status Decoding                          |     |

| 23. UART0                                            |     |

| 23.1. Baud Rate Generator                            |     |

| 23.2. Data Format                                    |     |

| 23.3. Configuration and Operation                    |     |

| 23.3.1. Data Transmission                            |     |

| 23.3.2. Data Reception                               |     |

| 23.3.3. Multiprocessor Communications                |     |

| 24. Enhanced Serial Peripheral Interface (SPI0)      |     |

| 24.1. Signal Descriptions                            |     |

| 24.1.1. Master Out, Slave In (MOSI)                  |     |

| 24.1.2. Master In, Slave Out (MISO)                  |     |

| 24.1.3. Serial Clock (SCK)                           |     |

| 24.1.4. Slave Select (NSS)                           |     |

| 24.2. SPI0 Master Mode Operation                     |     |

| 24.3. SPI0 Slave Mode Operation                      |     |

| 24.4. SPI0 Interrupt Sources                         |     |

| 24.5. Serial Clock Phase and Polarity                |     |

| 24.6. SPI Special Function Registers                 |     |

| 25. Timers                                           |     |

| 25.1. Timer 0 and Timer 1                            |     |

| 25.1.1. Mode 0: 13-bit Counter/Timer                 |     |

| 25.1.2. Mode 1: 16-bit Counter/Timer                 |     |

| 25.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload | 262 |

|       | 25.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)             | 263 |

|-------|---------------------------------------------------------------------|-----|

| 25    | 5.2. Timer 2                                                        | 269 |

|       | 25.2.1. 16-bit Timer with Auto-Reload                               | 269 |

|       | 25.2.2. 8-bit Timers with Auto-Reload                               | 269 |

|       | 25.2.3. External Oscillator Capture Mode                            | 270 |

| 25    | 5.3. Timer 3                                                        |     |

|       | 25.3.1. 16-Bit Timer with Auto-Reload                               |     |

|       | 25.3.2. 8-Bit Timers with Auto-Reload                               | 275 |

|       | 25.3.3. External Oscillator Capture Mode                            |     |

| 26. P | rogrammable Counter Array.                                          |     |

| 26    | 6.1. PCA Counter/Timer                                              | 282 |

| 26    | 6.2. PCA0 Interrupt Sources                                         | 283 |

| 26    | 6.3. Capture/Compare Modules                                        | 283 |

|       | 26.3.1. Edge-triggered Capture Mode                                 | 284 |

|       | 26.3.2. Software Timer (Compare) Mode                               | 285 |

|       | 26.3.3. High-Speed Output Mode                                      | 286 |

|       | 26.3.4. Frequency Output Mode                                       | 287 |

|       | 26.3.5. 8-bit, 9-bit, 10-bit and 11-bit Pulse Width Modulator Modes | 288 |

|       | 26.3.6. 16-Bit Pulse Width Modulator Mode                           |     |

| 26    | 6.4. Watchdog Timer Mode                                            | 291 |

|       | 26.4.1. Watchdog Timer Operation                                    |     |

|       | 26.4.2. Watchdog Timer Usage                                        | 292 |

| 26    | 6.5. Register Descriptions for PCA0                                 | 294 |

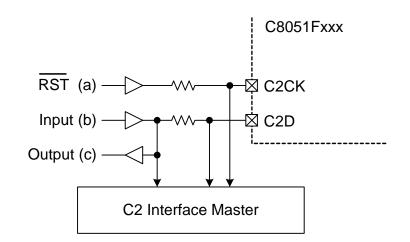

| 27. C | 2 Interface                                                         | 300 |

| 27    | 7.1. C2 Interface Registers                                         | 300 |

| 27    | 7.2. C2 Pin Sharing                                                 | 303 |

# C8051F55x/56x/57x

Figure 1.3. C8051F550-7 (24-pin) Block Diagram

Note that false rising edges and falling edges can be detected when the comparator is first powered on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed.

## SFR Definition 8.1. CPT0CN: Comparator0 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0HYP[1:0] |   | CP0HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/          | W |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

SFR Address = 0x9A; SFR Page = 0x00

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0–.                                                    |

|     |             | 1: Voltage on CP0+ > CP0                                                      |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3:2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

## **10.4.** Serial Number Special Function Registers (SFRs)

The C8051F55x/56x/57x devices include four SFRs, SN0 through SN3, that are pre-programmed during production with a unique, 32-bit serial number. The serial number provides a unique identification number for each device and can be read from the application firmware. If the serial number is not used in the application, these four registers can be used as general purpose SFRs.

## SFR Definition 10.7. SNn: Serial Number n

| Bit   | 7 6 5 4 3 2 1 0 |                                                                                                                                            |                     |             |            |           |           |  |  |  |  |

|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|------------|-----------|-----------|--|--|--|--|

| Nam   | e               | SERNUMn[7:0]                                                                                                                               |                     |             |            |           |           |  |  |  |  |

| Тур   | e               | R/W                                                                                                                                        |                     |             |            |           |           |  |  |  |  |

| Rese  | et              | Varies—Unique 32-bit value                                                                                                                 |                     |             |            |           |           |  |  |  |  |

| SFR / | Addresses: SN0  | = 0xF9; SI                                                                                                                                 | N1 = 0xFA;          | SN2 = 0xFB; | SN3 = 0xFC | ; SFR Pag | e = 0x0F; |  |  |  |  |

| Bit   | Name            |                                                                                                                                            |                     |             | Functior   | n         |           |  |  |  |  |

| 7:0   | SERNUMn[7:0     | ] Serial N                                                                                                                                 | Serial Number Bits. |             |            |           |           |  |  |  |  |

|       |                 | The four serial number registers form a 32-bit serial number, with SN3 as the most significant byte and SN0 as the least significant byte. |                     |             |            |           |           |  |  |  |  |

### C8051F55x/56x/57x.

### 11.2.1.1. General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 10.6). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

#### 11.2.1.2. Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 11.2.1.3. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

| Address   | 0(8)                   | 1(9)                | 2(A)               | 3(B)               | 4(C)               | 5(D)                   | 6(E)                   | 7(F)                   |

|-----------|------------------------|---------------------|--------------------|--------------------|--------------------|------------------------|------------------------|------------------------|

| ≪<br>F8 ( | SPI0CN                 | PCA0L<br>SN0        | PCA0H<br>SN1       | PCA0CPL0<br>SN2    | PCA0CPH0<br>SN3    | PCACPL4                | PCACPH4                | VDM0CN                 |

| F0 (      | ) B<br>F(All Pages)    | P0MAT<br>P0MDIN     | P0MASK<br>P1MDIN   | P1MAT<br>P2MDIN    | P1MASK<br>P3MDIN   |                        | EIP1<br>EIP1           | EIP2<br>EIP2           |

| E8 (      | ADC0CN                 | PCA0CPL1            | PCA0CPH1           | PCA0CPL2           | PCA0CPH2           | PCA0CPL3               | PCA0CPL3               | RSTSRC                 |

| E0 (      | ) ACC<br>- (All Pages) | XBR0                | XBR1               | CCH0CN             | IT01CF             |                        | EIE1<br>(All Pages)    | EIE2<br>(All Pages)    |

| D8 (      | =                      | PCA0MD<br>PCA0PWM   | PCA0CPM0           | PCA0CPM1           | PCA0CPM2           | PCA0CPM3               | PCA0CPM4               | PCA0CPM5               |

| D0 (<br>F | ) PSW<br>- (All Pages) | REF0CN              | LIN0DATA           | LIN0ADDR           | P0SKIP             | P1SKIP                 | P2SKIP                 | P3SKIP                 |

| C8 (      | TMR2CN                 | REG0CN<br>LIN0CF    | TMR2RLL            | TMR2RLH            | TMR2L              | TMR2H                  | PCA0CPL5               | PCA0CPH5               |

| C0 (      | ) SMB0CN               | SMB0CF              | SMB0DAT            | ADC0GTL            | ADC0GTH            | ADC0LTL                | ADC0LTH                | XBR2                   |

| B8 (      |                        |                     | ADC0TK             | ADC0MX             | ADC0CF             | ADC0L                  | ADC0H                  |                        |

| В0 (<br>Г | ) P3<br>F(All Pages)   | P2MAT               | P2MASK<br>EMI0CF   |                    |                    | P4<br>(All Pages)      | FLSCL<br>(All Pages)   | FLKEY<br>(All Pages)   |

| A8 (      | ) IE<br>F(All Pages)   | SMOD0               | EMI0CN<br>EMI0TC   | SBCON0             | SBRLL0             | SBRLH0                 | P3MAT<br>P3MDOUT       | P3MASK<br>P4MDOUT      |

| A0 (      | ) P2<br>F(All Pages)   | SPI0CFG<br>OSCICN   | SPI0CKR<br>OSCICRS | SPI0DAT            | POMDOUT            | P1MDOUT                | P2MDOUT                | SFRPAGE<br>(All Pages) |

| 98 (<br>F | ) SCON0                | SBUF0               | CPT0CN             | CPT0MD             | CPT0MX             | CPT1CN                 | CPT1MD<br>OSCIFIN      | CPT1MX<br>OSCXCN       |

| 90 (<br>F | ) P1<br>F(All Pages)   | TMR3CN              | TMR3RLL            | TMR3RLH            | TMR3L              | TMR3H                  |                        | CLKMUL                 |

| 88 (<br>F | TCON                   | TMOD<br>(All Pages) | TL0<br>(All Pages) | TL1<br>(All Pages) | TH0<br>(All Pages) | TH1<br>(All Pages)     | CKCON<br>(All Pages)   | PSCTL<br>CLKSEL        |

| 80 (<br>F | ) P0                   | SP<br>(All Pages)   | DPL<br>(All Pages) | DPH<br>(All Pages) | SFR0CN             | SFRNEXT<br>(All Pages) | SFRLAST<br>(All Pages) | PCON<br>(All Pages)    |

| L         | 0(8)<br>(bit address   | 1(9)                | 2(A)               | 3(B)               | 4(C)               | 5(D)                   | 6(E)                   | 7(F)                   |

## Table 12.1. Special Function Register (SFR) Memory Map for Pages 0x00 and 0x0F

## Table 13.1. Interrupt Summary

| Interrupt Source               | Interrupt<br>Vector | Priority<br>Order | Pending Flag                                                               | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|--------------------------------|---------------------|-------------------|----------------------------------------------------------------------------|------------------|----------------|--------------------|---------------------|

| Reset                          | 0x0000              | Тор               | None                                                                       | N/A              | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0<br>(INT0) | 0x0003              | 0                 | IE0 (TCON.1)                                                               | Y                | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow               | 0x000B              | 1                 | TF0 (TCON.5)                                                               | Y                | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1<br>(INT1) | 0x0013              | 2                 | IE1 (TCON.3)                                                               | Y                | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow               | 0x001B              | 3                 | TF1 (TCON.7)                                                               | Y                | Y              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                          | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y                | N              | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow               | 0x002B              | 5                 | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y                | N              | ET2 (IE.5)         | PT2 (IP.5)          |

| SPI0                           | 0x0033              | 6                 | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                | N              | ESPI0<br>(IE.6)    | PSPI0<br>(IP.6)     |

| SMB0                           | 0x003B              | 7                 | SI (SMB0CN.0)                                                              | Y                | Ν              | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| ADC0 Window Com-<br>pare       | 0x0043              | 8                 | ADOWINT<br>(ADC0CN.3)                                                      | Y                | N              | EWADC0<br>(EIE1.1) | PWADC0<br>(EIP1.1)  |

| ADC0 Conversion<br>Complete    | 0x004B              | 9                 | AD0INT (ADC0CN.5)                                                          | Y                | N              | EADC0<br>(EIE1.2)  | PADC0<br>(EIP1.2)   |

| Programmable<br>Counter Array  | 0x0053              | 10                | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)<br>COVF (PCA0PWM.6)                       | Y                | N              | EPCA0<br>(EIE1.3)  | PPCA0<br>(EIP1.3)   |

| Comparator0                    | 0x005B              | 11                | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | N                | N              | ECP0<br>(EIE1.4)   | PCP0<br>(EIP1.4)    |

| Comparator1                    | 0x0063              | 12                | CP1FIF (CPT1CN.4)<br>CP1RIF (CPT1CN.5)                                     | N                | N              | ECP1<br>(EIE1.5)   | PCP1<br>(EIP1.5)    |

| Timer 3 Overflow               | 0x006B              | 13                | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | N                | N              | ET3<br>(EIE1.6)    | PT3<br>(EIP1.6)     |

| LINO                           | 0x0073              | 14                | LINOINT (LINST.3)                                                          | N                | N*             | ELIN0<br>(EIE1.7)  | PLIN0<br>(EIP1.7)   |

| Voltage Regulator<br>Dropout   | 0x007B              | 15                | N/A                                                                        | N/A              | N/A            | EREG0<br>(EIE2.0)  | PREG0<br>(EIP2.0)   |

| CAN0                           | 0x0083              | 16                | CAN0INT<br>(CAN0CN.7)                                                      | N                | Y              | ECAN0<br>(EIE2.1)  | PCAN0<br>(EIP2.1)   |

| Port Match                     | 0x008B              | 17                | None                                                                       | N/A              | N/A            | EMAT<br>(EIE2.2)   | PMAT<br>(EIP2.2)    |

# SFR Definition 14.2. FLKEY: Flash Lock and Key

| Bit   | 7          | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|----|---|---|---|---|--|

| Name  | FLKEY[7:0] |   |   |    |   |   |   |   |  |

| Туре  |            |   |   | R/ | W |   |   |   |  |

| Reset | 0          | 0 | 0 | 0  | 0 | 0 | 0 | 0 |  |

#### SFR Address = 0xB7; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | FLKEY[7:0] | Flash Lock and Key Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | This register provides a lock and key function for Flash erasures and writes. Flash writes and erases are enabled by writing 0xA5 followed by 0xF1 to the FLKEY register. Flash writes and erases are automatically disabled after the next write or erase is complete. If any writes to FLKEY are performed incorrectly, or if a Flash write or erase operation is attempted while these operations are disabled, the Flash will be permanently locked from writes or erasures until the next device reset. If an application never writes to Flash, it can intentionally lock the Flash by writing a non-0xA5 value to FLKEY from software. |

|     |            | Read:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | When read, bits 1–0 indicate the current Flash lock state.<br>00: Flash is write/erase locked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |            | 01: The first key code has been written (0xA5).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |            | 10: Flash is unlocked (writes/erases allowed).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |            | 11: Flash writes/erases disabled until the next reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# SFR Definition 16.2. RSTSRC: Reset Source

| Bit   | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| Name  |   | FERROR | CORSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | 0 | Varies |

SFR Address = 0xEF; SFR Page = 0x00

| Bit   | Name       | Description                                                                                  | Write                                                                                                                                                                | Read                                                                                                                                           |

|-------|------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Unused     | Unused.                                                                                      | Don't care.                                                                                                                                                          | 0                                                                                                                                              |

| 6     | FERROR     | Flash Error Reset Flag.                                                                      | N/A                                                                                                                                                                  | Set to 1 if Flash<br>read/write/erase error<br>caused the last reset.                                                                          |

| 5     | CORSEF     | Comparator0 Reset Enable<br>and Flag.                                                        | Writing a 1 enables Com-<br>parator0 as a reset source<br>(active-low).                                                                                              | Set to 1 if Comparator0 caused the last reset.                                                                                                 |

| 4     | SWRSF      | Software Reset Force and Flag.                                                               | Writing a 1 forces a sys-<br>tem reset.                                                                                                                              | Set to 1 if last reset was<br>caused by a write to<br>SWRSF.                                                                                   |

| 3     | WDTRSF     | Watchdog Timer Reset Flag.                                                                   | N/A                                                                                                                                                                  | Set to 1 if Watchdog Timer<br>overflow caused the last<br>reset.                                                                               |

| 2     | MCDRSF     | Missing Clock Detector<br>Enable and Flag.                                                   | Writing a 1 enables the<br>Missing Clock Detector.<br>The MCD triggers a reset<br>if a missing clock condition<br>is detected.                                       | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                        |

| 1     | PORSF      | Power-On/V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the $V_{DD}$ monitor as a reset source.<br>Writing 1 to this bit before the $V_{DD}$ monitor is enabled and stabilized may cause a system reset. | Set to 1 anytime a power-<br>on or V <sub>DD</sub> monitor reset<br>occurs.<br>When set to 1 all other<br>RSTSRC flags are inde-<br>terminate. |

| 0     | PINRSF     | HW Pin Reset Flag.                                                                           | N/A                                                                                                                                                                  | Set to 1 if RST pin caused the last reset.                                                                                                     |

| Note: | Do not use | read-modify-write operations on this                                                         | s register                                                                                                                                                           | 1                                                                                                                                              |

# C8051F55x/56x/57x

# SFR Definition 18.6. OSCXCN: External Oscillator Control

| Bit   | 7      | 6           | 5         | 4  | 3 | 2         | 1   | 0 |  |

|-------|--------|-------------|-----------|----|---|-----------|-----|---|--|

| Name  | XTLVLD | ×           | OSCMD[2:0 | )] |   | XFCN[2:0] |     |   |  |

| Туре  | R      |             | R/W       |    |   |           | R/W |   |  |

| Reset | 0      | 0 0 0 0 0 0 |           |    |   | 0         |     |   |  |

## SFR Address = 0x9F; SFR Page = 0x0F

| Bit | Name        |          | -                                                                                            | Function                                  |                 |  |  |  |  |  |

|-----|-------------|----------|----------------------------------------------------------------------------------------------|-------------------------------------------|-----------------|--|--|--|--|--|

| 7   | XTLVLD      | Crystal  | Oscillator Valid Flag.                                                                       |                                           |                 |  |  |  |  |  |

|     |             | •        | nly when XOSCMD = 11                                                                         |                                           |                 |  |  |  |  |  |

|     |             | -        | Crystal Oscillator is unused or not yet stable.<br>Crystal Oscillator is running and stable. |                                           |                 |  |  |  |  |  |

|     |             | -        |                                                                                              |                                           |                 |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] |          | ternal Oscillator Mode Select.                                                               |                                           |                 |  |  |  |  |  |

|     |             |          | ternal Oscillator circuit of                                                                 |                                           |                 |  |  |  |  |  |

|     |             |          | ternal CMOS Clock Mod<br>ernal CMOS Clock Mod                                                |                                           |                 |  |  |  |  |  |

|     |             |          | Oscillator Mode.                                                                             |                                           |                 |  |  |  |  |  |

|     |             | 101: Ca  | pacitor Oscillator Mode.                                                                     |                                           |                 |  |  |  |  |  |

|     |             | -        | stal Oscillator Mode.                                                                        |                                           |                 |  |  |  |  |  |

|     |             | 111: Cry | 11: Crystal Oscillator Mode with divide by 2 stage.                                          |                                           |                 |  |  |  |  |  |

| 3   | Unused      | Read =   | Read = 0b; Write =0b                                                                         |                                           |                 |  |  |  |  |  |

| 2:0 | XFCN[2:0]   | Externa  | I Oscillator Frequency                                                                       | Control Bits.                             |                 |  |  |  |  |  |

|     |             |          | •                                                                                            | quency for Crystal or RC                  | mode.           |  |  |  |  |  |

|     |             | Set acc  | ording to the desired K F                                                                    | actor for C mode.                         |                 |  |  |  |  |  |

|     |             | XFCN     | Crystal Mode                                                                                 | RC Mode                                   | C Mode          |  |  |  |  |  |

|     |             | 000      | f ≤ 32 kHz                                                                                   | f ≤ 25 kHz                                | K Factor = 0.87 |  |  |  |  |  |

|     |             | 001      | 32 kHz < f ≤ 84 kHz                                                                          | 25 kHz < f ≤ 50 kHz                       | K Factor = 2.6  |  |  |  |  |  |

|     |             | 010      | 84 kHz < f ≤ 225 kHz                                                                         | 50 kHz < f ≤ 100 kHz                      | K Factor = 7.7  |  |  |  |  |  |

|     |             | 011      | 225 kHz < f ≤ 590 kHz                                                                        | 100 kHz < f ≤ 200 kHz                     | K Factor = 22   |  |  |  |  |  |

|     |             | 100      | 590 kHz < f ≤ 1.5 MHz                                                                        | 200 kHz < f ≤ 400 kHz                     | K Factor = 65   |  |  |  |  |  |

|     |             | 101      | $1.5 \text{ MHz} < f \le 4 \text{ MHz}$                                                      | 400 kHz < f ≤ 800 kHz                     | K Factor = 180  |  |  |  |  |  |

|     |             | 110      | $4 \text{ MHz} < f \le 10 \text{ MHz}$                                                       | 800 kHz < f ≤ 1.6 MHz                     | K Factor = 664  |  |  |  |  |  |

|     |             | 111      | $10 \text{ MHz} < f \le 30 \text{ MHz}$                                                      | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$ | K Factor = 1590 |  |  |  |  |  |

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VIO supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption and may be globally disabled by setting WEAKPUD to 1. The user should ensure that digital I/O are always internally or externally pulled or driven to a valid logic state to minimize power consumption. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

## 19.1.3. Interfacing Port I/O in a Multi-Voltage System

All Port I/O are capable of interfacing to digital logic operating at a supply voltage higher than VDD and less than 5.25 V. Connect the VIO pin to the voltage source of the interface logic.

## **19.2.** Assigning Port I/O Pins to Analog and Digital Functions

Port I/O pins P0.0–P3.7 can be assigned to various analog, digital, and external interrupt functions. P4.0 can be assigned to only digital functions. The Port pins assigned to analog functions should be configured for analog I/O, and Port pins assigned to digital or external interrupt functions should be configured for digital I/O.

#### **19.2.1. Assigning Port I/O Pins to Analog Functions**

Table 19.1 shows all available analog functions that require Port I/O assignments. **Port pins selected for these analog functions should have their corresponding bit in PnSKIP set to 1.** This reserves the pin for use by the analog function and does not allow it to be claimed by the Crossbar. Table 19.1 shows the potential mapping of Port I/O to each analog function.

| Analog Function                                       | Potentially Assignable<br>Port Pins | SFR(s) used for<br>Assignment |

|-------------------------------------------------------|-------------------------------------|-------------------------------|

| ADC Input                                             | P0.0–P3.7 <sup>1</sup>              | ADC0MX, PnSKIP                |

| Comparator0 or Compartor1 Input                       | P0.0–P2.7 <sup>1</sup>              | CPT0MX, CPT1MX,<br>PnSKIP     |

| Voltage Reference (VREF0) <sup>2</sup>                | P0.0                                | REF0CN, PnSKIP                |

| External Oscillator in Crystal Mode (XTAL1)           | P0.2                                | OSCXCN, PnSKIP                |

| External Oscillator in RC, C, or Crystal Mode (XTAL2) | P0.3                                | OSCXCN, PnSKIP                |

Table 19.1. Port I/O Assignment for Analog Functions

Notes:

**1.** P3.1–P3.7 are available on the 40-pin packages. P2.2-P3.0 are available 40-pin and 32-pin packages.

If VDD is selected as the voltage reference in the REF0CN register and the ADC is enabled in the ADC0CN register, the P0.0/VREF pin cannot operate as a general purpose I/O pin in open-drain mode. With the above settings, this pin can operate in push-pull output mode or as an analog input.

#### **19.2.2.** Assigning Port I/O Pins to Digital Functions

Any Port pins not assigned to analog functions may be assigned to digital functions or used as GPIO. Most digital functions rely on the Crossbar for pin assignment; however, some digital functions bypass the Crossbar in a manner similar to the analog functions listed above. **Port pins used by these digital func-tions and any Port pins selected for use as GPIO should have their corresponding bit in PnSKIP set to 1.** Table 19.2 shows all available digital functions and the potential mapping of Port I/O to each digital function.

# SFR Definition 19.19. P1SKIP: Port 1 Skip

| Bit   | 7 | 6           | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|-------|---|-------------|---|----|---|---|---|---|--|--|

| Name  |   | P1SKIP[7:0] |   |    |   |   |   |   |  |  |

| Туре  |   |             |   | R/ | W |   |   |   |  |  |

| Reset | 0 | 0           | 0 | 0  | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xD5; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                              |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1SKIP[7:0] | Port 1 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                     |

|     |             | These bits select Port 1 pins to be skipped by the Crossbar Decoder. Port pins<br>used for analog, special functions or GPIO should be skipped by the Crossbar.<br>0: Corresponding P1.n pin is not skipped by the Crossbar.<br>1: Corresponding P1.n pin is skipped by the Crossbar. |

## SFR Definition 19.20. P2: Port 2

| Bit   | 7 | 6       | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|---|---------|---|----|---|---|---|---|--|

| Name  |   | P2[7:0] |   |    |   |   |   |   |  |

| Туре  |   |         |   | R/ | W |   |   |   |  |

| Reset | 1 | 1       | 1 | 1  | 1 | 1 | 1 | 1 |  |

SFR Address = 0xA0; SFR Page = All Pages; Bit-Addressable

| Bit   | Name                                                         | Description                                                                                                                                  | Write                                                                         | Read                                                                    |  |  |  |  |  |  |

|-------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:0   | P2[7:0]                                                      | <b>Port 2Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P2.n Port pin is logic<br>LOW.<br>1: P2.n Port pin is logic<br>HIGH. |  |  |  |  |  |  |

| Note: | Note: P2.2-P2.7 are available on 40-pin and 32-pin packages. |                                                                                                                                              |                                                                               |                                                                         |  |  |  |  |  |  |

# 21. Controller Area Network (CAN0)

**Important Documentation Note**: The Bosch CAN Controller is integrated in the C8051F550/1/4/5, 'F560/ 1/4/5/8/9, and 'F572/3 devices. This section of the data sheet gives a description of the CAN controller as an overview and offers a description of how the Silicon Labs CIP-51 MCU interfaces with the on-chip Bosch CAN controller. In order to use the CAN controller, refer to Bosch's C\_CAN User's Manual as an accompanying manual to the Silicon Labs' data sheet.

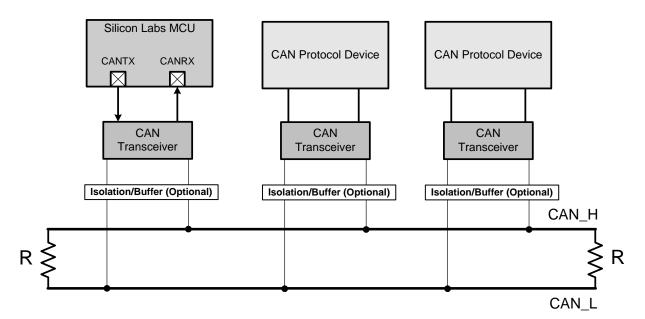

The C8051F550/1/4/5, 'F560/1/4/5/8/9, and 'F572/3 devices feature a Control Area Network (CAN) controller that enables serial communication using the CAN protocol. Silicon Labs CAN facilitates communication on a CAN network in accordance with the Bosch specification 2.0A (basic CAN) and 2.0B (full CAN). The CAN controller consists of a CAN Core, Message RAM (separate from the CIP-51 RAM), a message handler state machine, and control registers. Silicon Labs CAN is a protocol controller and does not provide physical layer drivers (i.e., transceivers). Figure 21.1 shows an example typical configuration on a CAN bus.

Silicon Labs' CAN operates at bit rates of up to 1 Mbit/second, though this can be limited by the physical layer chosen to transmit data on the CAN bus. The CAN processor has 32 Message Objects that can be configured to transmit or receive data. Incoming data, message objects and their identifier masks are stored in the CAN message RAM. All protocol functions for transmission of data and acceptance filtering is performed by the CAN controller and not by the CIP-51 MCU. In this way, minimal CPU bandwidth is needed to use CAN communication. The CIP-51 configures the CAN controller, accesses received data, and passes data for transmission via Special Function Registers (SFRs) in the CIP-51.

Figure 21.1. Typical CAN Bus Configuration

# SFR Definition 22.2. SMB0CN: SMBus Control

| Bit   | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0   |

|-------|--------|--------|-----|-----|-------|---------|-----|-----|

| Name  | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI  |

| Туре  | R      | R      | R/W | R/W | R     | R       | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0   |

### SFR Address = 0xC0; Bit-Addressable; SFR Page =0x00

| Bit | Name    | Description                                                                                                                                                                                                      | Read                                                                                                                       | Write                                                                                                                                                                                |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | SMBus Master/Slave<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a master.                                                                                                     | 0: SMBus operating in<br>slave mode.<br>1: SMBus operating in<br>master mode.                                              | N/A                                                                                                                                                                                  |

| 6   | TXMODE  | SMBus Transmit Mode<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a transmitter.                                                                                               | 0: SMBus in Receiver<br>Mode.<br>1: SMBus in Transmitter<br>Mode.                                                          | N/A                                                                                                                                                                                  |

| 5   | STA     | SMBus Start Flag.                                                                                                                                                                                                | 0: No Start or repeated<br>Start detected.<br>1: Start or repeated Start<br>detected.                                      | 0: No Start generated.<br>1: When Configured as a<br>Master, initiates a START<br>or repeated START.                                                                                 |

| 4   | STO     | SMBus Stop Flag.                                                                                                                                                                                                 | 0: No Stop condition<br>detected.<br>1: Stop condition detected<br>(if in Slave Mode) or pend-<br>ing (if in Master Mode). | 0: No STOP condition is<br>transmitted.<br>1: When configured as a<br>Master, causes a STOP<br>condition to be transmit-<br>ted after the next ACK<br>cycle.<br>Cleared by Hardware. |

| 3   | ACKRQ   | SMBus Acknowledge<br>Request.                                                                                                                                                                                    | 0: No Ack requested<br>1: ACK requested                                                                                    | N/A                                                                                                                                                                                  |

| 2   | ARBLOST | SMBus Arbitration Lost<br>Indicator.                                                                                                                                                                             | 0: No arbitration error.<br>1: Arbitration Lost                                                                            | N/A                                                                                                                                                                                  |

| 1   | ACK     | SMBus Acknowledge.                                                                                                                                                                                               | 0: NACK received.<br>1: ACK received.                                                                                      | 0: Send NACK<br>1: Send ACK                                                                                                                                                          |

| 0   | SI      | <b>SMBus Interrupt Flag.</b><br>This bit is set by hardware<br>under the conditions listed in<br>Table 15.3. SI must be cleared<br>by software. While SI is set,<br>SCL is held low and the<br>SMBus is stalled. | 0: No interrupt pending<br>1: Interrupt Pending                                                                            | <ul><li>0: Clear interrupt, and initiate next state machine event.</li><li>1: Force interrupt.</li></ul>                                                                             |

| Bit     | Set by Hardware When:                                                                                           | Cleared by Hardware When:                                                      |

|---------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| MASTER  | A START is generated.                                                                                           | <ul> <li>A STOP is generated.</li> </ul>                                       |

|         |                                                                                                                 | <ul> <li>Arbitration is lost.</li> </ul>                                       |

| TXMODE  | <ul> <li>START is generated.</li> </ul>                                                                         | <ul> <li>A START is detected.</li> </ul>                                       |

|         | <ul> <li>SMB0DAT is written before the start of an</li> </ul>                                                   | <ul> <li>Arbitration is lost.</li> </ul>                                       |

|         | SMBus frame.                                                                                                    | <ul> <li>SMB0DAT is not written before the start of an SMBus frame.</li> </ul> |

| STA     | <ul> <li>A START followed by an address byte is received.</li> </ul>                                            | <ul> <li>Must be cleared by software.</li> </ul>                               |

| STO     | <ul> <li>A STOP is detected while addressed as a<br/>slave.</li> </ul>                                          | A pending STOP is generated.                                                   |

|         | Arbitration is lost due to a detected STOP.                                                                     |                                                                                |

| ACKRQ   | <ul> <li>A byte has been received and an ACK<br/>response value is needed.</li> </ul>                           | After each ACK cycle.                                                          |

| ARBLOST | <ul> <li>A repeated START is detected as a<br/>MASTER when STA is low (unwanted<br/>repeated START).</li> </ul> | Each time SI is cleared.                                                       |

|         | <ul> <li>SCL is sensed low while attempting to<br/>generate a STOP or repeated START<br/>condition.</li> </ul>  |                                                                                |

|         | <ul> <li>SDA is sensed low while transmitting a 1<br/>(excluding ACK bits).</li> </ul>                          |                                                                                |

| ACK     | <ul> <li>The incoming ACK value is low<br/>(ACKNOWLEDGE).</li> </ul>                                            | <ul> <li>The incoming ACK value is high<br/>(NOT ACKNOWLEDGE).</li> </ul>      |

| SI      | <ul> <li>A START has been generated.</li> <li>Lost arbitration.</li> </ul>                                      | <ul> <li>Must be cleared by software.</li> </ul>                               |

|         | <ul> <li>A byte has been transmitted and an ACK/NACK received.</li> </ul>                                       |                                                                                |

|         | A byte has been received.                                                                                       |                                                                                |

|         | <ul> <li>A START or repeated START followed by a</li> </ul>                                                     |                                                                                |

|         | slave address + R/W has been received.                                                                          |                                                                                |

|         | A STOP has been received.                                                                                       |                                                                                |

## Table 22.3. Sources for Hardware Changes to SMB0CN

# C8051F55x/56x/57x

# SFR Definition 24.3. SPI0CKR: SPI0 Clock Rate

| Bit   | 7            | 6         5         4         3         2         1         0                                                                                                                                                                                                                                                                        |                                                           |             |           |         |   |   |  |  |  |  |

|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------|-----------|---------|---|---|--|--|--|--|

| Nam   | e            | -                                                                                                                                                                                                                                                                                                                                    | _                                                         | SCF         | R[7:0]    |         |   | _ |  |  |  |  |

| Туре  | ;            |                                                                                                                                                                                                                                                                                                                                      | R/W                                                       |             |           |         |   |   |  |  |  |  |

| Rese  | t O          | 0                                                                                                                                                                                                                                                                                                                                    | 0                                                         | 0           | 0         | 0       | 0 | 0 |  |  |  |  |

| SFR A | ddress = 0xA | 2; SFR Page                                                                                                                                                                                                                                                                                                                          | e = 0x00                                                  | ·           |           |         |   |   |  |  |  |  |

| Bit   | Name         |                                                                                                                                                                                                                                                                                                                                      |                                                           |             | Functior  | 1       |   |   |  |  |  |  |

| 7:0   | SCR[7:0]     | SPI0 Cloc                                                                                                                                                                                                                                                                                                                            | k Rate.                                                   |             |           |         |   |   |  |  |  |  |

|       |              | These bits determine the frequency of the SCK output when the SPI0 module is configured for master mode operation. The SCK clock frequency is a divided version of the system clock, and is given in the following equation, where SYSCLK is the system clock frequency and SPI0CKR is the 8-bit value held in the SPI0CKR register. |                                                           |             |           |         |   |   |  |  |  |  |

|       |              | <sup>f</sup> sck ⁼                                                                                                                                                                                                                                                                                                                   | $f_{SCK} = \frac{SYSCLK}{2 \text{ x (SPI0CKR[7:0] + 1)}}$ |             |           |         |   |   |  |  |  |  |

|       |              | for 0 <= S                                                                                                                                                                                                                                                                                                                           | for 0 <= SPI0CKR <= 255                                   |             |           |         |   |   |  |  |  |  |

|       |              | Example:                                                                                                                                                                                                                                                                                                                             | If SYSCLK                                                 | = 2 MHz and | I SPI0CKR | = 0x04, |   |   |  |  |  |  |

$$f_{SCK} = \frac{2000000}{2 \text{ x } (4+1)}$$

# SFR Definition 24.4. SPI0DAT: SPI0 Data

| Bit   | 7 | 6            | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|-------|---|--------------|---|----|---|---|---|---|--|--|

| Name  |   | SPI0DAT[7:0] |   |    |   |   |   |   |  |  |

| Туре  |   |              |   | R/ | W |   |   |   |  |  |

| Reset | 0 | 0            | 0 | 0  | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xA3; SFR Page = 0x00

| Bi  | Name         | Function                                                                                                                                                                                                                                     |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SPI0DAT[7:0] | SPI0 Transmit and Receive Data.                                                                                                                                                                                                              |

|     |              | The SPI0DAT register is used to transmit and receive SPI0 data. Writing data to SPI0DAT places the data into the transmit buffer and initiates a transfer when in Master Mode. A read of SPI0DAT returns the contents of the receive buffer. |

# SFR Definition 25.14. TMR3RLL: Timer 3 Reload Register Low Byte

| Bit                                 | 7    | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

|-------------------------------------|------|---------------|---|---|---|---|---|---|--|--|--|--|--|

| Nam                                 | e    | TMR3RLL[7:0]  |   |   |   |   |   |   |  |  |  |  |  |

| Туре                                | )    | R/W           |   |   |   |   |   |   |  |  |  |  |  |

| Rese                                | et 0 | 0             | 0 | 0 | 0 | 0 | 0 |   |  |  |  |  |  |

| SFR Address = 0x92; SFR Page = 0x00 |      |               |   |   |   |   |   |   |  |  |  |  |  |

| Bit                                 | Name | Name Function |   |   |   |   |   |   |  |  |  |  |  |

| ы   | Name         | Function                                                    |

|-----|--------------|-------------------------------------------------------------|

| 7:0 | TMR3RLL[7:0] | Timer 3 Reload Register Low Byte.                           |

|     |              | TMR3RLL holds the low byte of the reload value for Timer 3. |

## SFR Definition 25.15. TMR3RLH: Timer 3 Reload Register High Byte

| Bit                                 | 7             | 6                                                            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

|-------------------------------------|---------------|--------------------------------------------------------------|---|---|---|---|---|---|--|--|--|--|--|

| Nam                                 | e             | TMR3RLH[7:0]                                                 |   |   |   |   |   |   |  |  |  |  |  |

| Туре                                | 9             | R/W                                                          |   |   |   |   |   |   |  |  |  |  |  |

| Rese                                | et 0          | 0                                                            | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |  |  |

| SFR Address = 0x93; SFR Page = 0x00 |               |                                                              |   |   |   |   |   |   |  |  |  |  |  |

| Bit                                 | Name Function |                                                              |   |   |   |   |   |   |  |  |  |  |  |

| 7:0                                 | TMR3RLH[7:0   | MR3RLH[7:0] Timer 3 Reload Register High Byte.               |   |   |   |   |   |   |  |  |  |  |  |

|                                     |               | TMR3RLH holds the high byte of the reload value for Timer 3. |   |   |   |   |   |   |  |  |  |  |  |

| Operational Mode                                                                                                                                                                                                |   |   | PCA0CPMn |   |   |   |   |   |   |   | PCA0PWM |     |     |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----------|---|---|---|---|---|---|---|---------|-----|-----|--|--|

| Bit Number                                                                                                                                                                                                      | 7 | 6 | 5        | 4 | 3 | 2 | 1 | 0 | 7 | 6 | 5       | 4–2 | 1–0 |  |  |

| Capture triggered by positive edge on CEXn                                                                                                                                                                      | Х | Х | 1        | 0 | 0 | 0 | 0 | А | 0 | Х | В       | XXX | XX  |  |  |

| Capture triggered by negative edge on CEXn                                                                                                                                                                      | Х | Х | 0        | 1 | 0 | 0 | 0 | А | 0 | Х | В       | XXX | XX  |  |  |

| Capture triggered by any transition on CEXn                                                                                                                                                                     |   | Х | 1        | 1 | 0 | 0 | 0 | А | 0 | Х | В       | XXX | XX  |  |  |

| Software Timer                                                                                                                                                                                                  | Х | С | 0        | 0 | 1 | 0 | 0 | А | 0 | Х | В       | XXX | XX  |  |  |

| High Speed Output                                                                                                                                                                                               | Х | С | 0        | 0 | 1 | 1 | 0 | А | 0 | Х | В       | XXX | XX  |  |  |

| Frequency Output                                                                                                                                                                                                | Х | С | 0        | 0 | 0 | 1 | 1 | А | 0 | Х | В       | XXX | XX  |  |  |

| 8-Bit Pulse Width Modulator (7)                                                                                                                                                                                 | 0 | С | 0        | 0 | Е | 0 | 1 | А | 0 | Х | В       | XXX | 00  |  |  |

| 9-Bit Pulse Width Modulator (7)                                                                                                                                                                                 | 0 | С | 0        | 0 | Е | 0 | 1 | А | D | Х | В       | XXX | 01  |  |  |

| 10-Bit Pulse Width Modulator (7)                                                                                                                                                                                | 0 | С | 0        | 0 | Е | 0 | 1 | А | D | Х | В       | XXX | 10  |  |  |

| 11-Bit Pulse Width Modulator (7)                                                                                                                                                                                | 0 | С | 0        | 0 | Е | 0 | 1 | А | D | Х | В       | XXX | 11  |  |  |

| 16-Bit Pulse Width Modulator                                                                                                                                                                                    | 1 | С | 0        | 0 | Е | 0 | 1 | А | 0 | Х | В       | XXX | XX  |  |  |

| <ul> <li>Notes:</li> <li>1. X = Don't Care (no functional difference for individual module if 1 or 0).</li> <li>2. A = Enable interrupts for this module (PCA interrupt triggered on CCFn set to 1).</li> </ul> |   |   |          |   |   |   |   |   |   |   |         |     |     |  |  |

### Table 26.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare Modules

3. B = Enable 8th, 9th, 10th or 11th bit overflow interrupt (Depends on setting of CLSEL[1:0]).

4. C = When set to 0, the digital comparator is off. For high speed and frequency output modes, the associated pin will not toggle. In any of the PWM modes, this generates a 0% duty cycle (output = 0).

- 5. D = Selects whether the Capture/Compare register (0) or the Auto-Reload register (1) for the associated channel is accessed via addresses PCA0CPHn and PCA0CPLn.

- 6. E = When set, a match event will cause the CCFn flag for the associated channel to be set.

7. All modules set to 8, 9, 10 or 11-bit PWM mode use the same cycle length setting.

## 26.3.1. Edge-triggered Capture Mode