Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

|                            |                                                                  |

| Product Status             | Active                                                           |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 50MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), CANbus, LINbus, SPI, UART/USART |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                       |

| Number of I/O              | 18                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 2.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                     |

| Data Converters            | A/D 18x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 24-WFQFN Exposed Pad                                             |

| Supplier Device Package    | 24-QFN (4x4)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f554-im   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 22.3. Sources for Hardware Changes to SMB0CN               | 227 |

|------------------------------------------------------------------|-----|

| Table 22.4. SMBus Status Decoding                                |     |

| <u> </u>                                                         |     |

| Table 23.1. Baud Rate Generator Settings for Standard Baud Rates | 236 |

| Table 24.1. SPI Slave Timing Parameters                          | 258 |

| Table 26.1. PCA Timebase Input Options                           | 282 |

| Table 26.2. PCA0CPM and PCA0PWM Bit Settings for                 |     |

| PCA Capture/Compare Modules                                      | 284 |

| Table 26.3. Watchdog Timer Timeout Intervals1                    | 293 |

#### 6.3.2. Setting the Gain Value

The three programmable gain registers are accessed indirectly using the ADC0H and ADC0L registers when the GAINEN bit (ADC0CF.0) bit is set. ADC0H acts as the address register, and ADC0L is the data register. The programmable gain registers can only be written to and cannot be read. See Gain Register Definition 6.1, Gain Register Definition 6.2, and Gain Register Definition 6.3 for more information.

The gain is programmed using the following steps:

- 1. Set the GAINEN bit (ADC0CF.0)

- 2. Load the ADC0H with the ADC0GNH, ADC0GNL, or ADC0GNA address.

- 3. Load ADC0L with the desired value for the selected gain register.

- 4. Reset the GAINEN bit (ADC0CF.0)

#### Notes:

- 1. An ADC conversion should not be performed while the GAINEN bit is set.

- 2. Even with gain enabled, the maximum input voltage must be less than V<sub>REGIN</sub> and the maximum voltage of the signal after gain must be less than or equal to V<sub>REF</sub>.

In code, changing the value to 0.44 gain from the previous example looks like:

```

// in 'C':

ADC0CF = 0x01:

// GAINEN = 1

ADC0H = 0x04:

// Load the ADC0GNH address

ADC0L = 0x6C:

// Load the upper byte of 0x6CA to ADC0GNH

ADC0H = 0x07:

// Load the ADC0GNL address

// Load the lower nibble of 0x6CA to ADC0GNL

ADC0L = 0xA0;

ADC0H = 0x08:

// Load the ADC0GNA address

ADC0L = 0x01:

// Set the GAINADD bit

ADC0CF \&= ~0x01;

// GAINEN = 0

; in assembly

ORL ADC0CF,#01H

: GAINEN = 1

: Load the ADC0GNH address

MOV ADC0H,#04H

MOV ADC0L.#06CH

: Load the upper byte of 0x6CA to ADC0GNH

: Load the ADC0GNL address

MOV ADC0H,#07H

MOV ADC0L,#0A0H

: Load the lower nibble of 0x6CA to ADC0GNL

MOV ADC0H,#08H

: Load the ADC0GNA address

MOV ADC0L,#01H

: Set the GAINADD bit

ANL ADCOCF,#0FEH

: GAINEN = 0

```

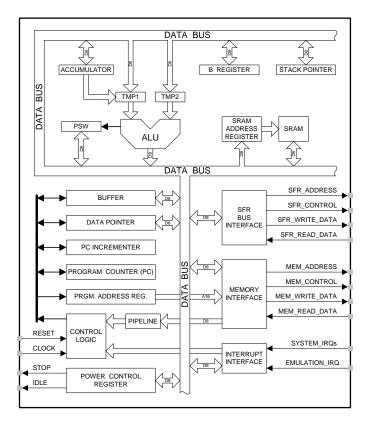

#### 10. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51™ instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware (see description in Section 27), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 10.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 50 MIPS Peak Throughput with 50 MHz Clock

- 0 to 50 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

#### 10.1. Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

Figure 10.1. CIP-51 Block Diagram

With the CIP-51's maximum system clock at 50 MHz, it has a peak throughput of 50 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

#### **Programming and Debugging Support**

In-system programming of the Flash program memory and communication with on-chip debug support logic is accomplished via the Silicon Labs 2-Wire Development Interface (C2).

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive, requiring no RAM, Stack, timers, or other on-chip resources. C2 details can be found in Section "27. C2 Interface" on page 300.

The CIP-51 is supported by development tools from Silicon Labs and third party vendors. Silicon Labs provides an integrated development environment (IDE) including editor, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via the C2 interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

**Table 12.3. Special Function Registers**

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Description                              | Page |

|----------|---------|------------------------------------------|------|

| ACC      | 0xE0    | Accumulator                              | 89   |

| ADC0CF   | 0xBC    | ADC0 Configuration                       | 58   |

| ADC0CN   | 0xE8    | ADC0 Control                             | 60   |

| ADC0GTH  | 0xC4    | ADC0 Greater-Than Compare High           | 62   |

| ADC0GTL  | 0xC3    | ADC0 Greater-Than Compare Low            | 62   |

| ADC0H    | 0xBE    | ADC0 High                                | 59   |

| ADC0L    | 0xBD    | ADC0 Low                                 | 59   |

| ADC0LTH  | 0xC6    | ADC0 Less-Than Compare Word High         | 63   |

| ADC0LTL  | 0xC5    | ADC0 Less-Than Compare Word Low          | 63   |

| ADC0MX   | 0xBB    | ADC0 Mux Configuration                   | 66   |

| ADC0TK   | 0xBA    | ADC0 Tracking Mode Select                | 61   |

| В        | 0xF0    | B Register                               | 89   |

| CCH0CN   | 0xE3    | Cache Control                            | 134  |

| CKCON    | 0x8E    | Clock Control                            | 260  |

| CLKMUL   | 0x97    | Clock Multiplier                         | 163  |

| CLKSEL   | 0x8F    | Clock Select                             | 158  |

| CPT0CN   | 0x9A    | Comparator0 Control                      | 72   |

| CPT0MD   | 0x9B    | Comparator0 Mode Selection               | 73   |

| CPT0MX   | 0x9C    | Comparator0 MUX Selection                | 77   |

| CPT1CN   | 0x9D    | Comparator1 Control                      | 72   |

| CPT1MD   | 0x9E    | Comparator1 Mode Selection               | 73   |

| CPT1MX   | 0x9F    | Comparator1 MUX Selection                | 77   |

| DPH      | 0x83    | Data Pointer High                        | 88   |

| DPL      | 0x82    | Data Pointer Low                         | 88   |

| EIE1     | 0xE6    | Extended Interrupt Enable 1              | 118  |

| EIE2     | 0xE7    | Extended Interrupt Enable 2              | 118  |

| EIP1     | 0xF6    | Extended Interrupt Priority 1            | 119  |

| EIP2     | 0xF7    | Extended Interrupt Priority 2            | 120  |

| EMI0CF   | 0xB2    | External Memory Interface Configuration  | 148  |

| EMI0CN   | 0xAA    | External Memory Interface Control        | 147  |

| EMI0TC   | 0xAA    | External Memory Interface Timing Control | 152  |

| FLKEY    | 0xB7    | Flash Lock and Key                       | 132  |

| FLSCL    | 0xB6    | Flash Scale                              | 133  |

| IE       | 0xA8    | Interrupt Enable                         | 116  |

| IP       | 0xB8    | Interrupt Priority                       | 117  |

#### 14.4. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of V<sub>DD</sub>, system clock frequency, or temperature. This accidental execution of Flash modifying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

The following guidelines are recommended for any system which contains routines which write or erase Flash from code.

#### 14.4.1. V<sub>DD</sub> Maintenance and the V<sub>DD</sub> monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- 2. Make certain that the minimum VREGIN rise time specification of 1 ms is met. If the system cannot meet this rise time specification, then add an external V<sub>DD</sub> brownout circuit to the RST<u>pin</u> of the device that holds the device in reset until  $V_{DD}$  reaches the minimum threshold and re-asserts RST if  $V_{DD}$  drops below the minimum threshold.

- 3. Enable the on-chip V<sub>DD</sub> monitor in the high setting and enable the V<sub>DD</sub> monitor as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For C-based systems, this will involve modifying the startup code added by the C compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the V<sub>DD</sub> monitor in the high setting and enabling the V<sub>DD</sub> monitor as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware", available from the Silicon Laboratories web site.

- 4. As an added precaution, explicitly enable the  $V_{DD}$  monitor in the high setting and enable the  $V_{DD}$ monitor as a reset source inside the functions that write and erase Flash memory. The V<sub>DD</sub> monitor enable instructions should be placed just after the instruction to set PSWE to a 1, but before the Flash write or erase operation instruction.

- Note: The output of the internal voltage regulator is calibrated by the MCU immediately after any reset event. The output of the un-calibrated internal regulator could be below the high threshold setting of the V<sub>DD</sub> Monitor. If this is the case and the V<sub>DD</sub> Monitor is set to the high threshold setting and if the MCU receives a non-power on reset (POR), the MCU will remain in reset until a POR occurs (i.e., V<sub>DD</sub> Monitor will keep the device in reset). A POR will force the V<sub>DD</sub> Monitor to the low threshold setting which is guaranteed to be below the un-calibrated output of the internal regulator. The device will then exit reset and resume normal operation. It is for this reason Silicon Labs strongly recommends that the V<sub>DD</sub> Monitor is always left in the low threshold setting (i.e. default value upon POR). When programming the Flash in-system, the V<sub>DD</sub> Monitor must be set to the high threshold setting. For the highest system reliability, the time the V<sub>DD</sub> Monitor is set to the high threshold setting should be minimized (e.g., setting the V<sub>DD</sub> Monitor to the high threshold setting just before the Flash write operation and then changing it back to the low threshold setting immediately after the Flash write operation).

- 5. Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct. "RSTSRC |= 0x02" is incorrect.

- 6. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a 1. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

### SFR Definition 15.1. PCON: Power Control

| Bit   | 7 | 6 | 5 | 4    | 3    | 2 | 1 | 0 |

|-------|---|---|---|------|------|---|---|---|

| Name  |   |   |   | STOP | IDLE |   |   |   |

| Туре  |   |   |   | R/W  | R/W  |   |   |   |

| Reset | 0 | 0 | 0 | 0    | 0    | 0 | 0 | 0 |

SFR Address = 0x87; SFR Page = All Pages

| Bit | Name    | Function                                                                                                                                                                                                                                                        |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | GF[5:0] | General Purpose Flags 5–0.  These are general purpose flags for use under software control.                                                                                                                                                                     |

| 1   | STOP    | Stop Mode Select. Setting this bit will place the CIP-51 in Stop mode. This bit will always be read as 0.  1: CPU goes into Stop mode (internal oscillator stopped).                                                                                            |

| 0   | IDLE    | IDLE: Idle Mode Select.  Setting this bit will place the CIP-51 in Idle mode. This bit will always be read as 0.  1: CPU goes into Idle mode. (Shuts off clock to CPU, but clock to Timers, Interrupts, Serial Ports, and Analog Peripherals are still active.) |

#### 17.5.3. Split Mode with Bank Select

When EMIOCF[3:2] are set to 10, the XRAM memory map is split into two areas, on-chip space and offchip space.

- Effective addresses below the internal XRAM size boundary will access on-chip XRAM space.

- Effective addresses above the internal XRAM size boundary will access off-chip space.

- 8-bit MOVX operations use the contents of EMI0CN to determine whether the memory access is onchip or off-chip. The upper 8-bits of the Address Bus A[15:8] are determined by EMIOCN, and the lower 8-bits of the Address Bus A[7:0] are determined by R0 or R1. All 16-bits of the Address Bus A[15:0] are driven in "Bank Select" mode.

- 16-bit MOVX operations use the contents of DPTR to determine whether the memory access is on-chip or off-chip, and the full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

#### 17.5.4. External Only

When EMIOCF[3:2] are set to 11, all MOVX operations are directed to off-chip space. On-chip XRAM is not visible to the CPU. This mode is useful for accessing off-chip memory located between 0x0000 and the internal XRAM size boundary.

- 8-bit MOVX operations ignore the contents of EMI0CN. The upper Address bits A[15:8] are not driven (identical behavior to an off-chip access in "Split Mode without Bank Select" described above). This allows the user to manipulate the upper address bits at will by setting the Port state directly. The lower 8-bits of the effective address A[7:0] are determined by the contents of R0 or R1.

- 16-bit MOVX operations use the contents of DPTR to determine the effective address A[15:0]. The full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

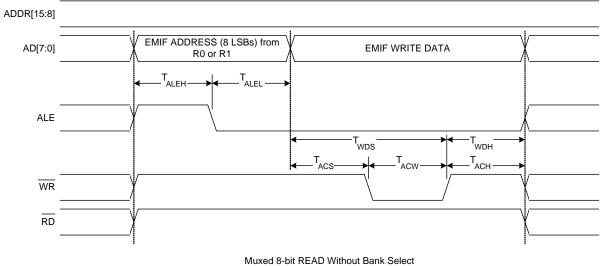

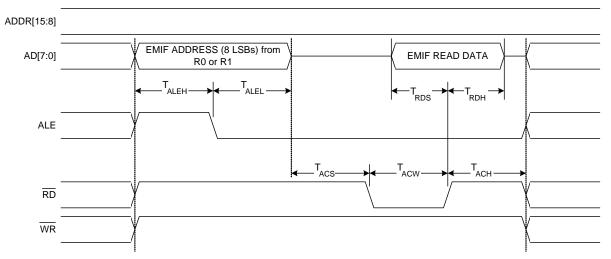

#### 17.6. Timing

The timing parameters of the External Memory Interface can be configured to enable connection to devices having different setup and hold time requirements. The Address Setup time, Address Hold time, RD and WR strobe widths, and in multiplexed mode, the width of the ALE pulse are all programmable in units of SYSCLK periods through EMIOTC, shown in SFR Definition 17.3, and EMIOCF[1:0].

The timing for an off-chip MOVX instruction can be calculated by adding 4 SYSCLK cycles to the timing parameters defined by the EMIOTC register. Assuming non-multiplexed operation, the minimum execution time for an off-chip XRAM operation is 5 SYSCLK cycles (1 SYSCLK for RD or WR pulse + 4 SYSCLKs). For multiplexed operations, the Address Latch Enable signal will require a minimum of 2 additional SYSCLK cycles. Therefore, the minimum execution time for an off-chip XRAM operation in multiplexed mode is 7 SYSCLK cycles (2 for /ALE + 1 for  $\overline{RD}$  or  $\overline{WR}$  + 4). The programmable setup and hold times default to the maximum delay settings after a reset. Table 17.2 lists the ac parameters for the External Memory Interface, and Figure 17.3 through Figure 17.5 show the timing diagrams for the different External Memory Interface modes and MOVX operations.

#### 17.6.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011

Muxed 8-bit WRITE Without Bank Select

Figure 17.4. Multiplexed 8-bit MOVX without Bank Select Timing

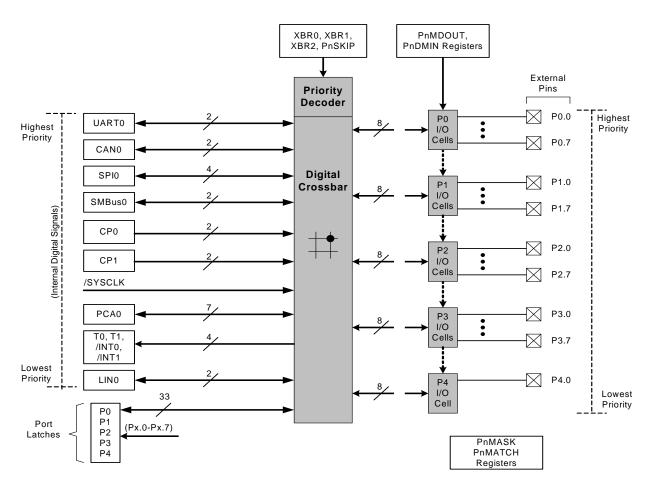

### 19. Port Input/Output

Digital and analog resources are available through 33 (C8051F568-9 and 'F570-5), 25 (C8051F550-7) or 18 (C8051F550-7) I/O pins. Port pins P0.0-P4.0 on the C8051F568-9 and 'F570-5, port pins P0.0-P3.0 on the C8051F560-7, and port pins P0.0-P2.1 on the C8051F550-7 can be defined as general-purpose I/O (GPIO), assigned to one of the internal digital resources, or assigned to an analog function as shown in Figure 19.3. Port pin P4.0 on the C8051F568-9 and 'F570-5 can be used as GPIO and is shared with the C2 Interface Data signal (C2D). Similarly, port pin P3.0 is shared with C2D on the C8051F560-7 and port pin P2.1 on the C8051F550-7. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 19.3 and Figure 19.4). The registers XBR0, XBR1, XBR2 are defined in SFR Definition 19.1 and SFR Definition 19.2 and are used to select internal digital functions.

The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n=0,1). Complete Electrical Specifications for Port I/O are given in Table 5.3 on page 40.

Figure 19.1. Port I/O Functional Block Diagram

## SFR Definition 19.1. XBR0: Port I/O Crossbar Register 0

| Bit   | 7     | 6    | 5     | 4    | 3     | 2     | 1     | 0     |

|-------|-------|------|-------|------|-------|-------|-------|-------|

| Name  | CP1AE | CP1E | CP0AE | CP0E | SMB0E | SPI0E | CAN0E | URT0E |

| Туре  | R/W   | R/W  | R/W   | R/W  | R/W   | R/W   | R/W   | R/W   |

| Reset | 0     | 0    | 0     | 0    | 0     | 0     | 0     | 0     |

SFR Address = 0xE1; SFR Page = 0x0F

| Bit | Name  | Function                                                                                   |

|-----|-------|--------------------------------------------------------------------------------------------|

| 7   | CP1AE | Comparator1 Asynchronous Output Enable.                                                    |

|     |       | O: Asynchronous CP1 unavailable at Port pin.     Synchronous CP1 routed to Port pin.       |

| 6   | CP1E  | Comparator1 Output Enable.                                                                 |

| 0   | OFIL  | 0: CP1 unavailable at Port pin.                                                            |

|     |       | 1: CP1 routed to Port pin.                                                                 |

| 5   | CP0AE | Comparator0 Asynchronous Output Enable.                                                    |

|     |       | 0: Asynchronous CP0 unavailable at Port pin.                                               |

|     |       | 1: Asynchronous CP0 routed to Port pin.                                                    |

| 4   | CP0E  | Comparator0 Output Enable.                                                                 |

|     |       | 0: CP0 unavailable at Port pin.                                                            |

|     |       | 1: CP0 routed to Port pin.                                                                 |

| 3   | SMB0E | SMBus I/O Enable.                                                                          |

|     |       | 0: SMBus I/O unavailable at Port pins.                                                     |

|     |       | 1: SMBus I/O routed to Port pins.                                                          |

| 2   | SPI0E | SPI I/O Enable.                                                                            |

|     |       | 0: SPI I/O unavailable at Port pins.                                                       |

|     |       | 1: SPI I/O routed to Port pins. Note that the SPI can be assigned either 3 or 4 GPIO pins. |

| 1   | CAN0E | CAN I/O Output Enable.                                                                     |

|     |       | 0: CAN I/O unavailable at Port pins.                                                       |

|     |       | 1: CAN_TX, CAN_RX routed to Port pins P0.6 and P0.7.                                       |

| 0   | URT0E | UART I/O Output Enable.                                                                    |

|     |       | 0: UART I/O unavailable at Port pin.                                                       |

|     |       | 1: UART TX0, RX0 routed to Port pins P0.4 and P0.5.                                        |

The application should perform the following steps when an interrupt is requested.

- 1. Check the DONE bit (LINOST.0) and the ERROR bit (LINOST.2).

- 2. If performing a master receive operation and the transfer was successful, read the received data from the data buffer.

- 3. If the transfer was not successful, check the error register to determine the kind of error. Further error handling has to be done by the application.

- 4. Set the RSTINT (LIN0CTRL.3) and RSTERR bits (LIN0CTRL.2) to reset the interrupt request and the error flags.

#### 20.4. LIN Slave Mode Operation

When the device is configured for slave mode operation, it must wait for a command from a master node. Access from the firmware to the data buffer and ID registers of the LIN controller is only possible when a data request is pending (DTREQ bit (LIN0ST.4) is 1) and also when the LIN bus is not active (ACTIVE bit (LIN0ST.7) is set to 0).

The LIN controller in slave mode detects the header of the message frame sent by the LIN master. If slave synchronization is enabled (autobaud), the slave synchronizes its internal bit time to the master bit time.

The LIN controller configured for slave mode will generated an interrupt in one of three situations:

- 1. After the reception of the IDENTIFIER FIELD

- 2. When an error is detected

- 3. When the message transfer is completed.

The application should perform the following steps when an interrupt is detected:

- 1. Check the status of the DTREQ bit (LINOST.4). This bit is set when the IDENTIFIER FIELD has been received.

- 2. If DTREQ (LINOST.4) is set, read the identifier from LINOID and process it. If DTREQ (LINOST.4) is not set, continue to step 7.

- 3. Set the TXRX bit (LINOCTRL.5) to 1 if the current frame is a transmit operation for the slave and set to 0 if the current frame is a receive operation for the slave.

- 4. Load the data length into LIN0SIZE.

- 5. For a slave transmit operation, load the data to transmit into the data buffer.

- 6. Set the DTACK bit (LIN0CTRL.4). Continue to step 10.

- 7. If DTREQ (LINOST.4) is not set, check the DONE bit (LINOST.0). The transmission was successful if the DONE bit is set.

- 8. If the transmission was successful and the current frame was a receive operation for the slave, load the received data bytes from the data buffer.

- 9. If the transmission was not successful, check LIN0ERR to determine the nature of the error. Further error handling has to be done by the application.

- 10. Set the RSTINT (LINOCTRL.3) and RSTERR bits (LINOCTRL.2) to reset the interrupt request and the error flags.

In addition to these steps, the application should be aware of the following:

- 1. If the current frame is a transmit operation for the slave, steps 1 through 5 must be completed during the IN-FRAME RESPONSE SPACE. If it is not completed in time, a timeout will be detected by the master.

- 2. If the current frame is a receive operation for the slave, steps 1 through 5 have to be finished until the reception of the first byte after the IDENTIFIER FIELD. Otherwise, the internal receive buffer of the LIN controller will be overwritten and a timeout error will be detected in the LIN controller.

### LIN Register Definition 20.4. LIN0DTn: LIN0 Data Byte n

| Bit   | 7   | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|------------|---|---|---|---|---|---|

| Name  |     | DATAn[7:0] |   |   |   |   |   |   |

| Туре  | R/W |            |   |   |   |   |   |   |

| Reset | 0   | 0          | 0 | 0 | 0 | 0 | 0 | 0 |

Indirect Address: LIN0DT1 = 0x00, LIN0DT2 = 0x01, LIN0DT3 = 0x02, LIN0DT4 = 0x03, LIN0DT5 = 0x04, LIN0DT6 = 0x05, LIN0DT7 = 0x06, LIN0DT8 = 0x07

| Bit | Name       | Function                                                                   |

|-----|------------|----------------------------------------------------------------------------|

| 7:0 | DATAn[7:0] | LIN Data Byte n.                                                           |

|     |            | Serial Data Byte that is received or transmitted across the LIN interface. |

### 21.2. CAN Registers

CAN registers are classified as follows:

- 1. CAN Controller Protocol Registers: CAN control, interrupt, error control, bus status, test modes.

- Message Object Interface Registers: Used to configure 32 Message Objects, send and receive data

to and from Message Objects. The CIP-51 MCU accesses the CAN message RAM via the Message

Object Interface Registers. Upon writing a message object number to an IF1 or IF2 Command Request

Register, the contents of the associated Interface Registers (IF1 or IF2) will be transferred to or from the

message object in CAN RAM.

- 3. **Message Handler Registers**: These read only registers are used to provide information to the CIP-51 MCU about the message objects (MSGVLD flags, Transmission Request Pending, New Data Flags) and Interrupts Pending (which Message Objects have caused an interrupt or status interrupt condition).

For the registers other than CANOCFG, refer to the Bosch CAN User's Guide for information on the function and use of the CAN Control Protocol Registers.

#### 21.2.1. CAN Controller Protocol Registers

The CAN Control Protocol Registers are used to configure the CAN controller, process interrupts, monitor bus status, and place the controller in test modes.

The registers are: CAN Control Register (CAN0CN), CAN Clock Configuration (CAN0CFG), CAN Status Register (CAN0STA), CAN Test Register (CAN0TST), Error Counter Register, Bit Timing Register, and the Baud Rate Prescaler (BRP) Extension Register.

#### 21.2.2. Message Object Interface Registers

There are two sets of Message Object Interface Registers used to configure the 32 Message Objects that transmit and receive data to and from the CAN bus. Message objects can be configured for transmit or receive, and are assigned arbitration message identifiers for acceptance filtering by all CAN nodes.

Message Objects are stored in Message RAM, and are accessed and configured using the Message Object Interface Registers.

#### 21.2.3. Message Handler Registers

The Message Handler Registers are read only registers. The message handler registers provide interrupt, error, transmit/receive requests, and new data information.

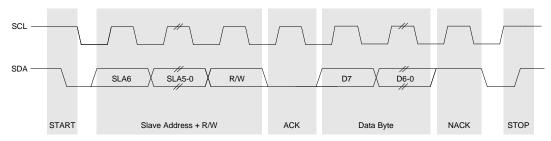

All transactions are initiated by a master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the slave address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time waiting for an ACK from the slave at the end of each byte. For READ operations, the slave transmits the data waiting for an ACK from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 22.3 illustrates a typical SMBus transaction.

Figure 22.3. SMBus Transaction

#### 22.3.1. Transmitter Vs. Receiver

On the SMBus communications interface, a device is the "transmitter" when it is sending an address or data byte to another device on the bus. A device is a "receiver" when an address or data byte is being sent to it from another device on the bus. The transmitter controls the SDA line during the address or data byte. After each byte of address or data information is sent by the transmitter, the receiver sends an ACK or NACK bit during the ACK phase of the transfer, during which time the receiver controls the SDA line.

#### 22.3.2. Arbitration

A master may start a transfer only if the bus is free. The bus is free after a STOP condition or after the SCL and SDA lines remain high for a specified time (see Section "22.3.5. SCL High (SMBus Free) Timeout" on page 221). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one master to give up the bus. The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW. Since the bus is open-drain, the bus will be pulled LOW. The master attempting the HIGH will detect a LOW SDA and lose the arbitration. The winning master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer if addressed. This arbitration scheme is non-destructive: one device always wins, and no data is lost.

#### 22.3.3. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I<sup>2</sup>C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 22.3.4. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

When the SMBTOE bit in SMBOCF is set, Timer 3 is used to detect SCL low timeouts. Timer 3 is forced to reload when SCL is high, and allowed to count when SCL is low. With Timer 3 enabled and configured to

### SFR Definition 25.8. TMR2CN: Timer 2 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1 | 0      |

|-------|------|------|--------|--------|---------|-----|---|--------|

| Name  | TF2H | TF2L | TF2LEN | TF2CEN | T2SPLIT | TR2 |   | T2XCLK |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R | R/W    |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0 | 0      |

SFR Address = 0xC8; Bit-Addressable; SFR Page = 0x00

| SFR F | FR Address = 0xC8; Bit-Addressable; SFR Page = 0x00 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|-------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit   | Name                                                | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 7     | TF2H                                                | Timer 2 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|       |                                                     | Set by hardware when the Timer 2 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 2 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                           |  |  |  |  |  |  |

| 6     | TF2L                                                | Timer 2 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|       |                                                     | Set by hardware when the Timer 2 low byte overflows from 0xFF to 0x00. TF2L will be set when the low byte overflows regardless of the Timer 2 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 5     | TF2LEN                                              | Timer 2 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|       |                                                     | When set to 1, this bit enables Timer 2 Low Byte interrupts. If Timer 2 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 2 overflows.                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 4     | TF2CEN                                              | Timer 2 Capture Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|       |                                                     | 0: Timer 2 Capture Mode is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|       |                                                     | 1: Timer 2 Capture Mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 3     | T2SPLIT                                             | Timer 2 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|       |                                                     | When this bit is set, Timer 2 operates as two 8-bit timers with auto-reload.  0: Timer 2 operates in 16-bit auto-reload mode.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|       |                                                     | 1: Timer 2 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 2     | TR2                                                 | Timer 2 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|       |                                                     | Timer 2 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables TMR2H only; TMR2L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 1     | Unused                                              | Read = 0b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 0     | T2XCLK                                              | Timer 2 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|       |                                                     | This bit selects the external clock source for Timer 2. If Timer 2 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 2 Clock Select bits (T2MH and T2ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.  0: Timer 2 clock is the system clock divided by 12.  1: Timer 2 clock is the external clock divided by 8 (synchronized with SYSCLK). |  |  |  |  |  |  |

## SFR Definition 25.16. TMR3L: Timer 3 Low Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|--|--|

| Name  | TMR3L[7:0] |   |   |   |   |   |   |   |  |  |  |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |  |  |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |  |

SFR Address = 0x94; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                      |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3L[7:0] | Timer 3 Low Byte.                                                                                                                             |

|     |            | In 16-bit mode, the TMR3L register contains the low byte of the 16-bit Timer 3. In 8-bit mode, TMR3L contains the 8-bit low byte timer value. |

## SFR Definition 25.17. TMR3H Timer 3 High Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|--|--|

| Name  | TMR3H[7:0] |   |   |   |   |   |   |   |  |  |  |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |  |  |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |  |

SFR Address = 0x95; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                        |  |  |  |  |  |  |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:0 | TMR3H[7:0] | Timer 3 High Byte.                                                                                                                              |  |  |  |  |  |  |

|     |            | In 16-bit mode, the TMR3H register contains the high byte of the 16-bit Timer 3. In 8-bit mode, TMR3H contains the 8-bit high byte timer value. |  |  |  |  |  |  |

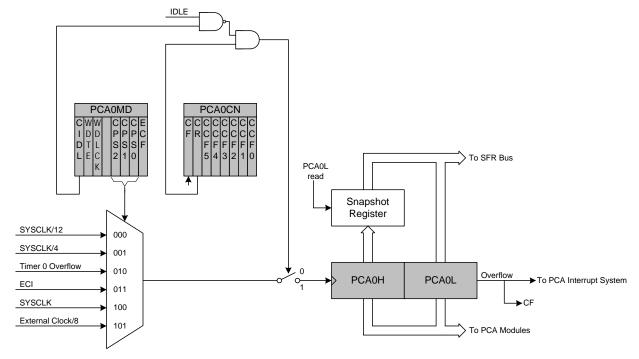

#### 26.1. PCA Counter/Timer

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte (MSB) of the 16-bit counter/timer and PCA0L is the low byte (LSB). Reading PCA0L automatically latches the value of PCA0H into a "snapshot" register; the following PCA0H read accesses this "snapshot" register. Reading the PCA0L Register first guarantees an accurate reading of the entire 16-bit PCA0 counter. Reading PCA0H or PCA0L does not disturb the counter operation. The CPS[2:0] bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 26.1.

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the CPU is in Idle mode.

**Table 26.1. PCA Timebase Input Options**

| CPS2      | CPS1          | CPS0        | Timebase                                                               |  |  |  |  |  |  |

|-----------|---------------|-------------|------------------------------------------------------------------------|--|--|--|--|--|--|

| 0         | 0             | 0           | System clock divided by 12.                                            |  |  |  |  |  |  |

| 0         | 0             | 1           | System clock divided by 4.                                             |  |  |  |  |  |  |

| 0         | 1             | 0           | Timer 0 overflow.                                                      |  |  |  |  |  |  |

| 0         | 1             | 1           | High-to-low transitions on ECI (max rate = system clock divided by 4). |  |  |  |  |  |  |

| 1         | 0             | 0           | System clock.                                                          |  |  |  |  |  |  |

| 1         | 0             | 1           | External oscillator source divided by 8.*                              |  |  |  |  |  |  |

| 1         | 1             | Х           | Reserved.                                                              |  |  |  |  |  |  |

| *Note: Ex | ternal oscill | ator source | divided by 8 is synchronized with the system clock.                    |  |  |  |  |  |  |

Figure 26.2. PCA Counter/Timer Block Diagram

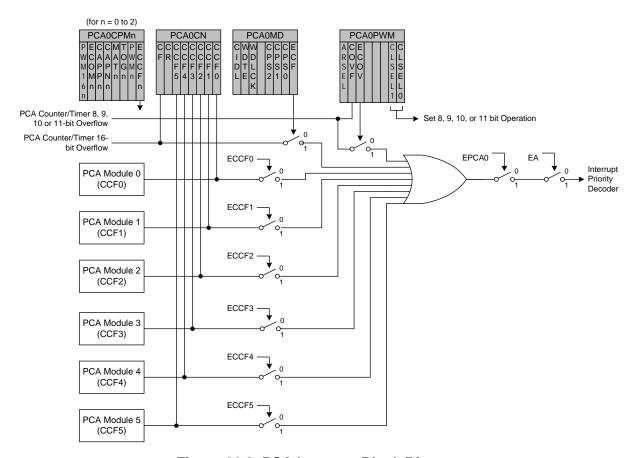

#### 26.2. PCA0 Interrupt Sources

Figure 26.3 shows a diagram of the PCA interrupt tree. There are five independent event flags that can be used to generate a PCA0 interrupt. They are as follows: the main PCA counter overflow flag (CF), which is set upon a 16-bit overflow of the PCA0 counter, an intermediate overflow flag (COVF), which can be set on an overflow from the 8th, 9th, 10th, or 11th bit of the PCA0 counter, and the individual flags for each PCA channel (CCF0, CCF1, CCF2, CCF3, CCF4, and CCF5), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA0 interrupt, using the corresponding interrupt enable flag (ECF for CF, ECOV for COVF, and ECCFn for each CCFn). PCA0 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1.

Figure 26.3. PCA Interrupt Block Diagram

#### 26.3. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: Edge-triggered Capture, Software Timer, High Speed Output, Frequency Output, 8 to 11-Bit Pulse Width Modulator, or 16-Bit Pulse Width Modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation. Table 26.2 summarizes the bit settings in the PCA0CPMn and PCA0PWM registers used to select the PCA capture/compare module's operating mode. All modules set to use 8, 9, 10, or 11-bit PWM mode must use the same cycle length (8-11 bits). Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt.

### Table 26.2. PCA0CPM and PCA0PWM Bit Settings for **PCA Capture/Compare Modules**

| Operational Mode                            |   |   | PCA0CPMn |   |   |   |   |   |   |   | PCA0PWM |     |     |  |  |

|---------------------------------------------|---|---|----------|---|---|---|---|---|---|---|---------|-----|-----|--|--|

| Bit Number                                  | 7 | 6 | 5        | 4 | 3 | 2 | 1 | 0 | 7 | 6 | 5       | 4–2 | 1–0 |  |  |

| Capture triggered by positive edge on CEXn  | X | Χ | 1        | 0 | 0 | 0 | 0 | Α | 0 | Χ | В       | XXX | XX  |  |  |

| Capture triggered by negative edge on CEXn  | Х | Χ | 0        | 1 | 0 | 0 | 0 | Α | 0 | Χ | В       | XXX | XX  |  |  |

| Capture triggered by any transition on CEXn | Х | Χ | 1        | 1 | 0 | 0 | 0 | Α | 0 | Χ | В       | XXX | XX  |  |  |

| Software Timer                              |   | С | 0        | 0 | 1 | 0 | 0 | Α | 0 | Χ | В       | XXX | XX  |  |  |

| High Speed Output                           | Х | С | 0        | 0 | 1 | 1 | 0 | Α | 0 | Χ | В       | XXX | XX  |  |  |

| Frequency Output                            | Х | С | 0        | 0 | 0 | 1 | 1 | Α | 0 | Χ | В       | XXX | XX  |  |  |

| 8-Bit Pulse Width Modulator (7)             | 0 | С | 0        | 0 | Е | 0 | 1 | Α | 0 | Χ | В       | XXX | 00  |  |  |

| 9-Bit Pulse Width Modulator (7)             | 0 | С | 0        | 0 | Е | 0 | 1 | Α | D | Χ | В       | XXX | 01  |  |  |

| 10-Bit Pulse Width Modulator (7)            | 0 | С | 0        | 0 | Е | 0 | 1 | Α | D | Χ | В       | XXX | 10  |  |  |

| 11-Bit Pulse Width Modulator (7)            | 0 | С | 0        | 0 | Е | 0 | 1 | Α | D | Χ | В       | XXX | 11  |  |  |

| 16-Bit Pulse Width Modulator                |   | С | 0        | 0 | Ε | 0 | 1 | Α | 0 | Χ | В       | XXX | XX  |  |  |

- **1.** X = Don't Care (no functional difference for individual module if 1 or 0).

- **2.** A = Enable interrupts for this module (PCA interrupt triggered on CCFn set to 1).

- 3. B = Enable 8th, 9th, 10th or 11th bit overflow interrupt (Depends on setting of CLSEL[1:0]).

- 4. C = When set to 0, the digital comparator is off. For high speed and frequency output modes, the associated pin will not toggle. In any of the PWM modes, this generates a 0% duty cycle (output = 0).

- 5. D = Selects whether the Capture/Compare register (0) or the Auto-Reload register (1) for the associated channel is accessed via addresses PCA0CPHn and PCA0CPLn.

- 6. E = When set, a match event will cause the CCFn flag for the associated channel to be set.

- 7. All modules set to 8, 9, 10 or 11-bit PWM mode use the same cycle length setting.

#### 26.3.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.