Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 50MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), CANbus, LINbus, SPI, UART/USART |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                       |

| Number of I/O              | 25                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 2.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                     |

| Data Converters            | A/D 25x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-VFQFN Exposed Pad                                             |

| Supplier Device Package    | 32-QFN (5x5)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f560-imr  |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 12.2. Interrupts and SFR Paging                                     | 95  |

|---------------------------------------------------------------------|-----|

| 12.3. SFR Page Stack Example                                        | 97  |

| 13. Interrupts                                                      | 112 |

| 13.1. MCU Interrupt Sources and Vectors                             | 112 |

| 13.1.1. Interrupt Priorities                                        | 113 |

| 13.1.2. Interrupt Latency                                           | 113 |

| 13.2. Interrupt Register Descriptions                               | 115 |

| 13.3. External Interrupts INTO and INT1                             |     |

| 14. Flash Memory                                                    |     |

| 14.1. Programming The Flash Memory                                  | 124 |

| 14.1.1. Flash Lock and Key Functions                                | 124 |

| 14.1.2. Flash Erase Procedure                                       |     |

| 14.1.3. Flash Write Procedure                                       | 125 |

| 14.1.4. Flash Write Optimization                                    | 126 |

| 14.2. Non-volatile Data Storage                                     |     |

| 14.3. Security Options                                              |     |

| 14.4. Flash Write and Erase Guidelines                              | 129 |

| 14.4.1. V <sub>DD</sub> Maintenance and the V <sub>DD</sub> monitor |     |

| 14.4.2. PSWE Maintenance                                            | 130 |

| 14.4.3. System Clock                                                |     |

| 15. Power Management Modes                                          |     |

| 15.1. Idle Mode                                                     | 135 |

| 15.2. Stop Mode                                                     | 136 |

| 15.3. Suspend Mode                                                  |     |

| 16. Reset Sources                                                   |     |

| 16.1. Power-On Reset                                                | 139 |

| 16.2. Power-Fail Reset/VDD Monitor                                  |     |

| 16.3. External Reset                                                | 141 |

| 16.4. Missing Clock Detector Reset                                  |     |

| 16.5. Comparator0 Reset                                             |     |

| 16.6. PCA Watchdog Timer Reset                                      |     |

| 16.7. Flash Error Reset                                             |     |

| 16.8. Software Reset                                                | 142 |

| 17. External Data Memory Interface and On-Chip XRAM                 |     |

| 17.1. Accessing XRAM                                                |     |

| 17.1.1. 16-Bit MOVX Example                                         |     |

| 17.1.2. 8-Bit MOVX Example                                          |     |

| 17.2. Configuring the External Memory Interface                     |     |

| 17.3. Port Configuration                                            |     |

| 17.4. Multiplexed Mode                                              |     |

| 17.5. Memory Mode Selection                                         |     |

| 17.5.1. Internal XRAM Only                                          |     |

| 17.5.2. Split Mode without Bank Select                              |     |

| 17.5.3. Split Mode with Bank Select                                 |     |

| 17.5.4. External Only                                               |     |

|       | 25.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)             | 263 |

|-------|---------------------------------------------------------------------|-----|

| 25    | 5.2. Timer 2                                                        | 269 |

|       | 25.2.1. 16-bit Timer with Auto-Reload                               | 269 |

|       | 25.2.2. 8-bit Timers with Auto-Reload                               | 269 |

|       | 25.2.3. External Oscillator Capture Mode                            | 270 |

| 25    | 5.3. Timer 3                                                        |     |

|       | 25.3.1. 16-Bit Timer with Auto-Reload                               |     |

|       | 25.3.2. 8-Bit Timers with Auto-Reload                               | 275 |

|       | 25.3.3. External Oscillator Capture Mode                            |     |

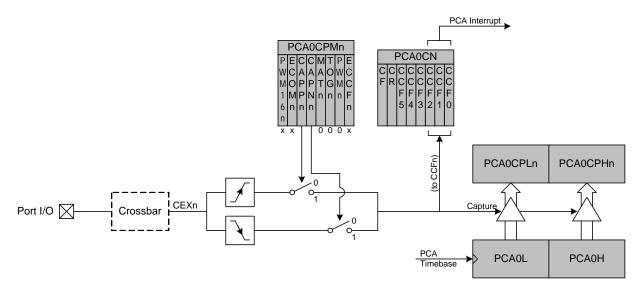

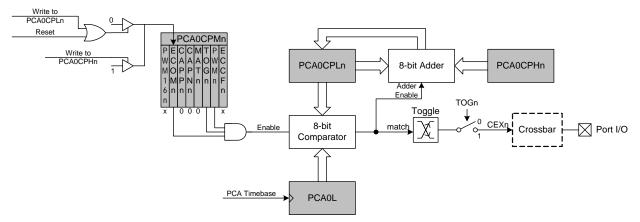

| 26. P | rogrammable Counter Array.                                          |     |

| 26    | 6.1. PCA Counter/Timer                                              | 282 |

| 26    | 6.2. PCA0 Interrupt Sources                                         | 283 |

| 26    | 6.3. Capture/Compare Modules                                        | 283 |

|       | 26.3.1. Edge-triggered Capture Mode                                 | 284 |

|       | 26.3.2. Software Timer (Compare) Mode                               | 285 |

|       | 26.3.3. High-Speed Output Mode                                      | 286 |

|       | 26.3.4. Frequency Output Mode                                       | 287 |

|       | 26.3.5. 8-bit, 9-bit, 10-bit and 11-bit Pulse Width Modulator Modes | 288 |

|       | 26.3.6. 16-Bit Pulse Width Modulator Mode                           |     |

| 26    | 6.4. Watchdog Timer Mode                                            | 291 |

|       | 26.4.1. Watchdog Timer Operation                                    |     |

|       | 26.4.2. Watchdog Timer Usage                                        | 292 |

| 26    | 6.5. Register Descriptions for PCA0                                 | 294 |

| 27. C | 2 Interface                                                         | 300 |

| 27    | 7.1. C2 Interface Registers                                         | 300 |

| 27    | 7.2. C2 Pin Sharing                                                 | 303 |

# 3. Pin Definitions

| Name   | Pin                | Pin                | Pin                | Туре          | Description                                                                 |

|--------|--------------------|--------------------|--------------------|---------------|-----------------------------------------------------------------------------|

|        | 40-pin<br>packages | 32-pin<br>packages | 24-pin<br>packages |               |                                                                             |

| VDD    | 4                  | 4                  | 3                  |               | Digital Supply Voltage. Must be connected.                                  |

| GND    | 6                  | 6                  | 4                  |               | Digital Ground. Must be connected.                                          |

| VDDA   | 5                  | 5                  | —                  |               | Analog Supply Voltage. Must be connected.                                   |

| GNDA   | 7                  | 7                  | 5                  |               | Analog Ground. Must be connected.                                           |

| VREGIN | 3                  | 3                  | 2                  |               | Voltage Regulator Input                                                     |

| VIO    | 2                  | 2                  | 1                  |               | Port I/O Supply Voltage. Must be connected.                                 |

| RST/   | 10                 | 10                 | 8                  | D I/O         | Device Reset. Open-drain output of internal POR or V <sub>DD</sub> Monitor. |

| C2CK   |                    |                    |                    | D I/O         | Clock signal for the C2 Debug Interface.                                    |

| P4.0/  | 9                  | _                  | —                  | D I/O or A In | Port 4.0. See SFR Definition 19.28.                                         |

| C2D    |                    |                    |                    | D I/O         | Bi-directional data signal for the C2 Debug Interface.                      |

| P3.0/  |                    | 9                  | _                  | D I/O or A In | Port 3.0. See SFR Definition 19.24.                                         |

| C2D    |                    |                    |                    | D I/O         | Bi-directional data signal for the C2 Debug Interface.                      |

| P2.1/  |                    | _                  | 7                  | D I/O or A In | Port 2.1. See SFR Definition 19.20.                                         |

| C2D    |                    |                    |                    | D I/O         | Bi-directional data signal for the C2 Debug Interface.                      |

| P0.0   | 8                  | 8                  | 6                  | D I/O or A In | Port 0.0. See SFR Definition 19.12.                                         |

| P0.1   | 1                  | 1                  | 24                 | D I/O or A In | Port 0.1                                                                    |

| P0.2   | 40                 | 32                 | 23                 | D I/O or A In | Port 0.2                                                                    |

| P0.3   | 39                 | 31                 | 22                 | D I/O or A In | Port 0.3                                                                    |

| P0.4   | 38                 | 30                 | 21                 | D I/O or A In | Port 0.4                                                                    |

| P0.5   | 37                 | 29                 | 20                 | D I/O or A In | Port 0.5                                                                    |

| P0.6   | 36                 | 28                 | 19                 | D I/O or A In | Port 0.6                                                                    |

| P0.7   | 35                 | 27                 | 18                 | D I/O or A In | Port 0.7                                                                    |

Table 3.1. Pin Definitions for the C8051F55x/56x/57x

### Table 10.1. CIP-51 Instruction Set Summary

| Mnemonic              | Description                              | Bytes | Clock<br>Cycles |

|-----------------------|------------------------------------------|-------|-----------------|

| Arithmetic Operations |                                          | I     |                 |

| ADD A, Rn             | Add register to A                        | 1     | 1               |

| ADD A, direct         | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri            | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data          | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn            | Add register to A with carry             | 1     | 1               |

| ADDC A, direct        | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri           | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data         | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn            | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct        | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri           | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data         | Subtract immediate from A with borrow    | 2     | 2               |

| INC A                 | Increment A                              | 1     | 1               |

| INC Rn                | Increment register                       | 1     | 1               |

| INC direct            | Increment direct byte                    | 2     | 2               |

| INC @Ri               | Increment indirect RAM                   | 1     | 2               |

| DEC A                 | Decrement A                              | 1     | 1               |

| DEC Rn                | Decrement register                       | 1     | 1               |

| DEC direct            | Decrement direct byte                    | 2     | 2               |

| DEC @Ri               | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR              | Increment Data Pointer                   | 1     | 1               |

| MUL AB                | Multiply A and B                         | 1     | 4               |

| DIV AB                | Divide A by B                            | 1     | 8               |

| DA A                  | Decimal adjust A                         | 1     | 1               |

| Logical Operations    |                                          | I     |                 |

| ANL A, Rn             | AND Register to A                        | 1     | 1               |

| ANL A, direct         | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri            | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data          | AND immediate to A                       | 2     | 2               |

| ANL direct, A         | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data     | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn             | OR Register to A                         | 1     | 1               |

| ORL A, direct         | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri            | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data          | OR immediate to A                        | 2     | 2               |

| ORL direct, A         | OR A to direct byte 2                    |       | 2               |

| ORL direct, #data     | OR immediate to direct byte 3            |       | 3               |

| XRL A, Rn             | Exclusive-OR Register to A 1             |       | 1               |

| XRL A, direct         | Exclusive-OR direct byte to A            | 2     | 2               |

| XRL A, @Ri            | Exclusive-OR indirect RAM to A           | 1     | 2               |

# SFR Definition 12.3. SFRNEXT: SFR Next

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-----------------|---|---|---|---|---|---|

| Name  |   | SFRNEXT[7:0]    |   |   |   |   |   |   |

| Туре  |   | R/W             |   |   |   |   |   |   |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

### SFR Address = 0x85; SFR Page = All Pages

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SFRNEXT[7:0] | SFR Page Bits.                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |              | This is the value that will go to the SFR Page register upon a return from inter-<br>rupt.                                                                                                                                                                                                                                                                                                                          |

|     |              | Write: Sets the SFR Page contained in the second byte of the SFR Stack. This will cause the SFRPAGE SFR to have this SFR page value upon a return from interrupt.                                                                                                                                                                                                                                                   |

|     |              | Read: Returns the value of the SFR page contained in the second byte of the SFR stack.                                                                                                                                                                                                                                                                                                                              |

|     |              | SFR page context is retained upon interrupts/return from interrupts in a 3 byte<br>SFR Page Stack: SFRPAGE is the first entry, SFRNEXT is the second, and<br>SFRLAST is the third entry. The SFR stack bytes may be used alter the context<br>in the SFR Page Stack, and will not cause the stack to "push" or "pop". Only<br>interrupts and return from interrupts cause pushes and pops of the SFR Page<br>Stack. |

|    |                      | •                   |                    | • •                |                    |                        |                        |                        |

|----|----------------------|---------------------|--------------------|--------------------|--------------------|------------------------|------------------------|------------------------|

|    | 0(8)                 | 1(9)                | 2(A)               | 3(B)               | 4(C)               | 5(D)                   | 6(E)                   | 7(F)                   |

| F8 |                      |                     | CAN0IF2DA2L        | CAN0IF2DA2H        | CAN0IF2DB1L        | CAN0IF2DB1H            | CAN0IF2DB2L            | CAN0IF2DB2H            |

| F0 | B<br>(All Pages)     |                     | CAN0IF2A2L         | CAN0IF2A2H         |                    |                        | CAN0IF2DA1L            | CAN0IF2DA1H            |

| E8 |                      | •                   | CAN0IF2M1L         | CAN0IF2M1H         | CAN0IF2M2L         | CAN0IF2M2H             | CAN0IF2A1L             | CAN0IF2A1H             |

| E0 | ACC<br>(All Pages)   |                     | CAN0IF2CML         | CAN0IF2CMH         |                    |                        | EIE1<br>(All Pages)    | EIE2<br>(All Pages)    |

| D8 |                      | •                   | CAN0IF1DB1L        | CAN0IF1DB1H        | CAN0IF1DB2L        | CAN0IF1DB2H            | CAN0IF2CRL             | CAN0IF2CRH             |

| D0 | PSW<br>(All Pages)   |                     | CAN0IF1MCL         | CAN0IF1MCH         | CAN0IF1DA1L        | CAN0IF1DA1H            | CAN0IF1DA2L            | CAN0IF1DA2H            |

| C8 |                      | •                   | CAN0IF1A1L         | CAN0IF1A1H         | CAN0IF1A2L         | CAN0IF1A2H             | CAN0IF2MCL             | CAN0IF2MCH             |

| C0 | CAN0CN               |                     | CAN0IF1CML         | CAN0IF1CMH         | CAN0IF1M1L         | CAN0IF1M1H             | CAN0IF1M2L             | CAN0IF1M2H             |

| B8 | IP<br>(All Pages)    |                     | CAN0MV1L           | CAN0MV1H           | CAN0MV2L           | CAN0MV2H               | CAN0IF1CRL             | CAN0IF1CRH             |

| B0 | P3<br>(All Pages)    |                     | CAN0IP2L           | CAN0IP2H           |                    | P4<br>(All Pages)      | FLSCL<br>(All Pages)   | FLKEY<br>(All Pages)   |

| A8 | IE<br>(All Pages)    |                     | CAN0ND1L           | CAN0ND1H           | CAN0ND2L           | CAN0ND2H               | CAN0IP1L               | CAN0IP1H               |

| A0 | P2<br>(All Pages)    | CAN0BRPE            | CAN0TR1L           | CAN0TR1H           | CAN0TR2L           | CAN0TR2H               |                        | SFRPAGE<br>(All Pages) |

| 98 | SCON0<br>(All Pages) |                     | CAN0BTL            | CAN0BTH            | CAN0IIDL           | CANOIIDH               | CAN0TST                |                        |

| 90 | P1<br>(All Pages)    |                     | CAN0CFG            |                    | CAN0STAT           |                        | CAN0ERRL               | CAN0ERRH               |

| 88 | TCON<br>(All Pages)  | TMOD<br>(All Pages) | TL0<br>(All Pages) | TL1<br>(All Pages) | TH0<br>(All Pages) | TH1<br>(All Pages)     | CKCON<br>(All Pages)   |                        |

| 80 | P0                   | SP<br>(All Pages)   | DPL<br>(All Pages) | DPH<br>(All Pages) |                    | SFRNEXT<br>(All Pages) | SFRLAST<br>(All Pages) | PCON<br>(All Pages)    |

|    | 0(8)<br>(bit addres  | 1(9)                | 2(A)               | 3(B)               | 4(C)               | 5(D)                   | 6(E)                   | 7(F)                   |

# Table 12.2. Special Function Register (SFR) Memory Map for Page 0x0C

# **13.2.** Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described in this section. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

# SFR Definition 18.3. OSCICRS: Internal Oscillator Coarse Calibration

| Bit                                 | 7      | 6            | 5                            | 4      | 3      | 2      | 1      | 0      |  |

|-------------------------------------|--------|--------------|------------------------------|--------|--------|--------|--------|--------|--|

| Name                                |        | OSCICRS[6:0] |                              |        |        |        |        |        |  |

| Туре                                | R      |              | R/W                          |        |        |        |        |        |  |

| Reset                               | 0      | Varies       | Varies                       | Varies | Varies | Varies | Varies | Varies |  |

| SFR Address = 0xA2; SFR Page = 0x0F |        |              |                              |        |        |        |        |        |  |

| Bit                                 | Name   |              | Function                     |        |        |        |        |        |  |

| 7                                   | Unused | Read =       | Read = 0: Write = Don't Care |        |        |        |        |        |  |

| 7   | Unused       | Read = 0; Write = Don't Care                                                                                                                                                                                                                                                                                     |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0 | OSCICRS[6:0] | Internal Oscillator Coarse Calibration Bits.                                                                                                                                                                                                                                                                     |

|     |              | These bits determine the internal oscillator period. When set to 0000000b, the internal oscillator operates at its slowest setting. When set to 1111111b, the internal oscillator operates at its fastest setting. The reset value is factory calibrated to generate an internal oscillator frequency of 24 MHz. |

### SFR Definition 18.4. OSCIFIN: Internal Oscillator Fine Calibration

| Bit   | 7 | 6 | 5            | 4      | 3      | 2      | 1      | 0      |

|-------|---|---|--------------|--------|--------|--------|--------|--------|

|       |   |   | OSCIFIN[5:0] |        |        |        |        |        |

| Туре  | R | R |              | R/W    |        |        |        |        |

| Reset | 0 | 0 | Varies       | Varies | Varies | Varies | Varies | Varies |

#### SFR Address = 0x9E; SFR Page = 0x0F

| Bit | Name         | Function                                                                                                                                                         |  |  |  |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7:6 | Unused       | Read = 00b; Write = Don't Care                                                                                                                                   |  |  |  |

| 5:0 | OSCIFIN[5:0] | Internal Oscillator Fine Calibration Bits.                                                                                                                       |  |  |  |

|     |              | These bits are fine adjustment for the internal oscillator period. The reset value is factory calibrated to generate an internal oscillator frequency of 24 MHz. |  |  |  |

# SFR Definition 19.2. XBR1: Port I/O Crossbar Register 1

| Bit   | 7   | 6   | 5    | 4           | 3         | 2 | 1      | 0        |

|-------|-----|-----|------|-------------|-----------|---|--------|----------|

|       | •   | -   | _    | -           | 0         | - | •      |          |

| Name  | T1E | T0E | ECIE | PCA0ME[2:0] |           |   | SYSCKE | Reserved |

| Туре  | R/W | R/W | R/W  | R/W         | R/W R/W R |   |        | R/W      |

| Type  |     |     |      |             |           |   |        | -        |

| Reset | 0   | 0   | 0    | 0           | 0         | 0 | 0      | 0        |

|       |     |     |      |             |           |   |        |          |

### SFR Address = 0xE2; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | T1E         | <b>T1 Enable.</b><br>0: T1 unavailable at Port pin.<br>1: T1 routed to Port pin.                                                                                                                                                                                                                                                                                                                                                                                    |

| 6   | TOE         | <b>T0 Enable.</b><br>0: T0 unavailable at Port pin.<br>1: T0 routed to Port pin.                                                                                                                                                                                                                                                                                                                                                                                    |

| 5   | ECIE        | PCA0 External Counter Input Enable.<br>0: ECI unavailable at Port pin.<br>1: ECI routed to Port pin.                                                                                                                                                                                                                                                                                                                                                                |

| 4:2 | PCA0ME[2:0] | <ul> <li>PCA Module I/O Enable Bits.</li> <li>000: All PCA I/O unavailable at Port pins.</li> <li>001: CEX0 routed to Port pin.</li> <li>010: CEX0, CEX1 routed to Port pins.</li> <li>011: CEX0, CEX1, CEX2 routed to Port pins.</li> <li>100: CEX0, CEX1, CEX2, CEX3 routed to Port pins.</li> <li>101: CEX0, CEX1, CEX2, CEX3, CEX4 routed to Port pins.</li> <li>110: CEX0, CEX1, CEX2, CEX3, CEX4, CEX5 routed to Port pins.</li> <li>111: RESERVED</li> </ul> |

| 1   | SYSCKE      | /SYSCLK Output Enable.<br>0: /SYSCLK unavailable at Port pin.<br>1: /SYSCLK output routed to Port pin.                                                                                                                                                                                                                                                                                                                                                              |

| 0   | Reserved    | Always Write to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# SFR Definition 19.10. P3MASK: Port 3 Mask Register

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-------------|---|---|---|---|---|---|---|--|--|

| Name  | P3MASK[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W         |   |   |   |   |   |   |   |  |  |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

#### SFR Address = 0xAF; SFR Page = 0x00

| Bit   | Name              | Function                                                                                                                                                                                            |

|-------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | P3MASK[7:0]       | Port 1 Mask Value.                                                                                                                                                                                  |

|       |                   | Selects P3 pins to be compared to the corresponding bits in P3MAT.<br>0: P3.n pin logic value is ignored and cannot cause a Port Mismatch event.<br>1: P3.n pin logic value is compared to P3MAT.n. |

| Note: | P3.0 is available | on 40-pin and 32-pin packages. P3.1-P3.7 are available on 40-pin packages                                                                                                                           |

# SFR Definition 19.11. P3MAT: Port 3 Match Register

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|

| Name  | P3MAT[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |  |

| Reset | 1          | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

SFR Address = 0xAE; SFR Page = 0x00

| Bit   | Name                 | Function                                                                                                                                                                                   |

|-------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | P3MAT[7:0]           | Port 3 Match Value.                                                                                                                                                                        |

|       |                      | Match comparison value used on Port 3 for bits in P3MAT which are set to 1.<br>0: P3.n pin logic value is compared with logic LOW.<br>1: P3.n pin logic value is compared with logic HIGH. |

| Note: | P3.0 is available of | on 40-pin and 32-pin packages. P3.1-P3.7 are available on 40-pin packages                                                                                                                  |

# SFR Definition 19.23. P2SKIP: Port 2 Skip

| Bit   | 7           | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|-------|-------------|---|---|----|---|---|---|---|--|--|

| Name  | P2SKIP[7:0] |   |   |    |   |   |   |   |  |  |

| Туре  |             |   |   | R/ | W |   |   |   |  |  |

| Reset | 0           | 0 | 0 | 0  | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xD6; SFR Page = 0x0F

| Bit   | Name                                                        | Function                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|-------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | P2SKIP[7:0]                                                 | Port 2 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|       |                                                             | <ul> <li>These bits select Port 2 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P2.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P2.n pin is skipped by the Crossbar.</li> </ul> |  |  |  |  |  |

| Note: | ote: P2.2-P2.7 are available on 40-pin and 32-pin packages. |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

# SFR Definition 19.24. P3: Port 3

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---------|---|---|---|---|---|---|---|--|--|--|

| Name  | P3[7:0] |   |   |   |   |   |   |   |  |  |  |

| Туре  | R/W     |   |   |   |   |   |   |   |  |  |  |

| Reset | 1       |   |   |   |   |   |   |   |  |  |  |

#### SFR Address = 0xB0; SFR Page = All Pages; Bit-Addressable

| Bit   | Name                                                                                              | Description                                                                                                                                   | Write                                                                         | Read                                                                    |  |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:0   | P3[7:0]                                                                                           | <b>Port 3 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P3.n Port pin is logic<br>LOW.<br>1: P3.n Port pin is logic<br>HIGH. |  |  |  |  |  |  |

| Note: | Note: P3.0 is available on 40-pin and 32-pin packages. P3.1-P3.7 are available on 40-pin packages |                                                                                                                                               |                                                                               |                                                                         |  |  |  |  |  |  |

$$multiplier = \frac{20000}{baud_rate} - 1$$

$$prescaler = ln \left[ \frac{SYSCLK}{(multiplier + 1) \times baud_rate \times 200} \right] \times \frac{1}{ln2} - 1$$

$$divider = \frac{SYSCLK}{(2^{(prescaler + 1)} \times (multiplier + 1) \times baud_rate)}$$

In all of these equations, the results must be rounded down to the nearest integer.

The following example shows the steps for calculating the baud rate values for a Master node running at 24 MHz and communicating at 19200 bits/sec. First, calculate the multiplier:

multiplier =

$$\frac{20000}{19200} - 1 = 0.0417 \cong 0$$

Next, calculate the prescaler:

prescaler =

$$\ln \frac{24000000}{(0+1) \times 19200 \times 200} \times \frac{1}{\ln 2} - 1 = 1.644 \cong 1$$

Finally, calculate the divider:

divider =

$$\frac{24000000}{2^{(1+1)} \times (0+1) \times 19200}$$

= 312.5  $\cong$  312

These values lead to the following baud rate:

baud\_rate =

$$\frac{24000000}{2^{(1+1)} \times (0+1) \times 312} \cong 19230.77$$

The following code programs the interface in Master mode, using the Enhanced Checksum and enables the interface to operate at 19230 bits/sec using a 24 MHz system clock.

| LINOCF = 0x80;<br>LINOCF  = 0x40;                                                                                                                                                    | <pre>// Activate the interface // Set the node as a Master</pre>                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>LINOADR = 0x0D;<br/>// Initialize the register (prescaler,<br/>LINODAT = ( 0x01 &lt;&lt; 6 ) + ( 0x00 &lt;&lt; 1<br/>LINOADR = 0x0C;<br/>LINODAT = (unsigned char)_0x138;</pre> | ) + ( ( 0x138 & 0x0100 ) >> 8 );<br>// Point to the LINODIV register                                                                                   |

| LIN0ADR = $0 \times 0B;$<br>LIN0DAT  = $0 \times 80;$<br>LIN0ADR = $0 \times 08;$<br>LIN0DAT = $0 \times 0C;$                                                                        | <pre>// Point to the LINOSIZE register // Initialize the checksum as Enhanced // Point to LINOCTRL register // Reset any error and the interrupt</pre> |

Table 20.2 includes the configuration values required for the typical system clocks and baud rates:

| Name                                | SFR Name<br>(High)                                                                                                                                                                                                                                                     | SFR                                                                                                                                                                                                                            | SFR Name                                                                                                                                                                                                                                                           | SFR                                                                                                                                                                                                                                                                                                                                              | 16-bit                                                                                                                                                                                                                                                                                                                                       | Deest                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | (ingn)                                                                                                                                                                                                                                                                 | سلمام ۸                                                                                                                                                                                                                        | (Low)                                                                                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                              | Reset<br>Value                                                                                                                                                                                                                                                                                                                                                                                             |

|                                     | ,                                                                                                                                                                                                                                                                      | Addr.                                                                                                                                                                                                                          | (LOW)                                                                                                                                                                                                                                                              | Addr.                                                                                                                                                                                                                                                                                                                                            | SFR                                                                                                                                                                                                                                                                                                                                          | Value                                                                                                                                                                                                                                                                                                                                                                                                      |

| IF2 Data A 2                        | CAN0IF2DA2H                                                                                                                                                                                                                                                            | 0xFB                                                                                                                                                                                                                           | CAN0IF2DA2L                                                                                                                                                                                                                                                        | 0xFA                                                                                                                                                                                                                                                                                                                                             | CAN0IF2DA2                                                                                                                                                                                                                                                                                                                                   | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| IF2 Data B 1                        | CAN0IF2DB1H                                                                                                                                                                                                                                                            | 0xFD                                                                                                                                                                                                                           | CAN0IF2DB1L                                                                                                                                                                                                                                                        | 0xFC                                                                                                                                                                                                                                                                                                                                             | CAN0IF2DB1                                                                                                                                                                                                                                                                                                                                   | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| IF2 Data B 2                        | CAN0IF2DB2H                                                                                                                                                                                                                                                            | 0xFF                                                                                                                                                                                                                           | CAN0IF2DB2L                                                                                                                                                                                                                                                        | 0xFE                                                                                                                                                                                                                                                                                                                                             | CAN0IF2DB2                                                                                                                                                                                                                                                                                                                                   | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| Transmission Request 1 <sup>1</sup> | CAN0TR1H                                                                                                                                                                                                                                                               | 0xA3                                                                                                                                                                                                                           | CAN0TR1L                                                                                                                                                                                                                                                           | 0xA2                                                                                                                                                                                                                                                                                                                                             | CAN0TR1                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| Transmission Request 2 <sup>1</sup> | CAN0TR2H                                                                                                                                                                                                                                                               | 0xA5                                                                                                                                                                                                                           | CAN0TR2L                                                                                                                                                                                                                                                           | 0xA4                                                                                                                                                                                                                                                                                                                                             | CAN0TR2                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| New Data 1 <sup>1</sup>             | CAN0ND1H                                                                                                                                                                                                                                                               | 0xAB                                                                                                                                                                                                                           | CAN0ND1L                                                                                                                                                                                                                                                           | 0xAA                                                                                                                                                                                                                                                                                                                                             | CAN0ND1                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| New Data 2 <sup>1</sup>             | CAN0ND2H                                                                                                                                                                                                                                                               | 0xAD                                                                                                                                                                                                                           | CAN0ND2L                                                                                                                                                                                                                                                           | 0xAC                                                                                                                                                                                                                                                                                                                                             | CAN0ND2                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| Interrupt Pending 1 <sup>1</sup>    | CAN0IP1H                                                                                                                                                                                                                                                               | 0xAF                                                                                                                                                                                                                           | CAN0IP1L                                                                                                                                                                                                                                                           | 0xAE                                                                                                                                                                                                                                                                                                                                             | CAN0IP1                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| Interrupt Pending 2 <sup>1</sup>    | CAN0IP2H                                                                                                                                                                                                                                                               | 0xB3                                                                                                                                                                                                                           | CAN0IP2L                                                                                                                                                                                                                                                           | 0xB2                                                                                                                                                                                                                                                                                                                                             | CAN0IP2                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| Message Valid 1 <sup>1</sup>        | CAN0MV1H                                                                                                                                                                                                                                                               | 0xBB                                                                                                                                                                                                                           | CAN0MV1L                                                                                                                                                                                                                                                           | 0xBA                                                                                                                                                                                                                                                                                                                                             | CAN0MV1                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| Message Valid 2 <sup>1</sup>        | CAN0MV2H                                                                                                                                                                                                                                                               | 0xBD                                                                                                                                                                                                                           | CAN0MV2L                                                                                                                                                                                                                                                           | 0xBC                                                                                                                                                                                                                                                                                                                                             | CAN0MV2                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                     | F2 Data B 1<br>F2 Data B 2<br>Fransmission Request 1 <sup>1</sup><br>Fransmission Request 2 <sup>1</sup><br>New Data 1 <sup>1</sup><br>New Data 2 <sup>1</sup><br>Interrupt Pending 1 <sup>1</sup><br>Interrupt Pending 2 <sup>1</sup><br>Message Valid 1 <sup>1</sup> | F2 Data B 1CANOIF2DB1HF2 Data B 2CANOIF2DB2HFransmission Request 11CANOTR1HFransmission Request 21CANOTR2HNew Data 11CANOND1HNew Data 21CANOID2Hnterrupt Pending 11CANOIP1Hnterrupt Pending 21CANOIP2HMessage Valid 11CANOMV1H | F2 Data B 1CANOIF2DB1H0xFDF2 Data B 2CANOIF2DB2H0xFFTransmission Request 11CANOTR1H0xA3Transmission Request 21CANOTR2H0xA5New Data 11CANOND1H0xA8New Data 21CANOID1H0xADnterrupt Pending 11CANOIP1H0xAFnterrupt Pending 21CANOIP2H0xB3Message Valid 11CANOMV1H0xBB | F2 Data B 1CANOIF2DB1H0xFDCANOIF2DB1LF2 Data B 2CANOIF2DB2H0xFFCANOIF2DB2LTransmission Request 11CANOTR1H0xA3CANOTR1LTransmission Request 21CANOTR2H0xA5CANOTR2LNew Data 11CANOND1H0xABCANOND1LNew Data 21CANOIP1H0xAFCANOND2Lnterrupt Pending 11CANOIP1H0xAFCANOIP1Lnterrupt Pending 21CANOIP2H0xB3CANOIP2LMessage Valid 11CANOMV1H0xBBCANOMV1L | F2 Data B 1CANOIF2DB1H0xFDCANOIF2DB1L0xFCF2 Data B 2CANOIF2DB2H0xFFCANOIF2DB2L0xFETransmission Request 11CANOTR1H0xA3CANOTR1L0xA2Transmission Request 21CANOTR2H0xA5CANOTR2L0xA4New Data 11CANOND1H0xABCANOND1L0xAANew Data 21CANOIP1H0xADCANOND2L0xACnterrupt Pending 11CANOIP1H0xAFCANOIP1L0xAEnterrupt Pending 21CANOIV1H0xBBCANOIV1L0xBA | F2 Data B 1CANOIF2DB1H0xFDCANOIF2DB1L0xFCCANOIF2DB1F2 Data B 2CANOIF2DB2H0xFFCANOIF2DB2L0xFECANOIF2DB2Transmission Request 11CANOTR1H0xA3CANOTR1L0xA2CANOTR1Transmission Request 21CANOTR2H0xA5CANOTR2L0xA4CANOTR2New Data 11CANOND1H0xA8CANOND1L0xAACANOND1New Data 21CANOND2H0xAFCANOIP2L0xACCANOND2nterrupt Pending 11CANOIP1H0xAFCANOIP1L0xAECANOIP1nterrupt Pending 21CANOIP2H0xB3CANOIV1L0xBACANOMV1 |

# Table 21.2. Standard CAN Registers and Reset Values

Notes:

1. Read-only register.

2. Write-enabled by CCE.

3. The reset value of CAN0TST could also be r0000000b, where r signifies the value of the CAN RX pin.

4. Write-enabled by Test.

# SFR Definition 21.1. CAN0CFG: CAN Clock Configuration

| Bit   | 7      | 6      | 5      | 4      | 3      | 2      | 1           | 0 |

|-------|--------|--------|--------|--------|--------|--------|-------------|---|

| Name  | Unused | Unused | Unused | Unused | Unused | Unused | SYSDIV[1:0] |   |

| Туре  | R      | R      | R      | R      | R      | R      | R/W         |   |

| Reset | 0      | 0      | 0      | 0      | 0      | 0      | 0           | 0 |

#### SFR Address = 0x92; SFR Page = 0x0C

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                      |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused      | Read = 000000b; Write = Don't Care.                                                                                                                                                                                                                                                                                           |

| 1:0 | SYSDIV[1:0] | CAN System Clock Divider Bits.                                                                                                                                                                                                                                                                                                |

|     |             | The CAN controller clock is derived from the CIP-51 system clock. The CAN control-<br>ler clock must be less than or equal to 25 MHz.<br>00: CAN controller clock = System Clock/1.<br>01: CAN controller clock = System Clock/2.<br>10: CAN controller clock = System Clock/4.<br>11: CAN controller clock = System Clock/8. |

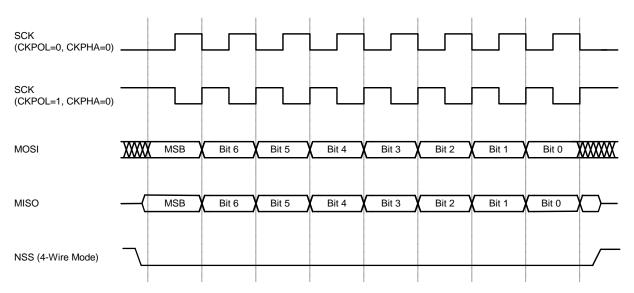

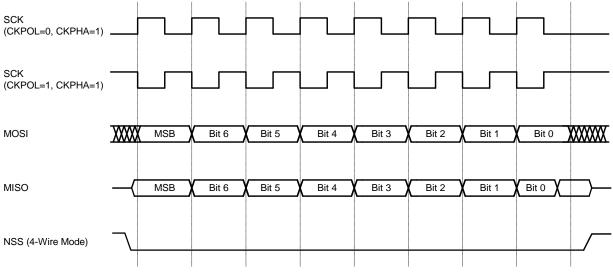

### 24.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. Note that the NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 24.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPI0 with the SPIEN bit. Figure 24.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.