Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 50MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), CANbus, LINbus, SPI, UART/USART |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                       |

| Number of I/O              | 25                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 2.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                     |

| Data Converters            | A/D 25x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-LQFP                                                          |

| Supplier Device Package    | 32-QFP (7x7)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f560-iqr  |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Figures

| Figure 1.1. C8051F568-9 and 'F570-5 (40-pin) Block Diagram                         | 17  |

|------------------------------------------------------------------------------------|-----|

| Figure 1.2. C8051F560-7 (32-pin) Block Diagram                                     |     |

| Figure 1.3. C8051F550-7 (24-pin) Block Diagram                                     |     |

| Figure 3.1. QFN-40 Pinout Diagram (Top View)                                       |     |

| Figure 3.2. QFP-32 Pinout Diagram (Top View)                                       |     |

| Figure 3.3. QFN-32 Pinout Diagram (Top View)                                       |     |

|                                                                                    |     |

| Figure 3.4. QFN-24 Pinout Diagram (Top View)<br>Figure 4.1. QFN-40 Package Drawing |     |

| 5 5 5                                                                              |     |

| Figure 4.2. QFN-40 Landing Diagram                                                 |     |

| Figure 4.3. QFP-32 Package Drawing                                                 |     |

| Figure 4.4. QFP-32 Landing Diagram                                                 |     |

| Figure 4.5. QFN-32 Package Drawing                                                 |     |

| Figure 4.6. QFN-32 Landing Diagram                                                 |     |

| Figure 4.7. QFN-24 Package Drawing                                                 |     |

| Figure 4.8. QFN-24 Landing Diagram                                                 |     |

| Figure 5.1. Minimum VDD Monitor Threshold vs. System Clock Frequency               |     |

| Figure 6.1. ADC0 Functional Block Diagram                                          |     |

| Figure 6.2. ADC0 Tracking Modes                                                    |     |

| Figure 6.3. 12-Bit ADC Tracking Mode Example                                       |     |

| Figure 6.4. 12-Bit ADC Burst Mode Example With Repeat Count Set to 4               |     |

| Figure 6.5. ADC0 Equivalent Input Circuit                                          |     |

| Figure 6.6. ADC Window Compare Example: Right-Justified Data                       |     |

| Figure 6.7. ADC Window Compare Example: Left-Justified Data                        |     |

| Figure 6.8. ADC0 Multiplexer Block Diagram                                         | 65  |

| Figure 6.9. Temperature Sensor Transfer Function                                   | 67  |

| Figure 7.1. Voltage Reference Functional Block Diagram                             | 68  |

| Figure 8.1. Comparator Functional Block Diagram                                    | 70  |

| Figure 8.2. Comparator Hysteresis Plot                                             | 71  |

| Figure 8.3. Comparator Input Multiplexer Block Diagram                             | 76  |

| Figure 9.1. External Capacitors for Voltage Regulator Input/Output—                |     |

| Regulator Enabled                                                                  | 79  |

| Figure 9.2. External Capacitors for Voltage Regulator Input/Output-Regulator Dis   | S-  |

| abled                                                                              |     |

| Figure 10.1. CIP-51 Block Diagram                                                  |     |

| Figure 11.1. C8051F55x/56x/57x Memory Map                                          |     |

| Figure 11.2. Flash Program Memory Map                                              |     |

| Figure 12.1. SFR Page Stack                                                        |     |

| Figure 12.2. SFR Page Stack While Using SFR Page 0x0 To Access SPI0DAT             |     |

| Figure 12.3. SFR Page Stack After CAN0 Interrupt Occurs                            |     |

| Figure 12.4. SFR Page Stack Upon PCA Interrupt Occurring During a CAN0 ISR .       |     |

| Figure 12.5. SFR Page Stack Upon Return From PCA Interrupt                         |     |

| Figure 12.6. SFR Page Stack Upon Return From CAN0 Interrupt                        |     |

| Figure 14.1. Flash Program Memory Map                                              |     |

|                                                                                    | 121 |

## SFR Definition 6.8. ADC0TK: ADC0 Tracking Mode Select

| Bit   | 7 | 6     | 5       | 4 | 3          | 2 | 1          | 0 |

|-------|---|-------|---------|---|------------|---|------------|---|

| Name  |   | AD0PV | VR[3:0] |   | AD0TM[1:0] |   | AD0TK[1:0] |   |

| Туре  |   | R/    | W       |   | R/         | W | R/         | W |

| Reset | 1 | 1     | 1       | 1 | 1          | 1 | 1          | 1 |

SFR Address = 0xBA; SFR Page = 0x00

| Bit | Name        | Function                                                                                                                                                                           |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | AD0PWR[3:0] | ADC0 Burst Power-up Time.                                                                                                                                                          |

|     |             | For BURSTEN = 0: ADC0 Power state controlled by AD0EN                                                                                                                              |

|     |             | For BURSTEN = 1, AD0EN = 1: ADC0 remains enabled and does not enter the very low power state                                                                                       |

|     |             | For BURSTEN = 1, AD0EN = 0: ADC0 enters the very low power state and is enabled after each convert start signal. The Power-up time is programmed according the following equation: |

|     |             | $AD0PWR = \frac{Tstartup}{200ns} - 1 \text{ or } Tstartup = (AD0PWR + 1)200ns$                                                                                                     |

| 3:2 | AD0TM[1:0]  | ADC0 Tracking Mode Enable Select Bits.                                                                                                                                             |

|     |             | 00: Reserved.                                                                                                                                                                      |

|     |             | 01: ADC0 is configured to Post-Tracking Mode.                                                                                                                                      |

|     |             | 10: ADC0 is configured to Pre-Tracking Mode.                                                                                                                                       |

|     |             | 11: ADC0 is configured to Dual Tracking Mode.                                                                                                                                      |

| 1:0 | AD0TK[1:0]  | ADC0 Post-Track Time.                                                                                                                                                              |

|     |             | 00: Post-Tracking time is equal to 2 SAR clock cycles + 2 FCLK cycles.                                                                                                             |

|     |             | 01: Post-Tracking time is equal to 4 SAR clock cycles + 2 FCLK cycles.                                                                                                             |

|     |             | 10: Post-Tracking time is equal to 8 SAR clock cycles + 2 FCLK cycles.<br>11: Post-Tracking time is equal to 16 SAR clock cycles + 2 FCLK cycles.                                  |

|     |             |                                                                                                                                                                                    |

## 6.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

## SFR Definition 10.6. PSW: Program Status Word

| Bit  | 7                                                                                                 | 6                                                                                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                             | 3               | 2             | 1              | 0            |  |  |  |

|------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------|---------------|----------------|--------------|--|--|--|

| Name | e CY                                                                                              | AC                                                                                                     | F0                                                                                                                                                                                                                                                                                                                                                                                                                       | RS                            | [<br>[1:0]      | OV            | F1             | PARITY       |  |  |  |

| Туре | R/W                                                                                               | R/W                                                                                                    | R/W R/W R/W R/W                                                                                                                                                                                                                                                                                                                                                                                                          |                               |                 |               |                | R            |  |  |  |

| Rese | -                                                                                                 | 0                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                             | 0               | 0             | 0              | 0            |  |  |  |

|      |                                                                                                   |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |                 |               |                |              |  |  |  |

| Г    | SFR Address = 0xD0; SFR Page = All Pages; Bit-Addressable         Bit       Name         Function |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |                 |               |                |              |  |  |  |

| 7    | CY                                                                                                | Carry Flag.                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                          |                               | - unotion       |               |                |              |  |  |  |

|      | 01                                                                                                | This bit is set<br>row (subtraction                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                          |                               | •               |               | •              | n) or a bor- |  |  |  |

| 6    | AC                                                                                                | Auxiliary Car                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 - 20 - 2                    |                 | - 10-11       |                | PC           |  |  |  |

|      |                                                                                                   | This bit is set<br>borrow from (s<br>metic operation                                                   | subtraction)                                                                                                                                                                                                                                                                                                                                                                                                             |                               | •               |               | • •            | ,            |  |  |  |

| 5    | F0                                                                                                | User Flag 0.                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |                 |               |                |              |  |  |  |

|      |                                                                                                   |                                                                                                        | This is a bit-addressable, general purpose flag for use under software control.                                                                                                                                                                                                                                                                                                                                          |                               |                 |               |                |              |  |  |  |

| 4:3  | RS[1:0]                                                                                           | Register Ban<br>These bits sel<br>00: Bank 0, Ao<br>01: Bank 1, Ao<br>10: Bank 2, Ao<br>11: Bank 3, Ao | ect which re<br>ddresses 0x0<br>ddresses 0x0<br>ddresses 0x                                                                                                                                                                                                                                                                                                                                                              | 00-0x07<br>08-0x0F<br>10-0x17 | s used durin    | g register ac | cesses.        |              |  |  |  |

| 2    | OV                                                                                                | This bit is set<br>An ADD, A<br>A MUL inst<br>A DIV instr                                              | <ul> <li>Overflow Flag.</li> <li>This bit is set to 1 under the following circumstances:</li> <li>An ADD, ADDC, or SUBB instruction causes a sign-change overflow.</li> <li>A MUL instruction results in an overflow (result is greater than 255).</li> <li>A DIV instruction causes a divide-by-zero condition.</li> <li>The OV bit is cleared to 0 by the ADD, ADDC, SUBB, MUL, and DIV instructions in all</li> </ul> |                               |                 |               |                |              |  |  |  |

| 1    | F1                                                                                                | <b>User Flag 1.</b><br>This is a bit-ad                                                                | ddressable, g                                                                                                                                                                                                                                                                                                                                                                                                            | general purp                  | ose flag for    | use under so  | oftware contr  | ol.          |  |  |  |

| 0    | PARITY                                                                                            | <b>Parity Flag.</b><br>This bit is set t<br>if the sum is e                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                        | ne sum of the                 | e eight bits in | the accumu    | lator is odd a | and cleared  |  |  |  |

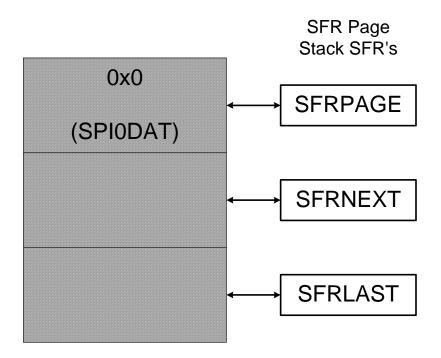

## 12.3. SFR Page Stack Example

The following is an example that shows the operation of the SFR Page Stack during interrupts. In this example, the SFR Control register is left in the default enabled state (i.e., SFRPGEN = 1), and the CIP-51 is executing in-line code that is writing values to SPI Data Register (SFR "SPI0DAT", located at address 0xA3 on SFR Page 0x00). The device is also using the CAN peripheral (CAN0) and the Programmable Counter Array (PCA0) peripheral to generate a PWM output. The PCA is timing a critical control function in its interrupt service and so its associated ISR that is set to high priority. At this point, the SFR page is set to access the SPI0DAT SFR (SFRPAGE = 0x00). See Figure 12.2.

Figure 12.2. SFR Page Stack While Using SFR Page 0x0 To Access SPI0DAT

# C8051F55x/56x/57x

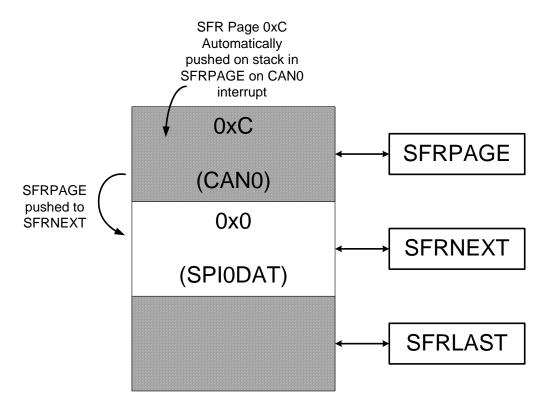

While CIP-51 executes in-line code (writing values to SPI0DAT in this example), the CAN0 Interrupt occurs. The CIP-51 vectors to the CAN0 ISR and pushes the current SFR Page value (SFR Page 0x00) into SFRNEXT in the SFR Page Stack. The SFR page needed to access CAN's SFRs is then automatically placed in the SFRPAGE register (SFR Page 0x0C). SFRPAGE is considered the "top" of the SFR Page Stack. Software can now access the CAN0 SFRs. Software may switch to any SFR Page by writing a new value to the SFRPAGE register at any time during the CAN0 ISR to access SFRs that are not on SFR Page 0x0C. See Figure 12.3.

Figure 12.3. SFR Page Stack After CAN0 Interrupt Occurs

## SFR Definition 13.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0xA8; Bit-Addressable; SFR Page = All Pages

| Bit | Name  | Function                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <ul> <li>Enable All Interrupts.</li> <li>Globally enables/disables all interrupts. It overrides individual interrupt mask settings.</li> <li>0: Disable all interrupt sources.</li> <li>1: Enable each interrupt according to its individual mask setting.</li> </ul> |

| 6   | ESPI0 | <ul> <li>Enable Serial Peripheral Interface (SPI0) Interrupt.</li> <li>This bit sets the masking of the SPI0 interrupts.</li> <li>0: Disable all SPI0 interrupts.</li> <li>1: Enable interrupt requests generated by SPI0.</li> </ul>                                 |

| 5   | ET2   | <ul> <li>Enable Timer 2 Interrupt.</li> <li>This bit sets the masking of the Timer 2 interrupt.</li> <li>0: Disable Timer 2 interrupt.</li> <li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li> </ul>                                          |

| 4   | ES0   | Enable UART0 Interrupt.<br>This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.<br>1: Enable UART0 interrupt.                                                                                                                             |

| 3   | ET1   | <ul> <li>Enable Timer 1 Interrupt.</li> <li>This bit sets the masking of the Timer 1 interrupt.</li> <li>0: Disable all Timer 1 interrupt.</li> <li>1: Enable interrupt requests generated by the TF1 flag.</li> </ul>                                                |

| 2   | EX1   | <ul> <li>Enable External Interrupt 1.</li> <li>This bit sets the masking of External Interrupt 1.</li> <li>0: Disable external interrupt 1.</li> <li>1: Enable interrupt requests generated by the INT1 input.</li> </ul>                                             |

| 1   | ET0   | <ul> <li>Enable Timer 0 Interrupt.</li> <li>This bit sets the masking of the Timer 0 interrupt.</li> <li>0: Disable all Timer 0 interrupt.</li> <li>1: Enable interrupt requests generated by the TF0 flag.</li> </ul>                                                |

| 0   | EX0   | <ul> <li>Enable External Interrupt 0.</li> <li>This bit sets the masking of External Interrupt 0.</li> <li>0: Disable external interrupt 0.</li> <li>1: Enable interrupt requests generated by the INTO input.</li> </ul>                                             |

## 14. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system, a single byte at a time, through the C2 interface or by software using the MOVX instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operation is not required. Code execution is stalled during a Flash write/erase operation. Refer to Table 5.5 for complete Flash memory electrical characteristics.

## 14.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Labs or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "27. C2 Interface" on page 300.

To ensure the integrity of Flash contents, it is strongly recommended that the on-chip  $V_{DD}$  Monitor be enabled in any system that includes code that writes and/or erases Flash memory from software. See Section 14.4 for more details. Before performing any Flash write or erase procedure, set the FLEWT bit in Flash Scale register (FLSCL) to 1. Also, note that 8-bit MOVX instructions cannot be used to erase or write to Flash memory at addresses higher than 0x00FF.

For –I (Industrial Grade) parts, parts programmed at a cold temperature below 0 °C may exhibit weakly programmed flash memory bits. If programmed at 0 °C or higher, there is no problem reading Flash across the entire temperature range of -40 °C to 125 °C. This temperature restriction does not apply to –A (Automotive Grade) devices.

#### 14.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 14.2.

## SFR Definition 14.2. FLKEY: Flash Lock and Key

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|

| Name  | FLKEY[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

#### SFR Address = 0xB7; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | FLKEY[7:0] | Flash Lock and Key Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | This register provides a lock and key function for Flash erasures and writes. Flash writes and erases are enabled by writing 0xA5 followed by 0xF1 to the FLKEY register. Flash writes and erases are automatically disabled after the next write or erase is complete. If any writes to FLKEY are performed incorrectly, or if a Flash write or erase operation is attempted while these operations are disabled, the Flash will be permanently locked from writes or erasures until the next device reset. If an application never writes to Flash, it can intentionally lock the Flash by writing a non-0xA5 value to FLKEY from software. |

|     |            | Read:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | When read, bits 1–0 indicate the current Flash lock state.<br>00: Flash is write/erase locked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |            | 01: The first key code has been written (0xA5).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |            | 10: Flash is unlocked (writes/erases allowed).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |            | 11: Flash writes/erases disabled until the next reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## SFR Definition 15.1. PCON: Power Control

| Bit   | 7 | 6 | 2    | 1    | 0 |   |   |   |

|-------|---|---|------|------|---|---|---|---|

| Name  |   |   | STOP | IDLE |   |   |   |   |

| Туре  |   |   | R/W  | R/W  |   |   |   |   |

| Reset | 0 | 0 | 0    | 0    | 0 | 0 | 0 | 0 |

SFR Address = 0x87; SFR Page = All Pages

| Bit | Name    | Function                                                                                                                                                                                                                                                                   |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | GF[5:0] | General Purpose Flags 5–0.<br>These are general purpose flags for use under software control.                                                                                                                                                                              |

| 1   | STOP    | Stop Mode Select.Setting this bit will place the CIP-51 in Stop mode. This bit will always be read as 0.1: CPU goes into Stop mode (internal oscillator stopped).                                                                                                          |

| 0   | IDLE    | <b>IDLE: Idle Mode Select.</b><br>Setting this bit will place the CIP-51 in Idle mode. This bit will always be read as 0.<br>1: CPU goes into Idle mode. (Shuts off clock to CPU, but clock to Timers, Interrupts, Serial Ports, and Analog Peripherals are still active.) |

## 16.2. Power-Fail Reset/V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the RST pin low and hold the CIP-51 in a reset state (see Figure 16.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads 1, the data may no longer be valid. The  $V_{DD}$  monitor is enabled after power-on resets. Its defined state (enabled/disabled) is not altered by any other reset source. For example, if the  $V_{DD}$  monitor is disabled by code and a software reset is performed, the  $V_{DD}$  monitor will still be disabled after the reset. To protect the integrity of Flash contents, the  $V_{DD}$  monitor must be enabled to the higher setting (VDMLVL = 1) and selected as a reset source if software contains routines which erase or write Flash memory. If the  $V_{DD}$  monitor is not enabled and set to the high level, any erase or write performed on Flash memory will cause a Flash Error device reset.

**Important Note:** If the  $V_{DD}$  monitor is being turned on from a disabled state, it should be enabled before it is selected as a reset source. Selecting the  $V_{DD}$  monitor as a reset source before it is enabled and stabilized may cause a system reset. In some applications, this reset may be undesirable. If this is not desirable in the application, a delay should be introduced between enabling the monitor and selecting it as a reset source. The procedure for enabling the  $V_{DD}$  monitor and configuring it as a reset source from a disabled state is as follows:

- 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDM0CN = 1).

- If necessary, wait for the V<sub>DD</sub> monitor to stabilize (see Table 5.4 for the V<sub>DD</sub> Monitor turn-on time). Note: This delay should be omitted if software contains routines that erase or write Flash memory.

- 3. Select the  $V_{DD}$  monitor as a reset source (PORSF bit in RSTSRC = 1).

See Figure 16.2 for  $V_{DD}$  monitor timing; note that the power-on-reset delay is not incurred after a  $V_{DD}$  monitor reset. See Table 5.4 for complete electrical characteristics of the  $V_{DD}$  monitor.

**Note:** The output of the internal voltage regulator is calibrated by the MCU immediately after any reset event. The output of the un-calibrated internal regulator could be below the high threshold setting of the  $V_{DD}$  Monitor. If this is the case *and* the  $V_{DD}$  Monitor is set to the high threshold setting *and* if the MCU receives a non-power on reset (POR), the MCU will remain in reset until a POR occurs (i.e.,  $V_{DD}$  Monitor will keep the device in reset). A POR will force the  $V_{DD}$  Monitor to the low threshold setting which is guaranteed to be below the un-calibrated output of the internal regulator. The device will then exit reset and resume normal operation. It is for this reason Silicon Labs strongly recommends that the  $V_{DD}$  Monitor is always left in the low threshold setting (i.e. default value upon POR).

When programming the Flash in-system, the  $V_{DD}$  Monitor must be set to the high threshold setting. For the highest system reliability, the time the  $V_{DD}$  Monitor is set to the high threshold setting should be minimized (e.g., setting the  $V_{DD}$  Monitor to the high threshold setting just before the Flash write operation and then changing it back to the low threshold setting immediately after the Flash write operation).

**Note:** The V<sub>DD</sub> Monitor may trigger on fast changes in voltage on the VDD pin, regardless of whether the voltage increased or decreased.

## SFR Definition 17.2. EMI0CF: External Memory Configuration

| Bit   | 7 | 6   | 5 | 4        | 3        | 2 | 1         | 0 |  |  |

|-------|---|-----|---|----------|----------|---|-----------|---|--|--|

| Name  |   |     |   | Reserved | EMD[1:0] |   | EALE[1:0] |   |  |  |

| Туре  |   | R/W |   |          |          |   |           |   |  |  |

| Reset | 0 | 0   | 0 | 0        | 0        | 0 | 1         | 1 |  |  |

#### SFR Address = 0xB2; SFR Page = 0x0F

| Bit | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:5 | Unused    | Read = 000b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 4   | Reserved  | Read = 0b; Must Write 0b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 3:2 | EMD[1:0]  | EMIF Operating Mode Select Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|     |           | 00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to on-chip memory space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|     |           | <ul> <li>01: Split Mode without Bank Select: Accesses below the 2 kB boundary are directed on-chip. Accesses above the 2 kB boundary are directed off-chip. 8-bit off-chip MOVX operations use current contents of the Address high port latches to resolve the upper address byte. To access off chip space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 2 kB boundary are directed on-chip. Accesses above the 2 kB boundary are directed off-chip. 8-bit off-chip MOVX operations uses the contents of EMI0CN to determine the high-byte of the address.</li> <li>11: External Only: MOVX accesses off-chip XRAM only. On-chip XRAM is not visible to the CPU.</li> </ul> |  |  |  |  |  |

| 1:0 | EALE[1:0] | ALE Pulse-Width Select Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|     |           | These bits only have an effect when $EMD2 = 0$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|     |           | 00: ALE high and ALE low pulse width = 1 SYSCLK cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|     |           | 01: ALE high and ALE low pulse width = 2 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|     |           | 10: ALE high and ALE low pulse width = 3 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|     |           | 11: ALE high and ALE low pulse width = 4 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

/RD

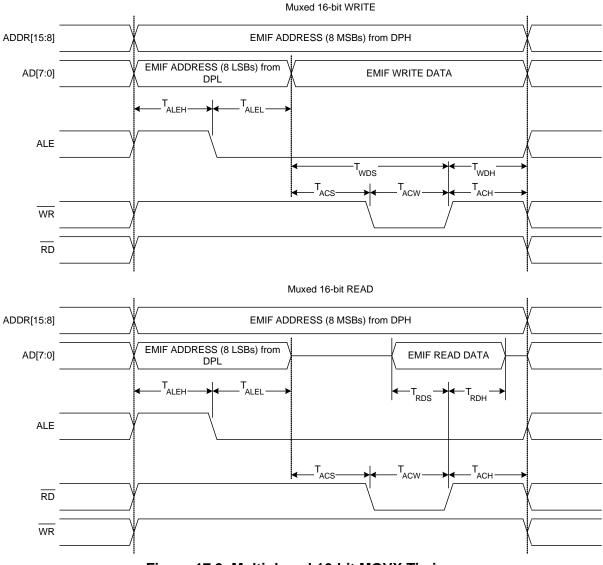

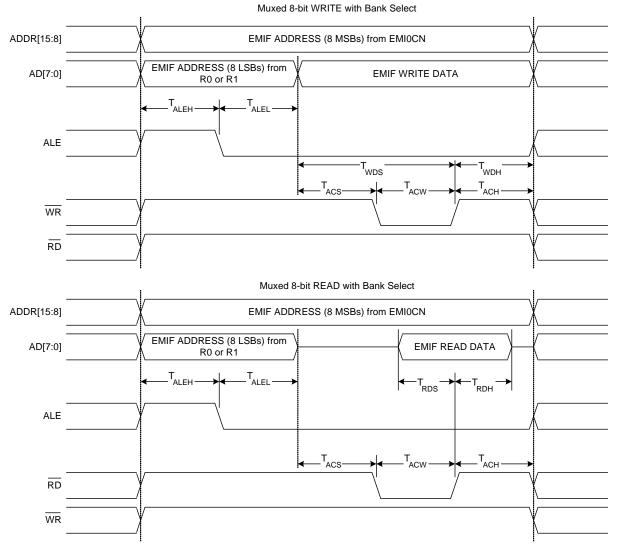

### 17.4. Multiplexed Mode

The External Memory Interface operates only in a Multiplexed mode. In Multiplexed mode, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. In this mode, an external latch (74HC373 or equivalent logic gate) is used to hold the lower 8-bits of the RAM address. The external latch is controlled by the ALE (Address Latch Enable) signal, which is driven by the External Memory Interface logic. An example of a Multiplexed Configuration is shown in Figure 17.1.

In Multiplexed mode, the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the Q outputs reflect the states of the 'D' inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time RD or WR is asserted.

A[15:8] A[15:8] ADDRESS BUS 74HC373 ALE G E ADDRESS/DATA BUS A[7:0] AD[7:0] Q D M  $V_{DD}$ 64 K X 8 SRAM (Optional) 8 F I/O[7:0] CE /WR WE

See Section "17.6.1. Multiplexed Mode" on page 153 for more information.

OE

#### 17.6.1. Multiplexed Mode 17.6.1.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011

Figure 17.3. Multiplexed 16-bit MOVX Timing

# C8051F55x/56x/57x

#### 17.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010

Figure 17.5. Multiplexed 8-bit MOVX with Bank Select Timing

## 18.4. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 18.1. A 10 M $\Omega$  resistor also must be wired across the XTAL2 and XTAL1 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 18.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 18.6).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.2 and P0.3 are used as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.3 is used as XTAL2. The Port I/O Crossbar should be configured to skip the Port pins used by the oscillator circuit; see Section "19.3. Priority Crossbar Decoder" on page 172 for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as **analog inputs**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See Section "19.4. Port I/O Initialization" on page 174 for details on Port input mode selection.

## SFR Definition 19.27. P3SKIP: Port 3Skip

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-------------|---|---|---|---|---|---|---|--|

| Name  | P3SKIP[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W         |   |   |   |   |   |   |   |  |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xD7; SFR Page = 0x0F

| Bit   | Name                                                                                              | Function                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:0   | P3SKIP[7:0]                                                                                       | Port 3 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|       |                                                                                                   | <ul> <li>These bits select Port 3 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P3.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P3.n pin is skipped by the Crossbar.</li> </ul> |  |  |  |  |  |  |

| Note: | lote: P3.0 is available on 40-pin and 32-pin packages. P3.1-P3.7 are available on 40-pin packages |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

## SFR Definition 19.28. P4: Port 4

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---------|---|---|---|---|---|---|---|--|

| Name  | P4[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W     |   |   |   |   |   |   |   |  |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |

SFR Address = 0xB5; SFR Page = All Pages

| Bit   | Name                                         | Description                                                                                                                                   | Write                                                                         | Read                                                                    |  |  |  |  |  |

|-------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | P4[7:0]                                      | <b>Port 4 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P4.n Port pin is logic<br>LOW.<br>1: P4.n Port pin is logic<br>HIGH. |  |  |  |  |  |

| Note: | e: Port 4.0 is available on 40-pin packages. |                                                                                                                                               |                                                                               |                                                                         |  |  |  |  |  |

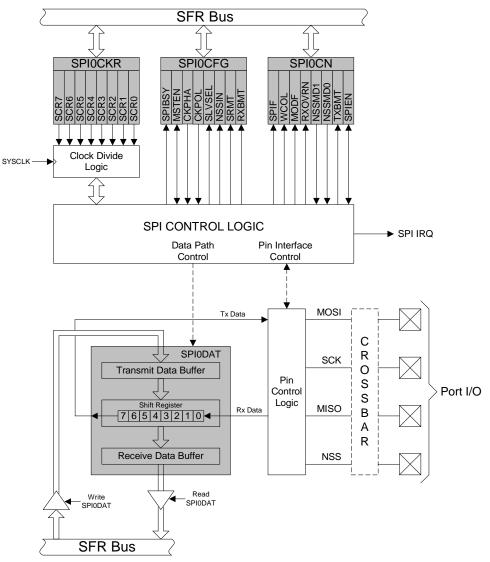

## 24. Enhanced Serial Peripheral Interface (SPI0)

The Enhanced Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

## SFR Definition 25.3. TMOD: Timer Mode

| Bit                                                                              | 7                                | 6                                                                                | 5            | 4             | 3             | 2             | 1              | 0               |  |  |

|----------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------|--------------|---------------|---------------|---------------|----------------|-----------------|--|--|

| Name                                                                             | GATE1                            | C/T1                                                                             | T1M[1:0]     |               | GATE0         | C/T0          | TOM            | [1:0]           |  |  |

| Туре                                                                             | R/W                              | R/W                                                                              | R/           | /W            | R/W           | R/W           | R/W            |                 |  |  |

| Reset 0                                                                          |                                  | 0                                                                                | 0            | 0             | 0             | 0             | 0              | 0               |  |  |

| SFR A                                                                            | ddress = 0x8                     | ; SFR Page = All Pages                                                           |              |               |               |               |                |                 |  |  |

| Bit                                                                              |                                  |                                                                                  |              |               |               |               |                |                 |  |  |

| 7                                                                                | GATE1                            | Timer 1 Ga                                                                       | te Control.  |               |               |               |                |                 |  |  |

|                                                                                  |                                  | 0: Timer 1 e                                                                     | nabled whe   | n TR1 = 1 irr | espective of  | INT1 logic le | evel.          |                 |  |  |

|                                                                                  |                                  |                                                                                  |              |               | 1 AND INT1    | is active as  | defined by b   | oit IN1PL in    |  |  |

|                                                                                  |                                  | register IT0                                                                     | 1CF (see SF  | R Definition  | 13.7).        |               |                |                 |  |  |

| 6                                                                                | C/T1                             | Counter/Ti                                                                       | mer 1 Selec  | t.            |               |               |                |                 |  |  |

|                                                                                  |                                  |                                                                                  |              | •             | ock defined b | •             | -              |                 |  |  |

|                                                                                  |                                  | 1: Counter: Timer 1 incremented by high-to-low transitions on external pin (T1). |              |               |               |               |                |                 |  |  |

| 5:4                                                                              | T1M[1:0]                         | Timer 1 Mo                                                                       | de Select.   |               |               |               |                |                 |  |  |

|                                                                                  |                                  |                                                                                  |              | ner 1 operat  | ion mode.     |               |                |                 |  |  |

|                                                                                  |                                  |                                                                                  | 13-bit Cour  |               |               |               |                |                 |  |  |

|                                                                                  |                                  |                                                                                  | 16-bit Court |               | Auto Doloo    | d             |                |                 |  |  |

| 10: Mode 2, 8-bit Counter/Timer with Auto-Reload<br>11: Mode 3, Timer 1 Inactive |                                  |                                                                                  |              |               |               | u             |                |                 |  |  |

| 3                                                                                | GATE0                            | Timer 0 Ga                                                                       |              |               |               |               |                |                 |  |  |

| Ŭ                                                                                | 0/1120                           |                                                                                  |              | n TR0 = 1 irr | espective of  | INTO logic le | evel           |                 |  |  |

|                                                                                  |                                  |                                                                                  |              |               |               |               |                | by bit IN0PL in |  |  |

|                                                                                  |                                  |                                                                                  |              | R Definition  |               |               | ,              |                 |  |  |

| 2                                                                                | C/T0                             | Counter/Timer 0 Select.                                                          |              |               |               |               |                |                 |  |  |

|                                                                                  |                                  |                                                                                  |              | •             | ock defined b | •             | •              |                 |  |  |

|                                                                                  |                                  | 1: Counter:                                                                      | Timer 0 incr | emented by    | high-to-low t | ransitions or | n external pir | n (T0).         |  |  |

| 1:0                                                                              | T0M[1:0]                         | Timer 0 Mo                                                                       | de Select.   |               |               |               |                |                 |  |  |

|                                                                                  |                                  |                                                                                  |              | ner 0 operat  | ion mode.     |               |                |                 |  |  |

|                                                                                  | 00: Mode 0, 13-bit Counter/Timer |                                                                                  |              |               |               |               |                |                 |  |  |

|                                                                                  |                                  |                                                                                  | 16-bit Court |               | n Auto-Reloa  | d             |                |                 |  |  |

|                                                                                  |                                  | -                                                                                |              |               |               | u             |                |                 |  |  |

|                                                                                  |                                  | 11: Mode 3, Two 8-bit Counter/Timers                                             |              |               |               |               |                |                 |  |  |

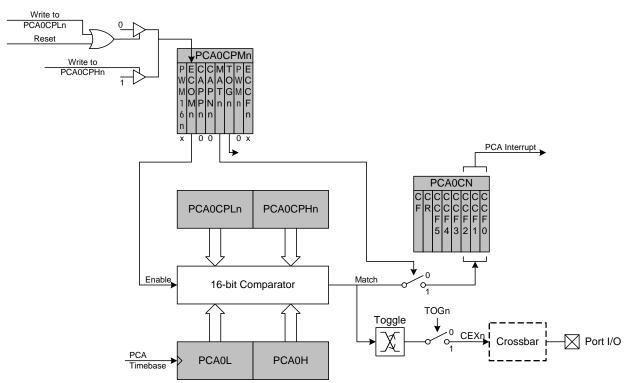

Figure 26.6. PCA High-Speed Output Mode Diagram

#### 26.3.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 26.1.

$$\mathsf{F}_{\mathsf{CEXn}} = \frac{\mathsf{F}_{\mathsf{PCA}}}{2 \times \mathsf{PCA0CPHn}}$$

**Note**: A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

#### Equation 26.1. Square Wave Frequency Output

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS[2:0] bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, CEXn is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register. Note that the MATn bit should normally be set to 0 in this mode. If the MATn bit is set to 1, the CCFn flag for the channel will be set when the 16-bit PCA0 counter and the 16-bit capture/compare register for the channel are equal.

## **DOCUMENT CHANGE LIST**

## **Revision 0.5 to Revision 1.0**

- Updated "2. Ordering Information" to include -A (Automotive) devices and automotive qualification information.

- Updated Figure 4.8 on page 35.

- Updated supply current related specifications throughout "5. Electrical Characteristics".

- Updated SFR Definition 7.1 to change VREF high setting to 2.20 V from 2.25 V.

- Updated Figure 8.1 to indicate that Comparators are powered from V<sub>IO</sub> and not V<sub>DDA</sub>.

- Updated the Gain Table in "6.3.1. Calculating the Gain Value" to fix the ADC0GNH Value in the last row.

- Updated Table 10.1 with correct timing for all branch instructions, MOVC, and CPL A.

- Updated "14.2. Non-volatile Data Storage" to clarify behavior of 8-bit MOVX instructions and when writing/erasing Flash.

- Updated SFR Definition 14.3 (FLSCL) to include FLEWT bit definition. This bit must be set before writing or erasing Flash. Also updated Table 5.5 to reflect new Flash Write and Erase timing.

- Updated "16.7. Flash Error Reset" with an additional cause of a Flash Error reset.

- Updated "19.1.3. Interfacing Port I/O in a Multi-Voltage System" to remove note regarding interfacing to voltages above VIO.

- Updated "22. SMBus" to remove all hardware ACK features, including SMB0ADM and SMB0ADR SFRs.

- Updated SFR Definition 23.1 (SCON0) to correct SFR Page to 0x00 from All Pages.

- All items from the C8051F55x-F56x-57x Errata dated November 5th, 2009 are incorporated into this data sheet.

## **Revision 1.0 to Revision 1.1**

- Updated "1. System Overview" with a voltage range specification for the internal oscillator.

- Updated Table 5.6, "Internal High-Frequency Oscillator Electrical Characteristics," on page 42 with new conditions for the internal oscillator accuracy. The internal oscillator accuracy is dependent on the operating voltage range.

- Updated "5. Electrical Characteristics" to remove the internal oscillator curve across temperature diagram.

- Updated Figure 6.4 on Page 51 with new timing diagram when using CNVSTR pin.

- Updated SFR Definition 7.1 (REF0CN) with oscillator suspend requirement for ZTCEN.

- Fixed incorrect cross references in "8. Comparators" .

- Updated SFR Definition 9.1 (REGOCN) with a new definition for Bit 6. The bit 6 reset value is 1b and must be written to 1b.

- Update "15.3. Suspend Mode" with note regarding ZTCEN.

- Added Port 2 Event and Port 3 Events to wake-up sources in "18.2.1. Internal Oscillator Suspend Mode"

- Updated "20. Local Interconnect Network (LIN0)" with a voltage range specification for the internal oscillator.

- Updated LIN Register Definitions 20.9 and 20.10 with correct reset values.

- Updated "21. Controller Area Network (CAN0)" with a voltage range specification for the internal oscillator.

- Updated C2 Register Definitions 27.2 and 27.3 with correct C2 and SFR Addresses.