Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), CANbus, SPI, UART/USART       |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 25x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f561-im |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F55x/56x/57x

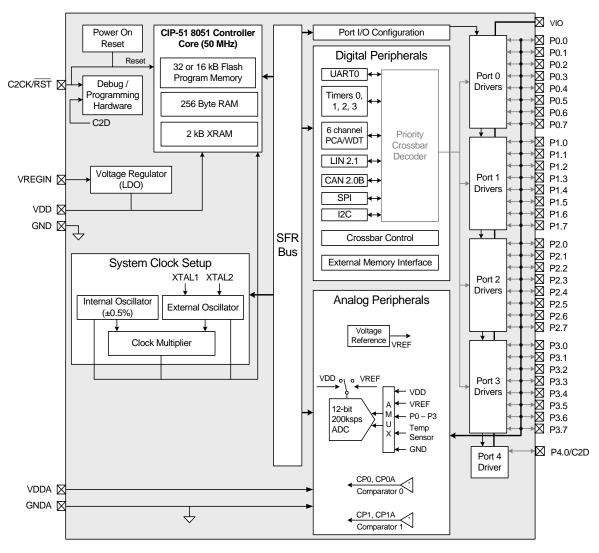

Figure 1.1. C8051F568-9 and 'F570-5 (40-pin) Block Diagram

# C8051F55x/56x/57x

Figure 1.3. C8051F550-7 (24-pin) Block Diagram

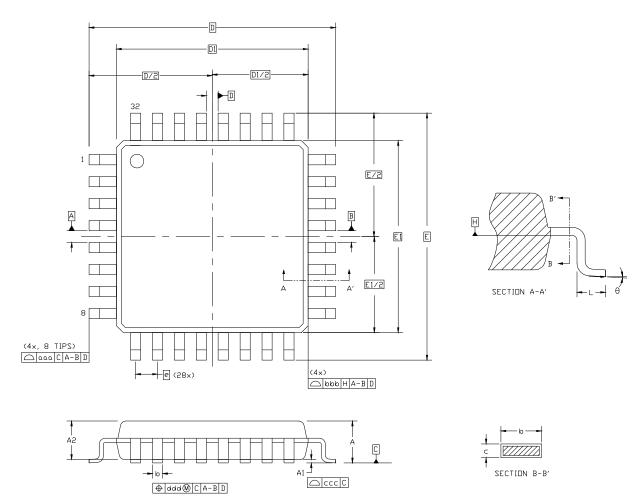

## 4.2. QFP-32 Package Specifications

Figure 4.3. QFP-32 Package Drawing

| Dimension | Min       | Тур  | Max  |   | Dimension | Min  | Тур       | Max  |

|-----------|-----------|------|------|---|-----------|------|-----------|------|

| A         | _         | —    | 1.60 |   | E         |      | 9.00 BSC. |      |

| A1        | 0.05      | —    | 0.15 |   | E1        |      | 7.00 BSC. |      |

| A2        | 1.35      | 1.40 | 1.45 |   | L         | 0.45 | 0.60      | 0.75 |

| b         | 0.30      | 0.37 | 0.45 |   | aaa       | 0.20 |           |      |

| С         | 0.09      | —    | 0.20 |   | bbb       |      | 0.20      |      |

| D         | 9.00 BSC. |      |      |   | CCC       |      | 0.10      |      |

| D1        | 7.00 BSC. |      |      |   | ddd       |      | 0.20      |      |

| е         | 0.80 BSC. |      |      | 1 | θ         | 0°   | 3.5°      | 7°   |

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC outline MS-026, variation BBA.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### Table 5.3. Port I/O DC Electrical Characteristics

$V_{DD}$  = 1.8 to 2.75 V, –40 to +125 °C unless otherwise specified.

| Parameters          | Conditions                                   | Min                    | Тур                   | Max       | Units |

|---------------------|----------------------------------------------|------------------------|-----------------------|-----------|-------|

| Output High Voltage | I <sub>OH</sub> = –3 mA, Port I/O push-pull  | V <sub>IO</sub> – 0.4  | —                     | _         | V     |

|                     | I <sub>OH</sub> = −10 μA, Port I/O push-pull | V <sub>IO</sub> – 0.02 | —                     | —         |       |

|                     | I <sub>OH</sub> = –10 mA, Port I/O push-pull | —                      | V <sub>IO</sub> – 0.7 | —         |       |

| Output Low Voltage  | V <sub>IO</sub> = 1.8 V:                     |                        |                       |           |       |

|                     | I <sub>OL</sub> = 70 μA                      | —                      | —                     | 50        |       |

|                     | I <sub>OL</sub> = 8.5 mA                     | —                      | —                     | 750       |       |

|                     | V <sub>IO</sub> = 2.7 V:                     |                        |                       |           |       |

|                     | I <sub>OL</sub> = 70 μA                      | —                      | —                     | 45        | mV    |

|                     | I <sub>OL</sub> = 8.5 mA                     | —                      | —                     | 550       |       |

|                     | V <sub>IO</sub> = 5.25 V:                    |                        |                       |           |       |

|                     | I <sub>OL</sub> = 70 μA                      | —                      | —                     | 40        |       |

|                     | I <sub>OL</sub> = 8.5 mA                     | —                      | —                     | 400       |       |

| Input High Voltage  | V <sub>REGIN</sub> = 5.25 V                  | 0.7 x VIO              | —                     |           | V     |

| Input Low Voltage   | V <sub>REGIN</sub> = 2.7 V                   | —                      | _                     | 0.3 x VIO | V     |

|                     | Weak Pullup Off                              | —                      | —                     | ±2        |       |

|                     | Weak Pullup On, V <sub>IO</sub> = 2.1 V,     |                        |                       |           |       |

|                     | $V_{IN} = 0 V, V_{DD} = 1.8 V$               |                        | 7                     | 9         |       |

| Input Leakage       | Weak Pullup On, $V_{IO} = 2.6$ V,            |                        |                       | Ū.        | μA    |

| Current             |                                              |                        | 47                    |           | μΛ    |

|                     | $V_{IN} = 0 V, V_{DD} = 2.6 V$               | —                      | 17                    | 22        |       |

|                     | Weak Pullup On, V <sub>IO</sub> = 5.0 V,     |                        |                       |           |       |

|                     | $V_{IN} = 0 V, V_{DD} = 2.6 V$               | —                      | 49                    | 115       |       |

# C8051F55x/56x/57x

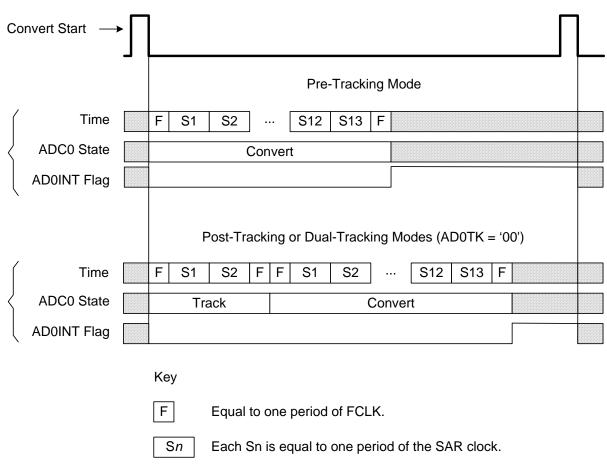

Figure 6.3. 12-Bit ADC Tracking Mode Example

#### 6.1.4. Burst Mode

Burst Mode is a power saving feature that allows ADC0 to remain in a very low power state between conversions. When Burst Mode is enabled, ADC0 wakes from a very low power state, accumulates 1, 4, 8, or 16 samples using an internal Burst Mode clock (approximately 25 MHz), then re-enters a very low power state. Since the Burst Mode clock is independent of the system clock, ADC0 can perform multiple conversions then enter a very low power state within a single system clock cycle, even if the system clock is slow (e.g., 32.768 kHz), or suspended.

Burst Mode is enabled by setting BURSTEN to logic 1. When in Burst Mode, AD0EN controls the ADC0 idle power state (i.e. the state ADC0 enters when not tracking or performing conversions). If AD0EN is set to logic 0, ADC0 is powered down after each burst. If AD0EN is set to logic 1, ADC0 remains enabled after each burst. On each convert start signal, ADC0 is awakened from its Idle Power State. If AD0C0 is powered down, it will automatically power up and wait the programmable Power-up Time controlled by the AD0PWR bits. Otherwise, ADC0 will start tracking and converting immediately. Figure 6.4 shows an example of Burst Mode Operation with a slow system clock and a repeat count of 4.

Important Note: When Burst Mode is enabled, only Post-Tracking and Dual-Tracking modes can be used.

When Burst Mode is enabled, a single convert start will initiate a number of conversions equal to the repeat count. When Burst Mode is disabled, a convert start is required to initiate each conversion. In both modes, the ADC0 End of Conversion Interrupt Flag (AD0INT) will be set after "repeat count" conversions have

# SFR Definition 6.5. ADC0H: ADC0 Data Word MSB

| Bit   | 7   | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|------------|---|---|---|---|---|---|

| Name  |     | ADC0H[7:0] |   |   |   |   |   |   |

| Туре  | R/W |            |   |   |   |   |   |   |

| Reset | 0   | 0          | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xBE; SFR Page = 0x00

| Bit | Name       | Function                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0H[7:0] | ADC0 Data Word High-Order Bits.                                                                        |

|     |            | For AD0LJST = 0 and AD0RPT as follows:                                                                 |

|     |            | 00: Bits 3–0 are the upper 4 bits of the 12-bit result. Bits 7–4 are 0000b.                            |

|     |            | 01: Bits 4–0 are the upper 5 bits of the 14-bit result. Bits 7–5 are 000b.                             |

|     |            | 10: Bits 5–0 are the upper 6 bits of the 15-bit result. Bits 7–6 are 00b.                              |

|     |            | 11: Bits 7–0 are the upper 8 bits of the 16-bit result.                                                |

|     |            | For AD0LJST = 1 (AD0RPT must be 00): Bits 7–0 are the most-significant bits of the ADC0 12-bit result. |

## SFR Definition 6.6. ADC0L: ADC0 Data Word LSB

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | ADC0L[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xBD; SFR Page = 0x00

| Bit | Name | Function                                                                                                                                                                                                                              |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 |      | ADC0 Data Word Low-Order Bits.<br>For AD0LJST = 0: Bits 7–0 are the lower 8 bits of the ADC0 Accumulated Result.<br>For AD0LJST = 1 (AD0RPT must be '00'): Bits 7–4 are the lower 4 bits of the 12-bit<br>result. Bits 3–0 are 0000b. |

# 9. Voltage Regulator (REG0)

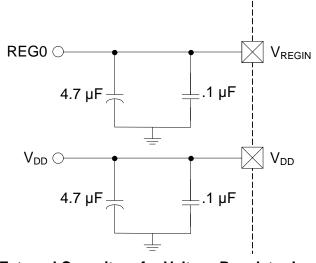

C8051F55x/56x/57x devices include an on-chip low dropout voltage regulator (REG0). The input to REG0 at the  $V_{REGIN}$  pin can be as high as 5.25 V. The output can be selected by software to 2.1 V or 2.6 V. When enabled, the output of REG0 appears on the  $V_{DD}$  pin, powers the microcontroller core, and can be used to power external devices. On reset, REG0 is enabled and can be disabled by software.

The Voltage regulator can generate an interrupt (if enabled by EREG0, EIE2.0) that is triggered whenever the  $V_{REGIN}$  input voltage drops below the dropout threshold voltage. This dropout interrupt has no pending flag and the recommended procedure to use it is as follows:

- 1. Wait enough time to ensure the  $V_{REGIN}$  input voltage is stable

- 2. Enable the dropout interrupt (EREG0, EIE2.0) and select the proper priority (PREG0, EIP2.0)

- 3. If triggered, inside the interrupt disable it (clear EREG0, EIE2.0), execute all procedures necessary to protect your application (put it in a safe mode and leave the interrupt now disabled.

- 4. In the main application, now running in the safe mode, regularly checks the DROPOUT bit (REG0CN.0). Once it is cleared by the regulator hardware the application can enable the interrupt again (EREG0, EIE1.6) and return to the normal mode operation.

The input ( $V_{REGIN}$ ) and output ( $V_{DD}$ ) of the voltage regulator should both be bypassed with a large capacitor (4.7  $\mu$ F + 0.1  $\mu$ F) to ground as shown in Figure 9.1. This capacitor will eliminate power spikes and provide any immediate power required by the microcontroller. The settling time associated with the voltage regulator is shown in Table 5.8 on page 43.

**Note:** The output of the internal voltage regulator is calibrated by the MCU immediately after any reset event. The output of the un-calibrated internal regulator could be below the high threshold setting of the  $V_{DD}$  Monitor. If this is the case *and* the  $V_{DD}$  Monitor is set to the high threshold setting *and* if the MCU receives a non-power on reset (POR), the MCU will remain in reset until a POR occurs (i.e.,  $V_{DD}$  Monitor will keep the device in reset). A POR will force the  $V_{DD}$  Monitor to the low threshold setting which is guaranteed to be below the un-calibrated output of the internal regulator. The device will then exit reset and resume normal operation. It is for this reason Silicon Labs strongly recommends that the  $V_{DD}$  Monitor is always left in the low threshold setting (i.e. default value upon POR).

# SFR Definition 13.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0xA8; Bit-Addressable; SFR Page = All Pages

| Bit | Name  | Function                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <ul> <li>Enable All Interrupts.</li> <li>Globally enables/disables all interrupts. It overrides individual interrupt mask settings.</li> <li>0: Disable all interrupt sources.</li> <li>1: Enable each interrupt according to its individual mask setting.</li> </ul> |

| 6   | ESPI0 | <ul> <li>Enable Serial Peripheral Interface (SPI0) Interrupt.</li> <li>This bit sets the masking of the SPI0 interrupts.</li> <li>0: Disable all SPI0 interrupts.</li> <li>1: Enable interrupt requests generated by SPI0.</li> </ul>                                 |

| 5   | ET2   | <ul> <li>Enable Timer 2 Interrupt.</li> <li>This bit sets the masking of the Timer 2 interrupt.</li> <li>0: Disable Timer 2 interrupt.</li> <li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li> </ul>                                          |

| 4   | ES0   | Enable UART0 Interrupt.<br>This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.<br>1: Enable UART0 interrupt.                                                                                                                             |

| 3   | ET1   | <ul> <li>Enable Timer 1 Interrupt.</li> <li>This bit sets the masking of the Timer 1 interrupt.</li> <li>0: Disable all Timer 1 interrupt.</li> <li>1: Enable interrupt requests generated by the TF1 flag.</li> </ul>                                                |

| 2   | EX1   | <ul> <li>Enable External Interrupt 1.</li> <li>This bit sets the masking of External Interrupt 1.</li> <li>0: Disable external interrupt 1.</li> <li>1: Enable interrupt requests generated by the INT1 input.</li> </ul>                                             |

| 1   | ET0   | <ul> <li>Enable Timer 0 Interrupt.</li> <li>This bit sets the masking of the Timer 0 interrupt.</li> <li>0: Disable all Timer 0 interrupt.</li> <li>1: Enable interrupt requests generated by the TF0 flag.</li> </ul>                                                |

| 0   | EX0   | <ul> <li>Enable External Interrupt 0.</li> <li>This bit sets the masking of External Interrupt 0.</li> <li>0: Disable external interrupt 0.</li> <li>1: Enable interrupt requests generated by the INTO input.</li> </ul>                                             |

# SFR Definition 14.3. FLSCL: Flash Scale

| Bit   | 7        | 6        | 5        | 4    | 3        | 2        | 1     | 0        |

|-------|----------|----------|----------|------|----------|----------|-------|----------|

| Name  | Reserved | Reserved | Reserved | FLRT | Reserved | Reserved | FLEWT | Reserved |

| Туре  | R/W      | R/W      | R/W      | R/W  | R/W      | R/W      | R/W   | R/W      |

| Reset | 0        | 0        | 0        | 0    | 0        | 0        | 0     | 0        |

#### SFR Address = 0xB6; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                            |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Reserved | Must Write 000b.                                                                                                                                                                                                                                                    |

| 4   | FLRT     | Flash Read Time Control.                                                                                                                                                                                                                                            |

|     |          | <ul> <li>This bit should be programmed to the smallest allowed value, according to the system clock speed.</li> <li>0: SYSCLK ≤ 25 MHz (Flash read strobe is one system clock).</li> <li>1: SYSCLK &gt; 25 MHz (Flash read strobe is two system clocks).</li> </ul> |

| 3:2 | Reserved | Must Write 00b.                                                                                                                                                                                                                                                     |

| 1   | FLEWT    | Flash Erase Write Time Control.<br>This bit should be set to 1b before Writing or Erasing Flash.<br>0: Short Flash Erase / Write Timing.<br>1: Extended Flash Erase / Write Timing.                                                                                 |

| 0   | Reserved | Must Write 0b.                                                                                                                                                                                                                                                      |

# C8051F55x/56x/57x

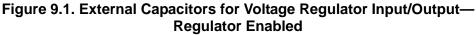

#### 17.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010

Figure 17.5. Multiplexed 8-bit MOVX with Bank Select Timing

# SFR Definition 18.3. OSCICRS: Internal Oscillator Coarse Calibration

| Bit      | 7            | 6                                                | 5            | 4         | 3          | 2  | 1 | 0 |  |  |

|----------|--------------|--------------------------------------------------|--------------|-----------|------------|----|---|---|--|--|

| Name     |              |                                                  | I            | C         | SCICRS[6:0 | )] | L |   |  |  |

| Туре     | R            |                                                  |              |           | R/W        |    |   |   |  |  |

| Reset    | 0            | Varies Varies Varies Varies Varies Varies Varies |              |           |            |    |   |   |  |  |

| SFR Ac   | dress = 0xA2 | 2; SFR Page                                      | e = 0x0F     |           |            |    |   | • |  |  |

| Bit Name |              |                                                  |              |           | Functior   | า  |   |   |  |  |

| 7        | Unused       | Read =                                           | 0. Write = D | on't Care |            |    |   |   |  |  |

| 7   | Unused       | Read = 0; Write = Don't Care                                                                                                                                                                                                                                                                                     |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0 | OSCICRS[6:0] | Internal Oscillator Coarse Calibration Bits.                                                                                                                                                                                                                                                                     |

|     |              | These bits determine the internal oscillator period. When set to 0000000b, the internal oscillator operates at its slowest setting. When set to 1111111b, the internal oscillator operates at its fastest setting. The reset value is factory calibrated to generate an internal oscillator frequency of 24 MHz. |

#### SFR Definition 18.4. OSCIFIN: Internal Oscillator Fine Calibration

| Bit   | 7 | 6 | 5      | 4                               | 3  | 2 | 1 | 0 |  |

|-------|---|---|--------|---------------------------------|----|---|---|---|--|

|       |   |   |        | OSCIFIN[5:0]                    |    |   |   |   |  |

| Туре  | R | R |        |                                 | R/ | W |   |   |  |

| Reset | 0 | 0 | Varies | Varies Varies Varies Varies Var |    |   |   |   |  |

#### SFR Address = 0x9E; SFR Page = 0x0F

| Bit | Name         | Function                                                                                                                                                         |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused       | Read = 00b; Write = Don't Care                                                                                                                                   |

| 5:0 | OSCIFIN[5:0] | Internal Oscillator Fine Calibration Bits.                                                                                                                       |

|     |              | These bits are fine adjustment for the internal oscillator period. The reset value is factory calibrated to generate an internal oscillator frequency of 24 MHz. |

# SFR Definition 19.8. P2MASK: Port 2 Mask Register

| Bit   | 7               | 6           | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |

|-------|-----------------|-------------|---|----|---|---|---|---|--|--|--|

| Name  |                 | P2MASK[7:0] |   |    |   |   |   |   |  |  |  |

| Туре  |                 |             |   | R/ | W |   |   |   |  |  |  |

| Reset | 0 0 0 0 0 0 0 0 |             |   |    |   |   |   |   |  |  |  |

SFR Address = 0xB2; SFR Page = 0x00

| Bit   | Name             | Function                                                                                                                                                                                            |

|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | P2MASK[7:0]      | Port 2 Mask Value.                                                                                                                                                                                  |

|       |                  | Selects P2 pins to be compared to the corresponding bits in P2MAT.<br>0: P2.n pin logic value is ignored and cannot cause a Port Mismatch event.<br>1: P2.n pin logic value is compared to P2MAT.n. |

| Note: | P2.2–P2.7 are av | ailable on 40-pin and 32-pin packages.                                                                                                                                                              |

## SFR Definition 19.9. P2MAT: Port 2 Match Register

| Bit   | 7 | 6          | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|-------|---|------------|---|----|---|---|---|---|--|--|

| Name  |   | P2MAT[7:0] |   |    |   |   |   |   |  |  |

| Туре  |   |            |   | R/ | W |   |   |   |  |  |

| Reset | 1 | 1          | 1 | 1  | 1 | 1 | 1 | 1 |  |  |

SFR Address = 0xB1; SFR Page = 0x00

| Bit   | Name             | Function                                                                                                                                                                                   |

|-------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | P2MAT[7:0]       | Port 2 Match Value.                                                                                                                                                                        |

|       |                  | Match comparison value used on Port 2 for bits in P2MAT which are set to 1.<br>0: P2.n pin logic value is compared with logic LOW.<br>1: P2.n pin logic value is compared with logic HIGH. |

| Note: | P2.2–P2.7 are av | ailable on 40-pin and 32-pin packages.                                                                                                                                                     |

The application should perform the following steps when an interrupt is requested.

- 1. Check the DONE bit (LIN0ST.0) and the ERROR bit (LIN0ST.2).

- 2. If performing a master receive operation and the transfer was successful, read the received data from the data buffer.

- 3. If the transfer was not successful, check the error register to determine the kind of error. Further error handling has to be done by the application.

- 4. Set the RSTINT (LIN0CTRL.3) and RSTERR bits (LIN0CTRL.2) to reset the interrupt request and the error flags.

#### 20.4. LIN Slave Mode Operation

When the device is configured for slave mode operation, it must wait for a command from a master node. Access from the firmware to the data buffer and ID registers of the LIN controller is only possible when a data request is pending (DTREQ bit (LINOST.4) is 1) and also when the LIN bus is not active (ACTIVE bit (LINOST.7) is set to 0).

The LIN controller in slave mode detects the header of the message frame sent by the LIN master. If slave synchronization is enabled (autobaud), the slave synchronizes its internal bit time to the master bit time.

The LIN controller configured for slave mode will generated an interrupt in one of three situations:

- 1. After the reception of the IDENTIFIER FIELD

- 2. When an error is detected

- 3. When the message transfer is completed.

The application should perform the following steps when an interrupt is detected:

- 1. Check the status of the DTREQ bit (LIN0ST.4). This bit is set when the IDENTIFIER FIELD has been received.

- 2. If DTREQ (LIN0ST.4) is set, read the identifier from LIN0ID and process it. If DTREQ (LIN0ST.4) is not set, continue to step 7.

- 3. Set the TXRX bit (LIN0CTRL.5) to 1 if the current frame is a transmit operation for the slave and set to 0 if the current frame is a receive operation for the slave.

- 4. Load the data length into LIN0SIZE.

- 5. For a slave transmit operation, load the data to transmit into the data buffer.

- 6. Set the DTACK bit (LIN0CTRL.4). Continue to step 10.

- 7. If DTREQ (LIN0ST.4) is not set, check the DONE bit (LIN0ST.0). The transmission was successful if the DONE bit is set.

- 8. If the transmission was successful and the current frame was a receive operation for the slave, load the received data bytes from the data buffer.

- 9. If the transmission was not successful, check LIN0ERR to determine the nature of the error. Further error handling has to be done by the application.

- 10.Set the RSTINT (LIN0CTRL.3) and RSTERR bits (LIN0CTRL.2) to reset the interrupt request and the error flags.

In addition to these steps, the application should be aware of the following:

- 1. If the current frame is a transmit operation for the slave, steps 1 through 5 must be completed during the IN-FRAME RESPONSE SPACE. If it is not completed in time, a timeout will be detected by the master.

- 2. If the current frame is a receive operation for the slave, steps 1 through 5 have to be finished until the reception of the first byte after the IDENTIFIER FIELD. Otherwise, the internal receive buffer of the LIN controller will be overwritten and a timeout error will be detected in the LIN controller.

#### 22.4.3. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

#### SFR Definition 22.3. SMB0DAT: SMBus Data

| Bit   | 7 | 6               | 5 | 4  | 3 | 2 | 2 1 0 |  |  |  |  |

|-------|---|-----------------|---|----|---|---|-------|--|--|--|--|

| Name  |   | SMB0DAT[7:0]    |   |    |   |   |       |  |  |  |  |

| Туре  |   |                 |   | R/ | W |   |       |  |  |  |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |    |   |   |       |  |  |  |  |

SFR Address = 0xC2; SMB0DAT = 0x00

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SMB0DAT[7:0] | SMBus Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |              | The SMB0DAT register contains a byte of data to be transmitted on the SMBus serial interface or a byte that has just been received on the SMBus serial interface. The CPU can read from or write to this register whenever the SI serial interrupt flag (SMB0CN.0) is set to logic 1. The serial data in the register remains stable as long as the SI flag is set. When the SI flag is not set, the system may be in the process of shifting data in/out and the CPU should not attempt to access this register. |

#### 22.5. SMBus Transfer Modes

The SMBus interface may be configured to operate as master and/or slave. At any particular time, it will be operating in one of the following four modes: Master Transmitter, Master Receiver, Slave Transmitter, or Slave Receiver. The SMBus interface enters Master Mode any time a START is generated, and remains in Master Mode until it loses an arbitration or generates a STOP. An SMBus interrupt is generated at the end of all SMBus byte frames. As a receiver, the interrupt for an ACK occurs **before** the ACK. As a transmitter, interrupts occur **after** the ACK.

|                     | Value            | s Re  | ead     |     | Current SMbus State                                                                         | Typical Response Options                                   | Va<br>Wr | lues<br>ite | sto | s<br>ected                     |

|---------------------|------------------|-------|---------|-----|---------------------------------------------------------------------------------------------|------------------------------------------------------------|----------|-------------|-----|--------------------------------|

| Mode                | Status<br>Vector | ACKRQ | ARBLOST | ACK |                                                                                             |                                                            | STA      | STO         | ACK | Next Status<br>Vector Expected |

|                     | 0100             | 0     | 0       | 0   | A slave byte was transmitted;<br>NACK received.                                             | No action required (expecting STOP condition).             | 0        | 0           | Х   | 0001                           |

| ter                 |                  | 0     | 0       | 1   | A slave byte was transmitted;<br>ACK received.                                              | Load SMB0DAT with next data byte to transmit.              | 0        | 0           | Х   | 0100                           |

| ansmit              |                  | 0     | 1       | Х   | A Slave byte was transmitted;<br>error detected.                                            | No action required (expecting Master to end transfer).     | 0        | 0           | Х   | 0001                           |

| Slave Transmitter   | 0101             | 0     | Х       | Х   | An illegal STOP or bus error<br>was detected while a Slave<br>Transmission was in progress. | Clear STO.                                                 | 0        | 0           | Х   |                                |

|                     | 0010             | 1     | 0       | Х   | A slave address + R/W was received; ACK requested.                                          | If Write, Acknowledge received address                     | 0        | 0           | 1   | 0000                           |

|                     |                  |       |         |     |                                                                                             | If Read, Load SMB0DAT with data byte; ACK received address | 0        | 0           | 1   | 0100                           |

|                     |                  |       |         |     |                                                                                             | NACK received address.                                     | 0        | 0           | 0   | —                              |

|                     |                  | 1     | 1       | Х   | Lost arbitration as master;<br>slave address + R/W received;                                | If Write, Acknowledge received address                     | 0        | 0           | 1   | 0000                           |

|                     |                  |       |         |     | ACK requested.                                                                              | If Read, Load SMB0DAT with data byte; ACK received address | 0        | 0           | 1   | 0100                           |

|                     |                  |       |         |     |                                                                                             | NACK received address.                                     | 0        | 0           | 0   |                                |

|                     |                  |       |         |     |                                                                                             | Reschedule failed transfer;<br>NACK received address.      | 1        | 0           | 0   | 1110                           |

|                     | 0001             | 0     | 0       | Х   | A STOP was detected while<br>addressed as a Slave Trans-<br>mitter or Slave Receiver.       | Clear STO.                                                 | 0        | 0           | Х   | _                              |

| eiver               |                  | 1     | 1       | Х   | Lost arbitration while attempt-<br>ing a STOP.                                              | No action required (transfer complete/aborted).            | 0        | 0           | 0   | —                              |

| Slave Rec           | 0000             | 1     | 0       | Х   | A slave byte was received;<br>ACK requested.                                                | Acknowledge received byte;<br>Read SMB0DAT.                | 0        | 0           | 1   | 0000                           |

| Slav                |                  |       |         |     |                                                                                             | NACK received byte.                                        | 0        | 0           | 0   | —                              |

|                     | 0010             | 0     | 1       | Х   | Lost arbitration while attempt-                                                             | Abort failed transfer.                                     | 0        | 0           | Х   |                                |

| ditic               |                  |       |         |     | ing a repeated START.                                                                       | Reschedule failed transfer.                                | 1        | 0           | Х   | 1110                           |

| Con                 | 0001             | 0     | 1       | Х   | Lost arbitration due to a                                                                   | Abort failed transfer.                                     | 0        | 0           | Х   | —                              |

| Bus Error Condition |                  |       |         |     | detected STOP.                                                                              | Reschedule failed transfer.                                | 1        | 0           | Х   | 1110                           |

| ΕĽ                  | 0000             | 1     | 1       | Х   | Lost arbitration while transmit-                                                            | Abort failed transfer.                                     | 0        | 0           | 0   | —                              |

| Bus                 |                  |       |         |     | ting a data byte as master.                                                                 | Reschedule failed transfer.                                | 1        | 0           | 0   | 1110                           |

### Table 22.4. SMBus Status Decoding (Continued)

| Parameter                | Description                                                   | Min                          | Мах                     | Units |

|--------------------------|---------------------------------------------------------------|------------------------------|-------------------------|-------|

| Master Mod               | <b>e Timing</b> <sup>*</sup> (See Figure 24.8 and Figure 24.9 | ))                           |                         |       |

| т <sub>мскн</sub>        | SCK High Time                                                 | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>MCKL</sub>        | SCK Low Time                                                  | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>MIS</sub>         | MISO Valid to SCK Shift Edge                                  | 1 x T <sub>SYSCLK</sub> + 20 | —                       | ns    |

| Т <sub>МІН</sub>         | SCK Shift Edge to MISO Change                                 | 0                            | —                       | ns    |

| Slave Mode               | <b>Timing</b> <sup>*</sup> (See Figure 24.10 and Figure 24.1  | 1)                           |                         |       |

| T <sub>SE</sub>          | NSS Falling to First SCK Edge                                 | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SD</sub>          | Last SCK Edge to NSS Rising                                   | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SEZ</sub>         | NSS Falling to MISO Valid                                     | _                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SDZ</sub>         | NSS Rising to MISO High-Z                                     | _                            | 4 x T <sub>SYSCLK</sub> | ns    |

| т <sub>скн</sub>         | SCK High Time                                                 | 5 x T <sub>SYSCLK</sub>      | —                       | ns    |

| Т <sub>СКL</sub>         | SCK Low Time                                                  | 5 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SIS</sub>         | MOSI Valid to SCK Sample Edge                                 | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SIH</sub>         | SCK Sample Edge to MOSI Change                                | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| Т <sub>SOH</sub>         | SCK Shift Edge to MISO Change                                 | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SLH</sub>         | Last SCK Edge to MISO Change<br>(CKPHA = 1 ONLY)              | 6 x T <sub>SYSCLK</sub>      | 8 x T <sub>SYSCLK</sub> | ns    |

| *Note: T <sub>SYSC</sub> | LK is equal to one period of the device system cl             | ock (SYSCLK).                | 1                       |       |

## Table 24.1. SPI Slave Timing Parameters

# SFR Definition 25.8. TMR2CN: Timer 2 Control

| Bit                                                                      | 7                                                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                        | 4      | 3       | 2   | 1 | 0      |  |

|--------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------|---------|-----|---|--------|--|

| Name                                                                     | TF2H                                                 | TF2L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TF2LEN                   | TF2CEN | T2SPLIT | TR2 |   | T2XCLK |  |

| Туре                                                                     | R/W                                                  | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W                      | R/W    | R/W     | R/W | R | R/W    |  |

| Rese                                                                     | <b>t</b> 0                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                        | 0      | 0       | 0   | 0 | 0      |  |

| SFR A                                                                    | SFR Address = 0xC8; Bit-Addressable; SFR Page = 0x00 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |        |         |     |   |        |  |

| Bit                                                                      | Name                                                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |        |         |     |   |        |  |

| 7                                                                        | TF2H Timer 2 High Byte Overflow Flag.                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |        |         |     |   |        |  |

|                                                                          |                                                      | Set by hardware when the Timer 2 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 2 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                                               |                          |        |         |     |   |        |  |

| 6                                                                        | TF2L                                                 | Timer 2 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |        |         |     |   |        |  |

|                                                                          |                                                      | Set by hardware when the Timer 2 low byte overflows from 0xFF to 0x00. TF2L will be set when the low byte overflows regardless of the Timer 2 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                            |                          |        |         |     |   |        |  |

| 5                                                                        | TF2LEN                                               | Timer 2 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |        |         |     |   |        |  |

|                                                                          |                                                      | When set to 1, this bit enables Timer 2 Low Byte interrupts. If Timer 2 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 2 overflows.                                                                                                                                                                                                                                                                                                                                       |                          |        |         |     |   |        |  |

| 4                                                                        | TF2CEN Timer 2 Capture Mode Enable.                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |        |         |     |   |        |  |

|                                                                          |                                                      | 0: Timer 2 Capture Mode is disabled.<br>1: Timer 2 Capture Mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |        |         |     |   |        |  |

| 3                                                                        | T2SPLIT Timer 2 Split Mode Enable.                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |        |         |     |   |        |  |

| When this bit is set, Timer 2 operates as two 8-bit                      |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | timers with auto-reload. |        |         |     |   |        |  |

| 0: Timer 2 operates in 16-bit auto<br>1: Timer 2 operates as two 8-bit a |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |        |         |     |   |        |  |

| 2                                                                        | TR2                                                  | Timer 2 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |        |         |     |   |        |  |

|                                                                          |                                                      | Timer 2 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables<br>TMR2H only; TMR2L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                                                       |                          |        |         |     |   |        |  |

| 1                                                                        | Unused                                               | Read = 0b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |        |         |     |   |        |  |

| 0                                                                        | T2XCLK                                               | Timer 2 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |        |         |     |   |        |  |

|                                                                          |                                                      | <ul> <li>This bit selects the external clock source for Timer 2. If Timer 2 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 2 Clock Select bits (T2MH and T2ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.</li> <li>0: Timer 2 clock is the system clock divided by 12.</li> <li>1: Timer 2 clock is the external clock divided by 8 (synchronized with SYSCLK).</li> </ul> |                          |        |         |     |   |        |  |

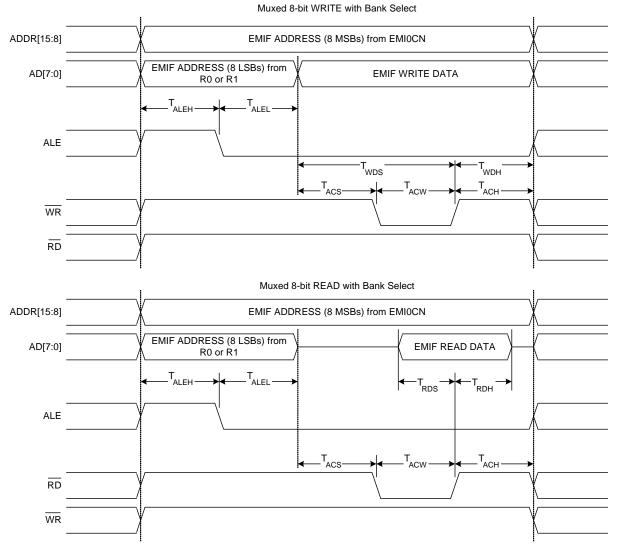

Figure 26.7. PCA Frequency Output Mode

#### 26.3.5. 8-bit, 9-bit, 10-bit and 11-bit Pulse Width Modulator Modes

Each module can be used independently to generate a pulse width modulated (PWM) output on its associated CEXn pin. The frequency of the output is dependent on the timebase for the PCA counter/timer, and the setting of the PWM cycle length (8, 9, 10 or 11-bits). For backwards-compatibility with the 8-bit PWM mode available on other devices, the 8-bit PWM mode operates slightly different than 9, 10 and 11-bit PWM modes. It is important to note that all channels configured for 8/9/10/11-bit PWM mode will use the same cycle length. It is not possible to configure one channel for 8-bit PWM mode and another for 11bit mode (for example). However, other PCA channels can be configured to Pin Capture, High-Speed Output, Software Timer, Frequency Output, or 16-bit PWM mode independently.

#### 26.3.5.1. 8-bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 8-bit PWM mode is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set. When the count value in PCA0L overflows, the CEXn output will be reset (see Figure 26.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the module's capture/compare high byte (PCA0CPHn) without software intervention. Setting the ECOMn and PWMn bits in the PCA0CPMn register, and setting the CLSEL bits in register PCA0PWM to 00b enables 8-Bit Pulse Width Modulator mode. If the MATn bit is set to 1, the CCFn flag for the module will be set each time an 8-bit comparator match (rising edge) occurs. The COVF flag in PCA0PWM can be used to detect the overflow (falling edge), which will occur every 256 PCA clock cycles. The duty cycle for 8-Bit PWM Mode is given in Equation 26.2.

Important Note About Capture/Compare Registers: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =  $\frac{(256 - PCA0CPHn)}{256}$

#### Equation 26.2. 8-Bit PWM Duty Cycle

Using Equation 26.2, the largest duty cycle is 100% (PCA0CPHn = 0), and the smallest duty cycle is 0.39% (PCA0CPHn = 0xFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

| System Clock (Hz)                                                                                                                                                                                                 | PCA0CPL5 | Timeout Interval (ms) |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------|--|--|--|--|--|

| 24,000,000                                                                                                                                                                                                        | 255      | 32.8                  |  |  |  |  |  |

| 24,000,000                                                                                                                                                                                                        | 128      | 16.5                  |  |  |  |  |  |

| 24,000,000                                                                                                                                                                                                        | 32       | 4.2                   |  |  |  |  |  |

| 3,000,000                                                                                                                                                                                                         | 255      | 262.1                 |  |  |  |  |  |

| 3,000,000                                                                                                                                                                                                         | 128      | 132.1                 |  |  |  |  |  |

| 3,000,000                                                                                                                                                                                                         | 32       | 33.8                  |  |  |  |  |  |

| 187,500 <sup>2</sup>                                                                                                                                                                                              | 255      | 4194                  |  |  |  |  |  |

| 187,500 <sup>2</sup>                                                                                                                                                                                              | 128      | 2114                  |  |  |  |  |  |

| 187,500 <sup>2</sup>                                                                                                                                                                                              | 32       | 541                   |  |  |  |  |  |

| <ul> <li>Notes:</li> <li>1. Assumes SYSCLK/12 as the PCA clock source, and a PCA0L value of 0x00 at the update time.</li> <li>2. Internal SYSCLK reset frequency = Internal Oscillator divided by 128.</li> </ul> |          |                       |  |  |  |  |  |

# Table 26.3. Watchdog Timer Timeout Intervals<sup>1</sup>

SILICON LABS

# **DOCUMENT CHANGE LIST**

# **Revision 0.5 to Revision 1.0**

- Updated "2. Ordering Information" to include -A (Automotive) devices and automotive qualification information.

- Updated Figure 4.8 on page 35.

- Updated supply current related specifications throughout "5. Electrical Characteristics".

- Updated SFR Definition 7.1 to change VREF high setting to 2.20 V from 2.25 V.

- Updated Figure 8.1 to indicate that Comparators are powered from V<sub>IO</sub> and not V<sub>DDA</sub>.

- Updated the Gain Table in "6.3.1. Calculating the Gain Value" to fix the ADC0GNH Value in the last row.

- Updated Table 10.1 with correct timing for all branch instructions, MOVC, and CPL A.

- Updated "14.2. Non-volatile Data Storage" to clarify behavior of 8-bit MOVX instructions and when writing/erasing Flash.

- Updated SFR Definition 14.3 (FLSCL) to include FLEWT bit definition. This bit must be set before writing or erasing Flash. Also updated Table 5.5 to reflect new Flash Write and Erase timing.

- Updated "16.7. Flash Error Reset" with an additional cause of a Flash Error reset.

- Updated "19.1.3. Interfacing Port I/O in a Multi-Voltage System" to remove note regarding interfacing to voltages above VIO.

- Updated "22. SMBus" to remove all hardware ACK features, including SMB0ADM and SMB0ADR SFRs.

- Updated SFR Definition 23.1 (SCON0) to correct SFR Page to 0x00 from All Pages.

- All items from the C8051F55x-F56x-57x Errata dated November 5th, 2009 are incorporated into this data sheet.

# **Revision 1.0 to Revision 1.1**

- Updated "1. System Overview" with a voltage range specification for the internal oscillator.

- Updated Table 5.6, "Internal High-Frequency Oscillator Electrical Characteristics," on page 42 with new conditions for the internal oscillator accuracy. The internal oscillator accuracy is dependent on the operating voltage range.

- Updated "5. Electrical Characteristics" to remove the internal oscillator curve across temperature diagram.

- Updated Figure 6.4 on Page 51 with new timing diagram when using CNVSTR pin.

- Updated SFR Definition 7.1 (REF0CN) with oscillator suspend requirement for ZTCEN.

- Fixed incorrect cross references in "8. Comparators" .

- Updated SFR Definition 9.1 (REGOCN) with a new definition for Bit 6. The bit 6 reset value is 1b and must be written to 1b.

- Update "15.3. Suspend Mode" with note regarding ZTCEN.

- Added Port 2 Event and Port 3 Events to wake-up sources in "18.2.1. Internal Oscillator Suspend Mode"

- Updated "20. Local Interconnect Network (LIN0)" with a voltage range specification for the internal oscillator.

- Updated LIN Register Definitions 20.9 and 20.10 with correct reset values.

- Updated "21. Controller Area Network (CAN0)" with a voltage range specification for the internal oscillator.

- Updated C2 Register Definitions 27.2 and 27.3 with correct C2 and SFR Addresses.