Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), LINbus, SPI, UART/USART       |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 25x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f562-im |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 21.2.2. Magagag Object Interface Registers           | 211 |

|------------------------------------------------------|-----|

| 21.2.2. Message Object Interface Registers           |     |

| 21.2.3. Message Handler Registers                    |     |

| 21.2.4. CAN Register Assignment                      |     |

| 22. SMBus                                            |     |

| 22.1. Supporting Documents                           |     |

| 22.2. SMBus Configuration                            |     |

| 22.3. SMBus Operation                                |     |

| 22.3.1. Transmitter Vs. Receiver                     |     |

| 22.3.2. Arbitration                                  |     |

| 22.3.3. Clock Low Extension                          |     |

| 22.3.4. SCL Low Timeout                              |     |

| 22.3.5. SCL High (SMBus Free) Timeout                |     |

| 22.4. Using the SMBus                                |     |

| 22.4.1. SMBus Configuration Register                 |     |

| 22.4.2. SMB0CN Control Register                      |     |

| 22.4.3. Data Register                                |     |

| 22.5. SMBus Transfer Modes                           | -   |

| 22.5.1. Write Sequence (Master)                      |     |

| 22.5.2. Read Sequence (Master)                       |     |

| 22.5.3. Write Sequence (Slave)                       |     |

| 22.5.4. Read Sequence (Slave)                        |     |

| 22.6. SMBus Status Decoding                          |     |

| 23. UART0                                            |     |

| 23.1. Baud Rate Generator                            |     |

| 23.2. Data Format                                    |     |

| 23.3. Configuration and Operation                    |     |

| 23.3.1. Data Transmission                            |     |

| 23.3.2. Data Reception                               |     |

| 23.3.3. Multiprocessor Communications                |     |

| 24. Enhanced Serial Peripheral Interface (SPI0)      |     |

| 24.1. Signal Descriptions                            |     |

| 24.1.1. Master Out, Slave In (MOSI)                  |     |

| 24.1.2. Master In, Slave Out (MISO)                  |     |

| 24.1.3. Serial Clock (SCK)                           |     |

| 24.1.4. Slave Select (NSS)                           |     |

| 24.2. SPI0 Master Mode Operation                     |     |

| 24.3. SPI0 Slave Mode Operation                      |     |

| 24.4. SPI0 Interrupt Sources                         |     |

| 24.5. Serial Clock Phase and Polarity                |     |

| 24.6. SPI Special Function Registers                 |     |

| 25. Timers                                           |     |

| 25.1. Timer 0 and Timer 1                            |     |

| 25.1.1. Mode 0: 13-bit Counter/Timer                 |     |

| 25.1.2. Mode 1: 16-bit Counter/Timer                 |     |

| 25.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload | 262 |

# List of Figures

| Figure 1.1. C8051F568-9 and 'F570-5 (40-pin) Block Diagram                         | 17  |

|------------------------------------------------------------------------------------|-----|

| Figure 1.2. C8051F560-7 (32-pin) Block Diagram                                     |     |

| Figure 1.3. C8051F550-7 (24-pin) Block Diagram                                     |     |

| Figure 3.1. QFN-40 Pinout Diagram (Top View)                                       |     |

| Figure 3.2. QFP-32 Pinout Diagram (Top View)                                       |     |

| Figure 3.3. QFN-32 Pinout Diagram (Top View)                                       |     |

|                                                                                    |     |

| Figure 3.4. QFN-24 Pinout Diagram (Top View)<br>Figure 4.1. QFN-40 Package Drawing |     |

| 5 5 5                                                                              |     |

| Figure 4.2. QFN-40 Landing Diagram                                                 |     |

| Figure 4.3. QFP-32 Package Drawing                                                 |     |

| Figure 4.4. QFP-32 Landing Diagram                                                 |     |

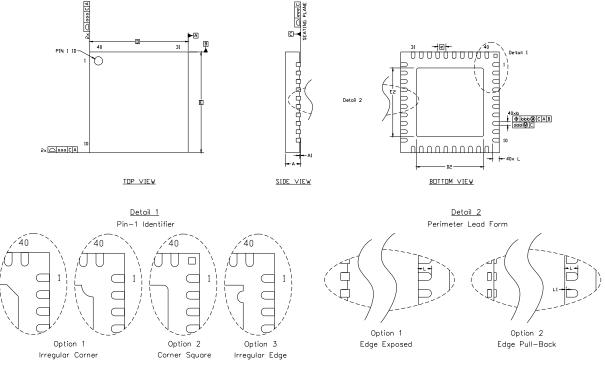

| Figure 4.5. QFN-32 Package Drawing                                                 |     |

| Figure 4.6. QFN-32 Landing Diagram                                                 |     |

| Figure 4.7. QFN-24 Package Drawing                                                 |     |

| Figure 4.8. QFN-24 Landing Diagram                                                 |     |

| Figure 5.1. Minimum VDD Monitor Threshold vs. System Clock Frequency               |     |

| Figure 6.1. ADC0 Functional Block Diagram                                          |     |

| Figure 6.2. ADC0 Tracking Modes                                                    |     |

| Figure 6.3. 12-Bit ADC Tracking Mode Example                                       |     |

| Figure 6.4. 12-Bit ADC Burst Mode Example With Repeat Count Set to 4               |     |

| Figure 6.5. ADC0 Equivalent Input Circuit                                          |     |

| Figure 6.6. ADC Window Compare Example: Right-Justified Data                       |     |

| Figure 6.7. ADC Window Compare Example: Left-Justified Data                        |     |

| Figure 6.8. ADC0 Multiplexer Block Diagram                                         | 65  |

| Figure 6.9. Temperature Sensor Transfer Function                                   | 67  |

| Figure 7.1. Voltage Reference Functional Block Diagram                             | 68  |

| Figure 8.1. Comparator Functional Block Diagram                                    | 70  |

| Figure 8.2. Comparator Hysteresis Plot                                             | 71  |

| Figure 8.3. Comparator Input Multiplexer Block Diagram                             | 76  |

| Figure 9.1. External Capacitors for Voltage Regulator Input/Output—                |     |

| Regulator Enabled                                                                  | 79  |

| Figure 9.2. External Capacitors for Voltage Regulator Input/Output-Regulator Dis   | S-  |

| abled                                                                              |     |

| Figure 10.1. CIP-51 Block Diagram                                                  |     |

| Figure 11.1. C8051F55x/56x/57x Memory Map                                          |     |

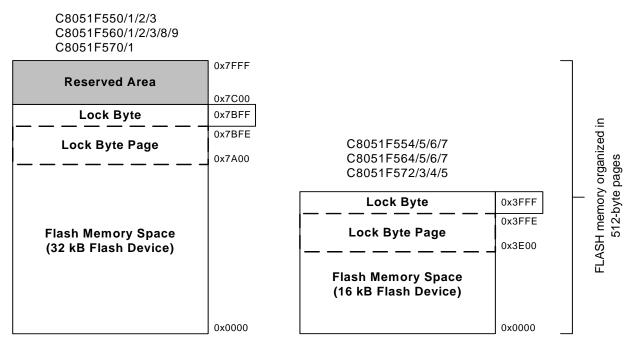

| Figure 11.2. Flash Program Memory Map                                              |     |

| Figure 12.1. SFR Page Stack                                                        |     |

| Figure 12.2. SFR Page Stack While Using SFR Page 0x0 To Access SPI0DAT             |     |

| Figure 12.3. SFR Page Stack After CAN0 Interrupt Occurs                            |     |

| Figure 12.4. SFR Page Stack Upon PCA Interrupt Occurring During a CAN0 ISR .       |     |

| Figure 12.5. SFR Page Stack Upon Return From PCA Interrupt                         |     |

| Figure 12.6. SFR Page Stack Upon Return From CAN0 Interrupt                        |     |

| Figure 14.1. Flash Program Memory Map                                              |     |

|                                                                                    | 121 |

## 4. Package Specifications

## 4.1. QFN-40 Package Specifications

## Figure 4.1. QFN-40 Package Drawing

| Dimension | Min      | Тур      | Max  | Dimension | Min  | Тур  | Max  |

|-----------|----------|----------|------|-----------|------|------|------|

| A         | 0.80     | 0.85     | 0.90 | E2        | 4.00 | 4.10 | 4.20 |

| A1        | 0.00     |          | 0.05 | L         | 0.35 | 0.40 | 0.45 |

| b         | 0.18     | 0.23     | 0.28 | L1        |      |      | 0.10 |

| D         | 6.00 BSC |          |      | aaa       |      |      | 0.10 |

| D2        | 4.00     | 4.10     | 4.20 | bbb       |      |      | 0.10 |

| е         |          | 0.50 BSC |      | ddd       |      |      | 0.05 |

| E         | 6.00 BSC |          |      | eee       |      |      | 0.08 |

#### Table 4.1. QFN-40 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

**3.** This drawing conforms to JEDEC Solid State Outline MO-220, variation VJJD-5, except for features A, D2, and E2 which are toleranced per supplier designation.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

Figure 11.2. Flash Program Memory Map

### 11.1.1. MOVX Instruction and Program Memory

The MOVX instruction in an 8051 device is typically used to access external data memory. On the C8051F55x/56x/57x devices, the MOVX instruction is normally used to read and write on-chip XRAM, but can be re-configured to write and erase on-chip Flash memory space. MOVC instructions are always used to read Flash memory, while MOVX write instructions are used to erase and write Flash. This Flash access feature provides a mechanism for the C8051F55x/56x/57x to update program code and use the program memory space for non-volatile data storage. Refer to Section "14. Flash Memory" on page 124 for further details.

### 11.2. Data Memory

The C8051F55x/56x/57x devices include 2304 bytes of RAM data memory. 256 bytes of this memory is mapped into the internal RAM space of the 8051. The other 2048 bytes of this memory is on-chip "external" memory. The data memory map is shown in Figure 11.1 for reference.

#### 11.2.1. Internal RAM

There are 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory. Figure 11.1 illustrates the data memory organization of the

## Table 12.3. Special Function Registers (Continued)

| SERs are listed in alphabetical order  | All undefined SFR locations are reserved |

|----------------------------------------|------------------------------------------|

| SERS are listed in alphabetical order. | All undernied SFR locations are reserved |

| Register | Address | Description                     | Page |

|----------|---------|---------------------------------|------|

| SMB0CF   | 0xC1    | SMBus0 Configuration            | 224  |

| SMB0CN   | 0xC0    | SMBus0 Control                  | 226  |

| SMB0DAT  | 0xC2    | SMBus0 Data                     | 228  |

| SMOD0    | 0xA9    | UART0 Mode                      | 243  |

| SN0      | 0xF9    | Serial Number 0                 | 91   |

| SN1      | 0xFA    | Serial Number 1                 | 91   |

| SN2      | 0xFB    | Serial Number 2                 | 91   |

| SN3      | 0xFC    | Serial Number 3                 | 91   |

| SP       | 0x81    | Stack Pointer                   | 89   |

| SPI0CFG  | 0xA1    | SPI0 Configuration              | 253  |

| SPI0CKR  | 0xA2    | SPI0 Clock Rate Control         | 255  |

| SPIOCN   | 0xF8    | SPI0 Control                    | 254  |

| SPIODAT  | 0xA3    | SPI0 Data                       | 255  |

| TCON     | 0x88    | Timer/Counter Control           | 265  |

| TH0      | 0x8C    | Timer/Counter 0 High            | 268  |

| TH1      | 0x8D    | Timer/Counter 1 High            | 268  |

| TL0      | 0x8A    | Timer/Counter 0 Low             | 267  |

| TL1      | 0x8B    | Timer/Counter 1 Low             | 267  |

| TMOD     | 0x89    | Timer/Counter Mode              | 266  |

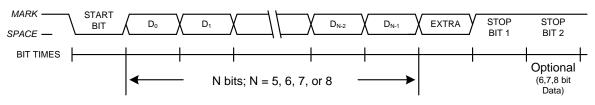

| TMR2CN   | 0xC8    | Timer/Counter 2 Control         | 272  |

| TMR2H    | 0xCD    | Timer/Counter 2 High            | 274  |

| TMR2L    | 0xCC    | Timer/Counter 2 Low             | 274  |

| TMR2RLH  | 0xCB    | Timer/Counter 2 Reload High     | 273  |

| TMR2RLL  | 0xCA    | Timer/Counter 2 Reload Low      | 273  |

| TMR3CN   | 0x91    | Timer/Counter 3 Control         | 278  |

| TMR3H    | 0x95    | Timer/Counter 3 High            | 280  |

| TMR3L    | 0x94    | Timer/Counter 3 Low             | 280  |

| TMR3RLH  | 0x93    | Timer/Counter 3 Reload High     | 279  |

| TMR3RLL  | 0x92    | Timer/Counter 3 Reload Low      | 279  |

| VDM0CN   | 0xFF    | V <sub>DD</sub> Monitor Control | 141  |

| XBR0     | 0xE1    | Port I/O Crossbar Control 0     | 176  |

| XBR1     | 0xE2    | Port I/O Crossbar Control 1     | 177  |

| XBR2     | 0xC7    | Port I/O Crossbar Control 2     | 178  |

/RD

## 17.4. Multiplexed Mode

The External Memory Interface operates only in a Multiplexed mode. In Multiplexed mode, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. In this mode, an external latch (74HC373 or equivalent logic gate) is used to hold the lower 8-bits of the RAM address. The external latch is controlled by the ALE (Address Latch Enable) signal, which is driven by the External Memory Interface logic. An example of a Multiplexed Configuration is shown in Figure 17.1.

In Multiplexed mode, the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the Q outputs reflect the states of the 'D' inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time RD or WR is asserted.

A[15:8] A[15:8] ADDRESS BUS 74HC373 ALE G E ADDRESS/DATA BUS A[7:0] AD[7:0] Q D M  $V_{DD}$ 64 K X 8 SRAM (Optional) 8 F I/O[7:0] CE /WR WE

See Section "17.6.1. Multiplexed Mode" on page 153 for more information.

OE

## SFR Definition 19.2. XBR1: Port I/O Crossbar Register 1

| Bit   | 7   | 6   | 5    | 4   | 3          | 2      | 1        | 0 |

|-------|-----|-----|------|-----|------------|--------|----------|---|

|       | •   | -   | _    | -   | 0          | •      |          |   |

| Name  | T1E | T0E | ECIE | F   | PCA0ME[2:0 | SYSCKE | Reserved |   |

| Туре  | R/W | R/W | R/W  | R/W | R/W        | R/W    | R/W      |   |

| Type  |     |     |      |     |            |        |          | - |

| Reset | 0   | 0   | 0    | 0   | 0          | 0      | 0        | 0 |

|       |     |     |      |     |            |        |          |   |

### SFR Address = 0xE2; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | T1E         | <b>T1 Enable.</b><br>0: T1 unavailable at Port pin.<br>1: T1 routed to Port pin.                                                                                                                                                                                                                                                                                                                                                                                    |

| 6   | TOE         | <b>T0 Enable.</b><br>0: T0 unavailable at Port pin.<br>1: T0 routed to Port pin.                                                                                                                                                                                                                                                                                                                                                                                    |

| 5   | ECIE        | PCA0 External Counter Input Enable.<br>0: ECI unavailable at Port pin.<br>1: ECI routed to Port pin.                                                                                                                                                                                                                                                                                                                                                                |

| 4:2 | PCA0ME[2:0] | <ul> <li>PCA Module I/O Enable Bits.</li> <li>000: All PCA I/O unavailable at Port pins.</li> <li>001: CEX0 routed to Port pin.</li> <li>010: CEX0, CEX1 routed to Port pins.</li> <li>011: CEX0, CEX1, CEX2 routed to Port pins.</li> <li>100: CEX0, CEX1, CEX2, CEX3 routed to Port pins.</li> <li>101: CEX0, CEX1, CEX2, CEX3, CEX4 routed to Port pins.</li> <li>110: CEX0, CEX1, CEX2, CEX3, CEX4, CEX5 routed to Port pins.</li> <li>111: RESERVED</li> </ul> |

| 1   | SYSCKE      | /SYSCLK Output Enable.<br>0: /SYSCLK unavailable at Port pin.<br>1: /SYSCLK output routed to Port pin.                                                                                                                                                                                                                                                                                                                                                              |

| 0   | Reserved    | Always Write to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## 19.6. Special Function Registers for Accessing and Configuring Port I/O

All Port I/O are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable, except for P4 which is only byte addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

Ports 0–3 have a corresponding PnSKIP register which allows its individual Port pins to be assigned to digital functions or skipped by the Crossbar. All Port pins used for analog functions, GPIO, or dedicated digital functions such as the EMIF should have their PnSKIP bit set to 1.

The Port input mode of the I/O pins is defined using the Port Input Mode registers (PnMDIN). Each Port cell can be configured for analog or digital I/O. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is P4, which can only be used for digital I/O.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings.

### SFR Definition 19.12. P0: Port 0

| Bit   | 7       | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---------|-----------------|---|---|---|---|---|---|--|

| Name  | P0[7:0] |                 |   |   |   |   |   |   |  |

| Туре  | R/W     |                 |   |   |   |   |   |   |  |

| Reset | 1       | 1 1 1 1 1 1 1 1 |   |   |   |   |   |   |  |

SFR Address = 0x80; SFR Page = All Pages; Bit-Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P0[7:0] | <b>Port 0 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P0.n Port pin is logic<br>LOW.<br>1: P0.n Port pin is logic<br>HIGH. |

$$multiplier = \frac{20000}{baud_rate} - 1$$

$$prescaler = ln \left[ \frac{SYSCLK}{(multiplier + 1) \times baud_rate \times 200} \right] \times \frac{1}{ln2} - 1$$

$$divider = \frac{SYSCLK}{(2^{(prescaler + 1)} \times (multiplier + 1) \times baud_rate)}$$

In all of these equations, the results must be rounded down to the nearest integer.

The following example shows the steps for calculating the baud rate values for a Master node running at 24 MHz and communicating at 19200 bits/sec. First, calculate the multiplier:

multiplier =

$$\frac{20000}{19200} - 1 = 0.0417 \cong 0$$

Next, calculate the prescaler:

prescaler =

$$\ln \frac{24000000}{(0+1) \times 19200 \times 200} \times \frac{1}{\ln 2} - 1 = 1.644 \cong 1$$

Finally, calculate the divider:

divider =

$$\frac{24000000}{2^{(1+1)} \times (0+1) \times 19200}$$

= 312.5  $\cong$  312

These values lead to the following baud rate:

baud\_rate =

$$\frac{24000000}{2^{(1+1)} \times (0+1) \times 312} \cong 19230.77$$

The following code programs the interface in Master mode, using the Enhanced Checksum and enables the interface to operate at 19230 bits/sec using a 24 MHz system clock.

| LINOCF = 0x80;<br>LINOCF  = 0x40;                                                                                                                                                    | <pre>// Activate the interface // Set the node as a Master</pre>                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>LINOADR = 0x0D;<br/>// Initialize the register (prescaler,<br/>LINODAT = ( 0x01 &lt;&lt; 6 ) + ( 0x00 &lt;&lt; 1<br/>LINOADR = 0x0C;<br/>LINODAT = (unsigned char)_0x138;</pre> | ) + ( ( 0x138 & 0x0100 ) >> 8 );<br>// Point to the LINODIV register                                                                                   |

| LIN0ADR = $0 \times 0B;$<br>LIN0DAT  = $0 \times 80;$<br>LIN0ADR = $0 \times 08;$<br>LIN0DAT = $0 \times 0C;$                                                                        | <pre>// Point to the LINOSIZE register // Initialize the checksum as Enhanced // Point to LINOCTRL register // Reset any error and the interrupt</pre> |

Table 20.2 includes the configuration values required for the typical system clocks and baud rates:

## 20.7. LIN Registers

The following Special Function Registers (SFRs) and indirect registers are available for the LIN controller.

#### 20.7.1. LIN Direct Access SFR Registers Definitions

## SFR Definition 20.1. LIN0ADR: LIN0 Indirect Address Register

| Bit   | 7            | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------------|-----------------|---|---|---|---|---|---|--|--|

| Name  | LIN0ADR[7:0] |                 |   |   |   |   |   |   |  |  |

| Туре  | R/W          |                 |   |   |   |   |   |   |  |  |

| Reset | 0            | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |

SFR Address = 0xD3; SFR Page = 0x00

| Bit | Name         | Function                                                                                                                                                                                                                                                |

|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | LIN0ADR[7:0] | LIN Indirect Address Register Bits.                                                                                                                                                                                                                     |

|     |              | This register hold an 8-bit address used to indirectly access the LIN0 core registers.<br>Table 20.4 lists the LIN0 core registers and their indirect addresses. Reads and<br>writes to LIN0DAT will target the register indicated by the LIN0ADR bits. |

## SFR Definition 20.2. LIN0DAT: LIN0 Indirect Data Register

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------------|---|---|---|---|---|---|---|--|

| Name  | LINODAT[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W          |   |   |   |   |   |   |   |  |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xD2; SFR Page = 0x00

| Bit | Name         | Function                                                                                                |

|-----|--------------|---------------------------------------------------------------------------------------------------------|

| 7:0 | LIN0DAT[7:0] | LIN Indirect Data Register Bits.                                                                        |

|     |              | When this register is read, it will read the contents of the LIN0 core register pointed to by LIN0ADR.  |

|     |              | When this register is written, it will write the value to the LIN0 core register pointed to by LIN0ADR. |

## LIN Register Definition 20.4. LIN0DTn: LIN0 Data Byte n

| Bit  | 7                                  | 6             | 5                                                                          | 4 | 3          | 2           | 1           | 0           |  |  |

|------|------------------------------------|---------------|----------------------------------------------------------------------------|---|------------|-------------|-------------|-------------|--|--|

| Nam  | e                                  | DATAn[7:0]    |                                                                            |   |            |             |             |             |  |  |

| Туре | 9                                  | R/W           |                                                                            |   |            |             |             |             |  |  |

| Rese | et 0                               | 0             | 0                                                                          | 0 | 0          | 0           | 0           | 0           |  |  |

|      | ct Address: LIN<br>0T6 = 0x05, LIN |               | ,                                                                          | , | DT3 = 0x02 | , LIN0DT4 = | 0x03, LIN0I | DT5 = 0x04, |  |  |

| Bit  | Name                               | Name Function |                                                                            |   |            |             |             |             |  |  |

| 7:0  | DATAn[7:0]                         | LIN Data E    | LIN Data Byte n.                                                           |   |            |             |             |             |  |  |

|      |                                    | Serial Data   | Serial Data Byte that is received or transmitted across the LIN interface. |   |            |             |             |             |  |  |

## LIN Register Definition 20.7. LIN0ERR: LIN0 Error Register

| Bit   | 7 | 6 | 5 | 4     | 3    | 2    | 1   | 0      |

|-------|---|---|---|-------|------|------|-----|--------|

| Name  |   |   |   | SYNCH | PRTY | TOUT | CHK | BITERR |

| Туре  | R | R | R | R     | R    | R    | R   | R      |

| Reset | 0 | 0 | 0 | 0     | 0    | 0    | 0   | 0      |

Indirect Address = 0x0A

| Bit | Name   | Function                                                                                                                                                  |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Unused | Read = 000b; Write = Don't Care                                                                                                                           |

| 4   | SYNCH  | Synchronization Error Bit (slave mode only).                                                                                                              |

|     |        | 0: No error with the SYNCH FIELD has been detected.                                                                                                       |

|     |        | 1: Edges of the SYNCH FIELD are outside of the maximum tolerance.                                                                                         |

| 3   | PRTY   | Parity Error Bit (slave mode only).                                                                                                                       |

|     |        | 0: No parity error has been detected.                                                                                                                     |

|     |        | 1: A parity error has been detected.                                                                                                                      |

| 2   | TOUT   | Timeout Error Bit.                                                                                                                                        |

|     |        | 0: A timeout error has not been detected.                                                                                                                 |

|     |        | 1: A timeout error has been detected. This error is detected whenever one of the fol-<br>lowing conditions is met:                                        |

|     |        | • The master is expecting data from a slave and the slave does not respond.                                                                               |

|     |        | <ul> <li>The slave is expecting data but no data is transmitted on the bus.</li> </ul>                                                                    |

|     |        | <ul> <li>A frame is not finished within the maximum frame length.</li> <li>The application does not set the DTACK bit (LIN0CTRL.4) or STOP bit</li> </ul> |

|     |        | (LINOCTRL.7) until the end of the reception of the first byte after the identifier.                                                                       |

| 1   | СНК    | Checksum Error Bit.                                                                                                                                       |

|     |        | 0: Checksum error has not been detected.                                                                                                                  |

|     |        | 1: Checksum error has been detected.                                                                                                                      |

| 0   | BITERR | Bit Transmission Error Bit.                                                                                                                               |

|     |        | 0: No error in transmission has been detected.                                                                                                            |

|     |        | 1: The bit value monitored during transmission is different than the bit value sent.                                                                      |

| Name                                | SFR Name<br>(High)                                                                                                                                                                                                                                                     | SFR                                                                                                                                                                                                                            | SFR Name                                                                                                                                                                                                                                                           | SFR                                                                                                                                                                                                                                                                                                            | 16-bit                                                                                                                                                                                                                                                                                                                                       | Deest                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | (ingn)                                                                                                                                                                                                                                                                 | سلمام ۸                                                                                                                                                                                                                        | (Low)                                                                                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                              | Reset<br>Value                                                                                                                                                                                                                                                                                                                                                                                             |

|                                     | ,                                                                                                                                                                                                                                                                      | Addr.                                                                                                                                                                                                                          | (LOW)                                                                                                                                                                                                                                                              | Addr.                                                                                                                                                                                                                                                                                                          | SFR                                                                                                                                                                                                                                                                                                                                          | Value                                                                                                                                                                                                                                                                                                                                                                                                      |

| IF2 Data A 2                        | CAN0IF2DA2H                                                                                                                                                                                                                                                            | 0xFB                                                                                                                                                                                                                           | CAN0IF2DA2L                                                                                                                                                                                                                                                        | 0xFA                                                                                                                                                                                                                                                                                                           | CAN0IF2DA2                                                                                                                                                                                                                                                                                                                                   | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| IF2 Data B 1                        | CAN0IF2DB1H                                                                                                                                                                                                                                                            | 0xFD                                                                                                                                                                                                                           | CAN0IF2DB1L                                                                                                                                                                                                                                                        | 0xFC                                                                                                                                                                                                                                                                                                           | CAN0IF2DB1                                                                                                                                                                                                                                                                                                                                   | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| IF2 Data B 2                        | CAN0IF2DB2H                                                                                                                                                                                                                                                            | 0xFF                                                                                                                                                                                                                           | CAN0IF2DB2L                                                                                                                                                                                                                                                        | 0xFE                                                                                                                                                                                                                                                                                                           | CAN0IF2DB2                                                                                                                                                                                                                                                                                                                                   | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| Transmission Request 1 <sup>1</sup> | CAN0TR1H                                                                                                                                                                                                                                                               | 0xA3                                                                                                                                                                                                                           | CAN0TR1L                                                                                                                                                                                                                                                           | 0xA2                                                                                                                                                                                                                                                                                                           | CAN0TR1                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| Transmission Request 2 <sup>1</sup> | CAN0TR2H                                                                                                                                                                                                                                                               | 0xA5                                                                                                                                                                                                                           | CAN0TR2L                                                                                                                                                                                                                                                           | 0xA4                                                                                                                                                                                                                                                                                                           | CAN0TR2                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| New Data 1 <sup>1</sup>             | CAN0ND1H                                                                                                                                                                                                                                                               | 0xAB                                                                                                                                                                                                                           | CAN0ND1L                                                                                                                                                                                                                                                           | 0xAA                                                                                                                                                                                                                                                                                                           | CAN0ND1                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| New Data 2 <sup>1</sup>             | CAN0ND2H                                                                                                                                                                                                                                                               | 0xAD                                                                                                                                                                                                                           | CAN0ND2L                                                                                                                                                                                                                                                           | 0xAC                                                                                                                                                                                                                                                                                                           | CAN0ND2                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| Interrupt Pending 1 <sup>1</sup>    | CAN0IP1H                                                                                                                                                                                                                                                               | 0xAF                                                                                                                                                                                                                           | CAN0IP1L                                                                                                                                                                                                                                                           | 0xAE                                                                                                                                                                                                                                                                                                           | CAN0IP1                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| Interrupt Pending 2 <sup>1</sup>    | CAN0IP2H                                                                                                                                                                                                                                                               | 0xB3                                                                                                                                                                                                                           | CAN0IP2L                                                                                                                                                                                                                                                           | 0xB2                                                                                                                                                                                                                                                                                                           | CAN0IP2                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| Message Valid 1 <sup>1</sup>        | CAN0MV1H                                                                                                                                                                                                                                                               | 0xBB                                                                                                                                                                                                                           | CAN0MV1L                                                                                                                                                                                                                                                           | 0xBA                                                                                                                                                                                                                                                                                                           | CAN0MV1                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

| Message Valid 2 <sup>1</sup>        | CAN0MV2H                                                                                                                                                                                                                                                               | 0xBD                                                                                                                                                                                                                           | CAN0MV2L                                                                                                                                                                                                                                                           | 0xBC                                                                                                                                                                                                                                                                                                           | CAN0MV2                                                                                                                                                                                                                                                                                                                                      | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                     | F2 Data B 1<br>F2 Data B 2<br>Fransmission Request 1 <sup>1</sup><br>Fransmission Request 2 <sup>1</sup><br>New Data 1 <sup>1</sup><br>New Data 2 <sup>1</sup><br>Interrupt Pending 1 <sup>1</sup><br>Interrupt Pending 2 <sup>1</sup><br>Message Valid 1 <sup>1</sup> | F2 Data B 1CANOIF2DB1HF2 Data B 2CANOIF2DB2HFransmission Request 11CANOTR1HFransmission Request 21CANOTR2HNew Data 11CANOND1HNew Data 21CANOID2Hnterrupt Pending 11CANOIP1Hnterrupt Pending 21CANOIP2HMessage Valid 11CANOMV1H | F2 Data B 1CANOIF2DB1H0xFDF2 Data B 2CANOIF2DB2H0xFFTransmission Request 11CANOTR1H0xA3Transmission Request 21CANOTR2H0xA5New Data 11CANOND1H0xA8New Data 21CANOID1H0xADnterrupt Pending 11CANOIP1H0xAFnterrupt Pending 21CANOIP2H0xB3Message Valid 11CANOMV1H0xBB | F2 Data B 1CANOIF2DB1H0xFDCANOIF2DB1LF2 Data B 2CANOIF2DB2H0xFFCANOIF2DB2LTransmission Request 11CANOTR1H0xA3CANOTR1LTransmission Request 21CANOTR2H0xA5CANOTR2LNew Data 11CANOND1H0xABCANOND1LNew Data 21CANOIP1H0xAFCANOND2LInterrupt Pending 11CANOIP1H0xAFCANOIP1LInterrupt Pending 21CANOIP2H0xBBCANOIV1L | F2 Data B 1CANOIF2DB1H0xFDCANOIF2DB1L0xFCF2 Data B 2CANOIF2DB2H0xFFCANOIF2DB2L0xFETransmission Request 11CANOTR1H0xA3CANOTR1L0xA2Transmission Request 21CANOTR2H0xA5CANOTR2L0xA4New Data 11CANOND1H0xABCANOND1L0xAANew Data 21CANOIP1H0xADCANOND2L0xACnterrupt Pending 11CANOIP1H0xAFCANOIP1L0xAEnterrupt Pending 21CANOIV1H0xBBCANOIV1L0xBA | F2 Data B 1CANOIF2DB1H0xFDCANOIF2DB1L0xFCCANOIF2DB1F2 Data B 2CANOIF2DB2H0xFFCANOIF2DB2L0xFECANOIF2DB2Transmission Request 11CANOTR1H0xA3CANOTR1L0xA2CANOTR1Transmission Request 21CANOTR2H0xA5CANOTR2L0xA4CANOTR2New Data 11CANOND1H0xA8CANOND1L0xAACANOND1New Data 21CANOND2H0xAFCANOIP2L0xACCANOND2nterrupt Pending 11CANOIP1H0xAFCANOIP1L0xAECANOIP1nterrupt Pending 21CANOIP2H0xB3CANOIV1L0xBACANOMV1 |

## Table 21.2. Standard CAN Registers and Reset Values

Notes:

1. Read-only register.

2. Write-enabled by CCE.

3. The reset value of CAN0TST could also be r0000000b, where r signifies the value of the CAN RX pin.

4. Write-enabled by Test.

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 22.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                 | Minimum SDA Setup Time                                                                                                                                                                                                                                                                                           | Minimum SDA Hold Time |  |  |  |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|--|--|

| 0                       | T <sub>low</sub> – 4 system clocks<br>or<br>1 system clock + s/w delay <sup>*</sup>                                                                                                                                                                                                                              | 3 system clocks       |  |  |  |  |  |  |

| 1                       | 11 system clocks                                                                                                                                                                                                                                                                                                 | 12 system clocks      |  |  |  |  |  |  |

| software a<br>ACK is wi | *Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. When using software acknowledgement, the s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero. |                       |  |  |  |  |  |  |

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "22.3.4. SCL Low Timeout" on page 220). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 22.4).

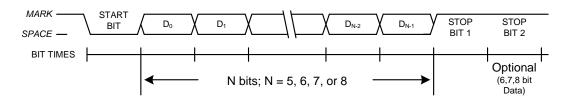

## 23.2. Data Format

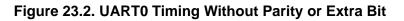

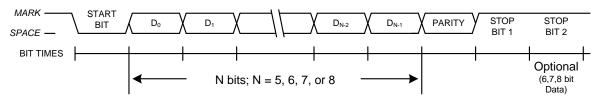

UART0 has a number of available options for data formatting. Data transfers begin with a start bit (logic low), followed by the data bits (sent LSB-first), a parity or extra bit (if selected), and end with one or two stop bits (logic high). The data length is variable between 5 and 8 bits. A parity bit can be appended to the data, and automatically generated and detected by hardware for even, odd, mark, or space parity. The stop bit length is selectable between 1 and 2 bit times, and a multi-processor communication mode is available for implementing networked UART buses. All of the data formatting options can be configured using the SMOD0 register, shown in SFR Definition 23.2. Figure 23.2 shows the timing for a UART0 transaction without parity or an extra bit enabled. Figure 23.3 shows the timing for a UART0 transaction with parity enabled (PE0 = 1). Figure 23.4 is an example of a UART0 transaction when the extra bit is enabled (XBE0 = 1). Note that the extra bit feature is not available when parity is enabled, and the second stop bit is only an option for data lengths of 6, 7, or 8 bits.

Figure 23.3. UART0 Timing With Parity

Figure 23.4. UART0 Timing With Extra Bit

## SFR Definition 24.1. SPI0CFG: SPI0 Configuration

| Bit   | 7      | 6     | 5     | 4     | 3      | 2     | 1    | 0     |

|-------|--------|-------|-------|-------|--------|-------|------|-------|

| Name  | SPIBSY | MSTEN | СКРНА | CKPOL | SLVSEL | NSSIN | SRMT | RXBMT |

| Туре  | R      | R/W   | R/W   | R/W   | R      | R     | R    | R     |

| Reset | 0      | 0     | 0     | 0     | 0      | 1     | 1    | 1     |

## SFR Address = 0xA1; SFR Page = 0x00

| Bit   | Name   | Function                                                                                                                                                                                 |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | SPIBSY | SPI Busy.                                                                                                                                                                                |

|       |        | This bit is set to logic 1 when a SPI transfer is in progress (master or slave mode).                                                                                                    |

| 6     | MSTEN  | Master Mode Enable.                                                                                                                                                                      |

|       |        | 0: Disable master mode. Operate in slave mode.                                                                                                                                           |

|       |        | 1: Enable master mode. Operate as a master.                                                                                                                                              |

| 5     | СКРНА  | SPI0 Clock Phase.                                                                                                                                                                        |

|       |        | 0: Data centered on first edge of SCK period.*                                                                                                                                           |

|       |        | 1: Data centered on second edge of SCK period.*                                                                                                                                          |

| 4     | CKPOL  | SPI0 Clock Polarity.                                                                                                                                                                     |

|       |        | 0: SCK line low in idle state.                                                                                                                                                           |

|       |        | 1: SCK line high in idle state.                                                                                                                                                          |

| 3     | SLVSEL | Slave Selected Flag.                                                                                                                                                                     |

|       |        | This bit is set to logic 1 whenever the NSS pin is low indicating SPI0 is the selected                                                                                                   |

|       |        | slave. It is cleared to logic 0 when NSS is high (slave not selected). This bit does not indicate the instantaneous value at the NSS pin, but rather a de-glitched ver-                  |

|       |        | sion of the pin input.                                                                                                                                                                   |

| 2     | NSSIN  | NSS Instantaneous Pin Input.                                                                                                                                                             |

|       |        | This bit mimics the instantaneous value that is present on the NSS port pin at the                                                                                                       |

|       |        | time that the register is read. This input is not de-glitched.                                                                                                                           |

| 1     | SRMT   | Shift Register Empty (valid in slave mode only).                                                                                                                                         |

|       |        | This bit will be set to logic 1 when all data has been transferred in/out of the shift                                                                                                   |

|       |        | register, and there is no new information available to read from the transmit buffer<br>or write to the receive buffer. It returns to logic 0 when a data byte is transferred to         |

|       |        | the shift register from the transmit buffer or by a transition on SCK. SRMT = 1 when                                                                                                     |

|       |        | in Master Mode.                                                                                                                                                                          |

| 0     | RXBMT  | Receive Buffer Empty (valid in slave mode only).                                                                                                                                         |

|       |        | This bit will be set to logic 1 when the receive buffer has been read and contains no                                                                                                    |

|       |        | new information. If there is new information available in the receive buffer that has                                                                                                    |

|       | · · ·  | not been read, this bit will return to logic 0. RXBMT = 1 when in Master Mode.                                                                                                           |

| Note: |        | data on MOSI is sampled in the center of each data bit. In master mode, data on MISO is<br>/SCLK before the end of each data bit, to provide maximum settling time for the slave device. |

|       |        | for timing parameters.                                                                                                                                                                   |

| I     |        |                                                                                                                                                                                          |

## SFR Definition 25.3. TMOD: Timer Mode