Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 25x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f563-im |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 21.2.2. Magagag Object Interface Registers           | 211 |

|------------------------------------------------------|-----|

| 21.2.2. Message Object Interface Registers           |     |

| 21.2.3. Message Handler Registers                    |     |

| 21.2.4. CAN Register Assignment                      |     |

| 22. SMBus                                            |     |

| 22.1. Supporting Documents                           |     |

| 22.2. SMBus Configuration                            |     |

| 22.3. SMBus Operation                                |     |

| 22.3.1. Transmitter Vs. Receiver                     |     |

| 22.3.2. Arbitration                                  |     |

| 22.3.3. Clock Low Extension                          |     |

| 22.3.4. SCL Low Timeout                              |     |

| 22.3.5. SCL High (SMBus Free) Timeout                |     |

| 22.4. Using the SMBus                                |     |

| 22.4.1. SMBus Configuration Register                 |     |

| 22.4.2. SMB0CN Control Register                      |     |

| 22.4.3. Data Register                                |     |

| 22.5. SMBus Transfer Modes                           | -   |

| 22.5.1. Write Sequence (Master)                      |     |

| 22.5.2. Read Sequence (Master)                       |     |

| 22.5.3. Write Sequence (Slave)                       |     |

| 22.5.4. Read Sequence (Slave)                        |     |

| 22.6. SMBus Status Decoding                          |     |

| 23. UART0                                            |     |

| 23.1. Baud Rate Generator                            |     |

| 23.2. Data Format                                    |     |

| 23.3. Configuration and Operation                    |     |

| 23.3.1. Data Transmission                            |     |

| 23.3.2. Data Reception                               |     |

| 23.3.3. Multiprocessor Communications                |     |

| 24. Enhanced Serial Peripheral Interface (SPI0)      |     |

| 24.1. Signal Descriptions                            |     |

| 24.1.1. Master Out, Slave In (MOSI)                  |     |

| 24.1.2. Master In, Slave Out (MISO)                  |     |

| 24.1.3. Serial Clock (SCK)                           |     |

| 24.1.4. Slave Select (NSS)                           |     |

| 24.2. SPI0 Master Mode Operation                     |     |

| 24.3. SPI0 Slave Mode Operation                      |     |

| 24.4. SPI0 Interrupt Sources                         |     |

| 24.5. Serial Clock Phase and Polarity                |     |

| 24.6. SPI Special Function Registers                 |     |

| 25. Timers                                           |     |

| 25.1. Timer 0 and Timer 1                            |     |

| 25.1.1. Mode 0: 13-bit Counter/Timer                 |     |

| 25.1.2. Mode 1: 16-bit Counter/Timer                 |     |

| 25.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload | 262 |

# 3. Pin Definitions

| Name   | Pin                | Pin                | Pin                | Туре          | Description                                                                 |

|--------|--------------------|--------------------|--------------------|---------------|-----------------------------------------------------------------------------|

|        | 40-pin<br>packages | 32-pin<br>packages | 24-pin<br>packages |               |                                                                             |

| VDD    | 4                  | 4                  | 3                  |               | Digital Supply Voltage. Must be connected.                                  |

| GND    | 6                  | 6                  | 4                  |               | Digital Ground. Must be connected.                                          |

| VDDA   | 5                  | 5                  | —                  |               | Analog Supply Voltage. Must be connected.                                   |

| GNDA   | 7                  | 7                  | 5                  |               | Analog Ground. Must be connected.                                           |

| VREGIN | 3                  | 3                  | 2                  |               | Voltage Regulator Input                                                     |

| VIO    | 2                  | 2                  | 1                  |               | Port I/O Supply Voltage. Must be connected.                                 |

| RST/   | 10                 | 10                 | 8                  | D I/O         | Device Reset. Open-drain output of internal POR or V <sub>DD</sub> Monitor. |

| C2CK   |                    |                    |                    | D I/O         | Clock signal for the C2 Debug Interface.                                    |

| P4.0/  | 9                  | _                  | —                  | D I/O or A In | Port 4.0. See SFR Definition 19.28.                                         |

| C2D    |                    |                    |                    | D I/O         | Bi-directional data signal for the C2 Debug Interface.                      |

| P3.0/  |                    | 9                  | _                  | D I/O or A In | Port 3.0. See SFR Definition 19.24.                                         |

| C2D    |                    |                    |                    | D I/O         | Bi-directional data signal for the C2 Debug Interface.                      |

| P2.1/  |                    | _                  | 7                  | D I/O or A In | Port 2.1. See SFR Definition 19.20.                                         |

| C2D    |                    |                    |                    | D I/O         | Bi-directional data signal for the C2 Debug Interface.                      |

| P0.0   | 8                  | 8                  | 6                  | D I/O or A In | Port 0.0. See SFR Definition 19.12.                                         |

| P0.1   | 1                  | 1                  | 24                 | D I/O or A In | Port 0.1                                                                    |

| P0.2   | 40                 | 32                 | 23                 | D I/O or A In | Port 0.2                                                                    |

| P0.3   | 39                 | 31                 | 22                 | D I/O or A In | Port 0.3                                                                    |

| P0.4   | 38                 | 30                 | 21                 | D I/O or A In | Port 0.4                                                                    |

| P0.5   | 37                 | 29                 | 20                 | D I/O or A In | Port 0.5                                                                    |

| P0.6   | 36                 | 28                 | 19                 | D I/O or A In | Port 0.6                                                                    |

| P0.7   | 35                 | 27                 | 18                 | D I/O or A In | Port 0.7                                                                    |

Table 3.1. Pin Definitions for the C8051F55x/56x/57x

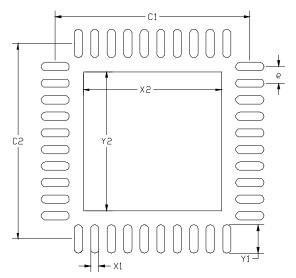

Figure 4.2. QFN-40 Landing Diagram

### Table 4.2. QFN-40 Landing Diagram Dimensions

| Dimension | Min       | Мах      |  | Dimension | Min  | Max  |

|-----------|-----------|----------|--|-----------|------|------|

| C1        | 5.80 5.90 |          |  | X2        | 4.10 | 4.20 |

| C2        | 5.80      | 5.90     |  | Y1        | 0.75 | 0.85 |

| е         | 0.50      | 0.50 BSC |  |           | 4.10 | 4.20 |

| X1        | 0.15      | 0.25     |  |           |      |      |

### Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimension and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on the IPC-SM-7351 guidelines.

- **4.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Solder Mask Design

5. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Stencil Design

- 6. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 7. The stencil thickness should be 0.125 mm (5 mils).

- 8. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- 9. A 4x4 array of 0.80 mm square openings on a 1.05 mm pitch should be used for the center ground pad.

#### Card Assembly

- **10.** A No-Clean, Type-3 solder paste is recommended.

- **11.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### **Table 5.4. Reset Electrical Characteristics**

-40 to +125 °C unless otherwise specified.

| Parameter                                              | Conditions                                                                            | Min                   | Тур  | Max                   | Units |

|--------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| RST Output Low Voltage                                 | VIO = 5 V; IOL = 70 µA                                                                |                       | _    | 40                    | mV    |

| RST Input High Voltage                                 |                                                                                       | 0.7 x V <sub>IO</sub> |      | —                     |       |

| RST Input Low Voltage                                  |                                                                                       | —                     |      | 0.3 x V <sub>IO</sub> |       |

| RST Input Pullup Current                               | $\overline{\text{RST}}$ = 0.0 V, VIO = 5 V                                            |                       | 49   | 115                   | μA    |

| $V_{DD}$ RST Threshold ( $V_{RST-LOW}$ )               |                                                                                       | 1.65                  | 1.75 | 1.80                  | V     |

| V <sub>DD</sub> RST Threshold (V <sub>RST-HIGH</sub> ) |                                                                                       | 2.25                  | 2.30 | 2.45                  | V     |

| V <sub>REGIN</sub> Ramp Time for Power On              | V <sub>REGIN</sub> Ramp 0–1.8 V                                                       | _                     |      | 1                     | ms    |

|                                                        | Time from last system clock rising edge to reset initiation                           |                       |      |                       |       |

| Missing Clock Detector Timeout                         | V <sub>DD</sub> = 2.1 V                                                               | 200                   | 340  | 600                   | μs    |

|                                                        | V <sub>DD</sub> = 2.5 V                                                               | 200                   | 250  | 600                   |       |

| Reset Time Delay                                       | Delay between release of<br>any reset source and code<br>execution at location 0x0000 |                       | 155  | 175                   | μs    |

| Minimum RST Low Time to<br>Generate a System Reset     |                                                                                       | 6                     | _    | —                     | μs    |

| V <sub>DD</sub> Monitor Turn-on Time                   |                                                                                       | _                     | 60   | 100                   | μs    |

| V <sub>DD</sub> Monitor Supply Current                 |                                                                                       |                       | 1    | 2                     | μA    |

### **Table 5.5. Flash Electrical Characteristics**

$V_{DD}$  = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter                                                                                                                                                                 | Conditions                                    | Min                                | Тур                | Max          | Units       |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------|--------------------|--------------|-------------|--|--|--|

| Flash Size                                                                                                                                                                | C8051F550-3, 'F560-3,<br>'F568-9, and 'F570-1 | :                                  | 32768 <sup>1</sup> |              |             |  |  |  |

|                                                                                                                                                                           | C8051F554-7, 'F564-7, and<br>'F572-5          | 16384                              |                    |              | Bytes       |  |  |  |

| Endurance                                                                                                                                                                 |                                               | 20 k                               | 150 k              |              | Erase/Write |  |  |  |

| Retention                                                                                                                                                                 | 125 °C                                        | 10                                 |                    |              | Years       |  |  |  |

| Erase Cycle Time                                                                                                                                                          | 25 MHz System Clock                           | 28                                 | 30                 | 45           | ms          |  |  |  |

| Write Cycle Time                                                                                                                                                          | 25 MHz System Clock                           | 79                                 | 84                 | 125          | μs          |  |  |  |

| V <sub>DD</sub>                                                                                                                                                           | Write/Erase operations                        | V <sub>RST-HIGH</sub> <sup>2</sup> | _                  | —            | V           |  |  |  |

| Temperature during<br>Programming Opera-<br>tions                                                                                                                         | –I Devices<br>–A Devices                      | 0<br>-40                           |                    | +125<br>+125 | °C          |  |  |  |

| <ol> <li>On the 32 kB Flash devices, 1024 bytes at addresses 0x7C00 to 0x7FFF are reserved.</li> <li>See Table 5.4 for the V<sub>RST-HIGH</sub> specification.</li> </ol> |                                               |                                    |                    |              |             |  |  |  |

# Gain Register Definition 6.3. ADC0GNA: ADC0 Additional Selectable Gain

| Bit     | 7             | 6            | 5        | 4        | 3        | 2        | 1        | 0       |  |

|---------|---------------|--------------|----------|----------|----------|----------|----------|---------|--|

| Nam     | e Reserved    | Reserved     | Reserved | Reserved | Reserved | Reserved | Reserved | GAINADD |  |

| Туре    | W             | W            | W        | W        | W        | W        | W        | W       |  |

| Rese    | <b>t</b> 0    | 0            | 0        | 0        | 0        | 0        | 0        | 1       |  |

| Indired | t Address = 0 | x08;         |          |          |          |          |          |         |  |

| Bit     | Name          | Function     |          |          |          |          |          |         |  |

| 7:1     | Reserved      | Must Write ( | 000000b. |          |          |          |          |         |  |

| 7:1  | Reserved                                                                                             | Must Write 000000b.                                                                            |  |  |  |  |  |  |  |

|------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 0    | GAINADD                                                                                              | ADC0 Additional Gain Bit.                                                                      |  |  |  |  |  |  |  |

|      |                                                                                                      | Setting this bit add 1/64 (0.016) gain to the gain value in the ADC0GNH and ADC0GNL registers. |  |  |  |  |  |  |  |

| Note | Note: This register is accessed indirectly; See Section 6.3.2 for details for writing this register. |                                                                                                |  |  |  |  |  |  |  |

## SFR Definition 6.7. ADC0CN: ADC0 Control

| Bit   | 7             | 6                                                                                                                                                                                                                       | 5                            | 4                            | 3                            | 2                      |               | 1                                     | 0          |  |

|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|------------------------|---------------|---------------------------------------|------------|--|

| Nam   | e AD0EN       | BURSTEN                                                                                                                                                                                                                 | AD0INT                       | AD0BUSY                      | ADOWINT                      | AD0LJS                 | ST            | AD0CM[1:0]                            |            |  |

| Туре  | e R/W         | R/W                                                                                                                                                                                                                     | R/W                          | R/W                          | R/W                          | R/W                    |               | R/W                                   |            |  |

| Rese  | et 0          | 0                                                                                                                                                                                                                       | 0                            | 0                            | 0                            | 0                      |               | 0                                     | 0          |  |

| SFR A | Address = 0xE | 8; SFR Page                                                                                                                                                                                                             | = 0x00; Bit                  | -Addressable                 | e                            |                        |               |                                       |            |  |

| Bit   | Name          | Function                                                                                                                                                                                                                |                              |                              |                              |                        |               |                                       |            |  |

| 7     | AD0EN         | ADC0 Enab                                                                                                                                                                                                               | le Bit.                      |                              |                              |                        |               |                                       |            |  |

|       |               | 0: ADC0 Dis<br>1: ADC0 Ena                                                                                                                                                                                              |                              |                              |                              |                        | versio        | ons.                                  |            |  |

| 6     | BURSTEN       | ADC0 Burst                                                                                                                                                                                                              | Mode Ena                     | ble Bit.                     |                              |                        |               |                                       |            |  |

|       |               | 0: Burst Moo<br>1: Burst Moo                                                                                                                                                                                            |                              |                              |                              |                        |               |                                       |            |  |

| 5     | AD0INT        | ADC0 Conv                                                                                                                                                                                                               | ersion Con                   | nplete Interr                | upt Flag.                    |                        |               |                                       |            |  |

|       |               | 0: ADC0 has<br>1: ADC0 has                                                                                                                                                                                              |                              |                              |                              | nce AD0I               | NT w          | vas last clea                         | ared.      |  |

| 4     | AD0BUSY       | ADC0 Busy                                                                                                                                                                                                               | Bit.                         | Read:                        |                              |                        | Writ          | e:                                    |            |  |

|       |               |                                                                                                                                                                                                                         |                              | in prog                      | C0 conversio                 |                        | 1: In         | o Effect.<br>itiates ADC<br>if AD0CM[ |            |  |

| 3     | AD0WINT       | ADC0 Wind                                                                                                                                                                                                               | ow Compa                     | re Interrupt                 | Flag.                        |                        |               |                                       |            |  |

|       |               | This bit mus<br>0: ADC0 Wir<br>cleared.<br>1: ADC0 Wir                                                                                                                                                                  | ndow Compa                   | arison Data                  | match has no                 |                        | ed sir        | nce this flag                         | g was last |  |

| 2     | AD0LJST       | ADC0 Left J                                                                                                                                                                                                             | ustify Sele                  | ct Bit.                      |                              |                        |               |                                       |            |  |

|       |               | 0: Data in ADC0H:ADC0L registers is right-justified<br>1: Data in ADC0H:ADC0L registers is left-justified. This option should not be used<br>with a repeat count greater than 1 (when AD0RPT[1:0] is 01b, 10b, or 11b). |                              |                              |                              |                        |               |                                       |            |  |

| 1:0   | AD0CM[1:0]    | ADC0 Start                                                                                                                                                                                                              | of Convers                   | ion Mode S                   | elect.                       |                        |               |                                       |            |  |

|       |               | 00: ADC0 st<br>01: ADC0 st<br>10: ADC0 st<br>11: ADC0 st                                                                                                                                                                | art-of-conve<br>art-of-conve | rsion source<br>rsion source | is overflow<br>is rising edg | of Timer<br>ge of exte | 1.<br>ernal ( |                                       |            |  |

# SFR Definition 8.2. CPT0MD: Comparator0 Mode Selection

| Bit   | 7 | 6 | 5      | 4      | 3 | 2 | 1          | 0 |

|-------|---|---|--------|--------|---|---|------------|---|

| Name  |   |   | CP0RIE | CP0FIE |   |   | CP0MD[1:0] |   |

| Туре  | R | R | R/W    | R/W    | R | R | R/W        |   |

| Reset | 0 | 0 | 0      | 0      | 0 | 0 | 1          | 0 |

### SFR Address = 0x9B; SFR Page = 0x00

| Bit | Name       | Function                                                                   |

|-----|------------|----------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b, Write = Don't Care.                                            |

| 5   | CP0RIE     | Comparator0 Rising-Edge Interrupt Enable.                                  |

|     |            | 0: Comparator0 Rising-edge interrupt disabled.                             |

|     |            | 1: Comparator0 Rising-edge interrupt enabled.                              |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.                                 |

|     |            | 0: Comparator0 Falling-edge interrupt disabled.                            |

|     |            | 1: Comparator0 Falling-edge interrupt enabled.                             |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                            |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select.                                                   |

|     |            | These bits affect the response time and power consumption for Comparator0. |

|     |            | 00: Mode 0 (Fastest Response Time, Highest Power Consumption)              |

|     |            | 01: Mode 1                                                                 |

|     |            | 10: Mode 2                                                                 |

|     |            | 11: Mode 3 (Slowest Response Time, Lowest Power Consumption)               |

# SFR Definition 8.5. CPT0MX: Comparator0 MUX Selection

| Bit   | 7             | 6           | 5                                                       | 4             | 3            | 2            | 1          | 0 |  |  |

|-------|---------------|-------------|---------------------------------------------------------|---------------|--------------|--------------|------------|---|--|--|

| Nam   | е             | CMX0        | N[3:0]                                                  | I             |              | CMXC         | P[3:0]     |   |  |  |

| Туре  | •             | R/          | R/W R/W                                                 |               | R/W          |              |            |   |  |  |

| Rese  | et 0          | 1           | 1                                                       | 1             | 0            | 1            | 1          | 1 |  |  |

| SFR A | Address = 0x9 | C; SFR Page | $e = 0 \times 00$                                       |               |              |              |            |   |  |  |

| Bit   | Name          | _           | Function                                                |               |              |              |            |   |  |  |

| 7:4   | CMX0N[3:0]    | Comparato   | r0 Negative                                             | Input MUX     | Selection.   |              |            |   |  |  |

|       |               | 0000:       | P0.                                                     | 1             |              |              |            |   |  |  |

|       |               | 0001:       | P0.                                                     | 3             |              |              |            |   |  |  |

|       |               | 0010:       | P0.                                                     | 5             |              |              |            |   |  |  |

|       |               | 0011:       | P0.                                                     | 7             |              |              |            |   |  |  |

|       |               | 0100:       | P1.                                                     | 1             |              |              |            |   |  |  |

|       |               | 0101:       | P1.                                                     | 3             |              |              |            |   |  |  |

|       |               | 0110:       | P1.                                                     | 5             |              |              |            |   |  |  |

|       |               | 0111:       | P1.                                                     | 7             |              |              |            |   |  |  |

|       |               | 1000:       | P2.                                                     | 1             |              |              |            |   |  |  |

|       |               | 1001:       | 001: P2.3 (only available on 40-pin and 32-pin devices) |               |              |              |            |   |  |  |

|       |               | 1010:       | P2.                                                     | 5 (only avail | able on 40-p | in and 32-pi | n devices) |   |  |  |

|       |               | 1011:       | P2.                                                     | 7 (only avail | able on 40-p | in and 32-pi | n devices) |   |  |  |

|       |               | 1100–11111: | Nor                                                     | ne            |              |              |            |   |  |  |

| 3:0   | CMX0P[3:0]    | Comparato   | r0 Positive                                             | Input MUX     | Selection.   |              |            |   |  |  |

|       |               | 0000:       | P0.                                                     | 0             |              |              |            |   |  |  |

|       |               | 0001:       | P0.                                                     | 2             |              |              |            |   |  |  |

|       |               | 0010:       | P0.                                                     | 4             |              |              |            |   |  |  |

|       |               | 0011:       | P0.                                                     | 6             |              |              |            |   |  |  |

|       |               | 0100:       | P1.                                                     | 0             |              |              |            |   |  |  |

|       |               | 0101:       | P1.                                                     | 2             |              |              |            |   |  |  |

|       |               | 0110:       | P1.                                                     | 4             |              |              |            |   |  |  |

|       |               | 0111:       | P1.                                                     | 6             |              |              |            |   |  |  |

|       |               | 1000:       | P2.                                                     | 0             |              |              |            |   |  |  |

|       |               | 1001:       | P2.                                                     | 2 (only avail | able on 40-p | in and 32-pi | n devices) |   |  |  |

|       |               | 1010:       | P2.                                                     | 4 (only avail | able on 40-p | in and 32-pi | n devices) |   |  |  |

|       |               | 1011:       | P2.                                                     | 6 (only avail | able on 40-p | in and 32-pi | n devices) |   |  |  |

|       |               | 1100–1111:  | Nor                                                     | ne            |              |              |            |   |  |  |

# Table 10.1. CIP-51 Instruction Set Summary (Continued)

| Mnemonic             | Description                                         | Bytes | Clock<br>Cycles |

|----------------------|-----------------------------------------------------|-------|-----------------|

| SETB C               | Set Carry                                           | 1     | 1               |

| SETB bit             | Set direct bit                                      | 2     | 2               |

| CPL C                | Complement Carry                                    | 1     | 1               |

| CPL bit              | Complement direct bit                               | 2     | 2               |

| ANL C, bit           | AND direct bit to Carry                             | 2     | 2               |

| ANL C, /bit          | AND complement of direct bit to Carry               | 2     | 2               |

| ORL C, bit           | OR direct bit to carry                              | 2     | 2               |

| ORL C, /bit          | OR complement of direct bit to Carry                | 2     | 2               |

| MOV C, bit           | Move direct bit to Carry                            | 2     | 2               |

| MOV bit, C           | Move Carry to direct bit                            | 2     | 2               |

| JC rel               | Jump if Carry is set                                | 2     | 2/(4-6)         |

| JNC rel              | Jump if Carry is not set                            | 2     | 2/(4-6)*        |

| JB bit, rel          | Jump if direct bit is set                           | 3     | 3/(5-7)*        |

| JNB bit, rel         | Jump if direct bit is not set                       | 3     | 3/(5-7)*        |

| JBC bit, rel         | Jump if direct bit is set and clear bit             | 3     | 3/(5-7)*        |

| Program Branching    |                                                     |       | •               |

| ACALL addr11         | Absolute subroutine call                            | 2     | 4-6*            |

| LCALL addr16         | Long subroutine call                                | 3     | 5-7*            |

| RET                  | Return from subroutine                              | 1     | 6-8*            |

| RETI                 | Return from interrupt                               | 1     | 6-8*            |

| AJMP addr11          | Absolute jump                                       | 2     | 4-6*            |

| LJMP addr16          | Long jump                                           | 3     | 5-7*            |

| SJMP rel             | Short jump (relative address)                       | 2     | 4-6*            |

| JMP @A+DPTR          | Jump indirect relative to DPTR                      | 1     | 3-5*            |

| JZ rel               | Jump if A equals zero                               | 2     | 2/(4-6)*        |

| JNZ rel              | Jump if A does not equal zero                       | 2     | 2/(4-6)*        |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3     | 4/(6-8)*        |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3     | 3/(6-8)*        |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3     | 3/(5-7)*        |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal | 3     | 4/(6-8)*        |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2     | 2/(4-6)*        |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero          | 3     | 3/(5-7)*        |

| NOP                  | No operation                                        | 1     | 1               |

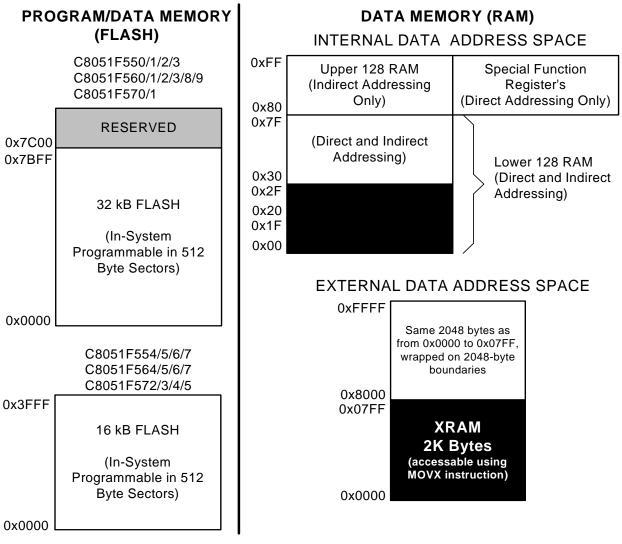

# **11. Memory Organization**

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The memory organization is shown in Figure 11.1

Figure 11.1. C8051F55x/56x/57x Memory Map

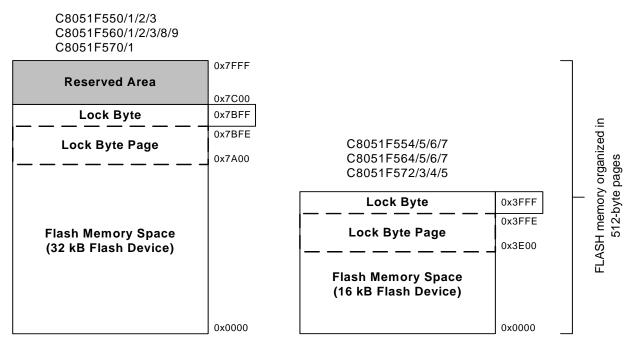

## 11.1. Program Memory

The CIP-51 core has a 64 kB program memory space. The C8051F55x/56x/57x devices implement 32 kB or 16 kB of this program memory space as in-system, re-programmable Flash memory, organized in a contiguous block from addresses 0x0000 to 0x7FFF in 32 kB devices and addresses 0x0000 to 0x3FFF in 16 kB devices. The address 0x7BFF in 32 kB devices and 0x3FFF in 16 kB devices serves as the security lock byte for the device. Addresses above 0x7BFF are reserved in the 32 kB devices.

Figure 11.2. Flash Program Memory Map

#### 11.1.1. MOVX Instruction and Program Memory

The MOVX instruction in an 8051 device is typically used to access external data memory. On the C8051F55x/56x/57x devices, the MOVX instruction is normally used to read and write on-chip XRAM, but can be re-configured to write and erase on-chip Flash memory space. MOVC instructions are always used to read Flash memory, while MOVX write instructions are used to erase and write Flash. This Flash access feature provides a mechanism for the C8051F55x/56x/57x to update program code and use the program memory space for non-volatile data storage. Refer to Section "14. Flash Memory" on page 124 for further details.

### 11.2. Data Memory

The C8051F55x/56x/57x devices include 2304 bytes of RAM data memory. 256 bytes of this memory is mapped into the internal RAM space of the 8051. The other 2048 bytes of this memory is on-chip "external" memory. The data memory map is shown in Figure 11.1 for reference.

#### 11.2.1. Internal RAM

There are 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory. Figure 11.1 illustrates the data memory organization of the

## SFR Definition 16.2. RSTSRC: Reset Source

| Bit   | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| Name  |   | FERROR | CORSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | 0 | Varies |

SFR Address = 0xEF; SFR Page = 0x00

| Bit   | Name       | Description                                                                                  | Write                                                                                                                                                                | Read                                                                                                                                           |

|-------|------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Unused     | Unused.                                                                                      | Don't care.                                                                                                                                                          | 0                                                                                                                                              |

| 6     | FERROR     | Flash Error Reset Flag.                                                                      | N/A                                                                                                                                                                  | Set to 1 if Flash<br>read/write/erase error<br>caused the last reset.                                                                          |

| 5     | CORSEF     | Comparator0 Reset Enable and Flag.                                                           | Writing a 1 enables Com-<br>parator0 as a reset source<br>(active-low).                                                                                              | Set to 1 if Comparator0 caused the last reset.                                                                                                 |

| 4     | SWRSF      | Software Reset Force and Flag.                                                               | Writing a 1 forces a sys-<br>tem reset.                                                                                                                              | Set to 1 if last reset was<br>caused by a write to<br>SWRSF.                                                                                   |

| 3     | WDTRSF     | Watchdog Timer Reset Flag.                                                                   | N/A                                                                                                                                                                  | Set to 1 if Watchdog Timer overflow caused the last reset.                                                                                     |

| 2     | MCDRSF     | Missing Clock Detector<br>Enable and Flag.                                                   | Writing a 1 enables the<br>Missing Clock Detector.<br>The MCD triggers a reset<br>if a missing clock condition<br>is detected.                                       | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                        |

| 1     | PORSF      | Power-On/V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the $V_{DD}$ monitor as a reset source.<br>Writing 1 to this bit before the $V_{DD}$ monitor is enabled and stabilized may cause a system reset. | Set to 1 anytime a power-<br>on or V <sub>DD</sub> monitor reset<br>occurs.<br>When set to 1 all other<br>RSTSRC flags are inde-<br>terminate. |

| 0     | PINRSF     | HW Pin Reset Flag.                                                                           | N/A                                                                                                                                                                  | Set to 1 if RST pin caused the last reset.                                                                                                     |

| Note: | Do not use | read-modify-write operations on this                                                         | s register                                                                                                                                                           |                                                                                                                                                |

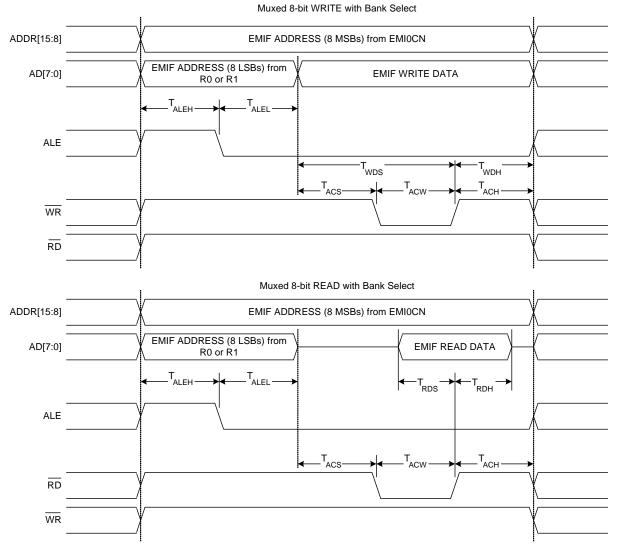

#### 17.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010

Figure 17.5. Multiplexed 8-bit MOVX with Bank Select Timing

| Parameter                 | Description                                          | Min*                    | Max*                     | Units |

|---------------------------|------------------------------------------------------|-------------------------|--------------------------|-------|

| T <sub>ACS</sub>          | Address/Control Setup Time                           | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ACW</sub>          | Address/Control Pulse Width                          | 1 x T <sub>SYSCLK</sub> | 16 x T <sub>SYSCLK</sub> | ns    |

| T <sub>ACH</sub>          | Address/Control Hold Time                            | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEH</sub>         | Address Latch Enable High Time                       | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEL</sub>         | Address Latch Enable Low Time                        | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>WDS</sub>          | Write Data Setup Time                                | 1 x T <sub>SYSCLK</sub> | 19 x T <sub>SYSCLK</sub> | ns    |

| T <sub>WDH</sub>          | Write Data Hold Time                                 | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>RDS</sub>          | Read Data Setup Time                                 | 20                      |                          | ns    |

| T <sub>RDH</sub>          | Read Data Hold Time                                  | 0                       |                          | ns    |

| lote: T <sub>SYSCLK</sub> | is equal to one period of the device system clock (S | YSCLK).                 | 1                        | 1     |

Table 17.2. AC Parameters for External Memory Interface

| Port    |   |   |           | Р                 | 0 |   |   |   |   |    |            | Р    | 1  |    |        |     |    |      |       | Р                  | 2    |       |       |         |    |   |   | Р                 | 3 |    |                  |   | Ρ |

|---------|---|---|-----------|-------------------|---|---|---|---|---|----|------------|------|----|----|--------|-----|----|------|-------|--------------------|------|-------|-------|---------|----|---|---|-------------------|---|----|------------------|---|---|

|         |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      | a     | P2.<br>vail<br>d3: | able | e o i | n 4(  | ) - p i | in |   |   | ilat              |   | on | P4.<br>40- <br>s |   |   |

| PIN I/O | 0 | 1 | 2         | 3                 | 4 | 5 | 6 | 7 | 0 | 1  | 2          | 3    | 4  | 5  | 6      | 7   | 0  | 1    | 2     | 3                  | 4    | 5     | 6     | 7       | 0  | 1 | 2 | 3                 | 4 | 5  | 6                | 7 | C |

| UART_TX |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| UART_RX |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| CAN_TX  |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| CAN_RX  |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| SCK     |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| MISO    |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| MOSI    |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| NSS     |   |   |           |                   |   |   |   |   |   | *1 | v s s      | S Is | or | Iy | p in r | ned | ou | t in | 4 - \ | vire               | SF   |       | 1 o d | е       |    |   |   |                   |   |    |                  |   |   |

| SDA     |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| SCL     |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| C P O   |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| CPOA    |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| C P 1   |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| CP1A    |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| SYSCLK  |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| CEX0    |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| CEX1    |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| CEX2    |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| CEX3    |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| CEX4    |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| CEX5    |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| ECI     |   |   |           |                   |   |   |   |   |   |    |            | İ    | İ  | l  | İ      |     |    |      |       |                    |      |       |       |         |    | Ì |   |                   |   |    |                  |   | Γ |

| ТО      |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| T 1     |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   | Γ |

| LIN_TX  |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   | Γ |

| LIN_RX  |   |   |           |                   |   |   |   |   |   |    |            |      |    |    |        |     |    |      |       |                    |      |       |       |         |    |   |   |                   |   |    |                  |   |   |

| _       | 0 |   | 1<br>P 03 | 0<br><b>5 K</b> I |   |   |   | 0 | 0 |    | 0<br>P 1 3 |      |    |    |        | 0   | 0  |      |       | 0<br><b>5 K</b> I  |      |       | 0     | 0       | 0  |   |   | 0<br><b>5 K</b> I |   |    | 0                | 0 |   |

Figure 19.4. Crossbar Priority Decoder in Example Configuration

## 19.4. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- 4. Assign Port pins to desired peripherals.

- 5. Enable the Crossbar (XBARE = 1).

All Port pins must be configured as either analog or digital inputs. Port 4 C8051F568-9 and 'F570-5 is a digital-only Port. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a 1 indicates a digital input, and a 0 indicates an analog input. All pins default to digital inputs on reset. See SFR Definition 19.13 for the PnMDIN register details.

## SFR Definition 19.15. P0SKIP: Port 0 Skip

| Bit   | 7           | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |

|-------|-------------|---|---|----|---|---|---|---|--|--|--|

| Name  | P0SKIP[7:0] |   |   |    |   |   |   |   |  |  |  |

| Туре  |             |   |   | R/ | W |   |   |   |  |  |  |

| Reset | 0           | 0 | 0 | 0  | 0 | 0 | 0 | 0 |  |  |  |

SFR Address = 0xD4; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0SKIP[7:0] | Port 0 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 0 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P0.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P0.n pin is skipped by the Crossbar.</li> </ul> |

### SFR Definition 19.16. P1: Port 1

| Bit   | 7       | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|---------|---|---|----|---|---|---|---|--|--|--|--|

| Name  | P1[7:0] |   |   |    |   |   |   |   |  |  |  |  |

| Туре  |         |   |   | R/ | W |   |   |   |  |  |  |  |

| Reset | 1       | 1 | 1 | 1  | 1 | 1 | 1 | 1 |  |  |  |  |

#### SFR Address = 0x90; SFR Page = All Pages; Bit-Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|

| 7:0 | P1[7:0] | <b>Port 1 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW. |

## LIN Register Definition 20.5. LIN0CTRL: LIN0 Control Register

| Bit   | 7    | 6     | 5    | 4     | 3      | 2      | 1      | 0     |

|-------|------|-------|------|-------|--------|--------|--------|-------|

| Name  | STOP | SLEEP | TXRX | DTACK | RSTINT | RSTERR | WUPREQ | STREQ |

| Туре  | W    | R/W   | R/W  | R/W   | W      | W      | R/W    | R/W   |

| Reset | 0    | 0     | 0    | 0     | 0      | 0      | 0      | 0     |

Indirect Address = 0x08

| Name   | Function                                                                                                                                                                     |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STOP   | Stop Communication Processing Bit. (slave mode only)<br>This bit always reads as 0.<br>0: No effect.                                                                         |

|        | 1: Block the processing of LIN communications until the next SYNC BREAK signal.                                                                                              |

| SLEEP  | Sleep Mode Bit. (slave mode only)                                                                                                                                            |

|        | <ul><li>0: Wake the device after receiving a Wakeup interrupt.</li><li>1: Put the device into sleep mode after receiving a Sleep Mode frame or a bus idle timeout.</li></ul> |

| TXRX   | Transmit / Receive Selection Bit.                                                                                                                                            |

|        | <ul><li>0: Current frame is a receive operation.</li><li>1: Current frame is a transmit operation.</li></ul>                                                                 |

| DTACK  | Data Acknowledge Bit. (slave mode only)                                                                                                                                      |

|        | Set to 1 after handling a data request interrupt to acknowledge the transfer. The bit will automatically be cleared to 0 by the LIN controller.                              |

| RSTINT | Reset Interrupt Bit.                                                                                                                                                         |

|        | This bit always reads as 0.                                                                                                                                                  |

|        | 0: No effect.<br>1: Reset the LININT bit (LIN0ST.3).                                                                                                                         |

| RSTERR | Reset Error Bit.                                                                                                                                                             |

|        | This bit always reads as 0.                                                                                                                                                  |

|        | 0: No effect.<br>1: Reset the error bits in LIN0ST and LIN0ERR.                                                                                                              |

|        | Wakeup Request Bit.                                                                                                                                                          |

| WUPREQ | Set to 1 to terminate sleep mode by sending a wakeup signal. The bit will automati-<br>cally be cleared to 0 by the LIN controller.                                          |

| STREQ  | Start Request Bit. (master mode only)                                                                                                                                        |

|        | 1: Start a LIN transmission. This should be set only after loading the identifier, data                                                                                      |

|        | length and data buffer if necessary.<br>The bit is reset to 0 upon transmission completion or error detection.                                                               |

|        | STOP<br>SLEEP<br>TXRX<br>DTACK<br>RSTINT<br>RSTERR<br>WUPREQ                                                                                                                 |

## SFR Definition 22.2. SMB0CN: SMBus Control

| Bit   | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0   |

|-------|--------|--------|-----|-----|-------|---------|-----|-----|

| Name  | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI  |

| Туре  | R      | R      | R/W | R/W | R     | R       | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0   |

#### SFR Address = 0xC0; Bit-Addressable; SFR Page =0x00

| Bit | Name    | Description                                                                                                                                                                                                      | Read                                                                                                                       | Write                                                                                                                                                                                |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | SMBus Master/Slave<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a master.                                                                                                     | 0: SMBus operating in<br>slave mode.<br>1: SMBus operating in<br>master mode.                                              | N/A                                                                                                                                                                                  |

| 6   | TXMODE  | SMBus Transmit Mode<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a transmitter.                                                                                               | 0: SMBus in Receiver<br>Mode.<br>1: SMBus in Transmitter<br>Mode.                                                          | N/A                                                                                                                                                                                  |

| 5   | STA     | SMBus Start Flag.                                                                                                                                                                                                | 0: No Start or repeated<br>Start detected.<br>1: Start or repeated Start<br>detected.                                      | 0: No Start generated.<br>1: When Configured as a<br>Master, initiates a START<br>or repeated START.                                                                                 |

| 4   | STO     | SMBus Stop Flag.                                                                                                                                                                                                 | 0: No Stop condition<br>detected.<br>1: Stop condition detected<br>(if in Slave Mode) or pend-<br>ing (if in Master Mode). | 0: No STOP condition is<br>transmitted.<br>1: When configured as a<br>Master, causes a STOP<br>condition to be transmit-<br>ted after the next ACK<br>cycle.<br>Cleared by Hardware. |

| 3   | ACKRQ   | SMBus Acknowledge<br>Request.                                                                                                                                                                                    | 0: No Ack requested<br>1: ACK requested                                                                                    | N/A                                                                                                                                                                                  |

| 2   | ARBLOST | SMBus Arbitration Lost<br>Indicator.                                                                                                                                                                             | 0: No arbitration error.<br>1: Arbitration Lost                                                                            | N/A                                                                                                                                                                                  |

| 1   | ACK     | SMBus Acknowledge.                                                                                                                                                                                               | 0: NACK received.<br>1: ACK received.                                                                                      | 0: Send NACK<br>1: Send ACK                                                                                                                                                          |

| 0   | SI      | <b>SMBus Interrupt Flag.</b><br>This bit is set by hardware<br>under the conditions listed in<br>Table 15.3. SI must be cleared<br>by software. While SI is set,<br>SCL is held low and the<br>SMBus is stalled. | 0: No interrupt pending<br>1: Interrupt Pending                                                                            | <ul><li>0: Clear interrupt, and initiate next state machine event.</li><li>1: Force interrupt.</li></ul>                                                                             |

## 24.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. Note that the NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 24.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPI0 with the SPIEN bit. Figure 24.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

### 24.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- 1. The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.