Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                             |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 2.25К х 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | A/D 25x12b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                              |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 32-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f563-imr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1. System Overview

C8051F55x/56x/57x devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 2.1 for specific product feature selection and part ordering numbers.

- High-speed pipelined 8051-compatible microcontroller core (up to 50 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- Controller Area Network (CAN 2.0B) Controller with 32 message objects, each with its own indentifier mask (C8051F550/1/4/5, 'F560/1/4/5/8/9, and 'F572/3)

- LIN 2.1 peripheral (fully backwards compatible, master and slave modes) (C8051F550/2/4/6, 'F560/2/4/6/8, and 'F570/2/4)

- True 12-bit 200 ksps 32-channel single-ended ADC with analog multiplexer

- Precision programmable 24 MHz internal oscillator that is within ±0.5% across the temperature range and for VDD voltages greater than or equal to the on-chip voltage regulator minimum output at the low setting. The oscillator is within ±1.0% for VDD voltages below this minimum output setting.

- On-chip Clock Multiplier to reach up to 50 MHz

- 32 kB (C8051F550-3, 'F560-3, 'F568-9, and 'F570-1) or 16 kB (C8051F554-7, 'F564-7, and 'F572-5) of on-chip Flash memory

- 2304 bytes of on-chip RAM

- SMBus/I2C, Enhanced UART, and Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- External Data Memory Interface (C8051F568-9 and 'F570-5) with 64 kB address space

- Programmable Counter/Timer Array (PCA) with six capture/compare modules and Watchdog Timer function

- On-chip Voltage Regulator

- On-chip Power-On Reset, V<sub>DD</sub> Monitor, and Temperature Sensor

- On-chip Voltage Comparator

- 33, 25, or 18 Port I/O (5 V push-pull)

With on-chip Voltage Regulator, Power-On Reset, V<sub>DD</sub> monitor, Watchdog Timer, and clock oscillator, the C8051F55x/56x/57x devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

The devices are specified for 1.8 V to 5.25 V operation over the automotive temperature range (-40 to +125 °C). The C8051F568-9 and 'F570-5 are available in 40-pin QFN packages, the C8051F560-7 devices are available in 32-pin QFP and QFN packages, and the C8051F550-7 are available in 24-pin QFN packages. All package options are lead-free and RoHS compliant. See Table 2.1 for ordering information. Block diagrams are included in Figure 1.1, Figure 1.2, and Figure 1.3.

## 4. Package Specifications

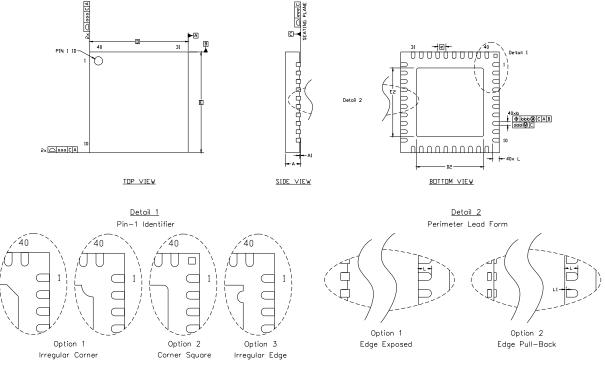

### 4.1. QFN-40 Package Specifications

### Figure 4.1. QFN-40 Package Drawing

| Dimension | Min      | Тур      | Max  | Dimension | Min  | Тур  | Max  |

|-----------|----------|----------|------|-----------|------|------|------|

| A         | 0.80     | 0.85     | 0.90 | E2        | 4.00 | 4.10 | 4.20 |

| A1        | 0.00     |          | 0.05 | L         | 0.35 | 0.40 | 0.45 |

| b         | 0.18     | 0.23     | 0.28 | L1        |      |      | 0.10 |

| D         |          | 6.00 BSC |      | aaa       |      |      | 0.10 |

| D2        | 4.00     | 4.10     | 4.20 | bbb       |      |      | 0.10 |

| е         | 0.50 BSC |          |      | ddd       |      |      | 0.05 |

| E         | 6.00 BSC |          |      | eee       |      |      | 0.08 |

### Table 4.1. QFN-40 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

**3.** This drawing conforms to JEDEC Solid State Outline MO-220, variation VJJD-5, except for features A, D2, and E2 which are toleranced per supplier designation.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

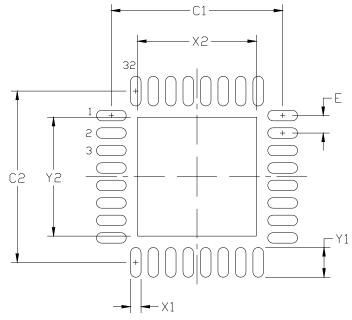

Figure 4.6. QFN-32 Landing Diagram

### Table 4.6. QFN-32 Landing Diagram Dimensions

| Dimension | Min      | Max  | ] | Dimension | Min  | Max  |

|-----------|----------|------|---|-----------|------|------|

| C1        | 4.80     | 4.90 |   | X2        | 3.20 | 3.40 |

| C2        | 4.80     | 4.90 |   | Y1        | 0.75 | 0.85 |

| е         | 0.50 BSC |      | 1 | Y2        | 3.20 | 3.40 |

| X1        | 0.20     | 0.30 |   |           |      |      |

Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

Solder Mask Design

**3.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

Stencil Design

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- 7. A 3x3 array of 1.0 mm openings on a 1.20 mm pitch should be used for the center ground pad.

Card Assembly

- 8. A No-Clean, Type-3 solder paste is recommended.

- **9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### 6.3.2. Setting the Gain Value

The three programmable gain registers are accessed indirectly using the ADC0H and ADC0L registers when the GAINEN bit (ADC0CF.0) bit is set. ADC0H acts as the address register, and ADC0L is the data register. The programmable gain registers can only be written to and cannot be read. See Gain Register Definition 6.1, Gain Register Definition 6.2, and Gain Register Definition 6.3 for more information.

The gain is programmed using the following steps:

- 1. Set the GAINEN bit (ADC0CF.0)

- 2. Load the ADC0H with the ADC0GNH, ADC0GNL, or ADC0GNA address.

- 3. Load ADC0L with the desired value for the selected gain register.

- 4. Reset the GAINEN bit (ADC0CF.0)

#### Notes:

- 1. An ADC conversion should not be performed while the GAINEN bit is set.

- 2. Even with gain enabled, the maximum input voltage must be less than V<sub>REGIN</sub> and the maximum voltage of the signal after gain must be less than or equal to V<sub>REF</sub>.

In code, changing the value to 0.44 gain from the previous example looks like:

// in 'C':

MOV ADC0H,#07H MOV ADC0L,#0A0H

MOV ADC0H,#08H

MOV ADC0L,#01H

ANL ADCOCF,#0FEH

| ADC0CF  = 0x01;  | // GAINEN = 1                                |

|------------------|----------------------------------------------|

| ADC0H = 0x04;    | // Load the ADC0GNH address                  |

| ADC0L = 0x6C;    | // Load the upper byte of 0x6CA to ADC0GNH   |

| ADC0H = 0x07;    | // Load the ADC0GNL address                  |

| ADC0L = 0xA0;    | // Load the lower nibble of 0x6CA to ADC0GNL |

| ADC0H = 0x08;    | // Load the ADC0GNA address                  |

| ADC0L = 0x01;    | // Set the GAINADD bit                       |

| ADC0CF &= ~0x01; | // GAINEN = 0                                |

|                  |                                              |

| ; in assembly    |                                              |

| ORL ADC0CF,#01H  | ; GAINEN = 1                                 |

| MOV ADC0H,#04H   | ; Load the ADC0GNH address                   |

| MOV ADC0L,#06CH  | ; Load the upper byte of 0x6CA to ADC0GNH    |

- ; Load the upper byte of 0x6CA to ADC0GNH

- : Load the ADC0GNL address

- ; Load the lower nibble of 0x6CA to ADC0GNL

- : Load the ADC0GNA address

- : Set the GAINADD bit

- ; GAINEN = 0

### SFR Definition 7.1. REF0CN: Reference Control

| Bit   | 7 | 6 | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|---|---|-------|-------|-------|-------|-------|-------|

| Name  |   |   | ZTCEN | REFLV | REFSL | TEMPE | BIASE | REFBE |

| Туре  | R | R | R     | R     | R/W   | R/W   | R/W   | R/W   |

| Reset | 0 | 0 | 0     | 0     | 0     | 0     | 0     | 0     |

### SFR Address = 0xD1; SFR Page = 0x00

| Bit | Name   | Function                                                                                                                                                                          |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b; Write = don't care.                                                                                                                                                   |

| 5   | ZTCEN  | Zero Temperature Coefficient Bias Enable Bit.                                                                                                                                     |

|     |        | This bit must be set to 1b before entering oscillator suspend mode.                                                                                                               |

|     |        | 0: ZeroTC Bias Generator automatically enabled when required.<br>1: ZeroTC Bias Generator forced on.                                                                              |

| 4   | REFLV  |                                                                                                                                                                                   |

| 4   | REFLV  | Voltage Reference Output Level Select.<br>This bit selects the output voltage level for the internal voltage reference                                                            |

|     |        | 0: Internal voltage reference set to 1.5 V.                                                                                                                                       |

|     |        | 1: Internal voltage reference set to 2.20 V.                                                                                                                                      |

| 3   | REFSL  | Voltage Reference Select.                                                                                                                                                         |

|     |        | This bit selects the ADCs voltage reference.                                                                                                                                      |

|     |        | 0: V <sub>REF</sub> pin used as voltage reference.                                                                                                                                |

|     |        | 1: $V_{DD}$ used as voltage reference. If $V_{DD}$ is selected as the voltage reference and the ADC is enabled in the ADC0CN register, the P0.0/VREF pin cannot operate as a gen- |

|     |        | eral purpose I/O pin in open-drain mode. With the above settings, this pin can operate                                                                                            |

|     |        | in push-pull output mode or as an analog input.                                                                                                                                   |

| 2   | TEMPE  | Temperature Sensor Enable Bit.                                                                                                                                                    |

|     |        | 0: Internal Temperature Sensor off.                                                                                                                                               |

|     |        | 1: Internal Temperature Sensor on.                                                                                                                                                |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.                                                                                                                                        |

|     |        | 0: Internal Bias Generator off.<br>1: Internal Bias Generator on.                                                                                                                 |

| 0   |        |                                                                                                                                                                                   |

| 0   | REFBE  | On-chip Reference Buffer Enable Bit.                                                                                                                                              |

|     |        | 0: On-chip Reference Buffer off.<br>1: On-chip Reference Buffer on. Internal voltage reference driven on the V <sub>REF</sub> pin.                                                |

|     |        |                                                                                                                                                                                   |

#### Notes on Registers, Operands and Addressing Modes:

**Rn**—Register R0–R7 of the currently selected register bank.

@Ri—Data RAM location addressed indirectly through R0 or R1.

**rel**—8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct**—8-bit internal data location's address. This could be a direct-access Data RAM location (0x00–0x7F) or an SFR (0x80–0xFF).

#data—8-bit constant

#data16—16-bit constant

**bit**—Direct-accessed bit in Data RAM or SFR

**addr11**—11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16**—16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 64 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

### 10.3. CIP-51 Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic I. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the datasheet associated with their corresponding system function.

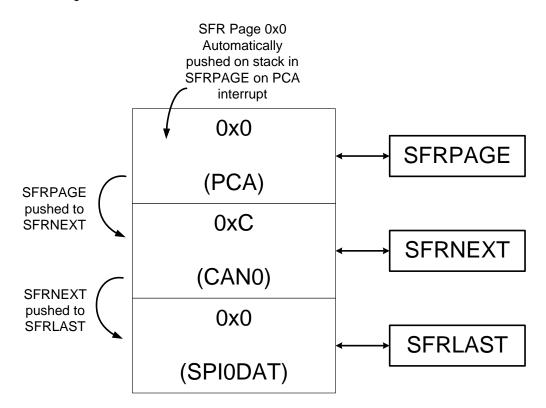

While in the CAN0 ISR, a PCA interrupt occurs. Recall the PCA interrupt is configured as a high priority interrupt, while the CAN0 interrupt is configured as a *low* priority interrupt. Thus, the CIP-51 will now vector to the high priority PCA ISR. Upon doing so, the CIP-51 will automatically place the SFR page needed to access the PCA's special function registers into the SFRPAGE register, SFR Page 0x00. The value that was in the SFRPAGE register before the PCA interrupt (SFR Page 0x0C for CAN0) is pushed down the stack into SFRNEXT. Likewise, the value that was in the SFRNEXT register before the PCA interrupt (in this case SFR Page 0x00 for SPI0DAT) is pushed down to the SFRLAST register, the "bottom" of the stack. Note that a value stored in SFRLAST (via a previous software write to the SFRLAST register) will be overwritten. See Figure 12.4.

Figure 12.4. SFR Page Stack Upon PCA Interrupt Occurring During a CAN0 ISR

### SFR Definition 13.4. EIP1: Extended Interrupt Priority 1

| Bit   | 7     | 6   | 5    | 4    | 3     | 2     | 1      | 0     |

|-------|-------|-----|------|------|-------|-------|--------|-------|

| Name  | PLIN0 | PT3 | PCP1 | PCP0 | PPCA0 | PADC0 | PWADC0 | PSMB0 |

| Туре  | R/W   | R/W | R/W  | R/W  | R/W   | R/W   | R/W    | R/W   |

| Reset | 0     | 0   | 0    | 0    | 0     | 0     | 0      | 0     |

### SFR Address = 0xF6; SFR Page = 0x00 and 0x0F

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                     |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PLIN0  | LIN0 Interrupt Priority Control.<br>This bit sets the priority of the LIN0 interrupt.<br>0: LIN0 interrupts set to low priority level.<br>1: LIN0 interrupts set to high priority level.                                                                                                                     |

| 6   | PT3    | Timer 3 Interrupt Priority Control.This bit sets the priority of the Timer 3 interrupt.0: Timer 3 interrupts set to low priority level.1: Timer 3 interrupts set to high priority level.                                                                                                                     |

| 5   | PCP1   | Comparator0 (CP1) Interrupt Priority Control.<br>This bit sets the priority of the CP1 interrupt.<br>0: CP1 interrupt set to low priority level.<br>1: CP1 interrupt set to high priority level.                                                                                                             |

| 4   | PCP0   | Comparator0 (CP0) Interrupt Priority Control.<br>This bit sets the priority of the CP0 interrupt.<br>0: CP0 interrupt set to low priority level.<br>1: CP0 interrupt set to high priority level.                                                                                                             |

| 3   | PPCA0  | <ul> <li>Programmable Counter Array (PCA0) Interrupt Priority Control.</li> <li>This bit sets the priority of the PCA0 interrupt.</li> <li>0: PCA0 interrupt set to low priority level.</li> <li>1: PCA0 interrupt set to high priority level.</li> </ul>                                                    |

| 2   | PADC0  | <ul> <li>ADC0 Conversion Complete Interrupt Priority Control.</li> <li>This bit sets the priority of the ADC0 Conversion Complete interrupt.</li> <li>0: ADC0 Conversion Complete interrupt set to low priority level.</li> <li>1: ADC0 Conversion Complete interrupt set to high priority level.</li> </ul> |

| 1   | PWADC0 | <ul> <li>ADC0 Window Comparator Interrupt Priority Control.</li> <li>This bit sets the priority of the ADC0 Window interrupt.</li> <li>0: ADC0 Window interrupt set to low priority level.</li> <li>1: ADC0 Window interrupt set to high priority level.</li> </ul>                                          |

| 0   | PSMB0  | <ul> <li>SMBus (SMB0) Interrupt Priority Control.</li> <li>This bit sets the priority of the SMB0 interrupt.</li> <li>0: SMB0 interrupt set to low priority level.</li> <li>1: SMB0 interrupt set to high priority level.</li> </ul>                                                                         |

The level of Flash security depends on the Flash access method. The three Flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 14.1 summarizes the Flash security features of the C8051F55x/56x/57x devices.

| Action                                                                      | C2 Debug                | User Firmware executing from: |                   |  |  |

|-----------------------------------------------------------------------------|-------------------------|-------------------------------|-------------------|--|--|

|                                                                             | Interface               | an unlocked page              | a locked page     |  |  |

| Read, Write or Erase unlocked pages<br>(except page with Lock Byte)         | Permitted               | Permitted                     | Permitted         |  |  |

| Read, Write or Erase locked pages<br>(except page with Lock Byte)           | Not Permitted           | Flash Error Reset             | Permitted         |  |  |

| Read or Write page containing Lock Byte<br>(if no pages are locked)         | Permitted               | Permitted                     | Permitted         |  |  |

| Read or Write page containing Lock Byte<br>(if any page is locked)          | Not Permitted           | Flash Error Reset             | Permitted         |  |  |

| Read contents of Lock Byte<br>(if no pages are locked)                      | Permitted               | Permitted                     | Permitted         |  |  |

| Read contents of Lock Byte<br>(if any page is locked)                       | Not Permitted           | Flash Error Reset             | Permitted         |  |  |

| Erase page containing Lock Byte<br>(if no pages are locked)                 | Permitted               | Flash Error Reset             | Flash Error Reset |  |  |

| Erase page containing Lock Byte—Unlock all<br>pages (if any page is locked) | C2 Device<br>Erase Only | Flash Error Reset             | Flash Error Reset |  |  |

| Lock additional pages<br>(change '1's to '0's in the Lock Byte)             | Not Permitted           | Flash Error Reset             | Flash Error Reset |  |  |

| Unlock individual pages<br>(change '0's to '1's in the Lock Byte)           | Not Permitted           | Flash Error Reset             | Flash Error Reset |  |  |

| Read, Write or Erase Reserved Area                                          | Not Permitted           | Flash Error Reset             | Flash Error Reset |  |  |

C2 Device Erase—Erases all Flash pages including the page containing the Lock Byte.

Flash Error Reset—Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is '1' after reset).

- All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

- Locking any Flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

### 17.5.3. Split Mode with Bank Select

When EMI0CF[3:2] are set to 10, the XRAM memory map is split into two areas, on-chip space and offchip space.

- Effective addresses below the internal XRAM size boundary will access on-chip XRAM space.

- Effective addresses above the internal XRAM size boundary will access off-chip space.

- 8-bit MOVX operations use the contents of EMI0CN to determine whether the memory access is onchip or off-chip. The upper 8-bits of the Address Bus A[15:8] are determined by EMI0CN, and the lower 8-bits of the Address Bus A[7:0] are determined by R0 or R1. All 16-bits of the Address Bus A[15:0] are driven in "Bank Select" mode.

- 16-bit MOVX operations use the contents of DPTR to determine whether the memory access is on-chip or off-chip, and the full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

### 17.5.4. External Only

When EMI0CF[3:2] are set to 11, all MOVX operations are directed to off-chip space. On-chip XRAM is not visible to the CPU. This mode is useful for accessing off-chip memory located between 0x0000 and the internal XRAM size boundary.

- 8-bit MOVX operations ignore the contents of EMI0CN. The upper Address bits A[15:8] are not driven (identical behavior to an off-chip access in "Split Mode without Bank Select" described above). This allows the user to manipulate the upper address bits at will by setting the Port state directly. The lower 8-bits of the effective address A[7:0] are determined by the contents of R0 or R1.

- 16-bit MOVX operations use the contents of DPTR to determine the effective address A[15:0]. The full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

### 17.6. Timing

The timing parameters of the External Memory Interface can be configured to enable connection to devices having different setup and hold time requirements. The Address Setup time, Address Hold time, RD and WR strobe widths, and in multiplexed mode, the width of the ALE pulse are all programmable in units of SYSCLK periods through EMI0TC, shown in SFR Definition 17.3, and EMI0CF[1:0].

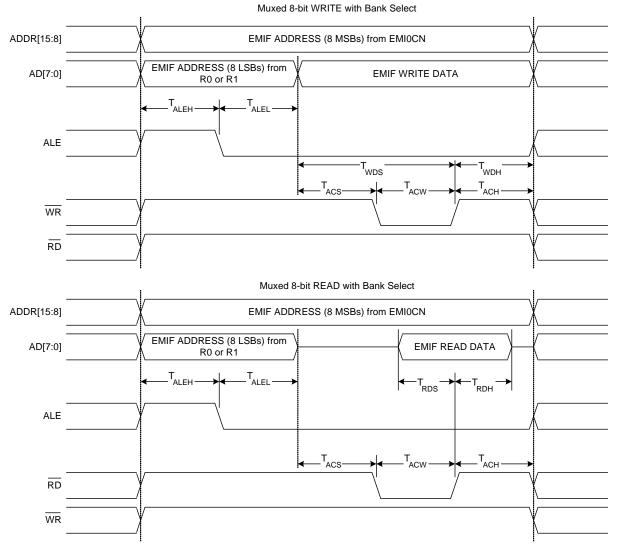

The timing for an off-chip MOVX instruction can be calculated by adding 4 SYSCLK cycles to the timing parameters defined by the EMI0TC register. Assuming non-multiplexed operation, the minimum execution time for an off-chip XRAM operation is 5 SYSCLK cycles (1 SYSCLK for RD or WR pulse + 4 SYSCLKs). For multiplexed operations, the Address Latch Enable signal will require a minimum of 2 additional SYSCLK cycles. Therefore, the minimum execution time for an off-chip XRAM operation in multiplexed mode is 7 SYSCLK cycles (2 for /ALE + 1 for RD or WR + 4). The programmable setup and hold times default to the maximum delay settings after a reset. Table 17.2 lists the ac parameters for the External Memory Interface, and Figure 17.3 through Figure 17.5 show the timing diagrams for the different External Memory Interface modes and MOVX operations.

### 17.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010

Figure 17.5. Multiplexed 8-bit MOVX with Bank Select Timing

### SFR Definition 18.6. OSCXCN: External Oscillator Control

| Bit   | 7      | 6   | 5         | 4  | 3 | 2 | 1         | 0 |

|-------|--------|-----|-----------|----|---|---|-----------|---|

| Name  | XTLVLD | ×   | OSCMD[2:0 | )] |   |   | XFCN[2:0] |   |

| Туре  | R      | R/W |           |    | R |   | R/W       |   |

| Reset | 0      | 0   | 0         | 0  | 0 | 0 | 0         | 0 |

### SFR Address = 0x9F; SFR Page = 0x0F

| Bit | Name        |          | -                                                                     | Function                                  |                 |  |  |  |  |  |

|-----|-------------|----------|-----------------------------------------------------------------------|-------------------------------------------|-----------------|--|--|--|--|--|

| 7   | XTLVLD      | Crystal  | Oscillator Valid Flag.                                                |                                           |                 |  |  |  |  |  |

|     |             | •        | Read only when XOSCMD = 11x.)                                         |                                           |                 |  |  |  |  |  |

|     |             | -        | Crystal Oscillator is unused or not yet stable.                       |                                           |                 |  |  |  |  |  |

|     |             | -        | al Oscillator is running a                                            |                                           |                 |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] |          | External Oscillator Mode Select.                                      |                                           |                 |  |  |  |  |  |

|     |             |          | ternal Oscillator circuit of                                          |                                           |                 |  |  |  |  |  |

|     |             |          | ternal CMOS Clock Mod<br>ernal CMOS Clock Mod                         |                                           |                 |  |  |  |  |  |

|     |             |          | Oscillator Mode.                                                      |                                           |                 |  |  |  |  |  |

|     |             | 101: Ca  | pacitor Oscillator Mode.                                              |                                           |                 |  |  |  |  |  |

|     |             | -        | stal Oscillator Mode.                                                 |                                           |                 |  |  |  |  |  |

|     |             | 111: Cry | 111: Crystal Oscillator Mode with divide by 2 stage.                  |                                           |                 |  |  |  |  |  |

| 3   | Unused      | Read =   | Read = 0b; Write =0b                                                  |                                           |                 |  |  |  |  |  |

| 2:0 | XFCN[2:0]   | Externa  | I Oscillator Frequency                                                | Control Bits.                             |                 |  |  |  |  |  |

|     |             |          | •                                                                     | quency for Crystal or RC                  | mode.           |  |  |  |  |  |

|     |             | Set acc  | ording to the desired K F                                             | actor for C mode.                         |                 |  |  |  |  |  |

|     |             | XFCN     | Crystal Mode                                                          | RC Mode                                   | C Mode          |  |  |  |  |  |

|     |             | 000      | f ≤ 32 kHz                                                            | f ≤ 25 kHz                                | K Factor = 0.87 |  |  |  |  |  |

|     |             | 001      | 32 kHz < f ≤ 84 kHz                                                   | 25 kHz < f ≤ 50 kHz                       | K Factor = 2.6  |  |  |  |  |  |

|     |             | 010      | 84 kHz < f ≤ 225 kHz                                                  | 50 kHz < f ≤ 100 kHz                      | K Factor = 7.7  |  |  |  |  |  |

|     |             | 011      | 225 kHz < f ≤ 590 kHz                                                 | 100 kHz < f ≤ 200 kHz                     | K Factor = 22   |  |  |  |  |  |

|     |             | 100      | 100 590 kHz < f $\le$ 1.5 MHz 200 kHz < f $\le$ 400 kHz K Factor = 65 |                                           |                 |  |  |  |  |  |

|     |             | 101      | 01 1.5 MHz < f $\leq$ 4 MHz 400 kHz < f $\leq$ 800 kHz K Factor = 180 |                                           |                 |  |  |  |  |  |

|     |             | 110      | $4 \text{ MHz} < f \le 10 \text{ MHz}$                                | 800 kHz < f ≤ 1.6 MHz                     | K Factor = 664  |  |  |  |  |  |

|     |             | 111      | $10 \text{ MHz} < f \le 30 \text{ MHz}$                               | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$ | K Factor = 1590 |  |  |  |  |  |

## **19. Port Input/Output**

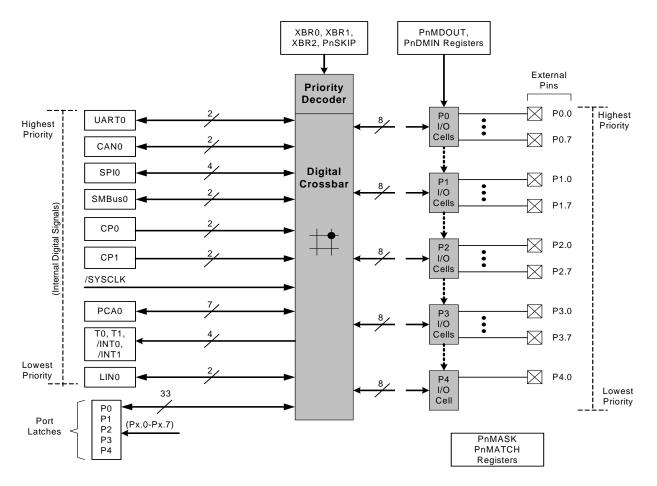

Digital and analog resources are available through 33 (C8051F568-9 and 'F570-5), 25 (C8051F550-7) or 18 (C8051F550-7) I/O pins. Port pins P0.0-P4.0 on the C8051F568-9 and 'F570-5, port pins P0.0-P3.0 on theC8051F560-7, and port pins P0.0-P2.1 on the C8051F550-7 can be defined as general-purpose I/O (GPIO), assigned to one of the internal digital resources, or assigned to an analog function as shown in Figure 19.3. Port pin P4.0 on the C8051F568-9 and 'F570-5 can be used as GPIO and is shared with the C2 Interface Data signal (C2D). Similarly, port pin P3.0 is shared with C2D on the C8051F560-7 and port pin P2.1 on the C8051F550-7. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 19.3 and Figure 19.4). The registers XBR0, XBR1, XBR2 are defined in SFR Definition 19.1 and SFR Definition 19.2 and are used to select internal digital functions.

The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1). Complete Electrical Specifications for Port I/O are given in Table 5.3 on page 40.

Figure 19.1. Port I/O Functional Block Diagram

### SFR Definition 19.10. P3MASK: Port 3 Mask Register

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-------------|---|---|---|---|---|---|---|--|

| Name  | P3MASK[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W         |   |   |   |   |   |   |   |  |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

### SFR Address = 0xAF; SFR Page = 0x00

| Bit   | Name              | Function                                                                                                                                                                                            |

|-------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | P3MASK[7:0]       | Port 1 Mask Value.                                                                                                                                                                                  |

|       |                   | Selects P3 pins to be compared to the corresponding bits in P3MAT.<br>0: P3.n pin logic value is ignored and cannot cause a Port Mismatch event.<br>1: P3.n pin logic value is compared to P3MAT.n. |

| Note: | P3.0 is available | on 40-pin and 32-pin packages. P3.1-P3.7 are available on 40-pin packages                                                                                                                           |

### SFR Definition 19.11. P3MAT: Port 3 Match Register

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|---|---|---|---|---|--|

| Name  | P3MAT[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |

| Reset | 1          | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |

SFR Address = 0xAE; SFR Page = 0x00

| Bit   | Name                 | Function                                                                                                                                                                                   |

|-------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | P3MAT[7:0]           | Port 3 Match Value.                                                                                                                                                                        |

|       |                      | Match comparison value used on Port 3 for bits in P3MAT which are set to 1.<br>0: P3.n pin logic value is compared with logic LOW.<br>1: P3.n pin logic value is compared with logic HIGH. |

| Note: | P3.0 is available of | on 40-pin and 32-pin packages. P3.1-P3.7 are available on 40-pin packages                                                                                                                  |

|                 |       | Baud (bits/sec) |      |       |       |      |       |       |      |       |       |      |       |       |      |

|-----------------|-------|-----------------|------|-------|-------|------|-------|-------|------|-------|-------|------|-------|-------|------|

|                 |       | 20 I            | ۲    |       | 19.2  | К    |       | 9.6   | K    |       | 4.8   | K    |       | 1 K   |      |

| SYSCLK<br>(MHz) | Mult. | Pres.           | Div. | Mult. | Pres. | Div. | Mult. | Pres. | Div. | Mult. | Pres. | Div. | Mult. | Pres. | Div. |

| 25              | 0     | 1               | 312  | 0     | 1     | 325  | 1     | 1     | 325  | 3     | 1     | 325  | 19    | 1     | 312  |

| 24.5            | 0     | 1               | 306  | 0     | 1     | 319  | 1     | 1     | 319  | 3     | 1     | 319  | 19    | 1     | 306  |

| 24              | 0     | 1               | 300  | 0     | 1     | 312  | 1     | 1     | 312  | 3     | 1     | 312  | 19    | 1     | 300  |

| 22.1184         | 0     | 1               | 276  | 0     | 1     | 288  | 1     | 1     | 288  | 3     | 1     | 288  | 19    | 1     | 276  |

| 16              | 0     | 1               | 200  | 0     | 1     | 208  | 1     | 1     | 208  | 3     | 1     | 208  | 19    | 1     | 200  |

| 12.25           | 0     | 0               | 306  | 0     | 0     | 319  | 1     | 0     | 319  | 3     | 0     | 319  | 19    | 0     | 306  |

| 12              | 0     | 0               | 300  | 0     | 0     | 312  | 1     | 0     | 312  | 3     | 0     | 312  | 19    | 0     | 300  |

| 11.0592         | 0     | 0               | 276  | 0     | 0     | 288  | 1     | 0     | 288  | 3     | 0     | 288  | 19    | 0     | 276  |

| 8               | 0     | 0               | 200  | 0     | 0     | 208  | 1     | 0     | 208  | 3     | 0     | 208  | 19    | 0     | 200  |

Table 20.2. Manual Baud Rate Parameters Examples

### 20.2.4. Baud Rate Calculations—Automatic Mode

If the LIN controller is configured for slave mode, only the prescaler and divider need to be calculated:

prescaler =

$$ln\left[\frac{SYSCLK}{4000000}\right] \times \frac{1}{ln2} - 1$$

divider =  $\frac{\text{SYSCLK}}{2^{(\text{prescaler} + 1)} \times 20000}$

The following example calculates the values of these variables for a 24 MHz system clock:

prescaler =

$$ln \left[ \frac{24000000}{4000000} \right] \times \frac{1}{ln2} - 1 = 1.585 \cong 1$$

divider =

$$\frac{24000000}{2^{(1+1)} \times 20000}$$

= 300

Table 20.3 presents some typical values of system clock and baud rate along with their factors.

### LIN Register Definition 20.5. LIN0CTRL: LIN0 Control Register

| Bit   | 7    | 6     | 5    | 4     | 3      | 2      | 1      | 0     |

|-------|------|-------|------|-------|--------|--------|--------|-------|

| Name  | STOP | SLEEP | TXRX | DTACK | RSTINT | RSTERR | WUPREQ | STREQ |

| Туре  | W    | R/W   | R/W  | R/W   | W      | W      | R/W    | R/W   |

| Reset | 0    | 0     | 0    | 0     | 0      | 0      | 0      | 0     |

Indirect Address = 0x08

| Bit | Name   | Function                                                                                                                                                                     |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | STOP   | Stop Communication Processing Bit. (slave mode only)This bit always reads as 0.0: No effect.                                                                                 |

|     |        | 1: Block the processing of LIN communications until the next SYNC BREAK signal.                                                                                              |

| 6   | SLEEP  | Sleep Mode Bit. (slave mode only)                                                                                                                                            |

|     |        | <ul><li>0: Wake the device after receiving a Wakeup interrupt.</li><li>1: Put the device into sleep mode after receiving a Sleep Mode frame or a bus idle timeout.</li></ul> |

| 5   | TXRX   | Transmit / Receive Selection Bit.                                                                                                                                            |

|     |        | <ul><li>0: Current frame is a receive operation.</li><li>1: Current frame is a transmit operation.</li></ul>                                                                 |

| 4   | DTACK  | Data Acknowledge Bit. (slave mode only)                                                                                                                                      |

|     |        | Set to 1 after handling a data request interrupt to acknowledge the transfer. The bit will automatically be cleared to 0 by the LIN controller.                              |

| 3   | RSTINT | Reset Interrupt Bit.                                                                                                                                                         |

|     |        | This bit always reads as 0.                                                                                                                                                  |

|     |        | 0: No effect.<br>1: Reset the LININT bit (LIN0ST.3).                                                                                                                         |

| 2   | RSTERR | Reset Error Bit.                                                                                                                                                             |

|     |        | This bit always reads as 0.                                                                                                                                                  |

|     |        | 0: No effect.                                                                                                                                                                |

|     |        | 1: Reset the error bits in LIN0ST and LIN0ERR.                                                                                                                               |

| 1   | WUPREQ | Wakeup Request Bit.                                                                                                                                                          |

|     |        | Set to 1 to terminate sleep mode by sending a wakeup signal. The bit will automati-<br>cally be cleared to 0 by the LIN controller.                                          |

| 0   | STREQ  | Start Request Bit. (master mode only)                                                                                                                                        |

|     |        | 1: Start a LIN transmission. This should be set only after loading the identifier, data                                                                                      |

|     |        | length and data buffer if necessary.<br>The bit is reset to 0 upon transmission completion or error detection.                                                               |

|     |        |                                                                                                                                                                              |

### 21.2.4. CAN Register Assignment

The standard Bosch CAN registers are mapped to SFR space as shown below and their full definitions are available in the CAN User's Guide. The name shown in the Name column matches what is provided in the CAN User's Guide. One additional SFR which is not a standard Bosch CAN register, CAN0CFG, is provided to configure the CAN clock. All CAN registers are located on SFR Page 0x0C.

| CAN   | Name                                | SFR Name    | SFR   | SFR Name    | SFR   | 16-bit     | Reset               |

|-------|-------------------------------------|-------------|-------|-------------|-------|------------|---------------------|

| Addr. |                                     | (High)      | Addr. | (Low)       | Addr. | SFR        | Value               |

| 0x00  | CAN Control Register                | _           | _     | CAN0CN      | 0xC0  | _          | 0x01                |

| 0x02  | Status Register                     | _           | _     | CAN0STAT    | 0x94  | _          | 0x00                |

| 0x04  | Error Counter <sup>1</sup>          | CAN0ERRH    | 0x97  | CAN0ERRL    | 0x96  | CAN0ERR    | 0x0000              |

| 0x06  | Bit Timing Register <sup>2</sup>    | CAN0BTH     | 0x9B  | CAN0BTL     | 0x9A  | CAN0BT     | 0x2301              |

| 0x08  | Interrupt Register <sup>1</sup>     | CANOIIDH    | 0x9D  | CAN0IIDL    | 0x9C  | CANOIID    | 0x0000              |

| 0x0A  | Test Register                       | _           | _     | CAN0TST     | 0x9E  | —          | 0x00 <sup>3,4</sup> |

| 0x0C  | BRP Extension Register <sup>2</sup> | _           |       | CAN0BRPE    | 0xA1  | —          | 0x00                |

| 0x10  | IF1 Command Request                 | CAN0IF1CRH  | 0xBF  | CAN0IF1CRL  | 0xBE  | CAN0IF1CR  | 0x0001              |

| 0x12  | IF1 Command Mask                    | CAN0IF1CMH  | 0xC3  | CAN0IF1CML  | 0xC2  | CAN0IF1CM  | 0x0000              |

| 0x14  | IF1 Mask 1                          | CAN0IF1M1H  | 0xC5  | CAN0IF1M1L  | 0xC4  | CAN0IF1M1  | 0xFFFF              |

| 0x16  | IF1 Mask 2                          | CAN0IF1M2H  | 0xC7  | CAN0IF1M2L  | 0xC6  | CAN0IF1M2  | 0xFFFF              |

| 0x18  | IF1 Arbitration 1                   | CAN0IF1A1H  | 0xCB  | CAN0IF1A1L  | 0xCA  | CAN0IF1A1  | 0x0000              |

| 0x1A  | IF1 Arbitration 2                   | CAN0IF1A2H  | 0xCD  | CAN0IF1A2L  | 0xCC  | CAN0IF1A2  | 0x0000              |

| 0x1C  | IF1 Message Control                 | CAN0IF1MCH  | 0xD3  | CAN0IF1MCL  | 0xD2  | CAN0IF1MC  | 0x0000              |

| 0x1E  | IF1 Data A 1                        | CAN0IF1DA1H | 0xD5  | CAN0IF1DA1L | 0xD4  | CAN0IF1DA1 | 0x0000              |

| 0x20  | IF1 Data A 2                        | CAN0IF1DA2H | 0xD7  | CAN0IF1DA2L | 0xD6  | CAN0IF1DA2 | 0x0000              |

| 0x22  | IF1 Data B 1                        | CAN0IF1DB1H | 0xDB  | CAN0IF1DB1L | 0xDA  | CAN0IF1DB1 | 0x0000              |

| 0x24  | IF1 Data B 2                        | CAN0IF1DB2H | 0xDD  | CAN0IF1DB2L | 0xDC  | CAN0IF1DB2 | 0x0000              |

| 0x40  | IF2 Command Request                 | CAN0IF2CRH  | 0xDF  | CAN0IF2CRL  | 0xDE  | CAN0IF2CR  | 0x0001              |

| 0x42  | IF2 Command Mask                    | CAN0IF2CMH  | 0xE3  | CAN0IF2CML  | 0xE2  | CAN0IF2CM  | 0x0000              |

| 0x44  | IF2 Mask 1                          | CAN0IF2M1H  | 0xEB  | CAN0IF2M1L  | 0xEA  | CAN0IF2M1  | 0xFFFF              |

| 0x46  | IF2 Mask 2                          | CAN0IF2M2H  | 0xED  | CAN0IF2M2L  | 0xEC  | CAN0IF2M2  | 0xFFFF              |

| 0x48  | IF2 Arbitration 1                   | CAN0IF2A1H  | 0xEF  | CAN0IF2A1L  | 0xEE  | CAN0IF2A1  | 0x0000              |

| 0x4A  | IF2 Arbitration 2                   | CAN0IF2A2H  | 0xF3  | CAN0IF2A2L  | 0xF2  | CAN0IF2A2  | 0x0000              |

| 0x4C  | IF2 Message Control                 | CAN0IF2MCH  | 0xCF  | CAN0IF2MCL  | 0xCE  | CAN0IF2MC  | 0x0000              |

| 0x4E  | IF2 Data A 1                        | CAN0IF2DA1H | 0xF7  | CAN0IF2DA1L | 0xF6  | CAN0IF2DA1 | 0x0000              |

|       |                                     |             |       |             |       |            |                     |

| Table 21.2. Standard CAN Registers and Reset V |

|------------------------------------------------|

|------------------------------------------------|

Notes:

1. Read-only register.

2. Write-enabled by CCE.

3. The reset value of CAN0TST could also be r0000000b, where r signifies the value of the CAN RX pin.

**4.** Write-enabled by Test.

### 22.5.4. Read Sequence (Slave)

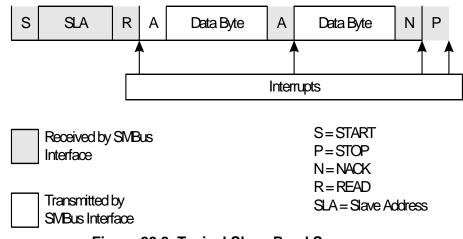

During a read sequence, an SMBus master reads data from a slave device. The slave in this transfer will be a receiver during the address byte, and a transmitter during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode (to receive the slave address) when a START followed by a slave address and direction bit (READ in this case) is received. Upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. The interrupt will occur after the ACK cycle.

If the received slave address is ignored, slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are transmitted. If the received slave address is acknowledged, data should be written to SMB0DAT to be transmitted. The interface enters Slave Transmitter Mode, and transmits one or more bytes of data. After each byte is transmitted, the master sends an acknowledge bit; if the acknowledge bit is an ACK, SMB0DAT should be written with the next data byte. If the acknowledge bit is a NACK, SMB0DAT should not be written to before SI is cleared (Note: an error condition may be generated if SMB0DAT is written following a received NACK while in Slave Transmitter Mode). The interface exits Slave Transmitter Mode after receiving a STOP. Note that the interface will switch to Slave Receiver Mode if SMB0DAT is not written following a Slave Transmitter interrupt. Figure 22.8 shows a typical slave read sequence. Two transmitted data bytes are shown, though any number of bytes may be transmitted. Notice that all of the 'data byte transferred' interrupts occur **after** the ACK cycle in this mode.

### 22.6. SMBus Status Decoding

The current SMBus status can be easily decoded using the SMB0CN register. In the tables, STATUS VECTOR refers to the four upper bits of SMB0CN: MASTER, TXMODE, STA, and STO. The shown response options are only the typical responses; application-specific procedures are allowed as long as they conform to the SMBus specification. Highlighted responses are allowed by hardware but do not conform to the SMBus specification.

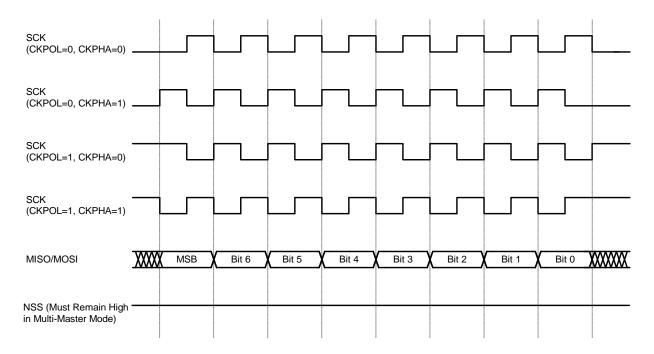

### 24.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 24.5. For slave mode, the clock and data relationships are shown in Figure 24.6 and Figure 24.7. CKPHA must be set to 0 on both the master and slave SPI when communicating between two of the following devices: C8051F04x, C8051F06x, C8051F12x, C8051F31x, C8051F32x, and C8051F33x.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 24.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

Figure 24.5. Master Mode Data/Clock Timing

## NOTES: