Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | · ·                                                             |

| RAM Size                   | 2.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | A/D 25x12b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                              |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-LQFP                                                         |

| Supplier Device Package    | 32-LQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f563-iqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## SFR Definition 6.13. ADC0MX: ADC0 Channel Select

| Bit   | 7 | 6 | 5 | 4           | 3 | 2 | 1 | 0 |  |  |

|-------|---|---|---|-------------|---|---|---|---|--|--|

| Name  |   |   |   | ADC0MX[5:0] |   |   |   |   |  |  |

| Туре  | R | R |   | R/W         |   |   |   |   |  |  |

| Reset | 0 | 0 | 1 | 1           | 1 | 1 | 1 | 1 |  |  |

SFR Address = 0xBB; SFR Page = 0x00;

| Bit | Name       |                     | Function                                                   |

|-----|------------|---------------------|------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b; Write = | = Don't Care.                                              |

| 5:0 | AMX0P[5:0] | AMUX0 Positive In   | put Selection.                                             |

|     |            | 000000:             | P0.0                                                       |

|     |            | 000001:             | P0.1                                                       |

|     |            | 000010:             | P0.2                                                       |

|     |            | 000011:             | P0.3                                                       |

|     |            | 000100:             | P0.4                                                       |

|     |            | 000101:             | P0.5                                                       |

|     |            | 000110:             | P0.6                                                       |

|     |            | 000111:             | P0.7                                                       |

|     |            | 001000:             | P1.0                                                       |

|     |            | 001001:             | P1.1                                                       |

|     |            | 001010:             | P1.2                                                       |

|     |            | 001011:             | P1.3                                                       |

|     |            | 001100:             | P1.4                                                       |

|     |            | 001101:             | P1.5                                                       |

|     |            | 001110:             | P1.6                                                       |

|     |            | 001111:             | P1.7                                                       |

|     |            | 010000:             | P2.0                                                       |

|     |            | 010001:             | P2.1                                                       |

|     |            | 010010:             | P2.2 (Only available on 40-pin and 32-pin package devices) |

|     |            | 010011:             | P2.3 (Only available on 40-pin and 32-pin package devices) |

|     |            | 010100:             | P2.4 (Only available on 40-pin and 32-pin package devices) |

|     |            | 010101:             | P2.5 (Only available on 40-pin and 32-pin package devices) |

|     |            | 010110:             | P2.6 (Only available on 40-pin and 32-pin package devices) |

|     |            | 010111:             | P2.7 (Only available on 40-pin and 32-pin package devices) |

|     |            | 011000:             | P3.0 (Only available on 40-pin and 32-pin package devices) |

|     |            | 011001:             | P3.1 (Only available on 40-pin package devices)            |

|     |            | 011010:             | P3.2 (Only available on 40-pin package devices)            |

|     |            | 011011:             | P3.3 (Only available on 40-pin package devices)            |

|     |            | 011100:             | P3.4 (Only available on 40-pin package devices)            |

|     |            | 011101:             | P3.5 (Only available on 40-pin package devices)            |

|     |            | 011110:             | P3.6 (Only available on 40-pin package devices)            |

|     |            | 011111:             | P3.7 (Only available on 40-pin package devices)            |

|     |            | 100000–101111:      | Reserved                                                   |

|     |            | 110000:             | Temp Sensor                                                |

|     |            | 110001:             | V <sub>DD</sub>                                            |

|     |            | 110010–1111111:     | GND                                                        |

Comparator outputs can be polled in software, used as an interrupt source, and/or routed to a Port pin. When routed to a Port pin, Comparator outputs are available asynchronous or synchronous to the system clock; the asynchronous output is available even in STOP mode (with no system clock active). When disabled, the Comparator output (if assigned to a Port I/O pin via the Crossbar) defaults to the logic low state, and the power supply to the comparator is turned off. See Section "19.3. Priority Crossbar Decoder" on page 172 for details on configuring Comparator outputs via the digital Crossbar. Comparator inputs can be externally driven from -0.25 V to (V<sub>DD</sub>) + 0.25 V without damage or upset. The complete Comparator electrical specifications are given in Table 5.12.

The Comparator response time may be configured in software via the CPTnMD registers (see SFR Definition 8.2). Selecting a longer response time reduces the Comparator supply current. See Table 5.12 for complete timing and supply current requirements.

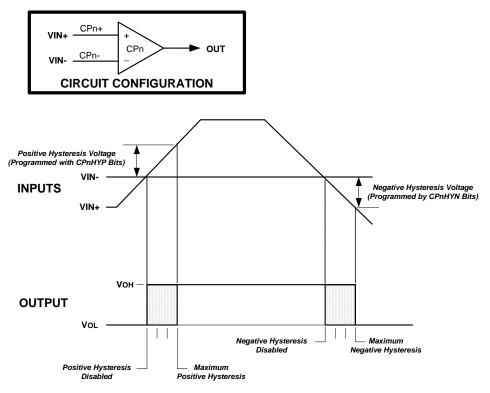

Comparator hysteresis is software-programmable via its Comparator Control register CPTnCN.

The amount of negative hysteresis voltage is determined by the settings of the CPnHYN bits. As shown in Figure 8.2, various levels of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CPnHYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see "13. Interrupts" .) The CPnFIF flag is set to 1 upon a Comparator falling-edge, and the CPnRIF flag is set to 1 upon the Comparator rising-edge. Once set, these bits remain set until cleared by software. The output state of the Comparator can be obtained at any time by reading the CPnOUT bit. The Comparator is enabled by setting the CPnEN bit to 1, and is disabled by clearing this bit to 0.

## SFR Definition 8.3. CPT1CN: Comparator1 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP1EN | CP1OUT | CP1RIF | CP1FIF | CP1HYP[1:0] |   | CP1HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/          | W |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

#### SFR Address = 0x9D; SFR Page = 0x00

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP1EN       | Comparator1 Enable Bit.                                                       |

|     |             | 0: Comparator1 Disabled.                                                      |

|     |             | 1: Comparator1 Enabled.                                                       |

| 6   | CP1OUT      | Comparator1 Output State Flag.                                                |

|     |             | 0: Voltage on CP1+ < CP1                                                      |

|     |             | 1: Voltage on CP1+ > CP1                                                      |

| 5   | CP1RIF      | Comparator1 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator1 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator1 Rising Edge has occurred.                                      |

| 4   | CP1FIF      | Comparator1 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator1 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator1 Falling-Edge has occurred.                                     |

| 3:2 | CP1HYP[1:0] | Comparator1 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP1HYN[1:0] | Comparator1 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

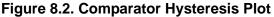

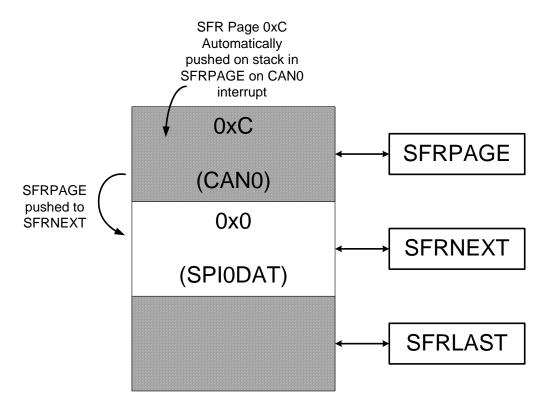

Figure 12.1. SFR Page Stack

Automatic hardware switching of the SFR Page on interrupts may be enabled or disabled as desired using the SFR Automatic Page Control Enable Bit located in the SFR Page Control Register (SFR0CN). This function defaults to "enabled" upon reset. In this way, the autoswitching function will be enabled unless disabled in software.

A summary of the SFR locations (address and SFR page) are provided in Table 12.3 in the form of an SFR memory map. Each memory location in the map has an SFR page row, denoting the page in which that SFR resides. Certain SFRs are accessible from ALL SFR pages, and are denoted by the "(ALL PAGES)" designation. For example, the Port I/O registers P0, P1, P2, and P3 all have the "(ALL PAGES)" designation, indicating these SFRs are accessible from all SFR pages regardless of the SFRPAGE register value.

While CIP-51 executes in-line code (writing values to SPI0DAT in this example), the CAN0 Interrupt occurs. The CIP-51 vectors to the CAN0 ISR and pushes the current SFR Page value (SFR Page 0x00) into SFRNEXT in the SFR Page Stack. The SFR page needed to access CAN's SFRs is then automatically placed in the SFRPAGE register (SFR Page 0x0C). SFRPAGE is considered the "top" of the SFR Page Stack. Software can now access the CAN0 SFRs. Software may switch to any SFR Page by writing a new value to the SFRPAGE register at any time during the CAN0 ISR to access SFRs that are not on SFR Page 0x0C. See Figure 12.3.

Figure 12.3. SFR Page Stack After CAN0 Interrupt Occurs

## 13. Interrupts

The C8051F55x/56x/57x devices include an extended interrupt system supporting a total of 18 interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regard-less of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE, EIE1, or EIE2). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

**Note:** Any instruction that clears a bit to disable an interrupt should be immediately followed by an instruction that has two or more opcode bytes. Using EA (global interrupt enable) as an example:

// in 'C': EA = 0; // clear EA bit. EA = 0; // this is a dummy instruction with two-byte opcode. ; in assembly: CLR EA ; clear EA bit. CLR EA ; this is a dummy instruction with two-byte opcode.

For example, if an interrupt is posted during the execution phase of a "CLR EA" opcode (or any instruction which clears a bit to disable an interrupt source), and the instruction is followed by a single-cycle instruction, the interrupt may be taken. However, a read of the enable bit will return a 0 inside the interrupt service routine. When the bit-clearing opcode is followed by a multi-cycle instruction, the interrupt will not be taken.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

### 13.1. MCU Interrupt Sources and Vectors

The C8051F55x/56x/57x MCUs support 18 interrupt sources. Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 13.1. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

### Table 13.1. Interrupt Summary

| Interrupt Source Interrupt Priority<br>Vector Order |        | Pending Flag | Bit addressable?                                                           | Cleared by HW? | Enable<br>Flag | Priority<br>Control |                    |

|-----------------------------------------------------|--------|--------------|----------------------------------------------------------------------------|----------------|----------------|---------------------|--------------------|

| Reset                                               | 0x0000 | Тор          | None                                                                       | N/A            | N/A            | Always<br>Enabled   | Always<br>Highest  |

| External Interrupt 0<br>(INT0)                      | 0x0003 | 0            | IE0 (TCON.1)                                                               | Y              | Y              | EX0 (IE.0)          | PX0 (IP.0)         |

| Timer 0 Overflow                                    | 0x000B | 1            | TF0 (TCON.5)                                                               | Y              | Y              | ET0 (IE.1)          | PT0 (IP.1)         |

| External Interrupt 1<br>(INT1)                      | 0x0013 | 2            | IE1 (TCON.3)                                                               | Y              | Y              | EX1 (IE.2)          | PX1 (IP.2)         |

| Timer 1 Overflow                                    | 0x001B | 3            | TF1 (TCON.7)                                                               | Y              | Y              | ET1 (IE.3)          | PT1 (IP.3)         |

| UART0                                               | 0x0023 | 4            | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y              | N              | ES0 (IE.4)          | PS0 (IP.4)         |

| Timer 2 Overflow                                    | 0x002B | 5            | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y              | N              | ET2 (IE.5)          | PT2 (IP.5)         |

| SPI0                                                | 0x0033 | 6            | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y              | N              | ESPI0<br>(IE.6)     | PSPI0<br>(IP.6)    |

| SMB0                                                | 0x003B | 7            | SI (SMB0CN.0)                                                              | Y              | Ν              | ESMB0<br>(EIE1.0)   | PSMB0<br>(EIP1.0)  |

| ADC0 Window Com-<br>pare                            | 0x0043 | 8            | ADOWINT<br>(ADC0CN.3)                                                      | Y              | N              | EWADC0<br>(EIE1.1)  | PWADC0<br>(EIP1.1) |

| ADC0 Conversion<br>Complete                         | 0x004B | 9            | AD0INT (ADC0CN.5)                                                          | Y              | N              | EADC0<br>(EIE1.2)   | PADC0<br>(EIP1.2)  |

| Programmable<br>Counter Array                       | 0x0053 | 10           | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)<br>COVF (PCA0PWM.6)                       | Y              | N              | EPCA0<br>(EIE1.3)   | PPCA0<br>(EIP1.3)  |

| Comparator0                                         | 0x005B | 11           | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | N              | N              | ECP0<br>(EIE1.4)    | PCP0<br>(EIP1.4)   |

| Comparator1                                         | 0x0063 | 12           | CP1FIF (CPT1CN.4)<br>CP1RIF (CPT1CN.5)                                     | N              | N              | ECP1<br>(EIE1.5)    | PCP1<br>(EIP1.5)   |

| Timer 3 Overflow                                    | 0x006B | 13           | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | N              | N              | ET3<br>(EIE1.6)     | PT3<br>(EIP1.6)    |

| LINO                                                | 0x0073 | 14           | LINOINT (LINST.3)                                                          | N              | N*             | ELIN0<br>(EIE1.7)   | PLIN0<br>(EIP1.7)  |

| Voltage Regulator<br>Dropout                        | 0x007B | 15           | N/A                                                                        | N/A            | N/A            | EREG0<br>(EIE2.0)   | PREG0<br>(EIP2.0)  |

| CAN0                                                | 0x0083 | 16           | CAN0INT<br>(CAN0CN.7)                                                      | N              | Y              | ECAN0<br>(EIE2.1)   | PCAN0<br>(EIP2.1)  |

| Port Match                                          | 0x008B | 17           | None                                                                       | N/A            | N/A            | EMAT<br>(EIE2.2)    | PMAT<br>(EIP2.2)   |

/RD

### 17.4. Multiplexed Mode

The External Memory Interface operates only in a Multiplexed mode. In Multiplexed mode, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. In this mode, an external latch (74HC373 or equivalent logic gate) is used to hold the lower 8-bits of the RAM address. The external latch is controlled by the ALE (Address Latch Enable) signal, which is driven by the External Memory Interface logic. An example of a Multiplexed Configuration is shown in Figure 17.1.

In Multiplexed mode, the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the Q outputs reflect the states of the 'D' inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time RD or WR is asserted.

A[15:8] A[15:8] ADDRESS BUS 74HC373 ALE G E ADDRESS/DATA BUS A[7:0] AD[7:0] Q D M  $V_{DD}$ 64 K X 8 SRAM (Optional) 8 F I/O[7:0] CE /WR WE

See Section "17.6.1. Multiplexed Mode" on page 153 for more information.

OE

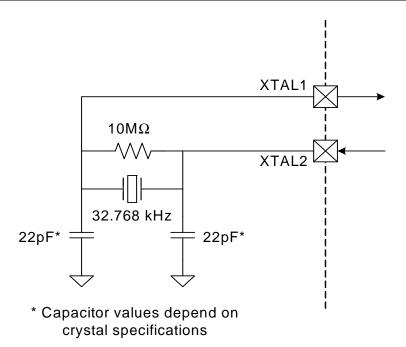

### 18.4. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 18.1. A 10 M $\Omega$  resistor also must be wired across the XTAL2 and XTAL1 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 18.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 18.6).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.2 and P0.3 are used as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.3 is used as XTAL2. The Port I/O Crossbar should be configured to skip the Port pins used by the oscillator circuit; see Section "19.3. Priority Crossbar Decoder" on page 172 for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as **analog inputs**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See Section "19.4. Port I/O Initialization" on page 174 for details on Port input mode selection.

### Figure 18.3. External 32.768 kHz Quartz Crystal Oscillator Connection Diagram

#### 18.4.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 18.1, Option 2. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation, according to Equation 18.1, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and R = the pull-up resistor value in k $\Omega$ .

$$f = 1.23 \times 10^3 / (R \times C)$$

### Equation 18.1. RC Mode Oscillator Frequency

For example: If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

f = 1.23(10<sup>3</sup>)/RC = 1.23(10<sup>3</sup>)/[246 x 50] = 0.1 MHz = 100 kHz

Referring to the table in SFR Definition 18.6, the required XFCN setting is 010b.

#### 18.4.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 18.1, Option 3. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation , where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and  $V_{DD}$  = the MCU power supply in Volts.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings. When the WEAKPUD bit in XBR2 is 0, a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a 0 to avoid unnecessary power dissipation.

Registers XBR0, XBR1, and XBR2 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR2 to 1 enables the Crossbar. Until the Crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table; as an alternative, the Configuration Wizard utility of the Silicon Labs IDE software will determine the Port I/O pin-assignments based on the XBRn Register settings.

The Crossbar must be enabled to use Port pins as standard Port I/O in output mode. Port output drivers are disabled while the Crossbar is disabled.

### SFR Definition 19.6. P1MASK: Port 1 Mask Register

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | P1MASK[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xF4; SFR Page = 0x00

| Bit | Name        | Function                                                                                                                                                                                            |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MASK[7:0] | Port 1 Mask Value.                                                                                                                                                                                  |

|     |             | Selects P1 pins to be compared to the corresponding bits in P1MAT.<br>0: P1.n pin logic value is ignored and cannot cause a Port Mismatch event.<br>1: P1.n pin logic value is compared to P1MAT.n. |

## SFR Definition 19.7. P1MAT: Port 1 Match Register

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|-----|---|---|---|---|---|---|--|

| Name  | P1MAT[7:0] |     |   |   |   |   |   |   |  |

| Туре  |            | R/W |   |   |   |   |   |   |  |

| Reset | 1          | 1   | 1 | 1 | 1 | 1 | 1 | 1 |  |

SFR Address = 0xF3; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                                                                   |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MAT[7:0] | Port 1 Match Value.                                                                                                                                                                        |

|     |            | Match comparison value used on Port 1 for bits in P1MAT which are set to 1.<br>0: P1.n pin logic value is compared with logic LOW.<br>1: P1.n pin logic value is compared with logic HIGH. |

### SFR Definition 19.13. P0MDIN: Port 0 Input Mode

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | POMDIN[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Address = 0xF1; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                  |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDIN[7:0] | Analog Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                                                                                                                                                                                                   |

|     |             | <ul> <li>Port pins configured for analog mode have their weak pull-up and digital receiver disabled. For analog mode, the pin also needs to be configured for open-drain mode in the P0MDOUT register.</li> <li>0: Corresponding P0.n pin is configured for analog mode.</li> <li>1: Corresponding P0.n pin is not configured for analog mode.</li> </ul> |

## SFR Definition 19.14. P0MDOUT: Port 0 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | P0MDOUT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xA4; SFR Page = 0x0F

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDOUT[7:0] | Output Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P0MDIN is logic 0.<br>0: Corresponding P0.n Output is open-drain.<br>1: Corresponding P0.n Output is push-pull. |

### LIN Register Definition 20.4. LIN0DTn: LIN0 Data Byte n

| Bit  | 7                                  | 6           | 5                | 4           | 3           | 2            | 1             | 0           |  |

|------|------------------------------------|-------------|------------------|-------------|-------------|--------------|---------------|-------------|--|

| Nam  | e                                  | DATAn[7:0]  |                  |             |             |              |               |             |  |

| Туре | 9                                  |             |                  | R/          | W           |              |               |             |  |

| Rese | et O                               | 0           | 0                | 0           | 0           | 0            | 0             | 0           |  |

|      | ct Address: LIN<br>0T6 = 0x05, LIN |             | ,                | ,           | DT3 = 0x02  | , LIN0DT4 =  | 0x03, LIN0I   | DT5 = 0x04, |  |

| Bit  | Name                               |             | Function         |             |             |              |               |             |  |

| 7:0  | DATAn[7:0]                         | LIN Data E  | _IN Data Byte n. |             |             |              |               |             |  |

|      |                                    | Serial Data | Byte that is     | received or | transmitted | across the L | IN interface. |             |  |

## 21. Controller Area Network (CAN0)

**Important Documentation Note**: The Bosch CAN Controller is integrated in the C8051F550/1/4/5, 'F560/ 1/4/5/8/9, and 'F572/3 devices. This section of the data sheet gives a description of the CAN controller as an overview and offers a description of how the Silicon Labs CIP-51 MCU interfaces with the on-chip Bosch CAN controller. In order to use the CAN controller, refer to Bosch's C\_CAN User's Manual as an accompanying manual to the Silicon Labs' data sheet.

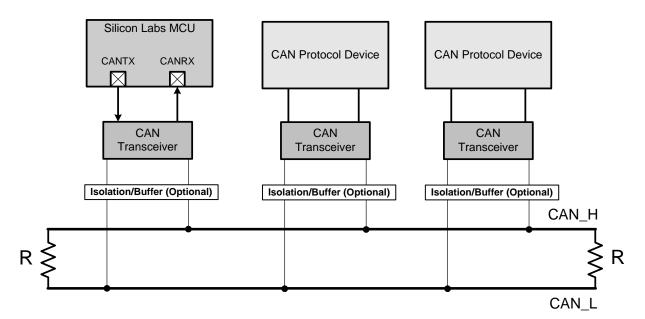

The C8051F550/1/4/5, 'F560/1/4/5/8/9, and 'F572/3 devices feature a Control Area Network (CAN) controller that enables serial communication using the CAN protocol. Silicon Labs CAN facilitates communication on a CAN network in accordance with the Bosch specification 2.0A (basic CAN) and 2.0B (full CAN). The CAN controller consists of a CAN Core, Message RAM (separate from the CIP-51 RAM), a message handler state machine, and control registers. Silicon Labs CAN is a protocol controller and does not provide physical layer drivers (i.e., transceivers). Figure 21.1 shows an example typical configuration on a CAN bus.

Silicon Labs' CAN operates at bit rates of up to 1 Mbit/second, though this can be limited by the physical layer chosen to transmit data on the CAN bus. The CAN processor has 32 Message Objects that can be configured to transmit or receive data. Incoming data, message objects and their identifier masks are stored in the CAN message RAM. All protocol functions for transmission of data and acceptance filtering is performed by the CAN controller and not by the CIP-51 MCU. In this way, minimal CPU bandwidth is needed to use CAN communication. The CIP-51 configures the CAN controller, accesses received data, and passes data for transmission via Special Function Registers (SFRs) in the CIP-51.

Figure 21.1. Typical CAN Bus Configuration

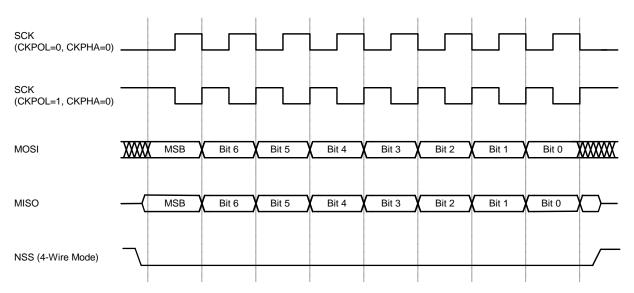

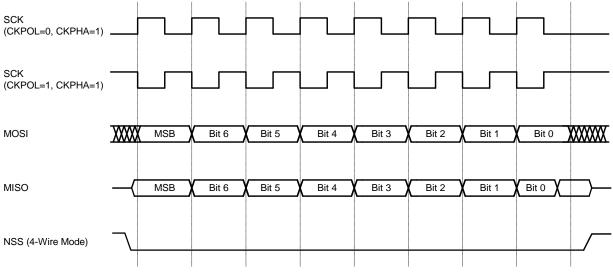

### 24.2. SPI0 Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPI0 is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.6). Writing a byte of data to the SPI0 data register (SPI0DAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPI0 master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPI0 master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPI0DAT.

When configured as a master, SPI0 can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSS-MD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPI0 when another master is accessing the bus. When NSS is pulled low in this mode, MSTEN (SPI0CN.6) and SPIEN (SPI0CN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODF, SPI0CN.5 = 1). Mode Fault will generate an interrupt if enabled. SPI0 must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 24.2 shows a connection diagram between two master devices in multiple-master mode.

3-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. In this mode, NSS is not used, and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 24.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSMD0 (SPI0CN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 24.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

### 24.6. SPI Special Function Registers

SPI0 is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI0 Bus are described in the following figures.

## SFR Definition 25.11. TMR2L: Timer 2 Low Byte

| Bit   | 7 | 6          | 5 | 4  | 3 | 2 | 1 | 0 |

|-------|---|------------|---|----|---|---|---|---|

| Name  |   | TMR2L[7:0] |   |    |   |   |   |   |

| Туре  |   |            |   | R/ | W |   |   |   |

| Reset | 0 | 0          | 0 | 0  | 0 | 0 | 0 | 0 |

SFR Address = 0xCC; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                          |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2L[7:0] | Timer 2 Low Byte.                                                                                                                                 |

|     |            | In 16-bit mode, the TMR2L register contains the low byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2L contains the 8-bit low byte timer value. |

### SFR Definition 25.12. TMR2H Timer 2 High Byte

| Bit   | 7 | 6          | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|---|------------|---|----|---|---|---|---|--|

| Name  |   | TMR2H[7:0] |   |    |   |   |   |   |  |

| Туре  |   |            |   | R/ | W |   |   |   |  |

| Reset | 0 | 0          | 0 | 0  | 0 | 0 | 0 | 0 |  |

SFR Address = 0xCD; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2H[7:0] | Timer 2 High Byte.                                                                                                                                  |

|     |            | In 16-bit mode, the TMR2H register contains the high byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2H contains the 8-bit high byte timer value. |

## SFR Definition 25.16. TMR3L: Timer 3 Low Byte

| Bit   | 7 | 6          | 5 | 4  | 3 | 2 | 1 | 0 |

|-------|---|------------|---|----|---|---|---|---|

| Name  |   | TMR3L[7:0] |   |    |   |   |   |   |

| Туре  |   |            |   | R/ | W |   |   |   |

| Reset | 0 | 0          | 0 | 0  | 0 | 0 | 0 | 0 |

SFR Address = 0x94; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                          |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3L[7:0] | Timer 3 Low Byte.                                                                                                                                 |

|     |            | In 16-bit mode, the TMR3L register contains the low byte of the 16-bit Timer 3. In 8-<br>bit mode, TMR3L contains the 8-bit low byte timer value. |

### SFR Definition 25.17. TMR3H Timer 3 High Byte

| Bit   | 7          | 6 | 5 | 4  | 3 | 2 | 1 | 0 |

|-------|------------|---|---|----|---|---|---|---|

| Name  | TMR3H[7:0] |   |   |    |   |   |   |   |

| Туре  |            |   |   | R/ | W |   |   |   |

| Reset | 0          | 0 | 0 | 0  | 0 | 0 | 0 | 0 |

SFR Address = 0x95; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3H[7:0] | Timer 3 High Byte.                                                                                                                                  |

|     |            | In 16-bit mode, the TMR3H register contains the high byte of the 16-bit Timer 3. In 8-<br>bit mode, TMR3H contains the 8-bit high byte timer value. |

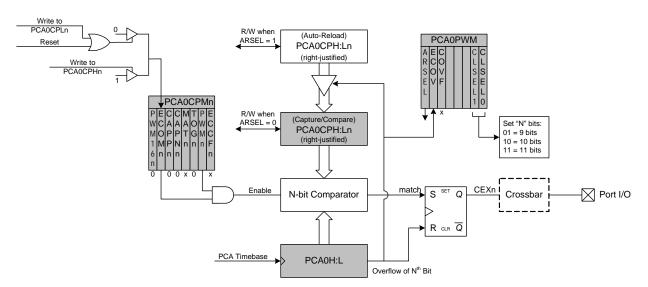

Figure 26.9. PCA 9, 10 and 11-Bit PWM Mode Diagram

#### 26.3.6. 16-Bit Pulse Width Modulator Mode

A PCA module may also be operated in 16-Bit PWM mode. 16-bit PWM mode is independent of the other (8/9/10/11-bit) PWM modes. In this mode, the 16-bit capture/compare module defines the number of PCA clocks for the low time of the PWM signal. When the PCA counter matches the module contents, the output on CEXn is asserted high; when the 16-bit counter overflows, CEXn is asserted low. To output a varying duty cycle, new value writes should be synchronized with PCA CCFn match interrupts. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register. For a varying duty cycle, match interrupts should be enabled (ECCFn = 1 AND MATn = 1) to help synchronize the capture/compare register writes. If the MATn bit is set to 1, the CCFn flag for the module will be set each time a 16-bit comparator match (rising edge) occurs. The CF flag in PCA0CN can be used to detect the overflow (falling edge). The duty cycle for 16-Bit PWM Mode is given by Equation 26.4.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

$Duty Cycle = \frac{(65536 - PCA0CPn)}{65536}$

#### Equation 26.4. 16-Bit PWM Duty Cycle

Using Equation 26.4, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is 0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.