Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), CANbus, SPI, UART/USART       |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 25x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f565-im |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

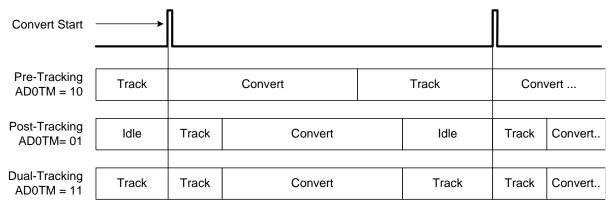

Post-Tracking Mode is selected when AD0TM is set to 01b. A programmable tracking time based on AD0TK is started immediately following the convert start signal. Conversions are started after the programmed tracking time ends. After a conversion is complete, ADC0 does not track the input. Rather, the sampling capacitor remains disconnected from the input making the input pin high-impedance until the next convert start signal.

Dual-Tracking Mode is selected when AD0TM is set to 11b. A programmable tracking time based on AD0TK is started immediately following the convert start signal. Conversions are started after the programmed tracking time ends. After a conversion is complete, ADC0 tracks continuously until the next conversion is started.

Depending on the output connected to the ADC input, additional tracking time, more than is specified in Table 5.9, may be required after changing MUX settings. See the settling time requirements described in Section "6.2.1. Settling Time Requirements" on page 52.

Figure 6.2. ADC0 Tracking Modes

#### 6.1.3. Timing

ADC0 has a maximum conversion speed specified in Table 5.9. ADC0 is clocked from the ADC0 Subsystem Clock (FCLK). The source of FCLK is selected based on the BURSTEN bit. When BURSTEN is logic 0, FCLK is derived from the current system clock. When BURSTEN is logic 1, FCLK is derived from the Burst Mode Oscillator, an independent clock source with a maximum frequency of 25 MHz.

When ADC0 is performing a conversion, it requires a clock source that is typically slower than FCLK. The ADC0 SAR conversion clock (SAR clock) is a divided version of FCLK. The divide ratio can be configured using the AD0SC bits in the ADC0CF register. The maximum SAR clock frequency is listed in Table 5.9.

ADC0 can be in one of three states at any given time: tracking, converting, or idle. Tracking time depends on the tracking mode selected. For Pre-Tracking Mode, tracking is managed by software and ADC0 starts conversions immediately following the convert start signal. For Post-Tracking and Dual-Tracking Modes, the tracking time after the convert start signal is equal to the value determined by the AD0TK bits plus 2 FCLK cycles. Tracking is immediately followed by a conversion. The ADC0 conversion time is always 13 SAR clock cycles plus an additional 2 FCLK cycles to start and complete a conversion. Figure 6.3 shows timing diagrams for a conversion in Pre-Tracking Mode and tracking plus conversion in Post-Tracking or Dual-Tracking Mode. In this example, repeat count is set to one.

# Gain Register Definition 6.3. ADC0GNA: ADC0 Additional Selectable Gain

| Bit     | 7             | 6            | 5        | 4        | 3        | 2        | 1        | 0       |

|---------|---------------|--------------|----------|----------|----------|----------|----------|---------|

| Nam     | e Reserved    | Reserved     | Reserved | Reserved | Reserved | Reserved | Reserved | GAINADD |

| Туре    | W             | W            | W        | W        | W        | W        | W        | W       |

| Rese    | <b>t</b> 0    | 0            | 0        | 0        | 0        | 0        | 0        | 1       |

| Indired | t Address = 0 | x08;         |          |          |          |          |          |         |

| Bit     | Name          | Function     |          |          |          |          |          |         |

| 7:1     | Reserved      | Must Write ( | 000000b. |          |          |          |          |         |

| 7:1  | Reserved                                                                                             | Must Write 000000b.                                                                            |  |  |  |  |  |  |

|------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0    | GAINADD                                                                                              | ADC0 Additional Gain Bit.                                                                      |  |  |  |  |  |  |

|      |                                                                                                      | Setting this bit add 1/64 (0.016) gain to the gain value in the ADC0GNH and ADC0GNL registers. |  |  |  |  |  |  |

| Note | Note: This register is accessed indirectly; See Section 6.3.2 for details for writing this register. |                                                                                                |  |  |  |  |  |  |

# SFR Definition 12.2. SFRPAGE: SFR Page

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|--------------|---|---|---|---|---|---|--|--|

| Name  |   | SFRPAGE[7:0] |   |   |   |   |   |   |  |  |

| Туре  |   | R/W          |   |   |   |   |   |   |  |  |

| Reset | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

#### SFR Address = 0xA7; SFR Page = All Pages

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SFRPAGE[7:0] | SFR Page Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |              | Represents the SFR Page the C8051 core uses when reading or modifying SFRs.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |              | Write: Sets the SFR Page.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |              | Read: Byte is the SFR page the C8051 core is using.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |              | When enabled in the SFR Page Control Register (SFR0CN), the C8051 core will automatically switch to the SFR Page that contains the SFRs of the corresponding peripheral/function that caused the interrupt, and return to the previous SFR page upon return from interrupt (unless SFR Stack was altered before a returning from the interrupt). SFRPAGE is the top byte of the SFR Page Stack, and push/pop events of this stack are caused by interrupts (and not by reading/writing to the SFRPAGE register) |

## SFR Definition 13.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7     | 6   | 5    | 4    | 3     | 2     | 1      | 0     |

|-------|-------|-----|------|------|-------|-------|--------|-------|

| Name  | ELIN0 | ET3 | ECP1 | ECP0 | EPCA0 | EADC0 | EWADC0 | ESMB0 |

| Туре  | R/W   | R/W | R/W  | R/W  | R/W   | R/W   | R/W    | R/W   |

| Reset | 0     | 0   | 0    | 0    | 0     | 0     | 0      | 0     |

#### SFR Address = 0xE6; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                                          |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ELIN0  | Enable LIN0 Interrupt.<br>This bit sets the masking of the LIN0 interrupt.<br>0: Disable LIN0 interrupts.<br>1: Enable interrupt requests generated by the LIN0INT flag.                                                                                                          |

| 6   | ET3    | <ul> <li>Enable Timer 3 Interrupt.</li> <li>This bit sets the masking of the Timer 3 interrupt.</li> <li>0: Disable Timer 3 interrupts.</li> <li>1: Enable interrupt requests generated by the TF3L or TF3H flags.</li> </ul>                                                     |

| 5   | ECP1   | Enable Comparator1 (CP1) Interrupt.<br>This bit sets the masking of the CP1 interrupt.<br>0: Disable CP1 interrupts.<br>1: Enable interrupt requests generated by the CP1RIF or CP1FIF flags.                                                                                     |

| 4   | ECP0   | Enable Comparator0 (CP0) Interrupt.<br>This bit sets the masking of the CP0 interrupt.<br>0: Disable CP0 interrupts.<br>1: Enable interrupt requests generated by the CP0RIF or CP0FIF flags.                                                                                     |

| 3   | EPCA0  | <ul> <li>Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> </ul>                                              |

| 2   | EADC0  | <ul> <li>Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> </ul>          |

| 1   | EWADC0 | <ul> <li>Enable Window Comparison ADC0 Interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ul> |

| 0   | ESMB0  | Enable SMBus (SMB0) Interrupt.<br>This bit sets the masking of the SMB0 interrupt.<br>0: Disable all SMB0 interrupts.<br>1: Enable interrupt requests generated by SMB0.                                                                                                          |

| Bit   | 7            | 6                                             | 5                                                                                                                                                                                                                   | 4        | 3        | 2        | 1        | 0      |

|-------|--------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|--------|

| Nam   | e Reserved   | Reserved                                      | CHPFEN                                                                                                                                                                                                              | Reserved | Reserved | Reserved | Reserved | CHBLKW |

| Туре  | R/W          | R/W                                           | R/W                                                                                                                                                                                                                 | R/W      | R/W      | R/W      | R/W      | R/W    |

| Rese  | <b>t</b> 0   | 0                                             | 1                                                                                                                                                                                                                   | 0        | 0        | 0        | 0        | 0      |

| SFR A | ddress = 0xE | 3; SFR Page                                   | = 0x0F                                                                                                                                                                                                              |          |          |          |          |        |

| Bit   | Name         | -                                             |                                                                                                                                                                                                                     |          | Function |          |          |        |

| 7:6   | Reserved     | Must Write 0                                  | 0b                                                                                                                                                                                                                  |          |          |          |          |        |

| 5     | CHPFEN       | Cache Prefe<br>0: Prefetch e<br>1: Prefetch e | ngine is disa                                                                                                                                                                                                       | abled.   |          |          |          |        |

| 4:1   | Reserved     | Must Write 0                                  | 000b.                                                                                                                                                                                                               |          |          |          |          |        |

| 0     | CHBLKW       | This bit allow<br>0: Each byte                | ust Write 0000b.<br>ock Write Enable Bit.<br>is bit allows block writes to Flash memory from firmware.<br>Each byte of a software Flash write is written individually.<br>Flash bytes are written in groups of two. |          |          |          |          |        |

## SFR Definition 14.5. ONESHOT: Flash Oneshot Period

| Bit   | 7 | 6 | 5 | 4 | 3           | 2   | 1   | 0   |

|-------|---|---|---|---|-------------|-----|-----|-----|

| Name  |   |   |   |   | PERIOD[3:0] |     |     |     |

| Туре  | R | R | R | R | R/W         | R/W | R/W | R/W |

| Reset | 0 | 0 | 0 | 0 | 1           | 1   | 1   | 1   |

#### SFR Address = 0xBE; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                  |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Unused      | Read = 0000b. Write = don't care.                                                                                                                                                                                                                                                         |

| 3:0 | PERIOD[3:0] | <b>Oneshot Period Control Bits.</b><br>These bits limit the internal Flash read strobe width as follows. When the Flash read strobe is de-asserted, the Flash memory enters a low-power state for the remainder of the system clock cycle.<br>$FLASH_{RDMAX} = 5ns + (PERIOD \times 5ns)$ |

#### 15.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the controller core to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the device performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100  $\mu$ s.

#### 15.3. Suspend Mode

Setting the SUSPEND bit (OSCICN.5) causes the hardware to halt the CPU and the high-frequency internal oscillator, and go into Suspend mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. Most digital peripherals are not active in Suspend mode. The exception to this is the Port Match feature.

Suspend mode can be terminated by three types of events, a port match (described in Section "19.5. Port Match" on page 179), a Comparator low output (if enabled), or a device reset event. When Suspend mode is terminated, the device will continue execution on the instruction following the one that set the SUSPEND bit. If the wake event was configured to generate an interrupt, the interrupt will be serviced upon waking the device. If Suspend mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

Note: Before entering suspend mode, firmware must set the ZTCEN bit in REF0CN (SFR Definition 7.1).

# SFR Definition 15.1. PCON: Power Control

| Bit   | 7 | 6 | 5    | 4    | 3   | 2 | 1 | 0 |

|-------|---|---|------|------|-----|---|---|---|

| Name  |   |   | STOP | IDLE |     |   |   |   |

| Туре  |   |   |      | R/W  | R/W |   |   |   |

| Reset | 0 | 0 | 0    | 0    | 0   | 0 | 0 | 0 |

SFR Address = 0x87; SFR Page = All Pages

| Bit | Name    | Function                                                                                                                                                                                                                                                                   |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | GF[5:0] | General Purpose Flags 5–0.<br>These are general purpose flags for use under software control.                                                                                                                                                                              |

| 1   | STOP    | Stop Mode Select.Setting this bit will place the CIP-51 in Stop mode. This bit will always be read as 0.1: CPU goes into Stop mode (internal oscillator stopped).                                                                                                          |

| 0   | IDLE    | <b>IDLE: Idle Mode Select.</b><br>Setting this bit will place the CIP-51 in Idle mode. This bit will always be read as 0.<br>1: CPU goes into Idle mode. (Shuts off clock to CPU, but clock to Timers, Interrupts, Serial Ports, and Analog Peripherals are still active.) |

# SFR Definition 18.3. OSCICRS: Internal Oscillator Coarse Calibration

| Bit    | 7            | 6           | 5            | 4         | 3      | 2      | 1      | 0      |  |  |  |  |

|--------|--------------|-------------|--------------|-----------|--------|--------|--------|--------|--|--|--|--|

| Name   |              |             | OSCICRS[6:0] |           |        |        |        |        |  |  |  |  |

| Туре   | R            |             | R/W          |           |        |        |        |        |  |  |  |  |

| Reset  | 0            | Varies      | Varies       | Varies    | Varies | Varies | Varies | Varies |  |  |  |  |

| SFR Ac | dress = 0xA2 | 2; SFR Page | e = 0x0F     |           |        |        |        | •      |  |  |  |  |

| Bit    | Name         |             | Function     |           |        |        |        |        |  |  |  |  |

| 7      | Unused       | Read =      | 0. Write = D | on't Care |        |        |        |        |  |  |  |  |

| 7   | Unused       | Read = 0; Write = Don't Care                                                                                                                                                                                                                                                                                     |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0 | OSCICRS[6:0] | Internal Oscillator Coarse Calibration Bits.                                                                                                                                                                                                                                                                     |

|     |              | These bits determine the internal oscillator period. When set to 0000000b, the internal oscillator operates at its slowest setting. When set to 1111111b, the internal oscillator operates at its fastest setting. The reset value is factory calibrated to generate an internal oscillator frequency of 24 MHz. |

#### SFR Definition 18.4. OSCIFIN: Internal Oscillator Fine Calibration

| Bit   | 7 | 6 | 5      | 4      | 3      | 2       | 1      | 0      |

|-------|---|---|--------|--------|--------|---------|--------|--------|

|       |   |   |        |        | OSCIF  | IN[5:0] |        |        |

| Туре  | R | R |        |        | R/     | W       |        |        |

| Reset | 0 | 0 | Varies | Varies | Varies | Varies  | Varies | Varies |

#### SFR Address = 0x9E; SFR Page = 0x0F

| Bit | Name         | Function                                                                                                                                                         |  |  |  |  |  |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:6 | Unused       | Read = 00b; Write = Don't Care                                                                                                                                   |  |  |  |  |  |

| 5:0 | OSCIFIN[5:0] | ernal Oscillator Fine Calibration Bits.                                                                                                                          |  |  |  |  |  |

|     |              | These bits are fine adjustment for the internal oscillator period. The reset value is factory calibrated to generate an internal oscillator frequency of 24 MHz. |  |  |  |  |  |

# SFR Definition 18.5. CLKMUL: Clock Multiplier

| Bit   | 7     | 6       | 5      | 4 | 3           | 2     | 1           | 0 |  |  |

|-------|-------|---------|--------|---|-------------|-------|-------------|---|--|--|

| Name  | MULEN | MULINIT | MULRDY |   | MULDIV[2:0] | MULSI | MULSEL[1:0] |   |  |  |

| Туре  | R/W   | R/W     | R      |   | R/W         |       | R/W         |   |  |  |

| Reset | 0     | 0       | 0      | 0 | 0           | 0     | 0           | 0 |  |  |

#### SFR Address = 0x97; SFR Page = 0x0F

| Bit   | Name        |                                      | Function                                                                                                          |                                                                           |  |  |  |  |  |  |  |  |  |

|-------|-------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 7     | MULEN       | Clock Multiplie<br>0: Clock Multipli |                                                                                                                   |                                                                           |  |  |  |  |  |  |  |  |  |

|       |             | 1: Clock Multipli                    |                                                                                                                   |                                                                           |  |  |  |  |  |  |  |  |  |

| 6     | MULINIT     | Clock Multiplie                      | r Initialize.                                                                                                     |                                                                           |  |  |  |  |  |  |  |  |  |

|       |             |                                      | the Clock Multiplier. The MULRD                                                                                   | . Once enabled, writing a 1 to this<br>Y bit reads 1 when the Clock Mul-  |  |  |  |  |  |  |  |  |  |

| 5     | MULRDY      | Clock Multiplie                      | ock Multiplier Ready.                                                                                             |                                                                           |  |  |  |  |  |  |  |  |  |

|       |             |                                      | : Clock Multiplier is not ready.<br>: Clock Multiplier is ready (PLL is locked).                                  |                                                                           |  |  |  |  |  |  |  |  |  |

| 4:2   | MULDIV[2:0] | Clock Multiplie                      | ock Multiplier Output Scaling Factor.                                                                             |                                                                           |  |  |  |  |  |  |  |  |  |

|       |             |                                      | 00: Clock Multiplier Output scaled by a factor of 1.                                                              |                                                                           |  |  |  |  |  |  |  |  |  |

|       |             |                                      | 01: Clock Multiplier Output scaled by a factor of 1.                                                              |                                                                           |  |  |  |  |  |  |  |  |  |

|       |             |                                      | 010: Clock Multiplier Output scaled by a factor of 1.<br>011: Clock Multiplier Output scaled by a factor of 2/3*. |                                                                           |  |  |  |  |  |  |  |  |  |

|       |             |                                      | iplier Output scaled by a factor o                                                                                |                                                                           |  |  |  |  |  |  |  |  |  |

|       |             |                                      | iplier Output scaled by a factor o                                                                                |                                                                           |  |  |  |  |  |  |  |  |  |

|       |             |                                      | plier Output scaled by a factor o                                                                                 |                                                                           |  |  |  |  |  |  |  |  |  |

|       |             |                                      | plier Output scaled by a factor of                                                                                |                                                                           |  |  |  |  |  |  |  |  |  |

|       |             |                                      | ck Multiplier output duty cycle is i                                                                              | not 50% for these settings.                                               |  |  |  |  |  |  |  |  |  |

| 1:0   | MULSEL[1:0] | Clock Multiplie                      | •                                                                                                                 |                                                                           |  |  |  |  |  |  |  |  |  |

|       |             | These bits selec                     | ct the clock supplied to the Clock                                                                                | Multiplier                                                                |  |  |  |  |  |  |  |  |  |

|       |             | MULSEL[1:0]                          | Selected Input Clock                                                                                              | Clock Multiplier Output<br>for MULDIV[2:0] = 000b                         |  |  |  |  |  |  |  |  |  |

|       |             | 00                                   | Internal Oscillator                                                                                               | Internal Oscillator x 2                                                   |  |  |  |  |  |  |  |  |  |

|       |             | 01                                   | External Oscillator                                                                                               | External Oscillator x 2                                                   |  |  |  |  |  |  |  |  |  |

|       |             | 10                                   | Internal Oscillator                                                                                               | Internal Oscillator x 4                                                   |  |  |  |  |  |  |  |  |  |

|       |             | 11                                   | External Oscillator                                                                                               | External Oscillator x 4                                                   |  |  |  |  |  |  |  |  |  |

| Notes |             |                                      | IHz, and so the Clock Multiplier outp<br>Oscillator x 2 is selected using the N                                   | but should be scaled accordingly.<br>MULSEL bits, MULDIV[2:0] is ignored. |  |  |  |  |  |  |  |  |  |

| Port    | P0 |   |   |   | 0 | <i>.</i> |   |   |   |   |   | Р | 1 | ÷ | • |   |   |   |   | Р    | 2   |                     |      |      |    | <i>.</i>                                           |   | Р | 3 |   | j. |   | Ρ4 |

|---------|----|---|---|---|---|----------|---|---|---|---|---|---|---|---|---|---|---|---|---|------|-----|---------------------|------|------|----|----------------------------------------------------|---|---|---|---|----|---|----|

|         |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   | a | vail | abl | 2.7<br>e oi<br>in p | n 4( | 0-pi | in | P3.1-P3.7, P4.0<br>available on 40-pin<br>packages |   |   |   |   |    |   |    |

| PIN I/O | 0  | 1 | 2 | 3 | 4 | 5        | 6 | 7 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3    | 4   | 5                   | 6    | 7    | 0  | 1                                                  | 2 | 3 | 4 | 5 | 6  | 7 | 0  |

| UART_TX |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| UART_RX |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| CAN_TX  |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| CAN_RX  |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| SCK     |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| MISO    |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| MOSI    |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| NSS     |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| SDA     |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| SCL     |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| CP0     |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| CP0A    |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| CP1     |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| CP1A    |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| SYSCLK  |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| CEX0    |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| CEX1    |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| CEX2    |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| CEX3    |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| CEX4    |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| CEX5    |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| ECI     |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| Т0      |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| T1      |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| LIN_TX  |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

| LIN_RX  |    |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |                     |      |      |    |                                                    |   |   |   |   |    |   |    |

Figure 19.3. Peripheral Availability on Port I/O Pins

Registers XBR0, XBR1, and XBR2 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL); and similarly when the UART, CAN or LIN are selected, the Crossbar assigns both pins associated with the peripheral (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.4; UART RX0 is always assigned to P0.5. CAN0 pin assignments are fixed to P0.6 for CAN\_TX and P0.7 for CAN\_RX. Standard Port I/Os appear contiguously after the prioritized functions have been assigned.

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, pending the state of the NSS-MD1–NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

As an example configuration, if CAN0, SPI0 in 4-wire mode, and PCA0 Modules 0, 1, and 2 are enabled on the crossbar with P0.1, P0.2, and P0.5 skipped, the registers should be set as follows: XBR0 = 0x06 (CAN0 and SPI0 enabled), XBR1 = 0x0C (PCA0 modules 0, 1, and 2 enabled), XBR2 = 0x40 (Crossbar enabled), and P0SKIP = 0x26 (P0.1, P0.2, and P0.5 skipped). The resulting crossbar would look as shown in Figure 19.4.

# SFR Definition 19.19. P1SKIP: Port 1 Skip

| Bit   | 7 | 6 | 5 | 4    | 3       | 2 | 1 | 0 |

|-------|---|---|---|------|---------|---|---|---|

| Name  |   | · |   | P1SK | IP[7:0] |   |   |   |

| Туре  |   |   |   | R/   | W       |   |   |   |

| Reset | 0 | 0 | 0 | 0    | 0       | 0 | 0 | 0 |

SFR Address = 0xD5; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1SKIP[7:0] | Port 1 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 1 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P1.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P1.n pin is skipped by the Crossbar.</li> </ul> |

### SFR Definition 19.20. P2: Port 2

| Bit   | 7   | 6 | 5 | 4   | 3    | 2 | 1   | 0 |  |  |  |

|-------|-----|---|---|-----|------|---|-----|---|--|--|--|

| Name  |     |   |   | P2[ | 7:0] |   |     |   |  |  |  |

| Туре  | R/W |   |   |     |      |   |     |   |  |  |  |

| Reset | 1   | 1 | 1 | 1   | 1    | 1 | 1 1 |   |  |  |  |

SFR Address = 0xA0; SFR Page = All Pages; Bit-Addressable

| Bit   | Name                                                         | Description                                                                                                                                  | Write                                                                         | Read                                                                    |  |  |  |  |  |  |  |

|-------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7:0   | P2[7:0]                                                      | <b>Port 2Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P2.n Port pin is logic<br>LOW.<br>1: P2.n Port pin is logic<br>HIGH. |  |  |  |  |  |  |  |

| Note: | Note: P2.2-P2.7 are available on 40-pin and 32-pin packages. |                                                                                                                                              |                                                                               |                                                                         |  |  |  |  |  |  |  |

## SFR Definition 19.25. P3MDIN: Port 3 Input Mode

| Bit   | 7 | 6               | 5 | 4    | 3       | 2 | 1 | 0 |  |  |

|-------|---|-----------------|---|------|---------|---|---|---|--|--|

| Name  |   |                 |   | P3MD | IN[7:0] |   |   |   |  |  |

| Туре  |   |                 |   | R/   | W       |   |   |   |  |  |

| Reset | 1 | 1 1 1 1 1 1 1 1 |   |      |         |   |   |   |  |  |

#### SFR Address = 0xF4; SFR Page = 0x0F

| Bit   | Name                                                                                            | Function                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0   | P3MDIN[7:0]                                                                                     | Analog Configuration Bits for P3.7–P3.0 (respectively).                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|       |                                                                                                 | <ul> <li>Port pins configured for analog mode have their weak pull-up and digital receiver disabled. For analog mode, the pin also needs to be configured for open-drain mode in the P3MDOUT register.</li> <li>0: Corresponding P3.n pin is configured for analog mode.</li> <li>1: Corresponding P3.n pin is not configured for analog mode.</li> </ul> |  |  |  |  |

| Note: | te: P3.0 is available on 40-pin and 32-pin packages. P3.1-P3.7 are available on 40-pin packages |                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

## SFR Definition 19.26. P3MDOUT: Port 3 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | P3MDOUT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xAE; SFR Page = 0x0F

| Bit   | Name                                                                                           | Function                                                                                                                                                                    |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | P3MDOUT[7:0]                                                                                   | Output Configuration Bits for P3.7–P3.0 (respectively).                                                                                                                     |  |  |  |  |  |

|       |                                                                                                | These bits are ignored if the corresponding bit in register P3MDIN is logic 0.<br>0: Corresponding P3.n Output is open-drain.<br>1: Corresponding P3.n Output is push-pull. |  |  |  |  |  |

| Note: | e: P3.0 is available on 40-pin and 32-pin packages. P3.1-P3.7 are available on 40-pin packages |                                                                                                                                                                             |  |  |  |  |  |

#### LIN Register Definition 20.11. LIN0ID: LIN0 Identifier Register

| Bit   | 7 | 6 | 5 | 4       | 3 | 2 | 1 | 0 |

|-------|---|---|---|---------|---|---|---|---|

| Name  |   |   |   | ID[5:0] |   |   |   |   |

| Туре  | R | R |   | R/W     |   |   |   |   |

| Reset | 0 | 0 | 0 | 0       | 0 | 0 | 0 | 0 |

Indirect Address = 0x0E

| Bit | Name    | Function                                                                                                                                                                                                                                                       |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused  | Read = 00b; Write = Don't Care.                                                                                                                                                                                                                                |

| 5:0 | ID[5:0] | LIN Identifier Bits.<br>These bits form the data identifier.<br>If the LINSIZE bits (LINOSIZE[3:0]) are 1111b, bits ID[5:4] are used to determine the<br>data size and are interpreted as follows:<br>00: 2 bytes<br>01: 2 bytes<br>10: 4 bytes<br>11: 8 bytes |

| Baud Rate | SYSCLK                                                       | v 1 | v | 1         |

|-----------|--------------------------------------------------------------|-----|---|-----------|

| Daug Nale | $= \frac{313021 \text{K}}{(65536 - (\text{SBRLH0:SBRLL0}))}$ | ^ 2 | ^ | Prescaler |

### Equation 23.1. UART0 Baud Rate

A quick reference for typical baud rates and clock frequencies is given in Table 23.1.

|        | Target Baud | Actual Baud | Baud Rate | Oscillator | SB0PS[1:0]       | Reload Value in |

|--------|-------------|-------------|-----------|------------|------------------|-----------------|

|        | Rate (bps)  | Rate (bps)  | Error     | Divide     | (Prescaler Bits) | SBRLH0:SBRLL0   |

|        |             |             |           | Factor     |                  |                 |

|        | 230400      | 230769      | 0.16%     | 208        | 11               | 0xFF98          |

|        | 115200      | 115385      | 0.16%     | 416        | 11               | 0xFF30          |

| : 48   | 57600       | 57554       | 0.08%     | 834        | 11               | 0xFE5F          |

| Ш<br>Ц | 28800       | 28812       | 0.04%     | 1666       | 11               | 0xFCBF          |

| SYSCLK | 14400       | 14397       | 0.02%     | 3334       | 11               | 0xF97D          |

| SYS    | 9600        | 9600        | 0.00%     | 5000       | 11               | 0xF63C          |

| .,     | 2400        | 2400        | 0.00%     | 20000      | 11               | 0xD8F0          |

|        | 1200        | 1200        | 0.00%     | 40000      | 11               | 0xB1E0          |

|        | 230400      | 230769      | 0.16%     | 104        | 11               | 0xFFCC          |

|        | 115200      | 115385      | 0.16%     | 208        | 11               | 0xFF98          |

| 24     | 57600       | 57692       | 0.16%     | 416        | 11               | 0xFF30          |

| н<br>Т | 28800       | 28777       | 0.08%     | 834        | 11               | 0xFE5F          |

| SYSCLK | 14400       | 14406       | 0.04%     | 1666       | 11               | 0xFCBF          |

| SYS    | 9600        | 9600        | 0.00%     | 2500       | 11               | 0xFB1E          |

| •,     | 2400        | 2400        | 0.00%     | 10000      | 11               | 0xEC78          |

|        | 1200        | 1200        | 0.00%     | 20000      | 11               | 0xD8F0          |

|        | 230400      | 230769      | 0.16%     | 52         | 11               | 0xFFE6          |

|        | 115200      | 115385      | 0.16%     | 104        | 11               | 0xFFCC          |

| 12     | 57600       | 57692       | 0.16%     | 208        | 11               | 0xFF98          |

| =<br>T | 28800       | 28846       | 0.16%     | 416        | 11               | 0xFF30          |

| SYSCLK | 14400       | 14388       | 0.08%     | 834        | 11               | 0xFE5F          |

| SYS    | 9600        | 9600        | 0.00%     | 1250       | 11               | 0xFD8F          |

| Ŭ      | 2400        | 2400        | 0.00%     | 5000       | 11               | 0xF63C          |

|        | 1200        | 1200        | 0.00%     | 10000      | 11               | 0xEC78          |

#### Table 23.1. Baud Rate Generator Settings for Standard Baud Rates

| Bit   | 7    | 6     | 5     | 4    | 3    | 2    | 1   | 0   |

|-------|------|-------|-------|------|------|------|-----|-----|

| Name  | OVR0 | PERR0 | THRE0 | REN0 | TBX0 | RBX0 | TI0 | RI0 |

| Туре  | R/W  | R/W   | R     | R/W  | R/W  | R/W  | R/W | R/W |

| Reset | 0    | 0     | 1     | 0    | 0    | 0    | 0   | 0   |

# SFR Definition 23.2. SMOD0: Serial Port 0 Control

| Bit   | 7                                     | 6                                                                                                                                                                                             | 5                                                                                                                                                                                                                                                            | 4   | 3        | 2      | 1            | 0    |

|-------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|--------|--------------|------|

| Nam   | e MCE0                                | S0P                                                                                                                                                                                           | F[1:0]                                                                                                                                                                                                                                                       | PE0 | SOD      | L[1:0] | XBE0         | SBL0 |

| Туре  | r <b>pe</b> R/W R/W R R/W R/W R/W R/W |                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |     |          |        | R/W          | R/W  |

| Rese  | et 0 0 0 0 1 1 0                      |                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |     |          |        | 0            |      |

| SFR A | Address = 0                           | xA9; SFR Page                                                                                                                                                                                 | e = 0x00                                                                                                                                                                                                                                                     |     |          |        |              |      |

| Bit   | Name                                  |                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |     | Function |        |              |      |

| 7     | MCE0                                  | 0: RI0 will be                                                                                                                                                                                | Multiprocessor Communication Enable.<br>D: RIO will be activated if stop bit(s) are 1.<br>I: RIO will be activated if stop bit(s) and extra bit are 1. Extra bit must be enabled using<br>KBE0.                                                              |     |          |        |              |      |

| 6:5   | S0PT[1:0]                             | 00: Odd Parity<br>01: Even Parit                                                                                                                                                              | Parity Type Select Bits.<br>00: Odd Parity<br>01: Even Parity                                                                                                                                                                                                |     |          |        |              |      |

|       |                                       | 10: Mark Parit<br>11: Space Par                                                                                                                                                               | ity.                                                                                                                                                                                                                                                         |     |          |        |              |      |

| 4     | PE0                                   | This bit enable<br>by bits S0PT[<br>0: Hardware p                                                                                                                                             | <ul> <li>Parity Enable.</li> <li>This bit enables hardware parity generation and checking. The parity type is selected by bits S0PT[1:0] when parity is enabled.</li> <li>0: Hardware parity is disabled.</li> <li>1: Hardware parity is enabled.</li> </ul> |     |          |        |              |      |

| 3:2   | S0DL[1:0]                             | Data Length.<br>00: 5-bit data<br>01: 6-bit data<br>10: 7-bit data<br>11: 8-bit data                                                                                                          | Data Length.<br>00: 5-bit data<br>01: 6-bit data<br>10: 7-bit data                                                                                                                                                                                           |     |          |        |              |      |

| 1     | XBE0                                  | <b>Extra Bit Enable.</b><br>When enabled, the value of TBX0 will be appended to the data field<br>0: Extra Bit is disabled.<br>1: Extra Bit is enabled.                                       |                                                                                                                                                                                                                                                              |     |          |        |              |      |

| 0     | SBL0                                  | Stop Bit Length.<br>0: Short—stop bit is active for one bit time<br>1: Long—stop bit is active for two bit times (data length = 6, 7, or 8 bits), or 1.5 bit times<br>(data length = 5 bits). |                                                                                                                                                                                                                                                              |     |          |        | .5 bit times |      |

## SFR Definition 25.13. TMR3CN: Timer 3 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1 | 0      |

|-------|------|------|--------|--------|---------|-----|---|--------|

| Name  | TF3H | TF3L | TF3LEN | TF3CEN | T3SPLIT | TR3 |   | T3XCLK |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R | R/W    |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0 | 0      |

#### SFR Address = 0x91;SFR Page = 0x00

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF3H    | <b>Timer 3 High Byte Overflow Flag.</b><br>Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                                            |

| 6   | TF3L    | <b>Timer 3 Low Byte Overflow Flag.</b><br>Set by hardware when the Timer 3 low byte overflows from 0xFF to 0x00. TF3L will be set when the low byte overflows regardless of the Timer 3 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                          |

| 5   | TF3LEN  | <b>Timer 3 Low Byte Interrupt Enable.</b><br>When set to 1, this bit enables Timer 3 Low Byte interrupts. If Timer 3 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 3 overflows.                                                                                                                                                                                                                                                                                                                                  |

| 4   | TF3CEN  | Timer 3 Capture Mode Enable.0: Timer 3 Capture Mode is disabled.1: Timer 3 Capture Mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3   | T3SPLIT | Timer 3 Split Mode Enable.When this bit is set, Timer 3 operates as two 8-bit timers with auto-reload.0: Timer 3 operates in 16-bit auto-reload mode.1: Timer 3 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                                                                                 |

| 2   | TR3     | <b>Timer 3 Run Control.</b><br>Timer 3 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables<br>TMR3H only; TMR3L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                                                                |

| 1   | Unused  | Read = 0b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0   | T3XCLK  | <ul> <li>Timer 3 External Clock Select.</li> <li>This bit selects the external clock source for Timer 3. If Timer 3 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 3 Clock Select bits (T3MH and T3ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.</li> <li>0: Timer 3 clock is the system clock divided by 12.</li> <li>1: Timer 3 clock is the external clock divided by 8 (synchronized with SYSCLK).</li> </ul> |

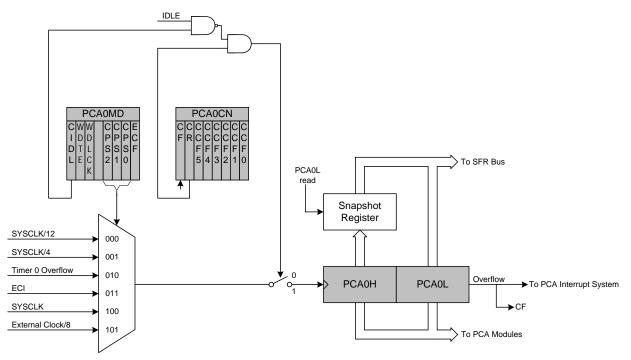

### 26.1. PCA Counter/Timer

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte (MSB) of the 16-bit counter/timer and PCA0L is the low byte (LSB). Reading PCA0L automatically latches the value of PCA0H into a "snapshot" register; the following PCA0H read accesses this "snapshot" register. **Reading the PCA0L Register first guarantees an accurate reading of the entire 16-bit PCA0 counter.** Reading PCA0H or PCA0L does not disturb the counter operation. The CPS[2:0] bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 26.1.

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the CPU is in Idle mode.

| CPS2                                                                                  | CPS1 | CPS0 | Timebase                                                        |  |  |

|---------------------------------------------------------------------------------------|------|------|-----------------------------------------------------------------|--|--|

| 0                                                                                     | 0    | 0    | System clock divided by 12.                                     |  |  |

| 0                                                                                     | 0    | 1    | System clock divided by 4.                                      |  |  |

| 0                                                                                     | 1    | 0    | Timer 0 overflow.                                               |  |  |

| 0                                                                                     | 1    | 1    | High-to-low transitions on ECI (max rate = system clock divided |  |  |

|                                                                                       |      |      | by 4).                                                          |  |  |

| 1                                                                                     | 0    | 0    | System clock.                                                   |  |  |

| 1                                                                                     | 0    | 1    | External oscillator source divided by 8.                        |  |  |

| 1                                                                                     | 1    | Х    | Reserved.                                                       |  |  |

| *Note: External oscillator source divided by 8 is synchronized with the system clock. |      |      |                                                                 |  |  |

Table 26.1. PCA Timebase Input Options

# C2 Register Definition 27.2. DEVICEID: C2 Device ID

| Bit                                                   | 7            | 6                                                                              | 5          | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------------------------------------------------------|--------------|--------------------------------------------------------------------------------|------------|---|---|---|---|---|--|--|--|

| Nam                                                   | e            | DEVICEID[7:0]                                                                  |            |   |   |   |   |   |  |  |  |

| Туре                                                  | 9            | R/W                                                                            |            |   |   |   |   |   |  |  |  |

| Rese                                                  | et 0         | 0                                                                              | 0          | 1 | 0 | 1 | 0 | 0 |  |  |  |

| C2 Address = 0xFD; SFR Address = 0xFD; SFR Page = 0xF |              |                                                                                |            |   |   |   |   |   |  |  |  |

| Bit                                                   | Name         |                                                                                | Function   |   |   |   |   |   |  |  |  |

| 7:0                                                   | DEVICEID[7:0 | Device I                                                                       | Device ID. |   |   |   |   |   |  |  |  |

|                                                       |              | This read-only register returns the 8-bit device ID: 0x22 (C8051F55x/56x/57x). |            |   |   |   |   |   |  |  |  |

### C2 Register Definition 27.3. REVID: C2 Revision ID

| Bit                                                   | 7          | 6                                                                                      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------------------------------------------------------|------------|----------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|--|

| Nam                                                   | e          | REVID[7:0]                                                                             |        |        |        |        |        |        |  |  |  |

| Туре                                                  | 9          | R/W                                                                                    |        |        |        |        |        |        |  |  |  |

| Rese                                                  | et Varies  | Varies                                                                                 | Varies | Varies | Varies | Varies | Varies | Varies |  |  |  |

| C2 Address = 0xFE; SFR Address = 0xFE; SFR Page = 0xF |            |                                                                                        |        |        |        |        |        |        |  |  |  |

| Bit                                                   | Name       | Function                                                                               |        |        |        |        |        |        |  |  |  |

| 7:0                                                   | REVID[7:0] | <b>Revision ID</b>                                                                     |        |        |        |        |        |        |  |  |  |

|                                                       |            | This read-only register returns the 8-bit revision ID. For example: 0x00 = Revision A. |        |        |        |        |        |        |  |  |  |

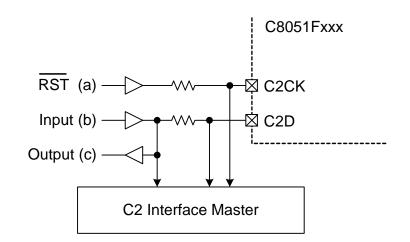

### 27.2. C2 Pin Sharing