Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore Processor8051Core Size8-BitSpeed50MHzConnectivitySMBus (2-Wire/I²C), CANbus, SPI, UART/USARTPeripheralsPOR, PWM, Temp Sensor, WDTNumber of I/O25Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size.National Size2.25K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.25VData ConvertersA/D 25x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core Size8-BitSpeed50MHzConnectivitySMBus (2-Wire/I²C), CANbus, SPI, UART/USARTPeripheralsPOR, PWM, Temp Sensor, WDTNumber of I/O25Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size2.25K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.25VData ConvertersA/D 25x12bOscillator TypeInternal                                                                                   |

| Speed50MHzConnectivitySMBus (2-Wire/I²C), CANbus, SPI, UART/USARTPeripheralsPOR, PWM, Temp Sensor, WDTNumber of I/O25Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size2.25K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.25VData ConvertersA/D 25x12bOscillator TypeInternal                                                                                                 |

| ConnectivitySMBus (2-Wire/I²C), CANbus, SPI, UART/USARTPeripheralsPOR, PWM, Temp Sensor, WDTNumber of I/O25Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size2.25K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.25VData ConvertersA/D 25x12bOscillator TypeInternal                                                                                                           |

| PeripheralsPOR, PWM, Temp Sensor, WDTNumber of I/O25Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size2.25K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.25VData ConvertersA/D 25x12bOscillator TypeInternal                                                                                                                                                                  |

| Number of I/O25Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size2.25K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.25VData ConvertersA/D 25x12bOscillator TypeInternal                                                                                                                                                                                                       |

| Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size2.25K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.25VData ConvertersA/D 25x12bOscillator TypeInternal                                                                                                                                                                                                                      |

| Program Memory TypeFLASHEEPROM Size-RAM Size2.25K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.25VData ConvertersA/D 25x12bOscillator TypeInternal                                                                                                                                                                                                                                                       |

| EEPROM Size-RAM Size2.25K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.25VData ConvertersA/D 25x12bOscillator TypeInternal                                                                                                                                                                                                                                                                               |

| RAM Size2.25K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 5.25VData ConvertersA/D 25x12bOscillator TypeInternal                                                                                                                                                                                                                                                                                           |

| Voltage - Supply (Vcc/Vdd)1.8V ~ 5.25VData ConvertersA/D 25x12bOscillator TypeInternal                                                                                                                                                                                                                                                                                                            |

| Data Converters     A/D 25x12b       Oscillator Type     Internal                                                                                                                                                                                                                                                                                                                                 |

| Oscillator Type Internal                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                   |

| Operating Temperature-40°C ~ 125°C (TA)                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                   |

| Mounting Type Surface Mount                                                                                                                                                                                                                                                                                                                                                                       |

| Package / Case 32-LQFP                                                                                                                                                                                                                                                                                                                                                                            |

| Supplier Device Package32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                              |

| Purchase URL https://www.e-xfl.com/product-detail/silicon-labs/c8051f565-iqr                                                                                                                                                                                                                                                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. System Overview

C8051F55x/56x/57x devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 2.1 for specific product feature selection and part ordering numbers.

- High-speed pipelined 8051-compatible microcontroller core (up to 50 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- Controller Area Network (CAN 2.0B) Controller with 32 message objects, each with its own indentifier mask (C8051F550/1/4/5, 'F560/1/4/5/8/9, and 'F572/3)

- LIN 2.1 peripheral (fully backwards compatible, master and slave modes) (C8051F550/2/4/6, 'F560/2/4/6/8, and 'F570/2/4)

- True 12-bit 200 ksps 32-channel single-ended ADC with analog multiplexer

- Precision programmable 24 MHz internal oscillator that is within ±0.5% across the temperature range and for VDD voltages greater than or equal to the on-chip voltage regulator minimum output at the low setting. The oscillator is within ±1.0% for VDD voltages below this minimum output setting.

- On-chip Clock Multiplier to reach up to 50 MHz

- 32 kB (C8051F550-3, 'F560-3, 'F568-9, and 'F570-1) or 16 kB (C8051F554-7, 'F564-7, and 'F572-5) of on-chip Flash memory

- 2304 bytes of on-chip RAM

- SMBus/I2C, Enhanced UART, and Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- External Data Memory Interface (C8051F568-9 and 'F570-5) with 64 kB address space

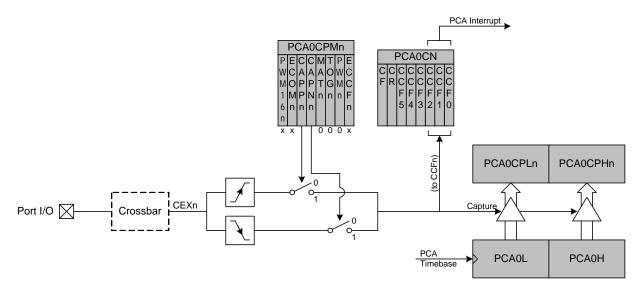

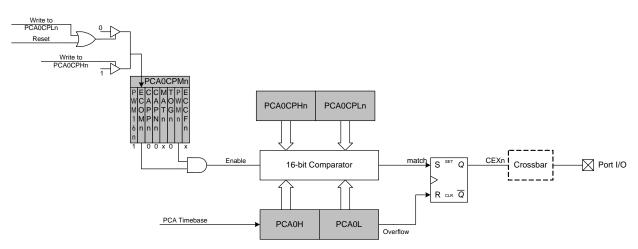

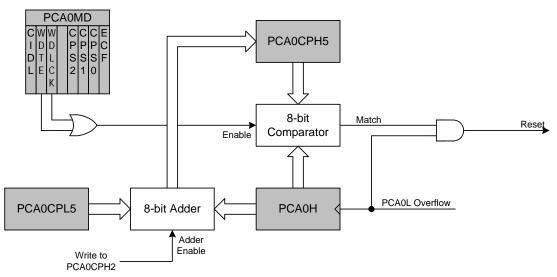

- Programmable Counter/Timer Array (PCA) with six capture/compare modules and Watchdog Timer function

- On-chip Voltage Regulator

- On-chip Power-On Reset, V<sub>DD</sub> Monitor, and Temperature Sensor

- On-chip Voltage Comparator

- 33, 25, or 18 Port I/O (5 V push-pull)

With on-chip Voltage Regulator, Power-On Reset, V<sub>DD</sub> monitor, Watchdog Timer, and clock oscillator, the C8051F55x/56x/57x devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

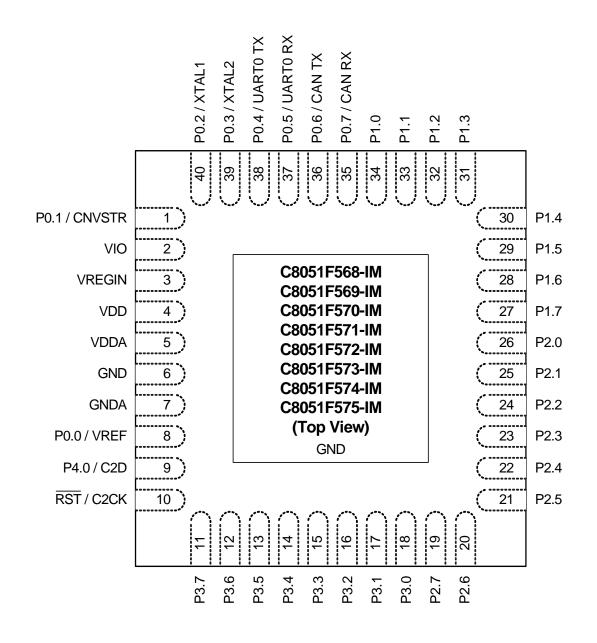

The devices are specified for 1.8 V to 5.25 V operation over the automotive temperature range (-40 to +125 °C). The C8051F568-9 and 'F570-5 are available in 40-pin QFN packages, the C8051F560-7 devices are available in 32-pin QFP and QFN packages, and the C8051F550-7 are available in 24-pin QFN packages. All package options are lead-free and RoHS compliant. See Table 2.1 for ordering information. Block diagrams are included in Figure 1.1, Figure 1.2, and Figure 1.3.

Figure 3.1. QFN-40 Pinout Diagram (Top View)

#### 6.3.2. Setting the Gain Value

The three programmable gain registers are accessed indirectly using the ADC0H and ADC0L registers when the GAINEN bit (ADC0CF.0) bit is set. ADC0H acts as the address register, and ADC0L is the data register. The programmable gain registers can only be written to and cannot be read. See Gain Register Definition 6.1, Gain Register Definition 6.2, and Gain Register Definition 6.3 for more information.

The gain is programmed using the following steps:

- 1. Set the GAINEN bit (ADC0CF.0)

- 2. Load the ADC0H with the ADC0GNH, ADC0GNL, or ADC0GNA address.

- 3. Load ADC0L with the desired value for the selected gain register.

- 4. Reset the GAINEN bit (ADC0CF.0)

#### Notes:

- 1. An ADC conversion should not be performed while the GAINEN bit is set.

- 2. Even with gain enabled, the maximum input voltage must be less than V<sub>REGIN</sub> and the maximum voltage of the signal after gain must be less than or equal to  $V_{REF}$ .

In code, changing the value to 0.44 gain from the previous example looks like:

// in 'C':

MOV ADC0H,#07H MOV ADC0L,#0A0H

MOV ADC0H,#08H

MOV ADC0L,#01H

ANL ADCOCF,#0FEH

| ADC0CF  = 0x01;  | // GAINEN = 1                                |

|------------------|----------------------------------------------|

| ADC0H = 0x04;    | // Load the ADC0GNH address                  |

| ADC0L = 0x6C;    | // Load the upper byte of 0x6CA to ADC0GNH   |

| ADC0H = 0x07;    | // Load the ADC0GNL address                  |

| ADC0L = 0xA0;    | // Load the lower nibble of 0x6CA to ADC0GNL |

| ADC0H = 0x08;    | // Load the ADC0GNA address                  |

| ADC0L = 0x01;    | // Set the GAINADD bit                       |

| ADC0CF &= ~0x01; | // GAINEN = 0                                |

|                  |                                              |

| ; in assembly    |                                              |

| ORL ADC0CF,#01H  | ; GAINEN = 1                                 |

| MOV ADC0H,#04H   | ; Load the ADC0GNH address                   |

| MOV ADC0L,#06CH  | ; Load the upper byte of 0x6CA to ADC0GNH    |

- ; Load the upper byte of 0x6CA to ADC0GNH

- : Load the ADC0GNL address

- ; Load the lower nibble of 0x6CA to ADC0GNL

- : Load the ADC0GNA address

- : Set the GAINADD bit

- ; GAINEN = 0

# SFR Definition 6.7. ADC0CN: ADC0 Control

| Bit   | 7             | 6                                                                                                                                                                                                                       | 5                                                                                                                                                                                                                                                                                                                                                          | 4             | 3         | 2      |        | 1          | 0 |  |

|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------|--------|--------|------------|---|--|

| Nam   | e AD0EN       | BURSTEN                                                                                                                                                                                                                 | AD0INT                                                                                                                                                                                                                                                                                                                                                     | AD0BUSY       | ADOWINT   | AD0LJS | ST     | AD0CM[1:0] |   |  |

| Туре  | e R/W         | R/W                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                                                                                                                                                        | R/W           | R/W       | R/W    |        | R/W        |   |  |

| Rese  | et 0          | 0 0 0 0 0 0 0                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                            |               |           |        | 0      |            |   |  |

| SFR A | Address = 0xE | 8; SFR Page                                                                                                                                                                                                             | = 0x00; Bit                                                                                                                                                                                                                                                                                                                                                | -Addressable  | e         |        |        |            |   |  |

| Bit   | Name          | Function                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                            |               |           |        |        |            |   |  |

| 7     | AD0EN         | ADC0 Enab                                                                                                                                                                                                               | le Bit.                                                                                                                                                                                                                                                                                                                                                    |               |           |        |        |            |   |  |

|       |               | 0: ADC0 Dis<br>1: ADC0 Ena                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                            |               |           |        | versio | ons.       |   |  |

| 6     | BURSTEN       | ADC0 Burst                                                                                                                                                                                                              | Mode Ena                                                                                                                                                                                                                                                                                                                                                   | ble Bit.      |           |        |        |            |   |  |

|       |               | 0: Burst Moo<br>1: Burst Moo                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                            |               |           |        |        |            |   |  |

| 5     | AD0INT        | ADC0 Conv                                                                                                                                                                                                               | ersion Con                                                                                                                                                                                                                                                                                                                                                 | nplete Interr | upt Flag. |        |        |            |   |  |

|       |               | 0: ADC0 has not completed a data conversion since AD0INT was last cleared.<br>1: ADC0 has completed a data conversion.                                                                                                  |                                                                                                                                                                                                                                                                                                                                                            |               |           |        |        | ared.      |   |  |

| 4     | AD0BUSY       | ADC0 Busy                                                                                                                                                                                                               | Bit.                                                                                                                                                                                                                                                                                                                                                       | Read:         |           |        | Writ   | e:         |   |  |

|       |               | 0: ADC0 conversion is not<br>in progress.0: No Effect.1: ADC0 conversion is in<br>progress.1: Initiates ADC0 Conver-<br>sion if AD0CM[1:0] = 00b                                                                        |                                                                                                                                                                                                                                                                                                                                                            |               |           |        |        |            |   |  |

| 3     | AD0WINT       | ADC0 Wind                                                                                                                                                                                                               | ow Compa                                                                                                                                                                                                                                                                                                                                                   | re Interrupt  | Flag.     |        |        |            |   |  |

|       |               | This bit must be cleared by software<br>0: ADC0 Window Comparison Data match has not occurred since this flag was last<br>cleared.<br>1: ADC0 Window Comparison Data match has occurred.                                |                                                                                                                                                                                                                                                                                                                                                            |               |           |        |        |            |   |  |

| 2     | AD0LJST       | ADC0 Left Justify Select Bit.                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                            |               |           |        |        |            |   |  |

|       |               | 0: Data in ADC0H:ADC0L registers is right-justified<br>1: Data in ADC0H:ADC0L registers is left-justified. This option should not be used<br>with a repeat count greater than 1 (when AD0RPT[1:0] is 01b, 10b, or 11b). |                                                                                                                                                                                                                                                                                                                                                            |               |           |        |        |            |   |  |

| 1:0   | AD0CM[1:0]    | ADC0 Start                                                                                                                                                                                                              | of Convers                                                                                                                                                                                                                                                                                                                                                 | ion Mode S    | elect.    |        |        |            |   |  |

|       |               | 01: ADC0 st<br>10: ADC0 st                                                                                                                                                                                              | <ul> <li>ADC0 Start of Conversion Mode Select.</li> <li>00: ADC0 start-of-conversion source is write of 1 to AD0BUSY.</li> <li>01: ADC0 start-of-conversion source is overflow of Timer 1.</li> <li>10: ADC0 start-of-conversion source is rising edge of external CNVSTR.</li> <li>11: ADC0 start-of-conversion source is overflow of Timer 2.</li> </ul> |               |           |        |        |            |   |  |

# SFR Definition 12.1. SFR0CN: SFR Page Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|-------|---|---|---|---|---|---|---|---------|

| Name  |   |   |   |   |   |   |   | SFRPGEN |

| Туре  | R | R | R | R | R | R | R | R/W     |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1       |

## SFR Address = 0x84; SFR Page = 0x0F

| Bit | Name    | Function                                                                                                                                                                                                                                        |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | Unused  | Read = 0000000b; Write = Don't Care                                                                                                                                                                                                             |

| 0   | SFRPGEN | SFR Automatic Page Control Enable.                                                                                                                                                                                                              |

|     |         | Upon interrupt, the C8051 Core will vector to the specified interrupt service routine<br>and automatically switch the SFR page to the corresponding peripheral or function's<br>SFR page. This bit is used to control this autopaging function. |

|     |         | 0: SFR Automatic Paging disabled. The C8051 core will not automatically change to the appropriate SFR page (i.e., the SFR page that contains the SFRs for the peripheral/function that was the source of the interrupt).                        |

|     |         | 1: SFR Automatic Paging enabled. Upon interrupt, the C8051 will switch the SFR page to the page that contains the SFRs for the peripheral or function that is the source of the interrupt.                                                      |

| Address   | 0(8)                   | 1(9)                | 2(A)               | 3(B)               | 4(C)               | 5(D)                   | 6(E)                   | 7(F)                   |

|-----------|------------------------|---------------------|--------------------|--------------------|--------------------|------------------------|------------------------|------------------------|

| ≪<br>F8 ( | SPI0CN                 | PCA0L<br>SN0        | PCA0H<br>SN1       | PCA0CPL0<br>SN2    | PCA0CPH0<br>SN3    | PCACPL4                | PCACPH4                | VDM0CN                 |

| F0 (      | ) B<br>F(All Pages)    | P0MAT<br>P0MDIN     | P0MASK<br>P1MDIN   | P1MAT<br>P2MDIN    | P1MASK<br>P3MDIN   |                        | EIP1<br>EIP1           | EIP2<br>EIP2           |

| E8 (      | ADC0CN                 | PCA0CPL1            | PCA0CPH1           | PCA0CPL2           | PCA0CPH2           | PCA0CPL3               | PCA0CPL3               | RSTSRC                 |

| E0 (      | ) ACC<br>- (All Pages) | XBR0                | XBR1               | CCH0CN             | IT01CF             |                        | EIE1<br>(All Pages)    | EIE2<br>(All Pages)    |

| D8 (      | =                      | PCA0MD<br>PCA0PWM   | PCA0CPM0           | PCA0CPM1           | PCA0CPM2           | PCA0CPM3               | PCA0CPM4               | PCA0CPM5               |

| D0 (<br>F | ) PSW<br>- (All Pages) | REF0CN              | LIN0DATA           | LIN0ADDR           | P0SKIP             | P1SKIP                 | P2SKIP                 | P3SKIP                 |

| C8 (      | TMR2CN                 | REG0CN<br>LIN0CF    | TMR2RLL            | TMR2RLH            | TMR2L              | TMR2H                  | PCA0CPL5               | PCA0CPH5               |

| C0 (      | ) SMB0CN               | SMB0CF              | SMB0DAT            | ADC0GTL            | ADC0GTH            | ADC0LTL                | ADC0LTH                | XBR2                   |

| B8 (      |                        |                     | ADC0TK             | ADC0MX             | ADC0CF             | ADC0L                  | ADC0H                  |                        |

| В0 (<br>Г | ) P3<br>F(All Pages)   | P2MAT               | P2MASK<br>EMI0CF   |                    |                    | P4<br>(All Pages)      | FLSCL<br>(All Pages)   | FLKEY<br>(All Pages)   |

| A8 (      | ) IE<br>F(All Pages)   | SMOD0               | EMI0CN<br>EMI0TC   | SBCON0             | SBRLL0             | SBRLH0                 | P3MAT<br>P3MDOUT       | P3MASK<br>P4MDOUT      |

| A0 (      | ) P2<br>F(All Pages)   | SPI0CFG<br>OSCICN   | SPI0CKR<br>OSCICRS | SPI0DAT            | POMDOUT            | P1MDOUT                | P2MDOUT                | SFRPAGE<br>(All Pages) |

| 98 (<br>F | ) SCON0                | SBUF0               | CPT0CN             | CPT0MD             | CPT0MX             | CPT1CN                 | CPT1MD<br>OSCIFIN      | CPT1MX<br>OSCXCN       |

| 90 (<br>F | ) P1<br>F(All Pages)   | TMR3CN              | TMR3RLL            | TMR3RLH            | TMR3L              | TMR3H                  |                        | CLKMUL                 |

| 88 (<br>F | TCON                   | TMOD<br>(All Pages) | TL0<br>(All Pages) | TL1<br>(All Pages) | TH0<br>(All Pages) | TH1<br>(All Pages)     | CKCON<br>(All Pages)   | PSCTL<br>CLKSEL        |

| 80 (<br>F | ) P0                   | SP<br>(All Pages)   | DPL<br>(All Pages) | DPH<br>(All Pages) | SFR0CN             | SFRNEXT<br>(All Pages) | SFRLAST<br>(All Pages) | PCON<br>(All Pages)    |

| L         | 0(8)<br>(bit address   | 1(9)                | 2(A)               | 3(B)               | 4(C)               | 5(D)                   | 6(E)                   | 7(F)                   |

# Table 12.1. Special Function Register (SFR) Memory Map for Pages 0x00 and 0x0F

# Table 12.3. Special Function Registers (Continued)

| SERs are listed in alphabetical order  | All undefined SFR locations are reserved |

|----------------------------------------|------------------------------------------|

| SERS are listed in alphabetical order. | All undernied SFR locations are reserved |

| Register | Address | Description                     | Page |  |  |

|----------|---------|---------------------------------|------|--|--|

| SMB0CF   | 0xC1    | SMBus0 Configuration            | 224  |  |  |

| SMB0CN   | 0xC0    | SMBus0 Control                  | 226  |  |  |

| SMB0DAT  | 0xC2    | SMBus0 Data                     | 228  |  |  |

| SMOD0    | 0xA9    | UART0 Mode                      | 243  |  |  |

| SN0      | 0xF9    | Serial Number 0                 | 91   |  |  |

| SN1      | 0xFA    | Serial Number 1                 | 91   |  |  |

| SN2      | 0xFB    | Serial Number 2                 | 91   |  |  |

| SN3      | 0xFC    | Serial Number 3                 | 91   |  |  |

| SP       | 0x81    | Stack Pointer                   | 89   |  |  |

| SPI0CFG  | 0xA1    | SPI0 Configuration              | 253  |  |  |

| SPI0CKR  | 0xA2    | SPI0 Clock Rate Control         | 255  |  |  |

| SPIOCN   | 0xF8    | SPI0 Control                    | 254  |  |  |

| SPIODAT  | 0xA3    | SPI0 Data                       | 255  |  |  |

| TCON     | 0x88    | Timer/Counter Control           | 265  |  |  |

| TH0      | 0x8C    | Timer/Counter 0 High            | 268  |  |  |

| TH1      | 0x8D    | Timer/Counter 1 High            | 268  |  |  |

| TL0      | 0x8A    | Timer/Counter 0 Low             | 267  |  |  |

| TL1      | 0x8B    | Timer/Counter 1 Low             | 267  |  |  |

| TMOD     | 0x89    | Timer/Counter Mode              | 266  |  |  |

| TMR2CN   | 0xC8    | Timer/Counter 2 Control         | 272  |  |  |

| TMR2H    | 0xCD    | Timer/Counter 2 High            | 274  |  |  |

| TMR2L    | 0xCC    | Timer/Counter 2 Low             | 274  |  |  |

| TMR2RLH  | 0xCB    | Timer/Counter 2 Reload High     | 273  |  |  |

| TMR2RLL  | 0xCA    | Timer/Counter 2 Reload Low      | 273  |  |  |

| TMR3CN   | 0x91    | Timer/Counter 3 Control         | 278  |  |  |

| TMR3H    | 0x95    | Timer/Counter 3 High            | 280  |  |  |

| TMR3L    | 0x94    | Timer/Counter 3 Low             | 280  |  |  |

| TMR3RLH  | 0x93    | Timer/Counter 3 Reload High     | 279  |  |  |

| TMR3RLL  | 0x92    | Timer/Counter 3 Reload Low      |      |  |  |

| VDM0CN   | 0xFF    | V <sub>DD</sub> Monitor Control |      |  |  |

| XBR0     | 0xE1    | Port I/O Crossbar Control 0     | 176  |  |  |

| XBR1     | 0xE2    | Port I/O Crossbar Control 1     | 177  |  |  |

| XBR2     | 0xC7    | Port I/O Crossbar Control 2     | 178  |  |  |

# SFR Definition 16.1. VDM0CN: V<sub>DD</sub> Monitor Control

| Bit   | 7      | 6       | 5      | 4 | 3 | 2 | 1 | 0 |

|-------|--------|---------|--------|---|---|---|---|---|

| Name  | VDMEN  | VDDSTAT | VDMLVL |   |   |   |   |   |

| Туре  | R/W    | R       | R/W    | R | R | R | R | R |

| Reset | Varies | Varies  | 0      | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xFF; SFR Page = 0x00

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN   | V <sub>DD</sub> Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |         | This bit turns the V <sub>DD</sub> monitor circuit on/off. The V <sub>DD</sub> Monitor cannot generate system resets until it is also selected as a reset source in register RSTSRC (SFR Definition 16.2). Selecting the V <sub>DD</sub> monitor as a reset source before it has stabilized may generate a system reset. In systems where this reset would be undesirable, a delay should be introduced between enabling the V <sub>DD</sub> Monitor and selecting it as a reset source. See Table 5.4 for the minimum V <sub>DD</sub> Monitor turn-on time.<br>0: V <sub>DD</sub> Monitor Disabled.<br>1: V <sub>DD</sub> Monitor Enabled. |

| 6   | VDDSTAT | V <sub>DD</sub> Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |         | This bit indicates the current power supply status ( $V_{DD}$ Monitor output).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |         | <ul> <li>0: V<sub>DD</sub> is at or below the V<sub>DD</sub> monitor threshold.</li> <li>1: V<sub>DD</sub> is above the V<sub>DD</sub> monitor threshold.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5   | VDMLVL  | V <sub>DD</sub> Monitor Level Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |         | 0: $V_{DD}$ Monitor Threshold is set to VRST-LOW<br>1: $V_{DD}$ Monitor Threshold is set to VRST-HIGH. This setting is required for any system includes code that writes to and/or erases Flash.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4:0 | Unused  | Read = 00000b; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# 16.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 5.4 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

# 16.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than the value specified in Table 5.4, "Reset Electrical Characteristics," on page 41, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

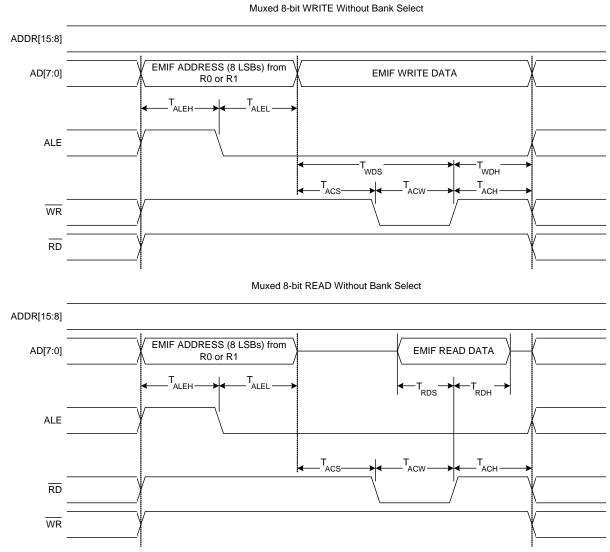

## 17.6.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011

Figure 17.4. Multiplexed 8-bit MOVX without Bank Select Timing

# C8051F55x/56x/57x

# SFR Definition 19.3. XBR2: Port I/O Crossbar Register 1

| Bit   | 7       | 6     | 5   | 4        | 3   | 2 | 1   | 0   |

|-------|---------|-------|-----|----------|-----|---|-----|-----|

| Name  | WEAKPUD | XBARE |     | Reserved |     |   |     |     |

| Туре  | R/W     | R/W   | R/W | R/W      | R/W | R | R/W | R/W |

| Reset | 0       | 0     | 0   | 0        | 0   | 0 | 0   | 0   |

# SFR Address = 0xC7; SFR Page = 0x0F

| Bit | Name     | Function                                                                                                                                 |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | WEAKPUD  | Port I/O Weak Pullup Disable.                                                                                                            |

|     |          | <ul><li>0: Weak Pullups enabled (except for Ports whose I/O are configured for analog mode).</li><li>1: Weak Pullups disabled.</li></ul> |

| 6   | XBARE    | Crossbar Enable.                                                                                                                         |

|     |          | 0: Crossbar disabled.                                                                                                                    |

|     |          | 1: Crossbar enabled.                                                                                                                     |

| 5:1 | Reserved | Always Write to 00000b.                                                                                                                  |

| 0   | LIN0E    | LIN I/O Output Enable.                                                                                                                   |

|     |          | 0: LIN I/O unavailable at Port pin.                                                                                                      |

|     |          | 1: LIN_TX, LIN_RX routed to Port pins.                                                                                                   |

# LIN Register Definition 20.8. LIN0SIZE: LIN0 Message Size Register

| Bit   | 7      | 6 | 5 | 4 | 3            | 2 | 1 | 0 |  |

|-------|--------|---|---|---|--------------|---|---|---|--|

| Name  | ENHCHK |   |   |   | LINSIZE[3:0] |   |   |   |  |

| Туре  | R/W    | R | R | R | R/W          |   |   |   |  |

| Reset | 0      | 0 | 0 | 0 | 0            | 0 | 0 | 0 |  |

Indirect Address = 0x0B

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                               |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ENHCHK       | <ul> <li>Checksum Selection Bit.</li> <li>0: Use the classic, specification 1.3 compliant checksum. Checksum covers the data bytes.</li> <li>1: Use the enhanced, specification 2.0 compliant checksum. Checksum covers data bytes and protected identifier.</li> </ul>                                                |

| 6:4 | Unused       | Read = 000b; Write = Don't Care                                                                                                                                                                                                                                                                                        |

| 3:0 | LINSIZE[3:0] | Data Field Size.<br>0000: 0 data bytes<br>0001: 1 data byte<br>0010: 2 data bytes<br>0011: 3 data bytes<br>0100: 4 data bytes<br>0101: 5 data bytes<br>0110: 6 data bytes<br>0111: 7 data bytes<br>1000: 8 data bytes<br>1001-1110: RESERVED<br>1111: Use the ID[1:0] bits (LIN0ID[5:4]) to determine the data length. |

# 22.1. Supporting Documents

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The I<sup>2</sup>C-Bus and How to Use It (including specifications), Philips Semiconductor.

- 2. The I<sup>2</sup>C-Bus Specification—Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification—Version 1.1, SBS Implementers Forum.

# 22.2. SMBus Configuration

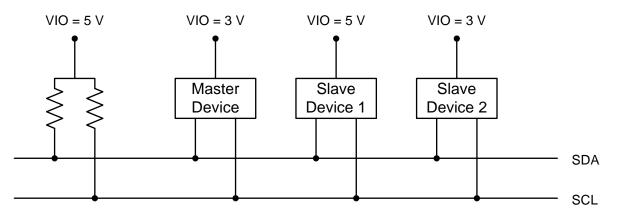

Figure 22.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 V and 5.0 V; different devices on the bus may operate at different voltage levels. The bi-directional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pullup resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

Figure 22.2. Typical SMBus Configuration

# 22.3. SMBus Operation

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. It is not necessary to specify one device as the Master in a system; any device who transmits a START and a slave address becomes the master for the duration of that transfer.

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7–1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Bytes that are received (by a master or slave) are acknowledged (ACK) with a low SDA during a high SCL (see Figure 22.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

The direction bit (R/W) occupies the least-significant bit position of the address byte. The direction bit is set to logic 1 to indicate a "READ" operation and cleared to logic 0 to indicate a "WRITE" operation.

# SFR Definition 22.2. SMB0CN: SMBus Control

| Bit   | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0   |

|-------|--------|--------|-----|-----|-------|---------|-----|-----|

| Name  | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI  |

| Туре  | R      | R      | R/W | R/W | R     | R       | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0   |

#### SFR Address = 0xC0; Bit-Addressable; SFR Page =0x00

| Bit | Name    | Description                                                                                                                                                                                                      | Read                                                                                                                       | Write                                                                                                                                                                                |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | SMBus Master/Slave<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a master.                                                                                                     | 0: SMBus operating in<br>slave mode.<br>1: SMBus operating in<br>master mode.                                              | N/A                                                                                                                                                                                  |

| 6   | TXMODE  | SMBus Transmit Mode<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a transmitter.                                                                                               | 0: SMBus in Receiver<br>Mode.<br>1: SMBus in Transmitter<br>Mode.                                                          | N/A                                                                                                                                                                                  |

| 5   | STA     | SMBus Start Flag.                                                                                                                                                                                                | 0: No Start or repeated<br>Start detected.<br>1: Start or repeated Start<br>detected.                                      | 0: No Start generated.<br>1: When Configured as a<br>Master, initiates a START<br>or repeated START.                                                                                 |

| 4   | STO     | SMBus Stop Flag.                                                                                                                                                                                                 | 0: No Stop condition<br>detected.<br>1: Stop condition detected<br>(if in Slave Mode) or pend-<br>ing (if in Master Mode). | 0: No STOP condition is<br>transmitted.<br>1: When configured as a<br>Master, causes a STOP<br>condition to be transmit-<br>ted after the next ACK<br>cycle.<br>Cleared by Hardware. |

| 3   | ACKRQ   | SMBus Acknowledge<br>Request.                                                                                                                                                                                    | 0: No Ack requested<br>1: ACK requested                                                                                    | N/A                                                                                                                                                                                  |

| 2   | ARBLOST | SMBus Arbitration Lost<br>Indicator.                                                                                                                                                                             | 0: No arbitration error.<br>1: Arbitration Lost                                                                            | N/A                                                                                                                                                                                  |

| 1   | ACK     | SMBus Acknowledge.                                                                                                                                                                                               | 0: NACK received.<br>1: ACK received.                                                                                      | 0: Send NACK<br>1: Send ACK                                                                                                                                                          |

| 0   | SI      | <b>SMBus Interrupt Flag.</b><br>This bit is set by hardware<br>under the conditions listed in<br>Table 15.3. SI must be cleared<br>by software. While SI is set,<br>SCL is held low and the<br>SMBus is stalled. | 0: No interrupt pending<br>1: Interrupt Pending                                                                            | <ul><li>0: Clear interrupt, and initiate next state machine event.</li><li>1: Force interrupt.</li></ul>                                                                             |

|                     | Value            | Values Read Curre |         |     | Current SMbus State                                                                         | Typical Response Options                                   | Values to<br>Write |     |     | s<br>ected                     |

|---------------------|------------------|-------------------|---------|-----|---------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------|-----|-----|--------------------------------|

| Mode                | Status<br>Vector | ACKRQ             | ARBLOST | ACK |                                                                                             |                                                            | STA                | STO | ACK | Next Status<br>Vector Expected |

|                     | 0100             | 0                 | 0       | 0   | A slave byte was transmitted;<br>NACK received.                                             | No action required (expecting STOP condition).             | 0                  | 0   | Х   | 0001                           |

| ter                 |                  | 0                 | 0       | 1   | A slave byte was transmitted;<br>ACK received.                                              | Load SMB0DAT with next data byte to transmit.              | 0                  | 0   | Х   | 0100                           |

| ansmit              |                  | 0                 | 1       | Х   | A Slave byte was transmitted;<br>error detected.                                            | No action required (expecting Master to end transfer).     | 0                  | 0   | Х   | 0001                           |

| Slave Transmitter   | 0101             | 0                 | Х       | Х   | An illegal STOP or bus error<br>was detected while a Slave<br>Transmission was in progress. | Clear STO.                                                 | 0                  | 0   | Х   |                                |

|                     | 0010             | 1                 | 0       | Х   | A slave address + R/W was received; ACK requested.                                          | If Write, Acknowledge received address                     | 0                  | 0   | 1   | 0000                           |

|                     |                  |                   |         |     |                                                                                             | If Read, Load SMB0DAT with data byte; ACK received address | 0                  | 0   | 1   | 0100                           |

|                     |                  |                   |         |     |                                                                                             | NACK received address.                                     | 0                  | 0   | 0   | —                              |

|                     |                  | 1                 | 1       | Х   | Lost arbitration as master;<br>slave address + R/W received;                                | If Write, Acknowledge received address                     | 0                  | 0   | 1   | 0000                           |

|                     |                  |                   |         |     | ACK requested.                                                                              | If Read, Load SMB0DAT with data byte; ACK received address | 0                  | 0   | 1   | 0100                           |

|                     |                  |                   |         |     |                                                                                             | NACK received address.                                     | 0                  | 0   | 0   |                                |

|                     |                  |                   |         |     |                                                                                             | Reschedule failed transfer;<br>NACK received address.      | 1                  | 0   | 0   | 1110                           |

|                     | 0001             | 0                 | 0       | Х   | A STOP was detected while<br>addressed as a Slave Trans-<br>mitter or Slave Receiver.       | Clear STO.                                                 | 0                  | 0   | Х   | _                              |

| eiver               |                  | 1                 | 1       | Х   | Lost arbitration while attempt-<br>ing a STOP.                                              | No action required (transfer complete/aborted).            | 0                  | 0   | 0   | —                              |

| Slave Rec           | 0000             | 1                 | 0       | Х   | A slave byte was received;<br>ACK requested.                                                | Acknowledge received byte;<br>Read SMB0DAT.                | 0                  | 0   | 1   | 0000                           |

| Slav                |                  |                   |         |     |                                                                                             | NACK received byte.                                        | 0                  | 0   | 0   | —                              |

|                     | 0010             | 0                 | 1       | Х   | Lost arbitration while attempt-                                                             | Abort failed transfer.                                     | 0                  | 0   | Х   |                                |

| ditic               |                  |                   |         |     | ing a repeated START.                                                                       | Reschedule failed transfer.                                | 1                  | 0   | Х   | 1110                           |

| Con                 | 0001             | 0                 | 1       | Х   | Lost arbitration due to a                                                                   | Abort failed transfer.                                     | 0                  | 0   | Х   | —                              |

| Bus Error Condition |                  |                   |         |     | detected STOP.                                                                              | Reschedule failed transfer.                                | 1                  | 0   | Х   | 1110                           |

| ΕĽ                  | 0000             | 1                 | 1       | Х   | Lost arbitration while transmit-                                                            | Abort failed transfer.                                     | 0                  | 0   | 0   | —                              |

| Bus                 |                  |                   |         |     | ting a data byte as master.                                                                 | Reschedule failed transfer.                                | 1                  | 0   | 0   | 1110                           |

# Table 22.4. SMBus Status Decoding (Continued)

# 23. UART0

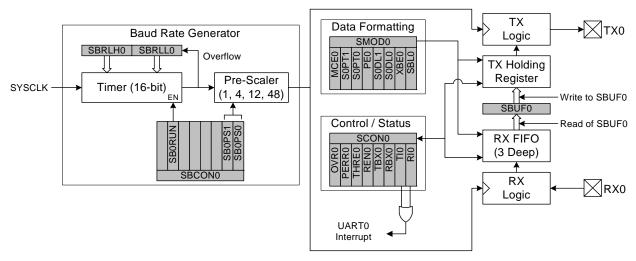

UART0 is an asynchronous, full duplex serial port offering a variety of data formatting options. A dedicated baud rate generator with a 16-bit timer and selectable prescaler is included, which can generate a wide range of baud rates (details in Section "23.1. Baud Rate Generator" on page 235). A received data FIFO allows UART0 to receive up to three data bytes before data is lost and an overflow occurs.

UART0 has six associated SFRs. Three are used for the Baud Rate Generator (SBCON0, SBRLH0, and SBRLL0), two are used for data formatting, control, and status functions (SCON0, SMOD0), and one is used to send and receive data (SBUF0). The single SBUF0 location provides access to both the transmit holding register and the receive FIFO. Writes to SBUF0 always access the Transmit register. Reads of SBUF0 always access the first byte of the Receive FIFO; it is not possible to read data from the Transmit Holding Register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete). If additional bytes are available in the Receive FIFO, the RI0 bit cannot be cleared by software.

Figure 23.1. UART0 Block Diagram

# 23.1. Baud Rate Generator

The UART0 baud rate is generated by a dedicated 16-bit timer which runs from the controller's core clock (SYSCLK) and has prescaler options of 1, 4, 12, or 48. The timer and prescaler options combined allow for a wide selection of baud rates over many clock frequencies.

The baud rate generator is configured using three registers: SBCON0, SBRLH0, and SBRLL0. The UART0 Baud Rate Generator Control Register (SBCON0, SFR Definition 23.4) enables or disables the baud rate generator and selects the prescaler value for the timer. The baud rate generator must be enabled for UART0 to function. Registers SBRLH0 and SBRLL0 contain a 16-bit reload value for the dedicated 16-bit timer. The internal timer counts up from the reload value on every clock tick. On timer overflows (0xFFFF to 0x0000), the timer is reloaded. The baud rate for UART0 is defined in Equation 23.1, where "BRG Clock" is the baud rate generator's selected clock source. For reliable UART operation, it is recommended that the UART baud rate is not configured for baud rates faster than SYSCLK/16.

# SFR Definition 25.2. TCON: Timer Control

| Bit   | 7            | 6                                                                                                                                                                                                                                                                   | 5                                      | 4                   | 3                           | 2   | 1   | 0   |  |  |  |

|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------|-----------------------------|-----|-----|-----|--|--|--|

| Nam   | e TF1        | TR1                                                                                                                                                                                                                                                                 | TF0                                    | TR0                 | IE1                         | IT1 | IE0 | IT0 |  |  |  |

| Туре  | R/W          | R/W                                                                                                                                                                                                                                                                 | R/W                                    | R/W                 | R/W                         | R/W | R/W | R/W |  |  |  |

| Rese  | t 0          | 0                                                                                                                                                                                                                                                                   | 0                                      | 0                   | 0                           | 0   | 0   | 0   |  |  |  |

| SFR A | ddress = 0x8 | 8; Bit-Addres                                                                                                                                                                                                                                                       | sable; SFR                             | l<br>Page = All P   | ages                        |     |     |     |  |  |  |

| Bit   | Name         | Function                                                                                                                                                                                                                                                            |                                        |                     |                             |     |     |     |  |  |  |

| 7     | TF1          | Timer 1 Ov                                                                                                                                                                                                                                                          | er 1 Overflow Flag.                    |                     |                             |     |     |     |  |  |  |

|       |              |                                                                                                                                                                                                                                                                     |                                        |                     | overflows. The CPU vecto    |     |     |     |  |  |  |

| 6     | TR1          | Timer 1 Ru                                                                                                                                                                                                                                                          | n Control.                             |                     |                             |     |     |     |  |  |  |

|       |              | Timer 1 is e                                                                                                                                                                                                                                                        | nabled by se                           | etting this bit     | to 1.                       |     |     |     |  |  |  |

| 5     | TF0          | Timer 0 Ov                                                                                                                                                                                                                                                          | •                                      |                     |                             |     |     |     |  |  |  |

|       |              | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                                                       |                                        |                     |                             |     |     |     |  |  |  |

| 4     | TR0          | Timer 0 Ru                                                                                                                                                                                                                                                          | n Control.                             |                     |                             |     |     |     |  |  |  |

|       |              | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                                                        |                                        |                     |                             |     |     |     |  |  |  |

| 3     | IE1          | External Int                                                                                                                                                                                                                                                        | terrupt 1.                             |                     |                             |     |     |     |  |  |  |

|       |              | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode.                             |                                        |                     |                             |     |     |     |  |  |  |

| 2     | IT1          | Interrupt 1 Type Select.                                                                                                                                                                                                                                            |                                        |                     |                             |     |     |     |  |  |  |

|       |              | This bit selects whether the configured INT1 interrupt will be edge or level sensitive.<br>INT1 is configured active low or high by the IN1PL bit in the IT01CF register (see<br>SFR Definition 13.7).<br>0: INT1 is level triggered.<br>1: INT1 is edge triggered. |                                        |                     |                             |     |     |     |  |  |  |

| 1     | IE0          | External Int                                                                                                                                                                                                                                                        | -                                      |                     |                             |     |     |     |  |  |  |

|       |              | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 0 service routine in edge-triggered mode.                             |                                        |                     |                             |     |     |     |  |  |  |

| 0     | IT0          | Interrupt 0 Type Select.                                                                                                                                                                                                                                            |                                        |                     |                             |     |     |     |  |  |  |

|       |              |                                                                                                                                                                                                                                                                     | igured activ<br>3.7).<br>vel triggered | e low or high<br>d. | ed INTO inte<br>by the INOF |     |     |     |  |  |  |

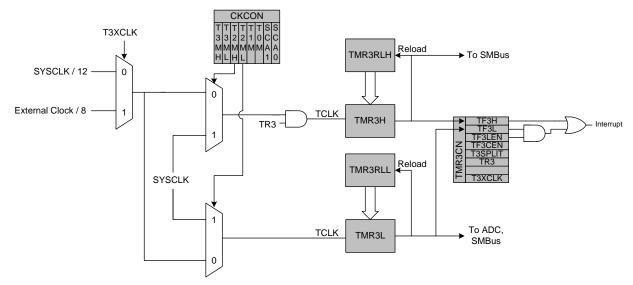

| ТЗМН | T3XCLK | TMR3H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK/12          |

| 0    | 1      | External Clock/8   |

| 1    | Х      | SYSCLK             |

| T3ML | T3XCLK | TMR3L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK/12          |

| 0    | 1      | External Clock/8   |

| 1    | Х      | SYSCLK             |

The TF3H bit is set when TMR3H overflows from 0xFF to 0x00; the TF3L bit is set when TMR3L overflows from 0xFF to 0x00. When Timer 3 interrupts are enabled, an interrupt is generated each time TMR3H overflows. If Timer 3 interrupts are enabled and TF3LEN (TMR3CN.5) is set, an interrupt is generated each time either TMR3L or TMR3H overflows. When TF3LEN is enabled, software must check the TF3H and TF3L flags to determine the source of the Timer 3 interrupt. The TF3H and TF3L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 25.8. Timer 3 8-Bit Mode Block Diagram

## 25.3.3. External Oscillator Capture Mode