Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Active                                                         |

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), LINbus, SPI, UART/USART       |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 25x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f566-im |

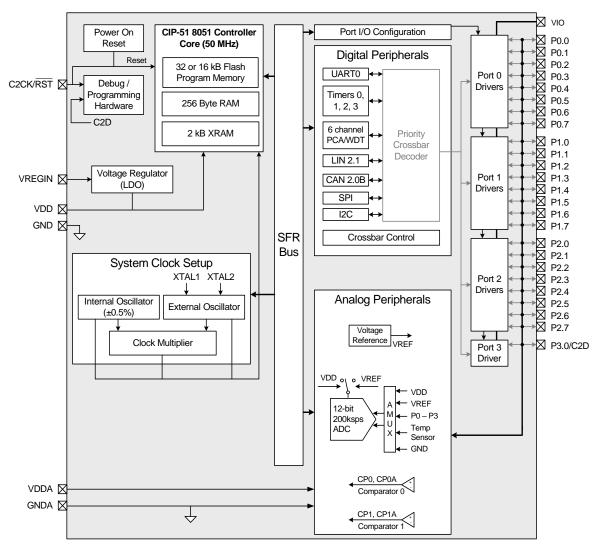

Figure 1.2. C8051F560-7 (32-pin) Block Diagram

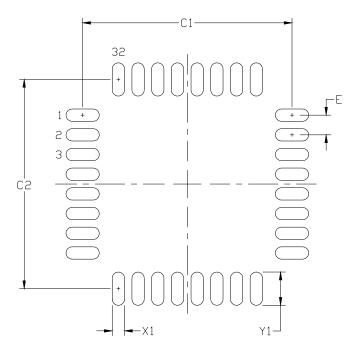

Figure 4.4. QFP-32 Landing Diagram

**Table 4.4. QFP-32 Landing Diagram Dimensions**

| Dimension | Min      | Max  |  |

|-----------|----------|------|--|

| C1        | 8.40     | 8.50 |  |

| C2        | 8.40     | 8.50 |  |

| Е         | 0.80 BSC |      |  |

| Dimension | Min  | Max  |

|-----------|------|------|

| X1        | 0.40 | 0.50 |

| Y1        | 1.25 | 1.35 |

|           |      |      |

#### Notes:

### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

### Solder Mask Design

3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \mu m$  minimum, all the way around the pad.

### Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

#### **Card Assembly**

- 7. A No-Clean, Type-3 solder paste is recommended.

- **8.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

SILICON LABS

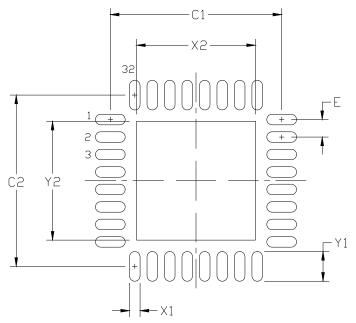

Figure 4.6. QFN-32 Landing Diagram

Table 4.6. QFN-32 Landing Diagram Dimensions

| Dimension | Min      | Max  |  | Dimension | Min  | Max  |

|-----------|----------|------|--|-----------|------|------|

| C1        | 4.80     | 4.90 |  | X2        | 3.20 | 3.40 |

| C2        | 4.80     | 4.90 |  | Y1        | 0.75 | 0.85 |

| е         | 0.50 BSC |      |  | Y2        | 3.20 | 3.40 |

| X1        | 0.20     | 0.30 |  |           |      |      |

### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

### Solder Mask Design

3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \, \mu m$  minimum, all the way around the pad.

#### Stencil Design

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- 7. A 3x3 array of 1.0 mm openings on a 1.20 mm pitch should be used for the center ground pad.

- 8. A No-Clean, Type-3 solder paste is recommended.

- 9. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### 7. Voltage Reference

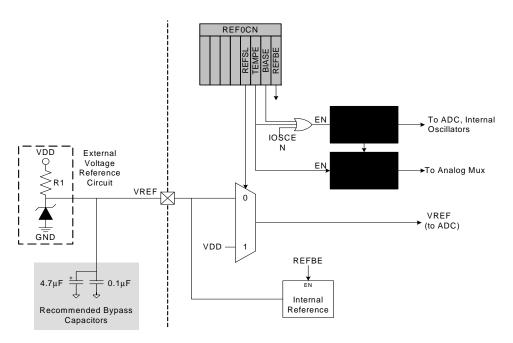

The Voltage reference multiplexer on the C8051F55x/56x/57x devices is configurable to use an externally connected voltage reference, the on-chip reference voltage generator routed to the VREF pin, or the  $V_{DD}$  power supply voltage (see Figure 7.1). The REFSL bit in the Reference Control register (REF0CN, SFR Definition 7.1) selects the reference source for the ADC. For an external source or the on-chip reference, REFSL should be set to 0 to select the VREF pin. To use  $V_{DD}$  as the reference source, REFSL should be set to 1.

The BIASE bit enables the internal voltage bias generator, which is used by the ADC, Temperature Sensor, and internal oscillator. This bias is automatically enabled when any peripheral which requires it is enabled, and it does not need to be enabled manually. The bias generator may be enabled manually by writing a 1 to the BIASE bit in register REFOCN. The electrical specifications for the voltage reference circuit are given in Table 5.11.

The on-chip voltage reference circuit consists of a temperature stable bandgap voltage reference generator and a gain-of-two output buffer amplifier. The output voltage is selectable between 1.5 V and 2.25 V. The on-chip voltage reference can be driven on the VREF pin by setting the REFBE bit in register REF0CN to a 1. The maximum load seen by the VREF pin must be less than 200  $\mu$ A to GND. Bypass capacitors of 0.1  $\mu$ F and 4.7  $\mu$ F are recommended from the VREF pin to GND. If the on-chip reference is not used, the REFBE bit should be cleared to 0. Electrical specifications for the on-chip voltage reference are given in Table 5.11.

Important Note about the VREF Pin: When using either an external voltage reference or the on-chip reference circuitry, the VREF pin should be configured as an analog pin and skipped by the Digital Crossbar. Refer to Section "19. Port Input/Output" on page 169 for the location of the VREF pin, as well as details of how to configure the pin in analog mode and to be skipped by the crossbar. If VDD is selected as the voltage reference in the REF0CN register and the ADC is enabled in the ADC0CN register, the P0.0/VREF pin cannot operate as a general purpose I/O pin in open-drain mode. With the above settings, this pin can operate in push-pull output mode or as an analog input.

Figure 7.1. Voltage Reference Functional Block Diagram

### SFR Definition 10.3. SP: Stack Pointer

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---------|---|---|---|---|---|---|---|--|

| Name  | SP[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W     |   |   |   |   |   |   |   |  |

| Reset | 0       | 0 | 0 | 0 | 0 | 1 | 1 | 1 |  |

SFR Address = 0x81; SFR Page = All Pages

| Bit | Name    | Function                                                                                                                                                                  |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                            |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incremented before every PUSH operation. The SP register defaults to 0x07 after reset. |

### SFR Definition 10.4. ACC: Accumulator

| Bit   | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|----------|---|---|---|---|---|---|--|--|

| Name  |   | ACC[7:0] |   |   |   |   |   |   |  |  |

| Туре  |   | R/W      |   |   |   |   |   |   |  |  |

| Reset | 0 | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xE0; SFR Page = All Pages; Bit-Addressable

| Bit | Name     | Function                                                    |

|-----|----------|-------------------------------------------------------------|

| 7:0 | ACC[7:0] | Accumulator.                                                |

|     |          | This register is the accumulator for arithmetic operations. |

### SFR Definition 10.5. B: B Register

| Bit   | 7      | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------|-----|---|---|---|---|---|---|--|

| Name  | B[7:0] |     |   |   |   |   |   |   |  |

| Туре  |        | R/W |   |   |   |   |   |   |  |

| Reset | 0      | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xF0; SFR Page = All Pages; Bit-Addressable

| Bi  | Name   | Function                                                                        |

|-----|--------|---------------------------------------------------------------------------------|

| 7:0 | B[7:0] | B Register.                                                                     |

|     |        | This register serves as a second accumulator for certain arithmetic operations. |

C8051F550/1/2/3 C8051F560/1/2/3/8/9

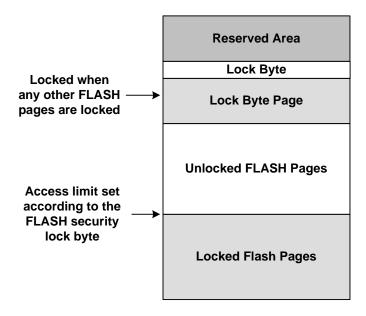

C8051F570/1 0x7FFF **Reserved Area** 0x7C00 Lock Byte 0x7BFF FLASH memory organized in 0x7BFE C8051F554/5/6/7 Lock Byte Page 0x7A00 C8051F564/5/6/7 512-byte pages C8051F572/3/4/5 Lock Byte 0x3FFF 0x3FFE Flash Memory Space **Lock Byte Page** 0x3E00 (32 kB Flash Device) Flash Memory Space (16 kB Flash Device) 0x0000 0x0000

Figure 11.2. Flash Program Memory Map

### 11.1.1. MOVX Instruction and Program Memory

The MOVX instruction in an 8051 device is typically used to access external data memory. On the C8051F55x/56x/57x devices, the MOVX instruction is normally used to read and write on-chip XRAM, but can be re-configured to write and erase on-chip Flash memory space. MOVC instructions are always used to read Flash memory, while MOVX write instructions are used to erase and write Flash. This Flash access feature provides a mechanism for the C8051F55x/56x/57x to update program code and use the program memory space for non-volatile data storage. Refer to Section "14. Flash Memory" on page 124 for further details.

#### 11.2. Data Memory

The C8051F55x/56x/57x devices include 2304 bytes of RAM data memory. 256 bytes of this memory is mapped into the internal RAM space of the 8051. The other 2048 bytes of this memory is on-chip "external" memory. The data memory map is shown in Figure 11.1 for reference.

#### 11.2.1. Internal RAM

93

There are 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory. Figure 11.1 illustrates the data memory organization of the

Rev. 1.2

CHICAN LARC

Table 12.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Description                       | Page |

|----------|---------|-----------------------------------|------|

| PCA0CPH1 | 0xEA    | PCA Capture 1 High                | 299  |

| PCA0CPH2 | 0xEC    | PCA Capture 2 High                | 299  |

| PCA0CPH3 | 0xEE    | PCA Capture 3 High                | 299  |

| PCA0CPH4 | 0xFE    | PCA Capture 4 High                | 299  |

| PCA0CPH5 | 0xCF    | PCA Capture 5 High                | 299  |

| PCA0CPL0 | 0xFB    | PCA Capture 0 Low                 | 299  |

| PCA0CPL1 | 0xE9    | PCA Capture 1 Low                 | 299  |

| PCA0CPL2 | 0xEB    | PCA Capture 2 Low                 | 299  |

| PCA0CPL3 | 0xED    | PCA Capture 3 Low                 | 299  |

| PCA0CPL4 | 0xFD    | PCA Capture 4 Low                 | 299  |

| PCA0CPL5 | 0xCE    | PCA Capture 5 Low                 | 299  |

| PCA0CPM0 | 0xDA    | PCA Module 0 Mode Register        | 297  |

| PCA0CPM1 | 0xDB    | PCA Module 1 Mode Register        | 297  |

| PCA0CPM2 | 0xDC    | PCA Module 2 Mode Register        | 297  |

| PCA0CPM3 | 0xDD    | PCA Module 3 Mode Register        | 297  |

| PCA0CPM4 | 0xDE    | PCA Module 4 Mode Register        | 297  |

| PCA0CPM5 | 0xDF    | PCA Module 5 Mode Register        | 297  |

| PCA0H    | 0xFA    | PCA Counter High                  | 298  |

| PCA0L    | 0xF9    | PCA Counter Low                   | 298  |

| PCA0MD   | 0xD9    | PCA Mode                          | 295  |

| PCA0PWM  | 0xD9    | PCA PWM Configuration             | 296  |

| PCON     | 0x87    | Power Control                     | 137  |

| PSCTL    | 0x8F    | Program Store R/W Control         | 131  |

| PSW      | 0xD0    | Program Status Word               | 90   |

| REF0CN   | 0xD1    | Voltage Reference Control         | 69   |

| REG0CN   | 0xC9    | Voltage Regulator Control         | 80   |

| RSTSRC   | 0xEF    | Reset Source Configuration/Status | 143  |

| SBCON0   | 0xAB    | UART0 Baud Rate Generator Control | 244  |

| SBRLH0   | 0xAD    | UART0 Baud Rate Reload High Byte  | 245  |

| SBRLL0   | 0xAC    | UART0 Baud Rate Reload Low Byte   | 245  |

| SBUF0    | 0x99    | UART0 Data Buffer                 | 244  |

| SCON0    | 0x98    | UART0 Control                     | 241  |

| SFR0CN   | 0x84    | SFR Page Control                  | 102  |

| SFRLAST  | 0x86    | SFR Stack Last Page               | 105  |

| SFRNEXT  | 0x85    | SFR Stack Next Page               | 104  |

| SFRPAGE  | 0xA7    | SFR Page Select                   | 103  |

**Table 13.1. Interrupt Summary**

| Interrupt Source              | Interrupt<br>Vector | Priority<br>Order | Pending Flag                                                               | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|-------------------------------|---------------------|-------------------|----------------------------------------------------------------------------|------------------|----------------|--------------------|---------------------|

| Reset                         | 0x0000              | Тор               | None                                                                       | N/A              | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0 (INT0)   | 0x0003              | 0                 | IE0 (TCON.1)                                                               | Υ                | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow              | 0x000B              | 1                 | TF0 (TCON.5)                                                               | Υ                | Υ              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1 (INT1)   | 0x0013              | 2                 | IE1 (TCON.3)                                                               | Υ                | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow              | 0x001B              | 3                 | TF1 (TCON.7)                                                               | Υ                | Υ              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                         | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Υ                | N              | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow              | 0x002B              | 5                 | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Υ                | N              | ET2 (IE.5)         | PT2 (IP.5)          |

| SPI0                          | 0x0033              | 6                 | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                | N              | ESPI0<br>(IE.6)    | PSPI0<br>(IP.6)     |

| SMB0                          | 0x003B              | 7                 | SI (SMB0CN.0)                                                              | Υ                | N              | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| ADC0 Window Compare           | 0x0043              | 8                 | AD0WINT<br>(ADC0CN.3)                                                      | Υ                | N              | EWADC0<br>(EIE1.1) | PWADC0<br>(EIP1.1)  |

| ADC0 Conversion<br>Complete   | 0x004B              | 9                 | ADOINT (ADCOCN.5)                                                          | Υ                | N              | EADC0<br>(EIE1.2)  | PADC0<br>(EIP1.2)   |

| Programmable<br>Counter Array | 0x0053              | 10                | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)<br>COVF (PCA0PWM.6)                       | Y                | N              | EPCA0<br>(EIE1.3)  | PPCA0<br>(EIP1.3)   |

| Comparator0                   | 0x005B              | 11                | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | N                | N              | ECP0<br>(EIE1.4)   | PCP0<br>(EIP1.4)    |

| Comparator1                   | 0x0063              | 12                | CP1FIF (CPT1CN.4)<br>CP1RIF (CPT1CN.5)                                     | N                | N              | ECP1<br>(EIE1.5)   | PCP1<br>(EIP1.5)    |

| Timer 3 Overflow              | 0x006B              | 13                | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | N                | N              | ET3<br>(EIE1.6)    | PT3<br>(EIP1.6)     |

| LIN0                          | 0x0073              | 14                | LINOINT (LINST.3)                                                          | N                | N*             | ELIN0<br>(EIE1.7)  | PLIN0<br>(EIP1.7)   |

| Voltage Regulator<br>Dropout  | 0x007B              | 15                | N/A                                                                        | N/A              | N/A            | EREG0<br>(EIE2.0)  | PREG0<br>(EIP2.0)   |

| CAN0                          | 0x0083              | 16                | CANOINT<br>(CANOCN.7)                                                      | N                | Υ              | ECAN0<br>(EIE2.1)  | PCAN0<br>(EIP2.1)   |

| Port Match                    | 0x008B              | 17                | None                                                                       | N/A              | N/A            | EMAT<br>(EIE2.2)   | PMAT<br>(EIP2.2)    |

| *Note: The LIN0INT bit i      | s cleared by s      | etting RSTII      | NT (LINCTRL.3)                                                             | •                | •              |                    | · · · · · ·         |

### 14.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. Note: MOVX read instructions always target XRAM.

### 14.3. Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to 1 before software can modify the Flash memory; both PSWE and PSEE must be set to 1 before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

A Security Lock Byte located at the last byte of Flash user space offers protection of the Flash program memory from access (reads, writes, or erases) by unprotected code or the C2 interface. The Flash security mechanism allows the user to lock n 512-byte Flash pages, starting at page 0 (addresses 0x0000 to 0x01FF), where n is the ones complement number represented by the Security Lock Byte. Note that the page containing the Flash Security Lock Byte is unlocked when no other Flash pages are locked (all bits of the Lock Byte are 1) and locked when any other Flash pages are locked (any bit of the Lock Byte is 0). See example in Figure 14.1.

| Security Lock Byte: | 11111101b                                  |

|---------------------|--------------------------------------------|

| 1s Complement:      | 0000010b                                   |

| Flash pages locked: | 3 (First two Flash pages + Lock Byte Page) |

Figure 14.1. Flash Program Memory Map

SILICON LABS

### 16.2. Power-Fail Reset/V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the  $\overline{RST}$  pin low and hold the CIP-51 in a reset state (see Figure 16.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads 1, the data may no longer be valid. The  $V_{DD}$  monitor is enabled after power-on resets. Its defined state (enabled/disabled) is not altered by any other reset source. For example, if the  $V_{DD}$  monitor is disabled by code and a software reset is performed, the  $V_{DD}$  monitor will still be disabled after the reset. To protect the integrity of Flash contents, the  $V_{DD}$  monitor must be enabled to the higher setting (VDMLVL = 1) and selected as a reset source if software contains routines which erase or write Flash memory. If the  $V_{DD}$  monitor is not enabled and set to the high level, any erase or write performed on Flash memory will cause a Flash Error device reset.

**Important Note:** If the  $V_{DD}$  monitor is being turned on from a disabled state, it should be enabled before it is selected as a reset source. Selecting the  $V_{DD}$  monitor as a reset source before it is enabled and stabilized may cause a system reset. In some applications, this reset may be undesirable. If this is not desirable in the application, a delay should be introduced between enabling the monitor and selecting it as a reset source. The procedure for enabling the  $V_{DD}$  monitor and configuring it as a reset source from a disabled state is as follows:

- 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDM0CN = 1).

- If necessary, wait for the V<sub>DD</sub> monitor to stabilize (see Table 5.4 for the V<sub>DD</sub> Monitor turn-on time).

Note: This delay should be omitted if software contains routines that erase or write Flash memory.

- 3. Select the V<sub>DD</sub> monitor as a reset source (PORSF bit in RSTSRC = 1).

See Figure 16.2 for  $V_{DD}$  monitor timing; note that the power-on-reset delay is not incurred after a  $V_{DD}$  monitor reset. See Table 5.4 for complete electrical characteristics of the  $V_{DD}$  monitor.

Note: The output of the internal voltage regulator is calibrated by the MCU immediately after any reset event. The output of the un-calibrated internal regulator could be below the high threshold setting of the V<sub>DD</sub> Monitor. If this is the case *and* the V<sub>DD</sub> Monitor is set to the high threshold setting *and* if the MCU receives a non-power on reset (POR), the MCU will remain in reset until a POR occurs (i.e., V<sub>DD</sub> Monitor will keep the device in reset). A POR will force the V<sub>DD</sub> Monitor to the low threshold setting which is guaranteed to be below the un-calibrated output of the internal regulator. The device will then exit reset and resume normal operation. It is for this reason Silicon Labs strongly recommends that the V<sub>DD</sub> Monitor is always left in the low threshold setting (i.e. default value upon POR)

When programming the Flash in-system, the  $V_{DD}$  Monitor must be set to the high threshold setting. For the highest system reliability, the time the  $V_{DD}$  Monitor is set to the high threshold setting should be minimized (e.g., setting the  $V_{DD}$  Monitor to the high threshold setting just before the Flash write operation and then changing it back to the low threshold setting immediately after the Flash write operation).

**Note:** The V<sub>DD</sub> Monitor may trigger on fast changes in voltage on the VDD pin, regardless of whether the voltage increased or decreased.

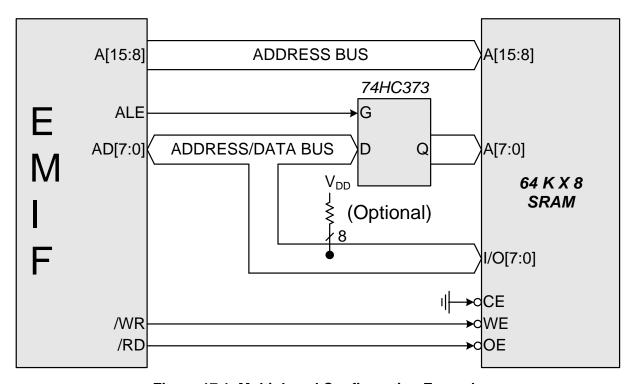

### 17.4. Multiplexed Mode

The External Memory Interface operates only in a Multiplexed mode. In Multiplexed mode, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. In this mode, an external latch (74HC373 or equivalent logic gate) is used to hold the lower 8-bits of the RAM address. The external latch is controlled by the ALE (Address Latch Enable) signal, which is driven by the External Memory Interface logic. An example of a Multiplexed Configuration is shown in Figure 17.1.

In Multiplexed mode, the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the Q outputs reflect the states of the 'D' inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time  $\overline{RD}$  or  $\overline{WR}$  is asserted.

See Section "17.6.1. Multiplexed Mode" on page 153 for more information.

Figure 17.1. Multiplexed Configuration Example

### 18.2. Programmable Internal Oscillator

All C8051F55x/56x/57x devices include a programmable internal high-frequency oscillator that defaults as the system clock after a system reset. The internal oscillator period can be adjusted via the OSCICRS and OSCIFIN registers defined in SFR Definition 18.3 and SFR Definition 18.4. On C8051F55x/56x/57x devices, OSCICRS and OSCIFIN are factory calibrated to obtain a 24 MHz base frequency. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, 8, 16, 32, 64, or 128, as defined by the IFCN bits in register OSCICN. The divide value defaults to 128 following a reset.

### 18.2.1. Internal Oscillator Suspend Mode

When software writes a logic 1 to SUSPEND (OSCICN.5), the internal oscillator is suspended. If the system clock is derived from the internal oscillator, the input clock to the peripheral or CIP-51 will be stopped until one of the following events occur:

- Port 0 Match Event.

- Port 1 Match Event.

- Port 2 Match Event.

- Port 3 Match Event.

- Comparator 0 enabled and output is logic 0.

When one of the oscillator awakening events occur, the internal oscillator, CIP-51, and affected peripherals resume normal operation, regardless of whether the event also causes an interrupt. The CPU resumes execution at the instruction following the write to SUSPEND.

Note: Before entering suspend mode, firmware must set the ZTCEN bit in REF0CN (SFR Definition 7.1).

- 3. The LIN controller does not directly support LIN Version 1.3 Extended Frames. If the application detects an unknown identifier (e.g. extended identifier), it has to write a 1 to the STOP bit (LINOCTRL.7) instead of setting the DTACK (LINOCTRL.4) bit. At that time, steps 2 through 5 can then be skipped. In this situation, the LIN controller stops the processing of LIN communication until the next SYNC BREAK is received.

- 4. Changing the configuration of the checksum during a transaction will cause the interface to reset and the transaction to be lost. To prevent this, the checksum should not be configured while a transaction is in progress. The same applies to changes in the LIN interface mode from slave mode to master mode and from master mode to slave mode.

### 20.5. Sleep Mode and Wake-Up

To reduce the system's power consumption, the LIN Protocol Specification defines a Sleep Mode. The message used to broadcast a Sleep Mode request must be transmitted by the LIN master application in the same way as a normal transmit message. The LIN slave application must decode the Sleep Mode Frame from the Identifier and data bytes. After that, it has to put the LIN slave node into the Sleep Mode by setting the SLEEP bit (LINOCTRL.6).

If the SLEEP bit (LINOCTRL.6) of the LIN slave application is not set and there is no bus activity for four seconds (specified bus idle timeout), the IDLTOUT bit (LINOST.6) is set and an interrupt request is generated. After that the application may assume that the LIN bus is in Sleep Mode and set the SLEEP bit (LINOCTRL.6).

Sending a wake-up signal from the master or any slave node terminates the Sleep Mode of the LIN bus. To send a wake-up signal, the application has to set the WUPREQ bit (LINOCTRL.1). After successful transmission of the wake-up signal, the DONE bit (LINOST.0) of the master node is set and an interrupt request is generated. The LIN slave does not generate an interrupt request after successful transmission of the wake-up signal but it generates an interrupt request if the master does not respond to the wake-up signal within 150 milliseconds. In that case, the ERROR bit (LINOST.2) and TOUT bit (LINOERR.2) are set. The application then has to decide whether or not to transmit another wake-up signal.

All LIN nodes that detect a wake-up signal will set the WAKEUP (LIN0ST.1) and DONE bits (LIN0ST.0) and generate an interrupt request. After that, the application has to clear the SLEEP bit (LIN0CTRL.6) in the LIN slave.

### 20.6. Error Detection and Handling

The LIN controller generates an interrupt request and stops the processing of the current frame if it detects an error. The application has to check the type of error by processing LIN0ERR. After that, it has to reset the error register and the ERROR bit (LIN0ST.2) by writing a 1 to the RSTERR bit (LIN0CTRL.2). Starting a new message with the LIN controller selected as master or sending a Wakeup signal with the LIN controller selected as a master or slave is possible only if the ERROR bit (LIN0ST.2) is set to 0.

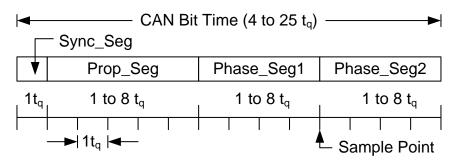

Figure 21.3. Four segments of a CAN Bit

The length of the 4 bit segments must be adjusted so that their sum is as close as possible to the desired bit time. Since each segment must be an integer multiple of the time quantum (tq), the closest achievable bit time is 24 tg (1000.008 ns), yielding a bit rate of 0.999992 Mbit/sec. The Sync Seg is a constant 1 tg. The Prop Seg must be greater than or equal to the propagation delay of 400 ns and so the choice is 10 tg (416.67 ns).

The remaining time quanta (13 tq) in the bit time are divided between Phase\_Seg1 and Phase\_Seg2 as shown in. Based on this equation, Phase\_Seg1 = 6 tq and Phase\_Seg2 = 7 tq.

- 1. If Phase\_Seg1 + Phase\_Seg2 is even, then Phase\_Seg2 = Phase\_Seg1. If the sum is odd, Phase\_Seg2 = Phase Seg1 + 1.

- 2. Phase\_Seg2 should be at least 2 tq.

#### **Equation 21.1. Assigning the Phase Segments**

The Synchronization Jump Width (SJW) timing parameter is defined by. It is used for determining the value written to the Bit Timing Register and for determining the required oscillator tolerance. Since we are using a quartz crystal as the system clock source, an oscillator tolerance calculation is not needed.

SJW = minimum (4, Phase Seg1)

#### **Equation 21.2. Synchronization Jump Width (SJW)**

The value written to the Bit Timing Register can be calculated using Equation 18.3. The BRP Extension register is left at its reset value of 0x0000.

$$BRPE = BRP - 1 = BRP \ Extension \ Register = 0x0000$$

$$SJWp = SJW - 1 = minimum \ (4, 6) - 1 = 3$$

$$TSEG1 = Prop\_Seg + Phase\_Seg1 - 1 = 10 + 6 - 1 = 15$$

$$TSEG2 = Phase\_Seg2 - 1 = 6$$

$$Bit \ Timing \ Register = (TSEG2 \times 0x1000) + (TSEG1 \times 0x0100)$$

$$Bit \ Timing \ Register = (TSEG2 \times 0x1000) + (SJWp \times 0x0040) + BRPE = 0x6FC0$$

Equation 21.3. Calculating the Bit Timing Register Value

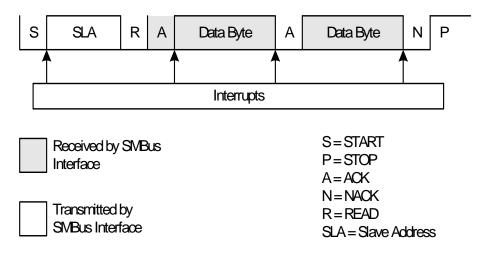

### 22.5.2. Read Sequence (Master)

During a read sequence, an SMBus master reads data from a slave device. The master in this transfer will be a transmitter during the address byte, and a receiver during all data bytes. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 (READ). Serial data is then received from the slave on SDA while the SMBus outputs the serial clock. The slave transmits one or more bytes of serial data. An interrupt is generated after each received byte.

Software must write the ACK bit at that time to ACK or NACK the received byte. Writing a 1 to the ACK bit generates an ACK; writing a 0 generates a NACK. Software should write a 0 to the ACK bit for the last data transfer, to transmit a NACK. The interface exits Master Receiver Mode after the STO bit is set and a STOP is generated. The interface will switch to Master Transmitter Mode if SMB0DAT is written while an active Master Receiver. Figure 22.6 shows a typical master read sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur **before** the ACK cycle in this mode.

Figure 22.6. Typical Master Read Sequence

### 23.3. Configuration and Operation

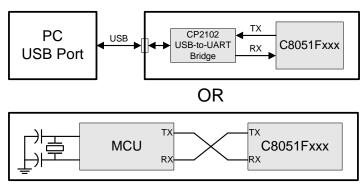

UARTO provides standard asynchronous, full duplex communication. It can operate in a point-to-point serial communications application, or as a node on a multi-processor serial interface. To operate in a pointto-point application, where there are only two devices on the serial bus, the MCE0 bit in SMOD0 should be cleared to 0. For operation as part of a multi-processor communications bus, the MCE0 and XBE0 bits should both be set to 1. In both types of applications, data is transmitted from the microcontroller on the TX0 pin, and received on the RX0 pin. The TX0 and RX0 pins are configured using the crossbar and the Port I/O registers, as detailed in Section "19. Port Input/Output" on page 169.

In typical UART communications, The transmit (TX) output of one device is connected to the receive (RX) input of the other device, either directly or through a bus transceiver, as shown in Figure 23.5.

Figure 23.5. Typical UART Interconnect Diagram

#### 23.3.1. Data Transmission

Data transmission is double-buffered and begins when software writes a data byte to the SBUF0 register. Writing to SBUF0 places data in the Transmit Holding Register, and the Transmit Holding Register Empty flag (THRE0) will be cleared to 0. If the UART's shift register is empty (i.e., no transmission in progress), the data will be placed in the Transmit Holding Register until the current transmission is complete. The TIO Transmit Interrupt Flag (SCON0.1) will be set at the end of any transmission (the beginning of the stop-bit time). If enabled, an interrupt will occur when TI0 is set.

**Note:** THRE0 can have a momentary glitch high when the UART Transmit Holding Register is not empty. The glitch will occur some time after SBUF0 was written with the previous byte and does not occur if THRE0 is checked in the instruction(s) immediately following the write to SBUF0. When firmware writes SBUF0 and SBUF0 is not empty, TX0 will be stuck low until the next device reset. Firmware should use or poll on TIO rather than THREO for asynchronous UART writes that may have a random delay in between transactions.

If the extra bit function is enabled (XBE0 = 1) and the parity function is disabled (PE0 = '0'), the value of the TBX0 (SCON0.3) bit will be sent in the extra bit position. When the parity function is enabled (PE0 = 1), hardware will generate the parity bit according to the selected parity type (selected with S0PT[1:0]), and append it to the data field. Note: when parity is enabled, the extra bit function is not available.

#### 23.3.2. Data Reception

Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be stored in the receive FIFO if the following conditions are met: the receive FIFO (3 bytes deep) must not be full, and the stop bit(s) must be logic 1. In the event that the receive FIFO is full, the incoming byte will be lost, and a Receive FIFO Overrun Error will be generated (OVR0 in register SCON0 will be set to logic 1). If the stop bit(s) were logic 0, the incoming data will not be stored in the receive FIFO. If the reception conditions are met, the data is stored in the receive FIFO, and

### SFR Definition 23.2. SMOD0: Serial Port 0 Control

| Bit   | 7    | 6         | 5 | 4   | 3         | 2   | 1    | 0    |

|-------|------|-----------|---|-----|-----------|-----|------|------|

| Name  | MCE0 | S0PT[1:0] |   | PE0 | S0DL[1:0] |     | XBE0 | SBL0 |

| Туре  | R/W  | R/W       | R | R/W | R/W       | R/W | R/W  | R/W  |

| Reset | 0    | 0         | 0 | 0   | 1         | 1   | 0    | 0    |

SFR Address = 0xA9: SFR Page = 0x00

|     |           | xA9; SFR Page = 0x00                                                                                                                                                  |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name      | Function                                                                                                                                                              |

| 7   | MCE0      | Multiprocessor Communication Enable.                                                                                                                                  |

|     |           | <ul><li>0: RI0 will be activated if stop bit(s) are 1.</li><li>1: RI0 will be activated if stop bit(s) and extra bit are 1. Extra bit must be enabled using</li></ul> |

|     |           | XBE0.                                                                                                                                                                 |

| 6:5 | S0PT[1:0] | Parity Type Select Bits.                                                                                                                                              |

|     |           | 00: Odd Parity                                                                                                                                                        |

|     |           | 01: Even Parity                                                                                                                                                       |

|     |           | 10: Mark Parity                                                                                                                                                       |

|     |           | 11: Space Parity.                                                                                                                                                     |

| 4   | PE0       | Parity Enable.                                                                                                                                                        |

|     |           | This bit enables hardware parity generation and checking. The parity type is selected by bits S0PT[1:0] when parity is enabled.                                       |

|     |           | 0: Hardware parity is disabled.                                                                                                                                       |

|     |           | 1: Hardware parity is enabled.                                                                                                                                        |

| 3:2 | S0DL[1:0] | Data Length.                                                                                                                                                          |

|     |           | 00: 5-bit data                                                                                                                                                        |

|     |           | 01: 6-bit data                                                                                                                                                        |

|     |           | 10: 7-bit data                                                                                                                                                        |

|     |           | 11: 8-bit data                                                                                                                                                        |

| 1   | XBE0      | Extra Bit Enable.                                                                                                                                                     |

|     |           | When enabled, the value of TBX0 will be appended to the data field                                                                                                    |

|     |           | 0: Extra Bit is disabled.                                                                                                                                             |

|     | 001.0     | 1: Extra Bit is enabled.                                                                                                                                              |

| 0   | SBL0      | Stop Bit Length.                                                                                                                                                      |

|     |           | 0: Short—stop bit is active for one bit time                                                                                                                          |

|     |           | 1: Long—stop bit is active for two bit times (data length = 6, 7, or 8 bits), or 1.5 bit times (data length = 5 bits).                                                |

### 25.1. Timer 0 and Timer 1

Each timer is implemented as a 16-bit register accessed as two separate bytes: a low byte (TL0 or TL1) and a high byte (TH0 or TH1). The Counter/Timer Control register (TCON) is used to enable Timer 0 and Timer 1 as well as indicate status. Timer 0 interrupts can be enabled by setting the ET0 bit in the IE register (Section "13.2. Interrupt Register Descriptions" on page 115); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register (Section "13.2. Interrupt Register Descriptions" on page 115). Both counter/timers operate in one of four primary modes selected by setting the Mode Select bits T1M1–T0M0 in the Counter/Timer Mode register (TMOD). Each timer can be configured independently. Each operating mode is described below.

#### 25.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 (TCON.5) is set and an interrupt will occur if Timer 0 interrupts are enabled.

The C/T0 bit (TMOD.2) selects the counter/timer's clock source. When C/T0 is set to logic 1, high-to-low transitions at the selected Timer 0 input pin (T0) increment the timer register (Refer to Section "19.3. Priority Crossbar Decoder" on page 172 for information on selecting and configuring external I/O pins). Clearing C/T selects the clock defined by the T0M bit (CKCON.3). When T0M is set, Timer 0 is clocked by the system clock. When T0M is cleared, Timer 0 is clocked by the source selected by the Clock Scale bits in CKCON (see SFR Definition 25.1).

Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see SFR Definition 13.7). Setting GATE0 to 1 allows the timer to be controlled by the external input signal INT0 (see Section "13.2. Interrupt Register Descriptions" on page 115), facilitating pulse width measurements.

| TR0             | GATE0                | Counter/Timer |          |  |  |  |

|-----------------|----------------------|---------------|----------|--|--|--|

| 0               | Х                    | Х             | Disabled |  |  |  |

| 1               | 0                    | Х             | Enabled  |  |  |  |

| 1               | 1 1 0 Disabled       |               |          |  |  |  |

| 1               | 1                    | 1             | Enabled  |  |  |  |

| Note: X = Don't | Note: X = Don't Care |               |          |  |  |  |

Setting TR0 does not force the timer to reset. The timer registers should be loaded with the desired initial value before the timer is enabled.

TL1 and TH1 form the 13-bit register for Timer 1 in the same manner as described above for TL0 and TH0. Timer 1 is configured and controlled using the relevant TCON and TMOD bits just as with Timer 0. The input signal  $\overline{\text{INT1}}$  is used with Timer 1; the  $\overline{\text{INT1}}$  polarity is defined by bit IN1PL in register IT01CF (see SFR Definition 13.7).

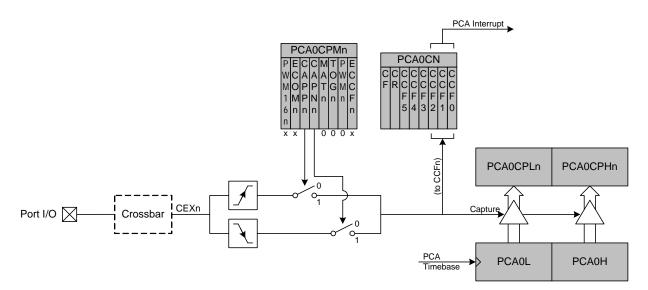

Figure 26.4. PCA Capture Mode Diagram

**Note:** The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.

### 26.3.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

## SFR Definition 26.2. PCA0MD: PCA Mode

| Bit   | 7    | 6    | 5     | 4 | 3        | 2   | 1   | 0   |

|-------|------|------|-------|---|----------|-----|-----|-----|

| Name  | CIDL | WDTE | WDLCK |   | CPS[2:0] |     |     | ECF |

| Туре  | R/W  | R/W  | R/W   | R | R/W      | R/W | R/W | R/W |

| Reset | 0    | 1    | 0     | 0 | 0        | 0   | 0   | 0   |

SFR Address = 0xD9; SFR Page = 0x00

| Bit | Name     | Function                                                                                                                                 |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CIDL     | PCA Counter/Timer Idle Control.                                                                                                          |

|     |          | Specifies PCA behavior when CPU is in Idle Mode.                                                                                         |

|     |          | 0: PCA continues to function normally while the system controller is in Idle Mode.                                                       |

|     |          | 1: PCA operation is suspended while the system controller is in Idle Mode.                                                               |

| 6   | WDTE     | Watchdog Timer Enable                                                                                                                    |

|     |          | If this bit is set, PCA Module 5 is used as the watchdog timer.                                                                          |

|     |          | 0: Watchdog Timer disabled.                                                                                                              |

|     |          | 1: PCA Module 5 enabled as Watchdog Timer.                                                                                               |

| 5   | WDLCK    | Watchdog Timer Lock                                                                                                                      |

|     |          | This bit locks/unlocks the Watchdog Timer Enable. When WDLCK is set, the Watchdog Timer may not be disabled until the next system reset. |

|     |          | 0: Watchdog Timer Enable unlocked.                                                                                                       |

|     |          | 1: Watchdog Timer Enable locked.                                                                                                         |

| 4   | Unused   | Read = 0b, Write = Don't care.                                                                                                           |

| 3:1 | CPS[2:0] | PCA Counter/Timer Pulse Select.                                                                                                          |

|     |          | These bits select the timebase source for the PCA counter                                                                                |

|     |          | 000: System clock divided by 12                                                                                                          |

|     |          | 001: System clock divided by 4                                                                                                           |

|     |          | 010: Timer 0 overflow                                                                                                                    |

|     |          | 011: High-to-low transitions on ECI (max rate = system clock divided by 4)                                                               |

|     |          | 100: System clock                                                                                                                        |

|     |          | 101: External clock divided by 8 (synchronized with the system clock) 11x: Reserved                                                      |

|     | FOF      |                                                                                                                                          |

| 0   | ECF      | PCA Counter/Timer Overflow Interrupt Enable.                                                                                             |

|     |          | This bit sets the masking of the PCA Counter/Timer Overflow (CF) interrupt.                                                              |

|     |          | 0: Disable the CF interrupt.                                                                                                             |

|     |          | 1: Enable a PCA Counter/Timer Overflow interrupt request when CF (PCA0CN.7) is set.                                                      |

|     |          | 1001.                                                                                                                                    |

**Note:** When the WDTE bit is set to 1, the other bits in the PCA0MD register cannot be modified. To change the contents of the PCA0MD register, the Watchdog Timer must first be disabled.