Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), LINbus, SPI, UART/USART        |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 2.25К х 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | A/D 25x12b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                              |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 32-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f566-imr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

been accumulated. Similarly, the Window Comparator will not compare the result to the greater-than and less-than registers until "repeat count" conversions have been accumulated.

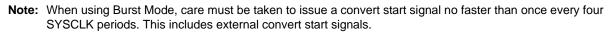

C = Converting

### Figure 6.4. 12-Bit ADC Burst Mode Example With Repeat Count Set to 4

# 7. Voltage Reference

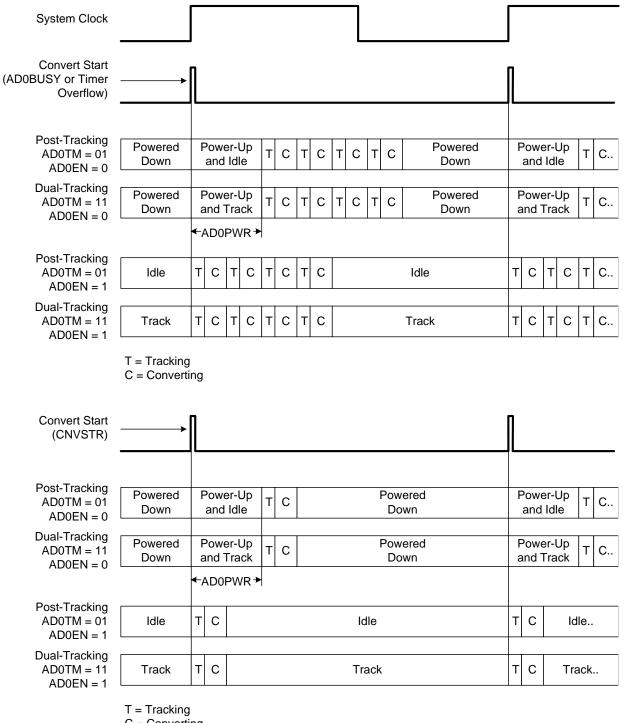

The Voltage reference multiplexer on the C8051F55x/56x/57x devices is configurable to use an externally connected voltage reference, the on-chip reference voltage generator routed to the VREF pin, or the V<sub>DD</sub> power supply voltage (see Figure 7.1). The REFSL bit in the Reference Control register (REF0CN, SFR Definition 7.1) selects the reference source for the ADC. For an external source or the on-chip reference, REFSL should be set to 0 to select the VREF pin. To use V<sub>DD</sub> as the reference source, REFSL should be set to 1.

The BIASE bit enables the internal voltage bias generator, which is used by the ADC, Temperature Sensor, and internal oscillator. This bias is automatically enabled when any peripheral which requires it is enabled, and it does not need to be enabled manually. The bias generator may be enabled manually by writing a 1 to the BIASE bit in register REFOCN. The electrical specifications for the voltage reference circuit are given in Table 5.11.

The on-chip voltage reference circuit consists of a temperature stable bandgap voltage reference generator and a gain-of-two output buffer amplifier. The output voltage is selectable between 1.5 V and 2.25 V. The on-chip voltage reference can be driven on the VREF pin by setting the REFBE bit in register REF0CN to a 1. The maximum load seen by the VREF pin must be less than 200  $\mu$ A to GND. Bypass capacitors of 0.1  $\mu$ F and 4.7  $\mu$ F are recommended from the VREF pin to GND. If the on-chip reference is not used, the REFBE bit should be cleared to 0. Electrical specifications for the on-chip voltage reference are given in Table 5.11.

**Important Note about the VREF Pin:** When using either an external voltage reference or the on-chip reference circuitry, the VREF pin should be configured as an analog pin and skipped by the Digital Crossbar. Refer to Section "19. Port Input/Output" on page 169 for the location of the VREF pin, as well as details of how to configure the pin in analog mode and to be skipped by the crossbar. If VDD is selected as the voltage reference in the REF0CN register and the ADC is enabled in the ADC0CN register, the P0.0/VREF pin cannot operate as a general purpose I/O pin in open-drain mode. With the above settings, this pin can operate in push-pull output mode or as an analog input.

Figure 7.1. Voltage Reference Functional Block Diagram

Note that false rising edges and falling edges can be detected when the comparator is first powered on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed.

## SFR Definition 8.1. CPT0CN: Comparator0 Control

| Bit   | 7     | 6      | 5      | 4      | 3     | 2       | 1    | 0       |

|-------|-------|--------|--------|--------|-------|---------|------|---------|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0H) | /P[1:0] | CP0H | /N[1:0] |

| Туре  | R/W   | R      | R/W    | R/W    | R/W   |         | R/   | W       |

| Reset | 0     | 0      | 0      | 0      | 0     | 0       | 0    | 0       |

SFR Address = 0x9A; SFR Page = 0x00

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0–.                                                    |

|     |             | 1: Voltage on CP0+ > CP0                                                      |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3:2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

# C8051F55x/56x/57x

# SFR Definition 8.5. CPT0MX: Comparator0 MUX Selection

| Bit   | 7             | 6           | 5                 | 4                                                  | 3            | 2            | 1          | 0 |  |

|-------|---------------|-------------|-------------------|----------------------------------------------------|--------------|--------------|------------|---|--|

| Nam   | е             | CMX0        | N[3:0]            | I                                                  | CMX0P[3:0]   |              |            |   |  |

| Туре  | •             | R/          | W                 |                                                    |              | R/           | W          |   |  |

| Rese  | et 0          | 1           | 1                 | 1                                                  | 0            | 1            | 1          | 1 |  |

| SFR A | Address = 0x9 | C; SFR Page | $e = 0 \times 00$ |                                                    |              |              |            |   |  |

| Bit   | Name          | _           |                   |                                                    | Function     |              |            |   |  |

| 7:4   | CMX0N[3:0]    | Comparato   | r0 Negative       | Input MUX                                          | Selection.   |              |            |   |  |

|       |               | 0000:       | P0.               | 1                                                  |              |              |            |   |  |

|       |               | 0001:       | P0.               | 3                                                  |              |              |            |   |  |

|       |               | 0010:       | P0.               | 5                                                  |              |              |            |   |  |

|       |               | 0011:       | P0.               | 7                                                  |              |              |            |   |  |

|       |               | 0100:       | P1.               | 1                                                  |              |              |            |   |  |

|       |               | 0101:       | P1.               | 3                                                  |              |              |            |   |  |

|       |               | 0110:       | P1.               | 5                                                  |              |              |            |   |  |

|       |               | 0111:       | P1.               | 7                                                  |              |              |            |   |  |

|       |               | 1000:       | P2.               | 1                                                  |              |              |            |   |  |

|       |               | 1001:       | P2.               | 3 (only avail                                      | able on 40-p | in and 32-pi | n devices) |   |  |

|       |               | 1010:       | P2.               | P2.5 (only available on 40-pin and 32-pin devices) |              |              |            |   |  |

|       |               | 1011:       | P2.               | 7 (only avail                                      | able on 40-p | in and 32-pi | n devices) |   |  |

|       |               | 1100–11111: | Nor               | ne                                                 |              |              |            |   |  |

| 3:0   | CMX0P[3:0]    | Comparato   | r0 Positive       | Input MUX                                          | Selection.   |              |            |   |  |

|       |               | 0000:       | P0.               | 0                                                  |              |              |            |   |  |

|       |               | 0001:       | P0.               | 2                                                  |              |              |            |   |  |

|       |               | 0010:       | P0.               | 4                                                  |              |              |            |   |  |

|       |               | 0011:       | P0.               | 6                                                  |              |              |            |   |  |

|       |               | 0100:       | P1.               | 0                                                  |              |              |            |   |  |

|       |               | 0101:       | P1.               | 2                                                  |              |              |            |   |  |

|       |               | 0110:       | P1.               | 4                                                  |              |              |            |   |  |

|       |               | 0111:       | P1.               | 6                                                  |              |              |            |   |  |

|       |               | 1000:       | P2.               | 0                                                  |              |              |            |   |  |

|       |               | 1001:       | P2.               | 2 (only avail                                      | able on 40-p | in and 32-pi | n devices) |   |  |

|       |               | 1010:       | P2.               | 4 (only avail                                      | able on 40-p | in and 32-pi | n devices) |   |  |

|       |               | 1011:       | P2.               | 6 (only avail                                      | able on 40-p | in and 32-pi | n devices) |   |  |

|       |               | 1100–1111:  | Nor               | ne                                                 |              |              |            |   |  |

# C8051F55x/56x/57x

# Table 10.1. CIP-51 Instruction Set Summary (Continued)

| Mnemonic             | Description                                         | Bytes | Clock<br>Cycles |  |

|----------------------|-----------------------------------------------------|-------|-----------------|--|

| SETB C               | Set Carry                                           | 1     | 1               |  |

| SETB bit             | Set direct bit                                      | 2     | 2               |  |

| CPL C                | Complement Carry                                    | 1     | 1               |  |

| CPL bit              | Complement direct bit                               | 2     | 2               |  |

| ANL C, bit           | AND direct bit to Carry                             | 2     | 2               |  |

| ANL C, /bit          | AND complement of direct bit to Carry               | 2     | 2               |  |

| ORL C, bit           | OR direct bit to carry                              | 2     | 2               |  |

| ORL C, /bit          | OR complement of direct bit to Carry                | 2     | 2               |  |

| MOV C, bit           | Move direct bit to Carry                            | 2     | 2               |  |

| MOV bit, C           | Move Carry to direct bit                            | 2     | 2               |  |

| JC rel               | Jump if Carry is set                                | 2     | 2/(4-6)         |  |

| JNC rel              | Jump if Carry is not set                            | 2     | 2/(4-6)*        |  |

| JB bit, rel          | Jump if direct bit is set                           | 3     | 3/(5-7)*        |  |

| JNB bit, rel         | Jump if direct bit is not set                       | 3     | 3/(5-7)*        |  |

| JBC bit, rel         | Jump if direct bit is set and clear bit             | 3     | 3/(5-7)*        |  |

| Program Branching    |                                                     |       | •               |  |

| ACALL addr11         | Absolute subroutine call                            | 2     | 4-6*            |  |

| LCALL addr16         | Long subroutine call                                | 3     | 5-7*            |  |

| RET                  | Return from subroutine                              | 1     | 6-8*            |  |

| RETI                 | Return from interrupt                               | 1     | 6-8*            |  |

| AJMP addr11          | Absolute jump                                       | 2     | 4-6*            |  |

| LJMP addr16          | Long jump                                           | 3     | 5-7*            |  |

| SJMP rel             | Short jump (relative address)                       | 2     | 4-6*            |  |

| JMP @A+DPTR          | Jump indirect relative to DPTR                      | 1     | 3-5*            |  |

| JZ rel               | Jump if A equals zero                               | 2     | 2/(4-6)*        |  |

| JNZ rel              | Jump if A does not equal zero                       | 2     | 2/(4-6)*        |  |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3     | 4/(6-8)*        |  |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3     | 3/(6-8)*        |  |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3     | 3/(5-7)*        |  |

| CJNE @Ri, #data, rel |                                                     |       | 4/(6-8)*        |  |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2     | 2/(4-6)*        |  |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero          | 3     | 3/(5-7)*        |  |

| NOP                  | No operation                                        | 1     | 1               |  |

# SFR Definition 12.1. SFR0CN: SFR Page Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|-------|---|---|---|---|---|---|---|---------|

| Name  |   |   |   |   |   |   |   | SFRPGEN |

| Туре  | R | R | R | R | R | R | R | R/W     |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1       |

### SFR Address = 0x84; SFR Page = 0x0F

| Bit | Name    | Function                                                                                                                                                                                                                                        |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | Unused  | Read = 0000000b; Write = Don't Care                                                                                                                                                                                                             |

| 0   | SFRPGEN | SFR Automatic Page Control Enable.                                                                                                                                                                                                              |

|     |         | Upon interrupt, the C8051 Core will vector to the specified interrupt service routine<br>and automatically switch the SFR page to the corresponding peripheral or function's<br>SFR page. This bit is used to control this autopaging function. |

|     |         | 0: SFR Automatic Paging disabled. The C8051 core will not automatically change to the appropriate SFR page (i.e., the SFR page that contains the SFRs for the peripheral/function that was the source of the interrupt).                        |

|     |         | 1: SFR Automatic Paging enabled. Upon interrupt, the C8051 will switch the SFR page to the page that contains the SFRs for the peripheral or function that is the source of the interrupt.                                                      |

# Table 12.3. Special Function Registers (Continued)

| Register    | Address | Description                          | Page |

|-------------|---------|--------------------------------------|------|

| IT01CF      | 0xE4    | INT0/INT1 Configuration              | 123  |

| LIN0ADR     | 0xD3    | LIN0 Address                         | 200  |

| LIN0CF      | 0xC9    | LIN0 Configuration                   | 200  |

| LIN0DAT     | 0xD2    | LIN0 Data                            | 201  |

| OSCICN      | 0xA1    | Internal Oscillator Control          | 160  |

| OSCICRS     | 0xA2    | Internal Oscillator Coarse Control   | 161  |

| OSCIFIN     | 0x9E    | Internal Oscillator Fine Calibration | 161  |

| OSCXCN      | 0x9F    | External Oscillator Control          | 165  |

| P0          | 0x80    | Port 0 Latch                         | 183  |

| POMASK      | 0xF2    | Port 0 Mask Configuration            | 179  |

| P0MAT       | 0xF1    | Port 0 Match Configuration           | 179  |

| POMDIN      | 0xF1    | Port 0 Input Mode Configuration      | 184  |

| P0MDOUT     | 0xA4    | Port 0 Output Mode Configuration     | 184  |

| P0SKIP      | 0xD4    | Port 0 Skip                          | 185  |

| P1          | 0x90    | Port 1 Latch                         | 185  |

| P1MASK      | 0xF4    | Port 1 Mask Configuration            | 180  |

| P1MAT       | 0xF3    | Port 1 Match Configuration           | 180  |

| P1MDIN      | 0xF2    | Port 1 Input Mode Configuration      | 186  |

| P1MDOUT     | 0xA5    | Port 1 Output Mode Configuration     | 186  |

| P1SKIP      | 0xD5    | Port 1 Skip                          | 187  |

| P2          | 0xA0    | Port 2 Latch                         | 187  |

| P2MASK      | 0xB2    | Port 2 Mask Configuration            | 181  |

| P2MAT       | 0xB1    | Port 2 Match Configuration           | 181  |

| P2MDIN      | 0xF3    | Port 2 Input Mode Configuration      | 188  |

| P2MDOUT     | 0xA6    | Port 2 Output Mode Configuration     | 188  |

| P2SKIP      | 0xD6    | Port 2 Skip                          | 189  |

| P3          | 0xB0    | Port 3 Latch                         | 189  |

| P3MASK      | 0xAF    | Port 3 Mask Configuration            | 182  |

| P3MAT       | 0xAE    | Port 3 Match Configuration           | 182  |

| P3MDIN      | 0xF4    | Port 3 Input Mode Configuration      | 190  |

| P3MDOUT     | 0xAE    | Port 3 Output Mode Configuration     | 190  |

| P3SKIP 0xD7 |         | Port 3 Skip                          | 191  |

| P4 0xB5 F   |         | Port 4 Latch                         | 191  |

| P4MDOUT     | 0xAF    | Port 4 Output Mode Configuration     | 192  |

| PCA0CN      | 0xD8    | PCA Control                          | 294  |

| PCA0CPH0    | 0xFC    | PCA Capture 0 High                   | 299  |

## 16.1. Power-On Reset

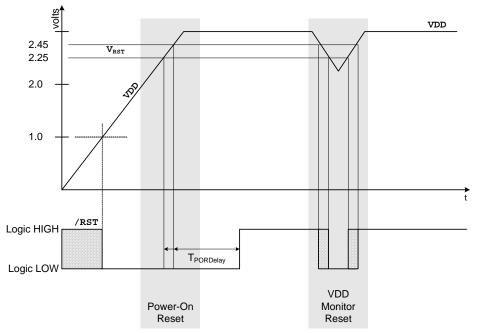

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until V<sub>DD</sub> settles above V<sub>RST</sub>. A delay occurs before the device is released from reset; the delay decreases as the V<sub>DD</sub> ramp time increases (V<sub>DD</sub> ramp time is defined as how fast V<sub>DD</sub> ramps from 0 V to V<sub>RST</sub>). Figure 16.2. plots the power-on and V<sub>DD</sub> monitor reset timing.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The V<sub>DD</sub> monitor is enabled following a power-on reset.

**Note:** For devices with a date code before year 2011, work week 24 (1124), if the /RST pin is held low for more than 1 second while power is applied to the device, and then /RST is released, a percentage of devices may lock up and fail to execute code. Toggling the /RST pin does not clear the condition. The condition is cleared by cycling power. Most devices that are affected will show the lock up behavior only within a narrow range of temperatures (a 5 to 10 °C window). Parts with a date code of year 2011, work week 24 (1124) or later do not have any restrictions on /RST low time. The date code of a device is a four-digit number on the bottom-most line of each device with the format YYWW, where YY is the two-digit calendar year and WW is the two digit work week.

Figure 16.2. Power-On and V<sub>DD</sub> Monitor Reset Timing

| Multiplexed Mode |          |  |  |  |  |

|------------------|----------|--|--|--|--|

| Signal Name      | Port Pin |  |  |  |  |

| RD               | P1.6     |  |  |  |  |

| WR               | P1.7     |  |  |  |  |

| ALE              | P1.5     |  |  |  |  |

| D0/A0            | P3.0     |  |  |  |  |

| D1/A1            | P3.1     |  |  |  |  |

| D2/A2            | P3.2     |  |  |  |  |

| D3/A3            | P3.3     |  |  |  |  |

| D4/A4            | P3.4     |  |  |  |  |

| D5/A5            | P3.5     |  |  |  |  |

| D6/A6            | P3.6     |  |  |  |  |

| D7/A7            | P3.7     |  |  |  |  |

| A8               | P2.0     |  |  |  |  |

| A9               | P2.1     |  |  |  |  |

| A10              | P2.2     |  |  |  |  |

| A11              | P2.3     |  |  |  |  |

| A12              | P2.4     |  |  |  |  |

| A13              | P2.5     |  |  |  |  |

| A14              | P2.6     |  |  |  |  |

| A15              | P2.7     |  |  |  |  |

# Table 17.1. EMIF Pinout (C8051F568-9 and 'F570-5)

# SFR Definition 18.5. CLKMUL: Clock Multiplier

| Bit   | 7     | 6       | 5      | 4           | 3 | 2           | 1  | 0 |

|-------|-------|---------|--------|-------------|---|-------------|----|---|

| Name  | MULEN | MULINIT | MULRDY | MULDIV[2:0] |   | MULSEL[1:0] |    |   |

| Туре  | R/W   | R/W     | R      | R/W         |   |             | R/ | W |

| Reset | 0     | 0       | 0      | 0           | 0 | 0           | 0  | 0 |

#### SFR Address = 0x97; SFR Page = 0x0F

| Bit   | Name        |                                                                                    | Function                                                                                                                                                                                        |                                                                           |  |  |  |  |

|-------|-------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

| 7     | MULEN       | Clock Multiplier Enable.<br>0: Clock Multiplier disabled.                          |                                                                                                                                                                                                 |                                                                           |  |  |  |  |

|       |             |                                                                                    | 1: Clock Multiplier enabled.                                                                                                                                                                    |                                                                           |  |  |  |  |

| 6     | MULINIT     | Clock Multiplie                                                                    | r Initialize.                                                                                                                                                                                   |                                                                           |  |  |  |  |

|       |             | bit will initialize                                                                | This bit is 0 when the Clock Multiplier is enabled. Once enabled, writing a 1 to this bit will initialize the Clock Multiplier. The MULRDY bit reads 1 when the Clock Multiplier is stabilized. |                                                                           |  |  |  |  |

| 5     | MULRDY      | Clock Multiplie                                                                    | r Ready.                                                                                                                                                                                        |                                                                           |  |  |  |  |

|       |             | 0: Clock Multiplier is not ready.<br>1: Clock Multiplier is ready (PLL is locked). |                                                                                                                                                                                                 |                                                                           |  |  |  |  |

| 4:2   | MULDIV[2:0] | Clock Multiplier Output Scaling Factor.                                            |                                                                                                                                                                                                 |                                                                           |  |  |  |  |

|       |             |                                                                                    | iplier Output scaled by a factor o                                                                                                                                                              |                                                                           |  |  |  |  |

|       |             |                                                                                    | iplier Output scaled by a factor o<br>iplier Output scaled by a factor o                                                                                                                        |                                                                           |  |  |  |  |

|       |             |                                                                                    | plier Output scaled by a factor o                                                                                                                                                               |                                                                           |  |  |  |  |

|       |             |                                                                                    | iplier Output scaled by a factor o                                                                                                                                                              |                                                                           |  |  |  |  |

|       |             |                                                                                    | iplier Output scaled by a factor o                                                                                                                                                              |                                                                           |  |  |  |  |

|       |             |                                                                                    | plier Output scaled by a factor o                                                                                                                                                               |                                                                           |  |  |  |  |

|       |             |                                                                                    | plier Output scaled by a factor of                                                                                                                                                              |                                                                           |  |  |  |  |

|       |             |                                                                                    | ck Multiplier output duty cycle is i                                                                                                                                                            | not 50% for these settings.                                               |  |  |  |  |

| 1:0   | MULSEL[1:0] | Clock Multiplie                                                                    | •                                                                                                                                                                                               |                                                                           |  |  |  |  |

|       |             | These bits selec                                                                   | ct the clock supplied to the Clock                                                                                                                                                              | Multiplier                                                                |  |  |  |  |

|       |             | MULSEL[1:0]                                                                        | Selected Input Clock                                                                                                                                                                            | Clock Multiplier Output<br>for MULDIV[2:0] = 000b                         |  |  |  |  |

|       |             | 00 Internal Oscillator Internal Oscillator x 2                                     |                                                                                                                                                                                                 |                                                                           |  |  |  |  |

|       |             | 01 External Oscillator External Oscillator x 2                                     |                                                                                                                                                                                                 |                                                                           |  |  |  |  |

|       |             | 10                                                                                 | 10 Internal Oscillator Internal Oscillator x 4                                                                                                                                                  |                                                                           |  |  |  |  |

|       |             | 11                                                                                 | External Oscillator                                                                                                                                                                             | External Oscillator x 4                                                   |  |  |  |  |

| Notes |             |                                                                                    | IHz, and so the Clock Multiplier outp<br>Oscillator x 2 is selected using the N                                                                                                                 | but should be scaled accordingly.<br>MULSEL bits, MULDIV[2:0] is ignored. |  |  |  |  |

# **19. Port Input/Output**

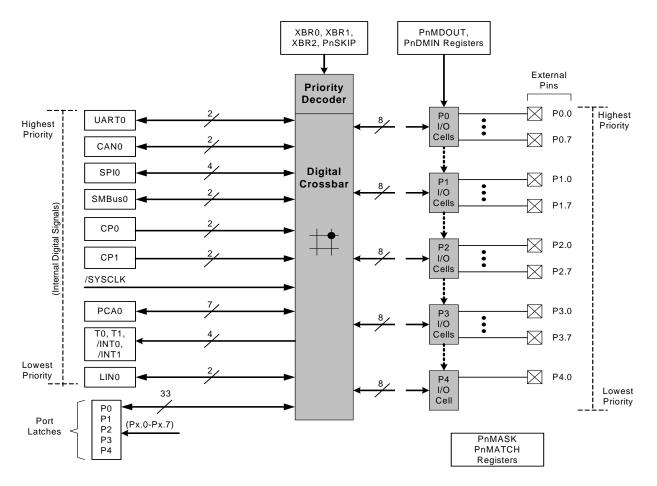

Digital and analog resources are available through 33 (C8051F568-9 and 'F570-5), 25 (C8051F550-7) or 18 (C8051F550-7) I/O pins. Port pins P0.0-P4.0 on the C8051F568-9 and 'F570-5, port pins P0.0-P3.0 on theC8051F560-7, and port pins P0.0-P2.1 on the C8051F550-7 can be defined as general-purpose I/O (GPIO), assigned to one of the internal digital resources, or assigned to an analog function as shown in Figure 19.3. Port pin P4.0 on the C8051F568-9 and 'F570-5 can be used as GPIO and is shared with the C2 Interface Data signal (C2D). Similarly, port pin P3.0 is shared with C2D on the C8051F560-7 and port pin P2.1 on the C8051F550-7. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 19.3 and Figure 19.4). The registers XBR0, XBR1, XBR2 are defined in SFR Definition 19.1 and SFR Definition 19.2 and are used to select internal digital functions.

The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1). Complete Electrical Specifications for Port I/O are given in Table 5.3 on page 40.

Figure 19.1. Port I/O Functional Block Diagram

- 3. The LIN controller does not directly support LIN Version 1.3 Extended Frames. If the application detects an unknown identifier (e.g. extended identifier), it has to write a 1 to the STOP bit (LIN0CTRL.7) instead of setting the DTACK (LIN0CTRL.4) bit. At that time, steps 2 through 5 can then be skipped. In this situation, the LIN controller stops the processing of LIN communication until the next SYNC BREAK is received.

- 4. Changing the configuration of the checksum during a transaction will cause the interface to reset and the transaction to be lost. To prevent this, the checksum should not be configured while a transaction is in progress. The same applies to changes in the LIN interface mode from slave mode to master mode and from master mode to slave mode.

## 20.5. Sleep Mode and Wake-Up

To reduce the system's power consumption, the LIN Protocol Specification defines a Sleep Mode. The message used to broadcast a Sleep Mode request must be transmitted by the LIN master application in the same way as a normal transmit message. The LIN slave application must decode the Sleep Mode Frame from the Identifier and data bytes. After that, it has to put the LIN slave node into the Sleep Mode by setting the SLEEP bit (LIN0CTRL.6).

If the SLEEP bit (LINOCTRL.6) of the LIN slave application is not set and there is no bus activity for four seconds (specified bus idle timeout), the IDLTOUT bit (LINOST.6) is set and an interrupt request is generated. After that the application may assume that the LIN bus is in Sleep Mode and set the SLEEP bit (LINOCTRL.6).

Sending a wake-up signal from the master or any slave node terminates the Sleep Mode of the LIN bus. To send a wake-up signal, the application has to set the WUPREQ bit (LIN0CTRL.1). After successful transmission of the wake-up signal, the DONE bit (LIN0ST.0) of the master node is set and an interrupt request is generated. The LIN slave does not generate an interrupt request after successful transmission of the wake-up signal but it generates an interrupt request if the master does not respond to the wake-up signal within 150 milliseconds. In that case, the ERROR bit (LIN0ST.2) and TOUT bit (LIN0ERR.2) are set. The application then has to decide whether or not to transmit another wake-up signal.

All LIN nodes that detect a wake-up signal will set the WAKEUP (LIN0ST.1) and DONE bits (LIN0ST.0) and generate an interrupt request. After that, the application has to clear the SLEEP bit (LIN0CTRL.6) in the LIN slave.

## 20.6. Error Detection and Handling

The LIN controller generates an interrupt request and stops the processing of the current frame if it detects an error. The application has to check the type of error by processing LIN0ERR. After that, it has to reset the error register and the ERROR bit (LIN0ST.2) by writing a 1 to the RSTERR bit (LIN0CTRL.2). Starting a new message with the LIN controller selected as master or sending a Wakeup signal with the LIN controller selected as a master or slave is possible only if the ERROR bit (LIN0ST.2) is set to 0.

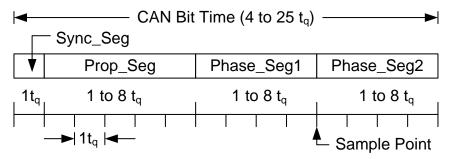

Figure 21.3. Four segments of a CAN Bit

The length of the 4 bit segments must be adjusted so that their sum is as close as possible to the desired bit time. Since each segment must be an integer multiple of the time quantum (tq), the closest achievable bit time is 24 tq (1000.008 ns), yielding a bit rate of 0.999992 Mbit/sec. The Sync\_Seg is a constant 1 tq. The Prop\_Seg must be greater than or equal to the propagation delay of 400 ns and so the choice is 10 tq (416.67 ns).

The remaining time quanta (13 tq) in the bit time are divided between Phase\_Seg1 and Phase\_Seg2 as shown in. Based on this equation, Phase\_Seg1 = 6 tq and Phase\_Seg2 = 7 tq.

Phase\_Seg1 + Phase\_Seg2 = Bit\_Time - (Synch\_Seg + Prop\_Seg)

- 1. If Phase\_Seg1 + Phase\_Seg2 is even, then Phase\_Seg2 = Phase\_Seg1. If the sum is odd, Phase\_Seg2 = Phase\_Seg1 + 1.

- 2. Phase\_Seg2 should be at least 2 tq.

### **Equation 21.1. Assigning the Phase Segments**

The Synchronization Jump Width (SJW) timing parameter is defined by. It is used for determining the value written to the Bit Timing Register and for determining the required oscillator tolerance. Since we are using a quartz crystal as the system clock source, an oscillator tolerance calculation is not needed.

#### SJW = minimum (4, Phase\_Seg1)

#### Equation 21.2. Synchronization Jump Width (SJW)

The value written to the Bit Timing Register can be calculated using Equation 18.3. The BRP Extension register is left at its reset value of 0x0000.

BRPE = BRP - 1 = BRP Extension Register = 0x0000SJWp = SJW - 1 = minimum (4, 6) - 1 = 3

TSEG1 = Prop\_Seg + Phase\_Seg1 - 1 = 10 + 6 - 1 = 15

$$TSEG2 = Phase_Seg2 - 1 = 6$$

Bit Timing Register = (TSEG2 x 0x1000) + (TSEG1 x 0x0100)

Bit Timing Register = (TSEG2 x 0x1000) + (TSEG1 x 0x0100) + (SJWp x 0x0040) + BRPE = 0x6FC0

### Equation 21.3. Calculating the Bit Timing Register Value

# SFR Definition 21.1. CAN0CFG: CAN Clock Configuration

| Bit   | 7      | 6      | 5      | 4      | 3      | 2      | 1    | 0       |

|-------|--------|--------|--------|--------|--------|--------|------|---------|

| Name  | Unused | Unused | Unused | Unused | Unused | Unused | SYSD | IV[1:0] |

| Туре  | R      | R      | R      | R      | R      | R      | R/W  |         |

| Reset | 0      | 0      | 0      | 0      | 0      | 0      | 0    | 0       |

#### SFR Address = 0x92; SFR Page = 0x0C

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                      |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused      | Read = 000000b; Write = Don't Care.                                                                                                                                                                                                                                                                                           |

| 1:0 | SYSDIV[1:0] | CAN System Clock Divider Bits.                                                                                                                                                                                                                                                                                                |

|     |             | The CAN controller clock is derived from the CIP-51 system clock. The CAN control-<br>ler clock must be less than or equal to 25 MHz.<br>00: CAN controller clock = System Clock/1.<br>01: CAN controller clock = System Clock/2.<br>10: CAN controller clock = System Clock/4.<br>11: CAN controller clock = System Clock/8. |

#### 22.4.3. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

## SFR Definition 22.3. SMB0DAT: SMBus Data

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | SMB0DAT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xC2; SMB0DAT = 0x00

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SMB0DAT[7:0] | SMBus Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |              | The SMB0DAT register contains a byte of data to be transmitted on the SMBus serial interface or a byte that has just been received on the SMBus serial interface. The CPU can read from or write to this register whenever the SI serial interrupt flag (SMB0CN.0) is set to logic 1. The serial data in the register remains stable as long as the SI flag is set. When the SI flag is not set, the system may be in the process of shifting data in/out and the CPU should not attempt to access this register. |

## 22.5. SMBus Transfer Modes

The SMBus interface may be configured to operate as master and/or slave. At any particular time, it will be operating in one of the following four modes: Master Transmitter, Master Receiver, Slave Transmitter, or Slave Receiver. The SMBus interface enters Master Mode any time a START is generated, and remains in Master Mode until it loses an arbitration or generates a STOP. An SMBus interrupt is generated at the end of all SMBus byte frames. As a receiver, the interrupt for an ACK occurs **before** the ACK. As a transmitter, interrupts occur **after** the ACK.

# C8051F55x/56x/57x

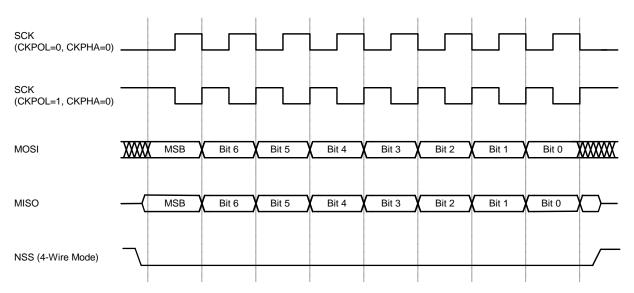

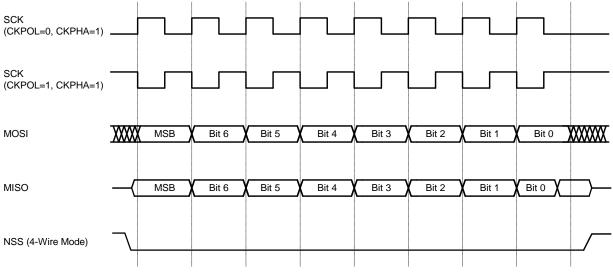

## 24.6. SPI Special Function Registers

SPI0 is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI0 Bus are described in the following figures.

# SFR Definition 24.2. SPI0CN: SPI0 Control

| Bit                                                            | 7             | 6                                                                                                                                                                                                                                                                                                                                                                                            | 5                                | 4      | 3    | 2      | 1     | 0     |  |  |  |

|----------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------|------|--------|-------|-------|--|--|--|

| Name                                                           | s SPIF        | WCOL                                                                                                                                                                                                                                                                                                                                                                                         | MODF                             | RXOVRN | NSSM | D[1:0] | TXBMT | SPIEN |  |  |  |

| Type         R/W         R/W         R/W         R/W         R |               |                                                                                                                                                                                                                                                                                                                                                                                              | R                                | R/W    |      |        |       |       |  |  |  |

| Rese                                                           | t 0           | 0                                                                                                                                                                                                                                                                                                                                                                                            | 0                                | 0      | 0    | 1      | 1     | 0     |  |  |  |

| SFR A                                                          | ddress = 0xF8 | ; Bit-Addres                                                                                                                                                                                                                                                                                                                                                                                 | Bit-Addressable; SFR Page = 0x00 |        |      |        |       |       |  |  |  |

| Bit                                                            | Name Function |                                                                                                                                                                                                                                                                                                                                                                                              |                                  |        |      |        |       |       |  |  |  |

| 7 SPIF                                                         |               | <b>SPI0 Interrupt Flag.</b><br>This bit is set to logic 1 by hardware at the end of a data transfer. If interrupts are enabled, setting this bit causes the CPU to vector to the SPI0 interrupt service routine. This bit is not automatically cleared by hardware. It must be cleared by soft-                                                                                              |                                  |        |      |        |       |       |  |  |  |

| 6                                                              | WCOL          | <ul> <li>ware.</li> <li>Write Collision Flag.</li> <li>This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) to indicate write to the SPI0 data register was attempted while a data transfer was in progres It must be cleared by software.</li> </ul>                                                                                                                     |                                  |        |      |        |       |       |  |  |  |

| 5                                                              | MODF          | <b>Mode Fault Flag.</b><br>This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) when a master mode collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01).<br>This bit is not automatically cleared by hardware. It must be cleared by software.                                                                                                              |                                  |        |      |        |       |       |  |  |  |

| 4                                                              | RXOVRN        | Receive Overrun Flag (valid in slave mode only).                                                                                                                                                                                                                                                                                                                                             |                                  |        |      |        |       |       |  |  |  |

|                                                                |               | This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) when the receive buffer still holds unread data from a previous transfer and the last bit of the current transfer is shifted into the SPI0 shift register. This bit is not automatically cleared by hardware. It must be cleared by software.                                                                        |                                  |        |      |        |       |       |  |  |  |

| 3:2                                                            | NSSMD[1:0]    | Slave Select Mode.                                                                                                                                                                                                                                                                                                                                                                           |                                  |        |      |        |       |       |  |  |  |

|                                                                |               | Selects between the following NSS operation modes:<br>(See Section 24.2 and Section 24.3).<br>00: 3-Wire Slave or 3-Wire Master Mode. NSS signal is not routed to a port pin.<br>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is an input to the device.<br>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the<br>device and will assume the value of NSSMD0. |                                  |        |      |        |       |       |  |  |  |

| 1                                                              | TXBMT         | Transmit Buffer Empty.                                                                                                                                                                                                                                                                                                                                                                       |                                  |        |      |        |       |       |  |  |  |

|                                                                |               | This bit will be set to logic 0 when new data has been written to the transmit buffer.<br>When data in the transmit buffer is transferred to the SPI shift register, this bit will<br>be set to logic 1, indicating that it is safe to write a new byte to the transmit buffer.                                                                                                              |                                  |        |      |        |       |       |  |  |  |

| 0                                                              | SPIEN         | SPI0 Enable.<br>0: SPI disabled.<br>1: SPI enabled.                                                                                                                                                                                                                                                                                                                                          |                                  |        |      |        |       |       |  |  |  |

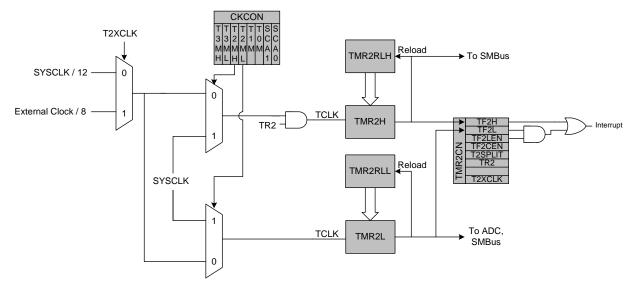

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK/12          |

| 0    | 1      | External Clock/8   |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK/12          |

| 0    | 1      | External Clock/8   |

| 1    | Х      | SYSCLK             |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 25.5. Timer 2 8-Bit Mode Block Diagram

### 25.2.3. External Oscillator Capture Mode

Capture Mode allows the external oscillator to be measured against the system clock. Timer 2 can be clocked from the system clock, or the system clock divided by 12, depending on the T2ML (CKCON.4), and T2XCLK bits. When a capture event is generated, the contents of Timer 2 (TMR2H:TMR2L) are loaded into the Timer 2 reload registers (TMR2RLH:TMR2RLL) and the TF2H flag is set. A capture event is generated by the falling edge of the clock source being measured, which is the external oscillator / 8. By recording the difference between two successive timer capture values, the external oscillator frequency can be determined with respect to the Timer 2 clock. The Timer 2 clock should be much faster than the capture clock to achieve an accurate reading. Timer 2 should be in 16-bit auto-reload mode when using Capture Mode.

For example, if T2ML = 1b and TF2CEN = 1b, Timer 2 will clock every SYSCLK and capture every external clock divided by 8. If the SYSCLK is 24 MHz and the difference between two successive captures is 5984, then the external clock frequency is as follows:

24 MHz/(5984/8) = 0.032086 MHz or 32.086 kHz

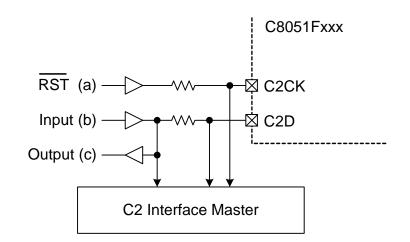

## 27.2. C2 Pin Sharing

The C2 protocol allows the C2 pins to be shared with user functions so that in-system debugging and Flash programming may be performed. This is possible because C2 communication is typically performed when the device is in the halt state, where all on-chip peripherals and user software are stalled. In this halted state, the C2 interface can safely 'borrow' the C2CK (RST) and C2D pins. In most applications, external resistors are required to isolate C2 interface traffic from the user application. A typical isolation configuration is shown in Figure 27.1.

Figure 27.1. Typical C2 Pin Sharing

The configuration in Figure 27.1 assumes the following:

- 1. The user input (b) cannot change state while the target device is halted.

- 2. The  $\overline{\text{RST}}$  pin on the target device is used as an input only.

Additional resistors may be necessary depending on the specific application.

303