Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Active                                                         |

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 25x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f567-im |

## 2. Ordering Information

The following features are common to all devices in this family:

- 50 MHz system clock and 50 MIPS throughput (peak)

- 2304 bytes of RAM (256 internal bytes and 2048 XRAM bytes)

- SMBus/I<sup>2</sup>C, Enhanced SPI, Enhanced UART

- Four Timers

- Six Programmable Counter Array channels

- Internal 24 MHz oscillator

- Internal Voltage Regulator

- 12-bit, 200 ksps ADC

- Internal Voltage Reference and Temperature Sensor

- Two Analog Comparators

Table 2.1 shows the feature that differentiate the devices in this family.

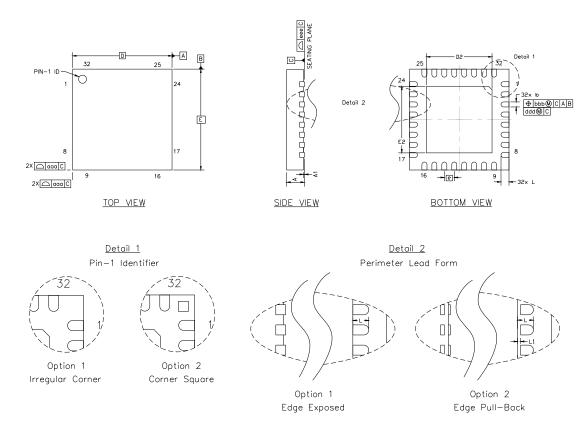

#### 4.3. QFN-32 Package Specifications

Figure 4.5. QFN-32 Package Drawing

**Table 4.5. QFN-32 Package Dimensions**

| Dimension | Min            | Тур       | Max  |  |  |  |

|-----------|----------------|-----------|------|--|--|--|

| А         | 0.80           | 0.9       | 1.00 |  |  |  |

| A1        | 0.00           | 0.02      | 0.05 |  |  |  |

| b         | 0.18           | 0.25      | 0.30 |  |  |  |

| D         |                | 5.00 BSC. |      |  |  |  |

| D2        | 3.20 3.30 3.40 |           |      |  |  |  |

| е         | 0.50 BSC.      |           |      |  |  |  |

| E         |                | 5.00 BSC. |      |  |  |  |

| Dimension | Min  | Тур  | Max  |

|-----------|------|------|------|

| E2        | 3.20 | 3.30 | 3.40 |

| L         | 0.30 | 0.40 | 0.50 |

| L1        | 0.00 | _    | 0.15 |

| aaa       | _    | _    | 0.15 |

| bbb       | _    | _    | 0.15 |

| ddd       | _    | _    | 0.05 |

| eee       | _    | _    | 0.08 |

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation VHHD except for custom features D2, E2, and L which are toleranced per supplier designation.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### 6.3.2. Setting the Gain Value

The three programmable gain registers are accessed indirectly using the ADC0H and ADC0L registers when the GAINEN bit (ADC0CF.0) bit is set. ADC0H acts as the address register, and ADC0L is the data register. The programmable gain registers can only be written to and cannot be read. See Gain Register Definition 6.1, Gain Register Definition 6.2, and Gain Register Definition 6.3 for more information.

The gain is programmed using the following steps:

- 1. Set the GAINEN bit (ADC0CF.0)

- 2. Load the ADC0H with the ADC0GNH, ADC0GNL, or ADC0GNA address.

- 3. Load ADC0L with the desired value for the selected gain register.

- 4. Reset the GAINEN bit (ADC0CF.0)

#### Notes:

- 1. An ADC conversion should not be performed while the GAINEN bit is set.

- 2. Even with gain enabled, the maximum input voltage must be less than V<sub>REGIN</sub> and the maximum voltage of the signal after gain must be less than or equal to V<sub>REF</sub>.

In code, changing the value to 0.44 gain from the previous example looks like:

```

// in 'C':

ADC0CF = 0x01:

// GAINEN = 1

ADC0H = 0x04:

// Load the ADC0GNH address

ADC0L = 0x6C:

// Load the upper byte of 0x6CA to ADC0GNH

ADC0H = 0x07:

// Load the ADC0GNL address

// Load the lower nibble of 0x6CA to ADC0GNL

ADC0L = 0xA0;

ADC0H = 0x08:

// Load the ADC0GNA address

ADC0L = 0x01:

// Set the GAINADD bit

ADC0CF \&= ~0x01;

// GAINEN = 0

; in assembly

ORL ADC0CF,#01H

: GAINEN = 1

: Load the ADC0GNH address

MOV ADC0H,#04H

MOV ADC0L.#06CH

: Load the upper byte of 0x6CA to ADC0GNH

: Load the ADC0GNL address

MOV ADC0H,#07H

MOV ADC0L,#0A0H

: Load the lower nibble of 0x6CA to ADC0GNL

MOV ADC0H,#08H

: Load the ADC0GNA address

MOV ADC0L,#01H

: Set the GAINADD bit

ANL ADCOCF,#0FEH

: GAINEN = 0

```

Note that false rising edges and falling edges can be detected when the comparator is first powered on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed.

### SFR Definition 8.1. CPT0CN: Comparator0 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0HYP[1:0] |   | CP0HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/          | W |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

SFR Address = 0x9A; SFR Page = 0x00

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0                                                      |

|     |             | 1: Voltage on CP0+ > CP0                                                      |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3:2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

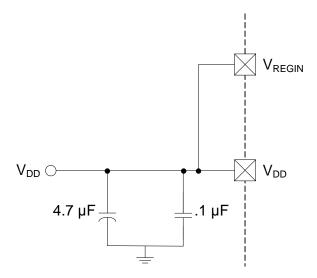

If the internal voltage regulator is not used, the VREGIN input should be tied to VDD, as shown in Figure 9.2.

Figure 9.2. External Capacitors for Voltage Regulator Input/Output—Regulator Disabled

### SFR Definition 9.1. REG0CN: Regulator Control

| Bit   | 7      | 6        | 5 | 4      | 3 | 2 | 1 | 0       |

|-------|--------|----------|---|--------|---|---|---|---------|

| Name  | REGDIS | Reserved |   | REG0MD |   |   |   | DROPOUT |

| Туре  | R/W    | R/W      | R | R/W    | R | R | R | R       |

| Reset | 0      | 1        | 0 | 1      | 0 | 0 | 0 | 0       |

SFR Address = 0xC9; SFR Page = 0x00

| Bit | Name     | Function                                    |

|-----|----------|---------------------------------------------|

| 7   | REGDIS   | Voltage Regulator Disable Bit.              |

|     |          | 0: Voltage Regulator Enabled                |

|     |          | 1: Voltage Regulator Disabled               |

| 6   | Reserved | Read = 1b; Must Write 1b.                   |

| 5   | Unused   | Read = 0b; Write = Don't Care.              |

| 4   | REG0MD   | Voltage Regulator Mode Select Bit.          |

|     |          | 0: Voltage Regulator Output is 2.1 V.       |

|     |          | 1: Voltage Regulator Output is 2.6 V.       |

| 3:1 | Unused   | Read = 000b. Write = Don't Care.            |

| 0   | DROPOUT  | Voltage Regulator Dropout Indicator.        |

|     |          | 0: Voltage Regulator is not in dropout.     |

|     |          | 1: Voltage Regulator is in or near dropout. |

### 10.4. Serial Number Special Function Registers (SFRs)

The C8051F55x/56x/57x devices include four SFRs, SN0 through SN3, that are pre-programmed during production with a unique, 32-bit serial number. The serial number provides a unique identification number for each device and can be read from the application firmware. If the serial number is not used in the application, these four registers can be used as general purpose SFRs.

#### SFR Definition 10.7. SNn: Serial Number n

| Bit   | 7 | 6            | 5  | 4           | 3              | 2  | 1 | 0 |  |  |

|-------|---|--------------|----|-------------|----------------|----|---|---|--|--|

| Name  |   | SERNUMn[7:0] |    |             |                |    |   |   |  |  |

| Туре  |   | R/W          |    |             |                |    |   |   |  |  |

| Reset |   |              | Va | aries—Uniqu | ıe 32-bit valu | ie |   |   |  |  |

SFR Addresses: SN0 = 0xF9; SN1 = 0xFA; SN2 = 0xFB; SN3 = 0xFC; SFR Page = 0x0F;

| Bi | t Name       | Function                                                                                                                                   |

|----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 7: | SERNUMn[7:0] | Serial Number Bits.                                                                                                                        |

|    |              | The four serial number registers form a 32-bit serial number, with SN3 as the most significant byte and SN0 as the least significant byte. |

### 12. Special Function Registers

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the C8051F55x/56x/57x's resources and peripherals. The CIP-51 controller core duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the sub-systems unique to the C8051F55x/56x/57x. This allows the addition of new functionality while retaining compatibility with the MCS-51™ instruction set. Table 12.3 lists the SFRs implemented in the C8051F55x/56x/57x device family.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g., P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing unoccupied addresses in the SFR space will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the data sheet, as indicated in Table 12.3, for a detailed description of each register.

#### 12.1. SFR Paging

The CIP-51 features SFR paging, allowing the device to map many SFRs into the 0x80 to 0xFF memory address space. The SFR memory space has 256 *pages*. In this way, each memory location from 0x80 to 0xFF can access up to 256 SFRs. The C8051F55x/56x/57x family of devices utilizes three SFR pages: 0x00, 0x0C, and 0x0F. SFR pages are selected using the Special Function Register Page Selection register, SFRPAGE (see SFR Definition 11.3). The procedure for reading and writing an SFR is as follows:

- 1. Select the appropriate SFR page number using the SFRPAGE register.

- 2. Use direct accessing mode to read or write the special function register (MOV instruction).

#### 12.2. Interrupts and SFR Paging

When an interrupt occurs, the SFR Page Register will automatically switch to the SFR page containing the flag bit that caused the interrupt. The automatic SFR Page switch function conveniently removes the burden of switching SFR pages from the interrupt service routine. Upon execution of the RETI instruction, the SFR page is automatically restored to the SFR Page in use prior to the interrupt. This is accomplished via a three-byte SFR Page Stack. The top byte of the stack is SFRPAGE, the current SFR Page. The second byte of the SFR Page Stack is SFRNEXT. The third, or bottom byte of the SFR Page Stack is SFRLAST. Upon an interrupt, the current SFRPAGE value is pushed to the SFRNEXT byte, and the value of SFRNEXT is pushed to SFRLAST. Hardware then loads SFRPAGE with the SFR Page containing the flag bit associated with the interrupt. On a return from interrupt, the SFR Page Stack is popped resulting in the value of SFRNEXT returning to the SFRPAGE register, thereby restoring the SFR page context without software intervention. The value in SFRLAST (0x00 if there is no SFR Page value in the bottom of the stack) of the stack is placed in SFRNEXT register. If desired, the values stored in SFRNEXT and SFR-LAST may be modified during an interrupt, enabling the CPU to return to a different SFR Page upon execution of the RETI instruction (on interrupt exit). Modifying registers in the SFR Page Stack does not cause a push or pop of the stack. Only interrupt calls and returns will cause push/pop operations on the SFR Page Stack.

On the C8051F55x/56x/57x devices, vectoring to an interrupt will switch SFRPAGE to page 0x00, except for the CAN0 interrupt which will switch SFRPAGE to page 0x0C.

Table 12.2. Special Function Register (SFR) Memory Map for Page 0x0C

|    | 0(8)                 | 1(9)                | 2(A)               | 3(B)               | 4(C)               | 5(D)                   | 6(E)                   | 7(F)                   |

|----|----------------------|---------------------|--------------------|--------------------|--------------------|------------------------|------------------------|------------------------|

| F8 |                      |                     | CAN0IF2DA2L        | CAN0IF2DA2H        | CAN0IF2DB1L        | CAN0IF2DB1H            | CAN0IF2DB2L            | CAN0IF2DB2H            |

| F0 | B<br>(All Pages)     |                     | CAN0IF2A2L         | CAN0IF2A2H         |                    |                        | CAN0IF2DA1L            | CAN0IF2DA1H            |

| E8 |                      |                     | CAN0IF2M1L         | CAN0IF2M1H         | CAN0IF2M2L         | CAN0IF2M2H             | CAN0IF2A1L             | CAN0IF2A1H             |

| E0 | ACC<br>(All Pages)   |                     | CAN0IF2CML         | CAN0IF2CMH         |                    |                        | EIE1<br>(All Pages)    | EIE2<br>(All Pages)    |

| D8 |                      |                     | CAN0IF1DB1L        | CAN0IF1DB1H        | CAN0IF1DB2L        | CAN0IF1DB2H            | CAN0IF2CRL             | CAN0IF2CRH             |

| D0 | PSW<br>(All Pages)   |                     | CAN0IF1MCL         | CAN0IF1MCH         | CAN0IF1DA1L        | CAN0IF1DA1H            | CAN0IF1DA2L            | CAN0IF1DA2H            |

| C8 |                      |                     | CAN0IF1A1L         | CAN0IF1A1H         | CAN0IF1A2L         | CAN0IF1A2H             | CAN0IF2MCL             | CAN0IF2MCH             |

| C0 | CAN0CN               |                     | CAN0IF1CML         | CAN0IF1CMH         | CAN0IF1M1L         | CAN0IF1M1H             | CAN0IF1M2L             | CAN0IF1M2H             |

| B8 | IP<br>(All Pages)    |                     | CAN0MV1L           | CAN0MV1H           | CAN0MV2L           | CAN0MV2H               | CAN0IF1CRL             | CAN0IF1CRH             |

| В0 | P3<br>(All Pages)    |                     | CAN0IP2L           | CAN0IP2H           |                    | P4<br>(All Pages)      | FLSCL<br>(All Pages)   | FLKEY<br>(All Pages)   |

| A8 | IE<br>(All Pages)    |                     | CAN0ND1L           | CAN0ND1H           | CAN0ND2L           | CAN0ND2H               | CAN0IP1L               | CAN0IP1H               |

| A0 | P2<br>(All Pages)    | CAN0BRPE            | CAN0TR1L           | CAN0TR1H           | CAN0TR2L           | CAN0TR2H               |                        | SFRPAGE<br>(All Pages) |

| 98 | SCON0<br>(All Pages) |                     | CAN0BTL            | CAN0BTH            | CANOIIDL           | CAN0IIDH               | CAN0TST                |                        |

| 90 | P1<br>(All Pages)    |                     | CAN0CFG            |                    | CAN0STAT           |                        | CAN0ERRL               | CAN0ERRH               |

| 88 | TCON                 | TMOD<br>(All Pages) | TL0<br>(All Pages) | TL1<br>(All Pages) | TH0<br>(All Pages) | TH1<br>(All Pages)     | CKCON<br>(All Pages)   |                        |

| 80 | P0<br>(All Pages)    | SP<br>(All Pages)   | DPL<br>(All Pages) | DPH<br>(All Pages) | , ,                | SFRNEXT<br>(All Pages) | SFRLAST<br>(All Pages) | PCON<br>(All Pages)    |

|    | 0(8)                 | 1(9)                | 2(A)               | 3(B)               | 4(C)               | 5(D)                   | 6(E)                   | 7(F)                   |

0(8) 1(9) (bit addressable)

### **Table 12.3. Special Function Registers (Continued)**

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Description                          | Page |

|----------|---------|--------------------------------------|------|

| IT01CF   | 0xE4    | INT0/INT1 Configuration              | 123  |

| LIN0ADR  | 0xD3    | LIN0 Address                         | 200  |

| LIN0CF   | 0xC9    | LIN0 Configuration                   | 200  |

| LIN0DAT  | 0xD2    | LIN0 Data                            | 201  |

| OSCICN   | 0xA1    | Internal Oscillator Control          | 160  |

| OSCICRS  | 0xA2    | Internal Oscillator Coarse Control   | 161  |

| OSCIFIN  | 0x9E    | Internal Oscillator Fine Calibration | 161  |

| OSCXCN   | 0x9F    | External Oscillator Control          | 165  |

| P0       | 0x80    | Port 0 Latch                         | 183  |

| P0MASK   | 0xF2    | Port 0 Mask Configuration            | 179  |

| P0MAT    | 0xF1    | Port 0 Match Configuration           | 179  |

| P0MDIN   | 0xF1    | Port 0 Input Mode Configuration      | 184  |

| P0MDOUT  | 0xA4    | Port 0 Output Mode Configuration     | 184  |

| P0SKIP   | 0xD4    | Port 0 Skip                          | 185  |

| P1       | 0x90    | Port 1 Latch                         | 185  |

| P1MASK   | 0xF4    | Port 1 Mask Configuration            | 180  |

| P1MAT    | 0xF3    | Port 1 Match Configuration           | 180  |

| P1MDIN   | 0xF2    | Port 1 Input Mode Configuration      | 186  |

| P1MDOUT  | 0xA5    | Port 1 Output Mode Configuration     | 186  |

| P1SKIP   | 0xD5    | Port 1 Skip                          | 187  |

| P2       | 0xA0    | Port 2 Latch                         | 187  |

| P2MASK   | 0xB2    | Port 2 Mask Configuration            | 181  |

| P2MAT    | 0xB1    | Port 2 Match Configuration           | 181  |

| P2MDIN   | 0xF3    | Port 2 Input Mode Configuration      | 188  |

| P2MDOUT  | 0xA6    | Port 2 Output Mode Configuration     | 188  |

| P2SKIP   | 0xD6    | Port 2 Skip                          | 189  |

| P3       | 0xB0    | Port 3 Latch                         | 189  |

| P3MASK   | 0xAF    | Port 3 Mask Configuration            | 182  |

| P3MAT    | 0xAE    | Port 3 Match Configuration           | 182  |

| P3MDIN   | 0xF4    | Port 3 Input Mode Configuration      | 190  |

| P3MDOUT  | 0xAE    | Port 3 Output Mode Configuration     | 190  |

| P3SKIP   | 0xD7    | Port 3 Skip                          | 191  |

| P4       | 0xB5    | Port 4 Latch                         | 191  |

| P4MDOUT  | 0xAF    | Port 4 Output Mode Configuration     | 192  |

| PCA0CN   | 0xD8    | PCA Control                          | 294  |

| PCA0CPH0 | 0xFC    | PCA Capture 0 High                   | 299  |

## SFR Definition 13.7. IT01CF: INT0/INT1 Configuration

| Bit   | 7     | 6          | 5   | 4 | 3     | 2          | 1 | 0 |

|-------|-------|------------|-----|---|-------|------------|---|---|

| Name  | IN1PL | IN1SL[2:0] |     |   | IN0PL | IN0SL[2:0] |   |   |

| Туре  | R/W   |            | R/W |   |       | R/W        |   |   |

| Reset | 0     | 0          | 0   | 0 | 0     | 0          | 0 | 0 |

SFR Address = 0xE4; SFR Page = 0x0F

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IN1PL      | INT1 Polarity. 0: INT1 input is active low. 1: INT1 input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6:4 | IN1SL[2:0] | INT1 Port Pin Selection Bits.  These bits select which Port pin is assigned to INT1. Note that this pin assignment is independent of the Crossbar; INT1 will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin. 000: Select P1.0 001: Select P1.1 010: Select P1.2 011: Select P1.3 100: Select P1.4 101: Select P1.5 110: Select P1.5 110: Select P1.6 111: Select P1.7 |

| 3   | IN0PL      | INTO Polarity. 0: INTO input is active low. 1: INTO input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2:0 | IN0SL[2:0] | INTO Port Pin Selection Bits.  These bits select which Port pin is assigned to INTO. Note that this pin assignment is independent of the Crossbar; INTO will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin. 000: Select P1.0  001: Select P1.1  010: Select P1.2  011: Select P1.3  100: Select P1.4  101: Select P1.5  110: Select P1.6  111: Select P1.7           |

### SFR Definition 16.2. RSTSRC: Reset Source

| Bit   | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| Name  |   | FERROR | C0RSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | 0 | Varies |

SFR Address = 0xEF; SFR Page = 0x00

| Bit   | Name       | Description                                                                                  | Write                                                                                                                                                                           | Read                                                                                                                                           |

|-------|------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Unused     | Unused.                                                                                      | Don't care.                                                                                                                                                                     | 0                                                                                                                                              |

| 6     | FERROR     | Flash Error Reset Flag.                                                                      | N/A                                                                                                                                                                             | Set to 1 if Flash read/write/erase error caused the last reset.                                                                                |

| 5     | C0RSEF     | Comparator0 Reset Enable and Flag.                                                           | Writing a 1 enables Comparator0 as a reset source (active-low).                                                                                                                 | Set to 1 if Comparator0 caused the last reset.                                                                                                 |

| 4     | SWRSF      | Software Reset Force and Flag.                                                               | Writing a 1 forces a system reset.                                                                                                                                              | Set to 1 if last reset was caused by a write to SWRSF.                                                                                         |

| 3     | WDTRSF     | Watchdog Timer Reset Flag.                                                                   | N/A                                                                                                                                                                             | Set to 1 if Watchdog Timer overflow caused the last reset.                                                                                     |

| 2     | MCDRSF     | Missing Clock Detector<br>Enable and Flag.                                                   | Writing a 1 enables the Missing Clock Detector. The MCD triggers a reset if a missing clock condition is detected.                                                              | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                        |

| 1     | PORSF      | Power-On/V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the V <sub>DD</sub> monitor as a reset source. Writing 1 to this bit before the V <sub>DD</sub> monitor is enabled and stabilized may cause a system reset. | Set to 1 anytime a power-<br>on or V <sub>DD</sub> monitor reset<br>occurs.<br>When set to 1 all other<br>RSTSRC flags are inde-<br>terminate. |

| 0     | PINRSF     | HW Pin Reset Flag.                                                                           | N/A                                                                                                                                                                             | Set to 1 if RST pin caused the last reset.                                                                                                     |

| Note: | Do not use | read-modify-write operations on this                                                         | s register                                                                                                                                                                      |                                                                                                                                                |

## **SFR Definition 17.1. EMIOCN: External Memory Interface Control**

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|------------|---|---|---|---|---|---|--|--|--|

| Name  |   | PGSEL[7:0] |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W        |   |   |   |   |   |   |  |  |  |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

SFR Address = 0xAA; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                                                   |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | PGSEL[7:0] | XRAM Page Select Bits.                                                                                                                                                     |

|     |            | The XRAM Page Select Bits provide the high byte of the 16-bit external data memory address when using an 8-bit MOVX command, effectively selecting a 256-byte page of RAM. |

|     |            | 0x00: 0x0000 to 0x00FF                                                                                                                                                     |

|     |            | 0x01: 0x0100 to 0x01FF                                                                                                                                                     |

|     |            | 0xFE: 0xFE00 to 0xFEFF 0xFF: 0xFF00 to 0xFFFF                                                                                                                              |

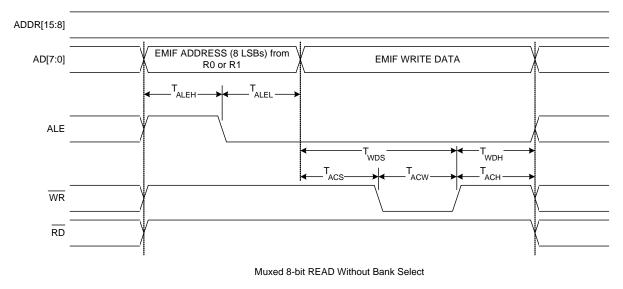

#### 17.6.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011

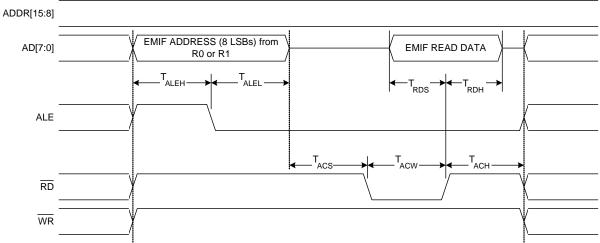

Muxed 8-bit WRITE Without Bank Select

Figure 17.4. Multiplexed 8-bit MOVX without Bank Select Timing

### SFR Definition 19.8. P2MASK: Port 2 Mask Register

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|-------------|---|---|---|---|---|---|--|--|--|

| Name  |   | P2MASK[7:0] |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W         |   |   |   |   |   |   |  |  |  |

| Reset | 0 | 0           | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

SFR Address = 0xB2; SFR Page = 0x00

| Bit   | Name                                                         | Function                                                                                                                                                                                        |  |  |  |  |  |  |

|-------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:0   | P2MASK[7:0]                                                  | Port 2 Mask Value.                                                                                                                                                                              |  |  |  |  |  |  |

|       |                                                              | Selects P2 pins to be compared to the corresponding bits in P2MAT.  0: P2.n pin logic value is ignored and cannot cause a Port Mismatch event.  1: P2.n pin logic value is compared to P2MAT.n. |  |  |  |  |  |  |

| Note: | Note: P2.2–P2.7 are available on 40-pin and 32-pin packages. |                                                                                                                                                                                                 |  |  |  |  |  |  |

### SFR Definition 19.9. P2MAT: Port 2 Match Register

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|------------|---|---|---|---|---|---|--|--|--|

| Name  |   | P2MAT[7:0] |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W        |   |   |   |   |   |   |  |  |  |

| Reset | 1 | 1          | 1 | 1 | 1 | 1 | 1 | 1 |  |  |  |

SFR Address = 0xB1; SFR Page = 0x00

| Bit   | Name             | Function                                                                                                                                                                               |

|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | P2MAT[7:0]       | Port 2 Match Value.                                                                                                                                                                    |

|       |                  | Match comparison value used on Port 2 for bits in P2MAT which are set to 1.  0: P2.n pin logic value is compared with logic LOW.  1: P2.n pin logic value is compared with logic HIGH. |

| Note: | P2.2-P2.7 are av | ailable on 40-pin and 32-pin packages.                                                                                                                                                 |

## SFR Definition 19.10. P3MASK: Port 3 Mask Register

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|-------------|---|---|---|---|---|---|--|--|--|

| Name  |   | P3MASK[7:0] |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W         |   |   |   |   |   |   |  |  |  |

| Reset | 0 | 0           | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

SFR Address = 0xAF; SFR Page = 0x00

| Bit   | Name              | Function                                                                                                                                                                                        |

|-------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | P3MASK[7:0]       | Port 1 Mask Value.                                                                                                                                                                              |

|       |                   | Selects P3 pins to be compared to the corresponding bits in P3MAT.  0: P3.n pin logic value is ignored and cannot cause a Port Mismatch event.  1: P3.n pin logic value is compared to P3MAT.n. |

| Note: | P3.0 is available | on 40-pin and 32-pin packages. P3.1-P3.7 are available on 40-pin packages                                                                                                                       |

### SFR Definition 19.11. P3MAT: Port 3 Match Register

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|------------|---|---|---|---|---|---|--|--|--|

| Name  |   | P3MAT[7:0] |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W        |   |   |   |   |   |   |  |  |  |

| Reset | 1 | 1          | 1 | 1 | 1 | 1 | 1 | 1 |  |  |  |

SFR Address = 0xAE; SFR Page = 0x00

| Bit   | Name                                                                                           | Function                                                                                                                                                                               |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:0   | P3MAT[7:0]                                                                                     | Port 3 Match Value.                                                                                                                                                                    |  |  |  |  |  |  |

|       |                                                                                                | Match comparison value used on Port 3 for bits in P3MAT which are set to 1.  0: P3.n pin logic value is compared with logic LOW.  1: P3.n pin logic value is compared with logic HIGH. |  |  |  |  |  |  |

| Note: | e: P3.0 is available on 40-pin and 32-pin packages. P3.1-P3.7 are available on 40-pin packages |                                                                                                                                                                                        |  |  |  |  |  |  |

Table 22.3. Sources for Hardware Changes to SMB0CN

| Bit     | Set by Hardware When:                                                                                           | Cleared by Hardware When:                                     |

|---------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| MASTER  | <ul><li>A START is generated.</li></ul>                                                                         | ■ A STOP is generated.                                        |

|         |                                                                                                                 | <ul><li>Arbitration is lost.</li></ul>                        |

| TXMODE  | ■ START is generated.                                                                                           | ■ A START is detected.                                        |

|         | <ul><li>SMB0DAT is written before the start of an</li></ul>                                                     | Arbitration is lost.                                          |

|         | SMBus frame.                                                                                                    | SMB0DAT is not written before the<br>start of an SMBus frame. |

| STA     | A START followed by an address byte is<br>received.                                                             | Must be cleared by software.                                  |

| STO     | A STOP is detected while addressed as a slave.                                                                  | A pending STOP is generated.                                  |

|         | Arbitration is lost due to a detected STOP.                                                                     |                                                               |

| ACKRQ   | <ul> <li>A byte has been received and an ACK<br/>response value is needed.</li> </ul>                           | After each ACK cycle.                                         |

| ARBLOST | <ul> <li>A repeated START is detected as a<br/>MASTER when STA is low (unwanted<br/>repeated START).</li> </ul> | ■ Each time SI is cleared.                                    |

|         | <ul> <li>SCL is sensed low while attempting to<br/>generate a STOP or repeated START<br/>condition.</li> </ul>  |                                                               |

|         | <ul> <li>SDA is sensed low while transmitting a 1<br/>(excluding ACK bits).</li> </ul>                          |                                                               |

| ACK     | The incoming ACK value is low (ACKNOWLEDGE).                                                                    | The incoming ACK value is high<br>(NOT ACKNOWLEDGE).          |

| SI      | A START has been generated.                                                                                     | Must be cleared by software.                                  |

|         | <ul><li>Lost arbitration.</li></ul>                                                                             |                                                               |

|         | <ul> <li>A byte has been transmitted and an<br/>ACK/NACK received.</li> </ul>                                   |                                                               |

|         | A byte has been received.                                                                                       |                                                               |

|         | <ul> <li>A START or repeated START followed by a<br/>slave address + R/W has been received.</li> </ul>          |                                                               |

|         | A STOP has been received.                                                                                       |                                                               |

Table 22.4. SMBus Status Decoding

|                    | Values Read      |       | Values Read |     | Ilues Read                                                    |                                                                                             | Typical Response Options | Val<br>Wr | lues<br>ite | sto                            | s<br>ected |

|--------------------|------------------|-------|-------------|-----|---------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------|-----------|-------------|--------------------------------|------------|

| Mode               | Status<br>Vector | ACKRQ | ARBLOST     | ACK |                                                               |                                                                                             | STA                      | STO       | ACK         | Next Status<br>Vector Expected |            |

|                    | 1110             | 0     | 0           | Х   | A master START was generated.                                 | Load slave address + R/W into SMB0DAT.                                                      | 0                        | 0         | Х           | 1100                           |            |

|                    | 1100             | 0     | 0           | 0   | A master data or address byte was transmitted; NACK received. | Set STA to restart transfer.  Abort transfer.                                               | 0                        | 0         | X           | 1110                           |            |

|                    |                  | 0     | 0           | 1   | A master data or address byte was transmitted; ACK            | Load next data byte into SMB0-DAT.                                                          | 0                        | 0         | Х           | 1100                           |            |

|                    |                  |       |             |     | received.                                                     | End transfer with STOP.                                                                     | 0                        | 1         | Χ           | _                              |            |

| smitter            |                  |       |             |     |                                                               | End transfer with STOP and start another transfer.                                          | 1                        | 1         | Х           | _                              |            |

| rans               |                  |       |             |     |                                                               | Send repeated START.                                                                        | 1                        | 0         | Х           | 1110                           |            |

| Master Transmitter |                  |       |             |     |                                                               | Switch to Master Receiver Mode (clear SI without writing new data to SMB0DAT).              | 0                        | 0         | Х           | 1000                           |            |

|                    | 1000             | 1     | 0           | Χ   | A master data byte was received; ACK requested.               | Acknowledge received byte;<br>Read SMB0DAT.                                                 | 0                        | 0         | 1           | 1000                           |            |

|                    |                  |       |             |     |                                                               | Send NACK to indicate last byte, and send STOP.                                             | 0                        | 1         | 0           | _                              |            |

|                    |                  |       |             |     |                                                               | Send NACK to indicate last byte, and send STOP followed by START.                           | 1                        | 1         | 0           | 1110                           |            |

|                    |                  |       |             |     |                                                               | Send ACK followed by repeated START.                                                        | 1                        | 0         | 1           | 1110                           |            |

|                    |                  |       |             |     |                                                               | Send NACK to indicate last byte, and send repeated START.                                   | 1                        | 0         | 0           | 1110                           |            |

| eceiver            |                  |       |             |     |                                                               | Send ACK and switch to Master<br>Transmitter Mode (write to<br>SMB0DAT before clearing SI). | 0                        | 0         | 1           | 1100                           |            |

| Master Receive     |                  |       |             |     |                                                               | Send NACK and switch to Master Transmitter Mode (write to SMB0DAT before clearing SI).      | 0                        | 0         | 0           | 1100                           |            |

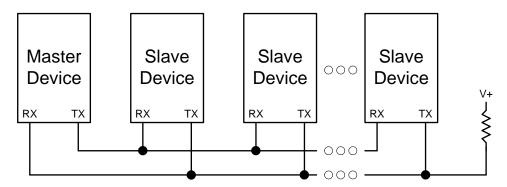

#### 23.3.3. Multiprocessor Communications

UART0 supports multiprocessor communication between a master processor and one or more slave processors by special use of the extra data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its extra bit is logic 1; in a data byte, the extra bit is always set to logic 0.

Setting the MCE0 bit (SMOD0.7) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the extra bit is logic 1 (RBX0 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned address. If the addresses match, the slave will clear its MCE0 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0 bits set and do not generate interrupts on the reception of the following data bytes, thereby ignoring the data. Once the entire message is received, the addressed slave resets its MCE0 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 23.6. UART Multi-Processor Mode Interconnect Diagram

## SFR Definition 26.4. PCA0CPMn: PCA Capture/Compare Mode

| Bit   | 7      | 6     | 5     | 4     | 3    | 2    | 1    | 0     |

|-------|--------|-------|-------|-------|------|------|------|-------|

| Name  | PWM16n | ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMn | ECCFn |

| Туре  | R/W    | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W   |

| Reset | 0      | 0     | 0     | 0     | 0    | 0    | 0    | 0     |

SFR Addresses: PCA0CPM0 = 0xDA, PCA0CPM1 = 0xDB, PCA0CPM2 = 0xDC; PCA0CPM3 = 0xDD, PCA0CPM4 = 0xDE, PCA0CPM5 = 0xDF, SFR Page (all registers) = 0x00

| Bit   | Name                                                                                                                                                                                                                | Function                                                                                                                                                                                                                                                                                                            |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7     | PWM16n                                                                                                                                                                                                              | 16-bit Pulse Width Modulation Enable.                                                                                                                                                                                                                                                                               |  |  |  |

|       |                                                                                                                                                                                                                     | This bit enables 16-bit mode when Pulse Width Modulation mode is enabled.                                                                                                                                                                                                                                           |  |  |  |

|       |                                                                                                                                                                                                                     | 0: 8 to 11-bit PWM selected.                                                                                                                                                                                                                                                                                        |  |  |  |

|       |                                                                                                                                                                                                                     | 1: 16-bit PWM selected.                                                                                                                                                                                                                                                                                             |  |  |  |

| 6     | ECOMn                                                                                                                                                                                                               | Comparator Function Enable.                                                                                                                                                                                                                                                                                         |  |  |  |

|       |                                                                                                                                                                                                                     | This bit enables the comparator function for PCA module n when set to 1.                                                                                                                                                                                                                                            |  |  |  |

| 5     | CAPPn                                                                                                                                                                                                               | Capture Positive Function Enable.                                                                                                                                                                                                                                                                                   |  |  |  |

|       |                                                                                                                                                                                                                     | This bit enables the positive edge capture for PCA module n when set to 1.                                                                                                                                                                                                                                          |  |  |  |

| 4     | CAPNn                                                                                                                                                                                                               | Capture Negative Function Enable.                                                                                                                                                                                                                                                                                   |  |  |  |

|       |                                                                                                                                                                                                                     | This bit enables the negative edge capture for PCA module n when set to 1.                                                                                                                                                                                                                                          |  |  |  |

| 3     | MATn                                                                                                                                                                                                                | Match Function Enable.                                                                                                                                                                                                                                                                                              |  |  |  |

|       |                                                                                                                                                                                                                     | This bit enables the match function for PCA module n when set to 1. When enabled, matches of the PCA counter with a module's capture/compare register cause the CCFn bit in PCA0MD register to be set to logic 1.                                                                                                   |  |  |  |

| 2     | TOGn                                                                                                                                                                                                                | Toggle Function Enable.                                                                                                                                                                                                                                                                                             |  |  |  |

|       |                                                                                                                                                                                                                     | This bit enables the toggle function for PCA module n when set to 1. When enabled, matches of the PCA counter with a module's capture/compare register cause the logic level on the CEXn pin to toggle. If the PWMn bit is also set to logic 1, the module operates in Frequency Output Mode.                       |  |  |  |

| 1     | PWMn                                                                                                                                                                                                                | Pulse Width Modulation Mode Enable.                                                                                                                                                                                                                                                                                 |  |  |  |

|       |                                                                                                                                                                                                                     | This bit enables the PWM function for PCA module n when set to 1. When enabled, a pulse width modulated signal is output on the CEXn pin. 8 to 11-bit PWM is used if PWM16n is cleared; 16-bit mode is used if PWM16n is set to logic 1. If the TOGn bit is also set, the module operates in Frequency Output Mode. |  |  |  |

| 0     | ECCFn                                                                                                                                                                                                               | Capture/Compare Flag Interrupt Enable.                                                                                                                                                                                                                                                                              |  |  |  |

|       |                                                                                                                                                                                                                     | This bit sets the masking of the Capture/Compare Flag (CCFn) interrupt.                                                                                                                                                                                                                                             |  |  |  |

|       |                                                                                                                                                                                                                     | 0: Disable CCFn interrupts.                                                                                                                                                                                                                                                                                         |  |  |  |

|       |                                                                                                                                                                                                                     | 1: Enable a Capture/Compare Flag interrupt request when CCFn is set.                                                                                                                                                                                                                                                |  |  |  |

| Note: | ote: When the WDTE bit is set to 1, the PCA0CPM5 register cannot be modified, and module 5 acts as the<br>watchdog timer. To change the contents of the PCA0CPM5 register or the function of module 5, the Watchdog |                                                                                                                                                                                                                                                                                                                     |  |  |  |

when the WDTE bit is set to 1, the PCA0CPM5 register cannot be modified, and module 5 acts as the watchdog timer. To change the contents of the PCA0CPM5 register or the function of module 5, the Watchdog Timer must be disabled.

## SFR Definition 26.5. PCA0L: PCA Counter/Timer Low Byte

| Bit   | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|-----------|-----|-----|-----|-----|-----|-----|-----|--|

| Name  | PCA0[7:0] |     |     |     |     |     |     |     |  |

| Туре  | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset | 0         | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

SFR Address = 0xF9; SFR Page = 0x00

| Bit   | Name                                                                                                              | Function                                                                     |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | PCA0[7:0]                                                                                                         | PCA Counter/Timer Low Byte.                                                  |  |  |  |  |  |

|       |                                                                                                                   | The PCA0L register holds the low byte (LSB) of the 16-bit PCA Counter/Timer. |  |  |  |  |  |

| Noto: | Ista: When the WDTE hit is set to 1, the PCAOL register cannot be modified by software. To change the contents of |                                                                              |  |  |  |  |  |

**Note:** When the WDTE bit is set to 1, the PCA0L register cannot be modified by software. To change the contents of the PCA0L register, the Watchdog Timer must first be disabled.

### SFR Definition 26.6. PCA0H: PCA Counter/Timer High Byte

| Bit   | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | PCA0[15:8] |     |     |     |     |     |     |     |

| Туре  | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0xFA; SFR Page = 0x00

| Bit   | Name                                                                                                                                                                             | Function                                                                                                                                                                                                                                      |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | PCA0[15:8]                                                                                                                                                                       | PCA Counter/Timer High Byte.                                                                                                                                                                                                                  |  |  |  |  |  |

|       |                                                                                                                                                                                  | The PCA0H register holds the high byte (MSB) of the 16-bit PCA Counter/Timer. Reads of this register will read the contents of a "snapshot" register, whose contents are updated only when the contents of PCA0L are read (see Section 26.1). |  |  |  |  |  |

| Note: | Note: When the WDTE bit is set to 1, the PCA0H register cannot be modified by software. To change the contents of the PCA0H register, the Watchdog Timer must first be disabled. |                                                                                                                                                                                                                                               |  |  |  |  |  |

SILICON LABS