## Silicon Labs - <u>C8051F570-IM Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

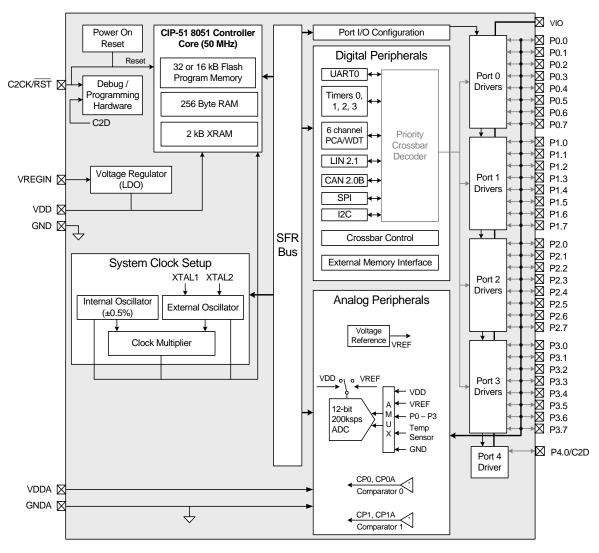

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 50MHz                                                             |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), LINbus, SPI, UART/USART |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                        |

| Number of I/O              | 33                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 2.25К х 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                      |

| Data Converters            | A/D 32x12b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 40-VFQFN Exposed Pad                                              |

| Supplier Device Package    | 40-QFN (6x6)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f570-im    |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 12.2. Interrupts and SFR Paging                                     | 95  |

|---------------------------------------------------------------------|-----|

| 12.3. SFR Page Stack Example                                        | 97  |

| 13. Interrupts                                                      | 112 |

| 13.1. MCU Interrupt Sources and Vectors                             | 112 |

| 13.1.1. Interrupt Priorities                                        | 113 |

| 13.1.2. Interrupt Latency                                           | 113 |

| 13.2. Interrupt Register Descriptions                               | 115 |

| 13.3. External Interrupts INTO and INT1                             |     |

| 14. Flash Memory                                                    |     |

| 14.1. Programming The Flash Memory                                  | 124 |

| 14.1.1. Flash Lock and Key Functions                                | 124 |

| 14.1.2. Flash Erase Procedure                                       |     |

| 14.1.3. Flash Write Procedure                                       | 125 |

| 14.1.4. Flash Write Optimization                                    | 126 |

| 14.2. Non-volatile Data Storage                                     |     |

| 14.3. Security Options                                              |     |

| 14.4. Flash Write and Erase Guidelines                              | 129 |

| 14.4.1. V <sub>DD</sub> Maintenance and the V <sub>DD</sub> monitor |     |

| 14.4.2. PSWE Maintenance                                            | 130 |

| 14.4.3. System Clock                                                |     |

| 15. Power Management Modes                                          |     |

| 15.1. Idle Mode                                                     | 135 |

| 15.2. Stop Mode                                                     | 136 |

| 15.3. Suspend Mode                                                  |     |

| 16. Reset Sources                                                   |     |

| 16.1. Power-On Reset                                                | 139 |

| 16.2. Power-Fail Reset/VDD Monitor                                  |     |

| 16.3. External Reset                                                | 141 |

| 16.4. Missing Clock Detector Reset                                  |     |

| 16.5. Comparator0 Reset                                             |     |

| 16.6. PCA Watchdog Timer Reset                                      |     |

| 16.7. Flash Error Reset                                             |     |

| 16.8. Software Reset                                                | 142 |

| 17. External Data Memory Interface and On-Chip XRAM                 |     |

| 17.1. Accessing XRAM                                                |     |

| 17.1.1. 16-Bit MOVX Example                                         |     |

| 17.1.2. 8-Bit MOVX Example                                          |     |

| 17.2. Configuring the External Memory Interface                     |     |

| 17.3. Port Configuration                                            |     |

| 17.4. Multiplexed Mode                                              |     |

| 17.5. Memory Mode Selection                                         |     |

| 17.5.1. Internal XRAM Only                                          |     |

| 17.5.2. Split Mode without Bank Select                              |     |

| 17.5.3. Split Mode with Bank Select                                 |     |

| 17.5.4. External Only                                               |     |

Figure 1.1. C8051F568-9 and 'F570-5 (40-pin) Block Diagram

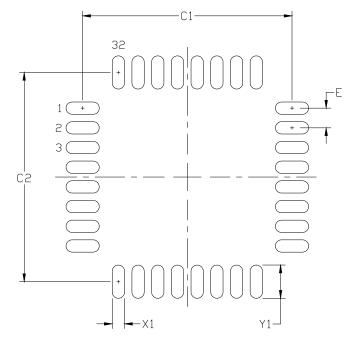

Figure 4.4. QFP-32 Landing Diagram

Table 4.4. QFP-32 Landing Diagram Dimensions

| Dimension | Min Max    |      |    | Dimension | Min  | Max  |

|-----------|------------|------|----|-----------|------|------|

| C1        | 8.40       | 8.50 |    | X1        | 0.40 | 0.50 |

| C2        | C2 8.40 8. |      | Y1 |           | 1.25 | 1.35 |

| E         | 0.80 BSC   |      |    |           |      |      |

### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design

**3.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

#### **Stencil Design**

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

#### Card Assembly

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# SFR Definition 6.9. ADC0GTH: ADC0 Greater-Than Data High Byte

| Bit   | 7             | 6            | 5                                            | 4 | 3        | 2 | 1 | 0 |  |  |  |  |  |

|-------|---------------|--------------|----------------------------------------------|---|----------|---|---|---|--|--|--|--|--|

| Nam   | e             | ADC0GTH[7:0] |                                              |   |          |   |   |   |  |  |  |  |  |

| Туре  | 9             | R/W          |                                              |   |          |   |   |   |  |  |  |  |  |

| Rese  | et 1          | 1            | 1                                            | 1 | 1        |   |   |   |  |  |  |  |  |

| SFR A | Address = 0xC | 4; SFR Page  | e = 0x00                                     |   |          |   |   |   |  |  |  |  |  |

| Bit   | Name Function |              |                                              |   | Function |   |   |   |  |  |  |  |  |

| 7:0   | ADC0GTH[7:    | 0] ADC0 G    | ADC0 Greater-Than Data Word High-Order Bits. |   |          |   |   |   |  |  |  |  |  |

# SFR Definition 6.10. ADC0GTL: ADC0 Greater-Than Data Low Byte

| Bit   | 7              | 6            | 5                                           | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

|-------|----------------|--------------|---------------------------------------------|---|---|---|---|---|--|--|--|--|--|

| Nam   | e              | ADC0GTL[7:0] |                                             |   |   |   |   |   |  |  |  |  |  |

| Туре  | 9              | R/W          |                                             |   |   |   |   |   |  |  |  |  |  |

| Rese  | et 1           | 1            | 1                                           | 1 | 1 |   |   |   |  |  |  |  |  |

| SFR A | Address = 0xC3 | 3; SFR Page  | e = 0x00                                    |   |   |   |   |   |  |  |  |  |  |

| Bit   | Name           |              | Function                                    |   |   |   |   |   |  |  |  |  |  |

| 7:0   | ADC0GTL[7:0    | )] ADC0 G    | ADC0 Greater-Than Data Word Low-Order Bits. |   |   |   |   |   |  |  |  |  |  |

# SFR Definition 8.5. CPT0MX: Comparator0 MUX Selection

| Bit   | 7            | 6           | 5                 | 4                                                  | 3            | 2            | 1          | 0 |  |  |  |  |

|-------|--------------|-------------|-------------------|----------------------------------------------------|--------------|--------------|------------|---|--|--|--|--|

| Nam   | е            | CMX0        | N[3:0]            | I                                                  |              | CMXC         | P[3:0]     |   |  |  |  |  |

| Туре  | •            | R/          | W                 |                                                    |              | R/           | W          |   |  |  |  |  |

| Rese  | et 0         | 1           | 1                 | 1                                                  | 0            | 1            | 1          | 1 |  |  |  |  |

| SFR A | ddress = 0x9 | C; SFR Page | $e = 0 \times 00$ |                                                    |              |              |            |   |  |  |  |  |

| Bit   | Name         | _           |                   |                                                    | Function     |              |            |   |  |  |  |  |

| 7:4   | CMX0N[3:0]   | Comparato   | r0 Negative       | Input MUX                                          | Selection.   |              |            |   |  |  |  |  |

|       |              | 0000:       | P0.               | 1                                                  |              |              |            |   |  |  |  |  |

|       |              | 0001:       | P0.               | 3                                                  |              |              |            |   |  |  |  |  |

|       |              | 0010:       | P0.               | 5                                                  |              |              |            |   |  |  |  |  |

|       |              | 0011:       | P0.               | 7                                                  |              |              |            |   |  |  |  |  |

|       |              | 0100:       | P1.               | 1                                                  |              |              |            |   |  |  |  |  |

|       |              | 0101:       | P1.               | 3                                                  |              |              |            |   |  |  |  |  |

|       |              | 0110:       | P1.               | 5                                                  |              |              |            |   |  |  |  |  |

|       |              | 0111:       | P1.               | P1.7                                               |              |              |            |   |  |  |  |  |

|       |              | 1000:       | P2.               | P2.1                                               |              |              |            |   |  |  |  |  |

|       |              | 1001:       | P2.               | P2.3 (only available on 40-pin and 32-pin devices) |              |              |            |   |  |  |  |  |

|       |              | 1010:       | P2.               | P2.5 (only available on 40-pin and 32-pin devices) |              |              |            |   |  |  |  |  |

|       |              | 1011:       | P2.               | P2.7 (only available on 40-pin and 32-pin devices) |              |              |            |   |  |  |  |  |

|       |              | 1100–11111: | Nor               | None                                               |              |              |            |   |  |  |  |  |

| 3:0   | CMX0P[3:0]   | Comparato   | r0 Positive       | Input MUX                                          | Selection.   |              |            |   |  |  |  |  |

|       |              | 0000:       | P0.               | 0                                                  |              |              |            |   |  |  |  |  |

|       |              | 0001:       | P0.               | 2                                                  |              |              |            |   |  |  |  |  |

|       |              | 0010:       | P0.               | 4                                                  |              |              |            |   |  |  |  |  |

|       |              | 0011:       | P0.               | 6                                                  |              |              |            |   |  |  |  |  |

|       |              | 0100:       | P1.               | 0                                                  |              |              |            |   |  |  |  |  |

|       |              | 0101:       | P1.               | 2                                                  |              |              |            |   |  |  |  |  |

|       |              | 0110:       | P1.               | 4                                                  |              |              |            |   |  |  |  |  |

|       |              | 0111:       | P1.               | 6                                                  |              |              |            |   |  |  |  |  |

|       |              | 1000:       | P2.               | 0                                                  |              |              |            |   |  |  |  |  |

|       |              | 1001:       | P2.               | 2 (only avail                                      | able on 40-p | in and 32-pi | n devices) |   |  |  |  |  |

|       |              | 1010:       | P2.               | 4 (only avail                                      | able on 40-p | in and 32-pi | n devices) |   |  |  |  |  |

|       |              | 1011:       | P2.               | 6 (only avail                                      | able on 40-p | in and 32-pi | n devices) |   |  |  |  |  |

|       |              | 1100–1111:  | Nor               | ne                                                 |              |              |            |   |  |  |  |  |

## 16.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0–), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

## 16.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "26.4. Watchdog Timer Mode" on page 291; the WDT is enabled and clocked by SYSCLK/12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

### 16.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address in or above the reserved space.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address in or above the reserved space.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address in or above the reserved space.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "14.3. Security Options" on page 127).

- A Flash read, write, or erase is attempted when the VDD Monitor is not enabled to the high threshold and set as a reset source.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

### 16.8. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the RST pin is unaffected by this reset.

## 18.2. Programmable Internal Oscillator

All C8051F55x/56x/57x devices include a programmable internal high-frequency oscillator that defaults as the system clock after a system reset. The internal oscillator period can be adjusted via the OSCICRS and OSCIFIN registers defined in SFR Definition 18.3 and SFR Definition 18.4. On C8051F55x/56x/57x devices, OSCICRS and OSCIFIN are factory calibrated to obtain a 24 MHz base frequency. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, 8, 16, 32, 64, or 128, as defined by the IFCN bits in register OSCICN. The divide value defaults to 128 following a reset.

#### 18.2.1. Internal Oscillator Suspend Mode

When software writes a logic 1 to SUSPEND (OSCICN.5), the internal oscillator is suspended. If the system clock is derived from the internal oscillator, the input clock to the peripheral or CIP-51 will be stopped until one of the following events occur:

- Port 0 Match Event.

- Port 1 Match Event.

- Port 2 Match Event.

- Port 3 Match Event.

- Comparator 0 enabled and output is logic 0.

When one of the oscillator awakening events occur, the internal oscillator, CIP-51, and affected peripherals resume normal operation, regardless of whether the event also causes an interrupt. The CPU resumes execution at the instruction following the write to SUSPEND.

Note: Before entering suspend mode, firmware must set the ZTCEN bit in REF0CN (SFR Definition 7.1).

# SFR Definition 19.27. P3SKIP: Port 3Skip

| Bit   | 7 6 5 4 3 2 1 |                 |  |    |   |  |  |  |  |  |  |  |  |

|-------|---------------|-----------------|--|----|---|--|--|--|--|--|--|--|--|

| Name  | P3SKIP[7:0]   |                 |  |    |   |  |  |  |  |  |  |  |  |

| Туре  |               |                 |  | R/ | W |  |  |  |  |  |  |  |  |

| Reset | 0             | 0 0 0 0 0 0 0 0 |  |    |   |  |  |  |  |  |  |  |  |

SFR Address = 0xD7; SFR Page = 0x0F

| Bit   | Name                                                                                              | Function                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 7:0   | P3SKIP[7:0]                                                                                       | Port 3 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|       |                                                                                                   | <ul> <li>These bits select Port 3 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P3.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P3.n pin is skipped by the Crossbar.</li> </ul> |  |  |  |  |  |  |  |  |

| Note: | Note: P3.0 is available on 40-pin and 32-pin packages. P3.1-P3.7 are available on 40-pin packages |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

## SFR Definition 19.28. P4: Port 4

| Bit   | 7       | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|---------|---------------|---|---|---|---|---|---|--|--|--|--|

| Name  | P4[7:0] |               |   |   |   |   |   |   |  |  |  |  |

| Туре  | R/W     |               |   |   |   |   |   |   |  |  |  |  |

| Reset | 1       | 1 1 1 1 1 1 1 |   |   |   |   |   |   |  |  |  |  |

SFR Address = 0xB5; SFR Page = All Pages

| Bit   | Name                                            | Description                                                                                                                                   | Write                                                                         | Read                                                                    |  |  |  |  |  |  |  |

|-------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7:0   | P4[7:0]                                         | <b>Port 4 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P4.n Port pin is logic<br>LOW.<br>1: P4.n Port pin is logic<br>HIGH. |  |  |  |  |  |  |  |

| Note: | Note: Port 4.0 is available on 40-pin packages. |                                                                                                                                               |                                                                               |                                                                         |  |  |  |  |  |  |  |

## SFR Definition 19.29. P4MDOUT: Port 4 Output Mode

| Bit   | 7              | 6                                                                                         | 5            | 4             | 3            | 2            | 1 | 0 |  |  |  |  |

|-------|----------------|-------------------------------------------------------------------------------------------|--------------|---------------|--------------|--------------|---|---|--|--|--|--|

| Nam   |                |                                                                                           |              |               |              |              |   |   |  |  |  |  |

| Туре  | Type R/W       |                                                                                           |              |               |              |              |   |   |  |  |  |  |

| Rese  | et 0           | 0                                                                                         | 0            | 0             | 0            | 0            | 0 | 0 |  |  |  |  |

| SFR A | Address = 0xAl | F; SFR Page                                                                               | e = 0x0F     |               |              |              |   |   |  |  |  |  |

| Bit   | Name           |                                                                                           |              |               | Function     |              |   |   |  |  |  |  |

| 7:0   | P4MDOUT[7:     | 0] Output (                                                                               | Configuratio | on Bits for P | 4.7–P4.0 (re | espectively) |   |   |  |  |  |  |

|       |                | 0: Corresponding P4.n Output is open-drain.<br>1: Corresponding P4.n Output is push-pull. |              |               |              |              |   |   |  |  |  |  |

**Note:** Port 4.0 is available on 40-pin packages.

192

# 20. Local Interconnect Network (LIN0)

**Important Note:** This chapter assumes an understanding of the Local Interconnect Network (LIN) protocol. For more information about the LIN protocol, including specifications, please refer to the LIN consortium (http://www.lin-subbus.org).

LIN is an asynchronous, serial communications interface used primarily in automotive networks. The Silicon Laboratories LIN controller is compliant to the 2.1 Specification, implements a complete hardware LIN interface and includes the following features:

- Selectable Master and Slave modes.

- Automatic baud rate option in slave mode.

- The internal oscillator is accurate to within 0.5% of 24 MHz across the entire temperature range and for VDD voltages greater than or equal to the minimum output of the on-chip voltage regulator, so an external oscillator is not necessary for master mode operation for most systems.

Note: The minimum system clock (SYSCLK) required when using the LIN controller is 8 MHz.

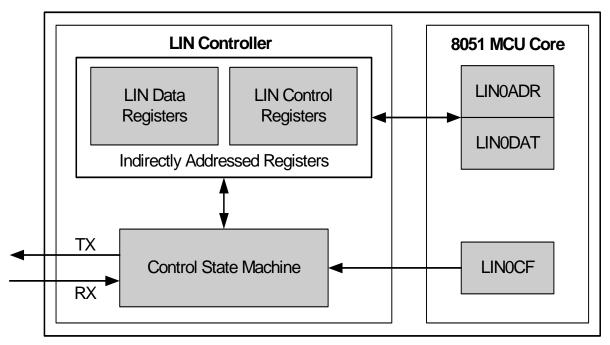

Figure 20.1. LIN Block Diagram

The LIN controller has four main components:

- LIN Access Registers—Provide the interface between the MCU core and the LIN controller.

- LIN Data Registers—Where transmitted and received message data bytes are stored.

- LIN Control Registers—Control the functionality of the LIN interface.

- Control State Machine and Bit Streaming Logic—Contains the hardware that serializes messages and controls the bus timing of the controller.

The application should perform the following steps when an interrupt is requested.

- 1. Check the DONE bit (LIN0ST.0) and the ERROR bit (LIN0ST.2).

- 2. If performing a master receive operation and the transfer was successful, read the received data from the data buffer.

- 3. If the transfer was not successful, check the error register to determine the kind of error. Further error handling has to be done by the application.

- 4. Set the RSTINT (LIN0CTRL.3) and RSTERR bits (LIN0CTRL.2) to reset the interrupt request and the error flags.

## 20.4. LIN Slave Mode Operation

When the device is configured for slave mode operation, it must wait for a command from a master node. Access from the firmware to the data buffer and ID registers of the LIN controller is only possible when a data request is pending (DTREQ bit (LINOST.4) is 1) and also when the LIN bus is not active (ACTIVE bit (LINOST.7) is set to 0).

The LIN controller in slave mode detects the header of the message frame sent by the LIN master. If slave synchronization is enabled (autobaud), the slave synchronizes its internal bit time to the master bit time.

The LIN controller configured for slave mode will generated an interrupt in one of three situations:

- 1. After the reception of the IDENTIFIER FIELD

- 2. When an error is detected

- 3. When the message transfer is completed.

The application should perform the following steps when an interrupt is detected:

- 1. Check the status of the DTREQ bit (LIN0ST.4). This bit is set when the IDENTIFIER FIELD has been received.

- 2. If DTREQ (LIN0ST.4) is set, read the identifier from LIN0ID and process it. If DTREQ (LIN0ST.4) is not set, continue to step 7.

- 3. Set the TXRX bit (LIN0CTRL.5) to 1 if the current frame is a transmit operation for the slave and set to 0 if the current frame is a receive operation for the slave.

- 4. Load the data length into LIN0SIZE.

- 5. For a slave transmit operation, load the data to transmit into the data buffer.

- 6. Set the DTACK bit (LIN0CTRL.4). Continue to step 10.

- 7. If DTREQ (LIN0ST.4) is not set, check the DONE bit (LIN0ST.0). The transmission was successful if the DONE bit is set.

- 8. If the transmission was successful and the current frame was a receive operation for the slave, load the received data bytes from the data buffer.

- 9. If the transmission was not successful, check LIN0ERR to determine the nature of the error. Further error handling has to be done by the application.

- 10.Set the RSTINT (LIN0CTRL.3) and RSTERR bits (LIN0CTRL.2) to reset the interrupt request and the error flags.

In addition to these steps, the application should be aware of the following:

- 1. If the current frame is a transmit operation for the slave, steps 1 through 5 must be completed during the IN-FRAME RESPONSE SPACE. If it is not completed in time, a timeout will be detected by the master.

- 2. If the current frame is a receive operation for the slave, steps 1 through 5 have to be finished until the reception of the first byte after the IDENTIFIER FIELD. Otherwise, the internal receive buffer of the LIN controller will be overwritten and a timeout error will be detected in the LIN controller.

- 3. The LIN controller does not directly support LIN Version 1.3 Extended Frames. If the application detects an unknown identifier (e.g. extended identifier), it has to write a 1 to the STOP bit (LIN0CTRL.7) instead of setting the DTACK (LIN0CTRL.4) bit. At that time, steps 2 through 5 can then be skipped. In this situation, the LIN controller stops the processing of LIN communication until the next SYNC BREAK is received.

- 4. Changing the configuration of the checksum during a transaction will cause the interface to reset and the transaction to be lost. To prevent this, the checksum should not be configured while a transaction is in progress. The same applies to changes in the LIN interface mode from slave mode to master mode and from master mode to slave mode.

## 20.5. Sleep Mode and Wake-Up

To reduce the system's power consumption, the LIN Protocol Specification defines a Sleep Mode. The message used to broadcast a Sleep Mode request must be transmitted by the LIN master application in the same way as a normal transmit message. The LIN slave application must decode the Sleep Mode Frame from the Identifier and data bytes. After that, it has to put the LIN slave node into the Sleep Mode by setting the SLEEP bit (LIN0CTRL.6).

If the SLEEP bit (LINOCTRL.6) of the LIN slave application is not set and there is no bus activity for four seconds (specified bus idle timeout), the IDLTOUT bit (LINOST.6) is set and an interrupt request is generated. After that the application may assume that the LIN bus is in Sleep Mode and set the SLEEP bit (LINOCTRL.6).

Sending a wake-up signal from the master or any slave node terminates the Sleep Mode of the LIN bus. To send a wake-up signal, the application has to set the WUPREQ bit (LIN0CTRL.1). After successful transmission of the wake-up signal, the DONE bit (LIN0ST.0) of the master node is set and an interrupt request is generated. The LIN slave does not generate an interrupt request after successful transmission of the wake-up signal but it generates an interrupt request if the master does not respond to the wake-up signal within 150 milliseconds. In that case, the ERROR bit (LIN0ST.2) and TOUT bit (LIN0ERR.2) are set. The application then has to decide whether or not to transmit another wake-up signal.

All LIN nodes that detect a wake-up signal will set the WAKEUP (LIN0ST.1) and DONE bits (LIN0ST.0) and generate an interrupt request. After that, the application has to clear the SLEEP bit (LIN0CTRL.6) in the LIN slave.

### 20.6. Error Detection and Handling

The LIN controller generates an interrupt request and stops the processing of the current frame if it detects an error. The application has to check the type of error by processing LIN0ERR. After that, it has to reset the error register and the ERROR bit (LIN0ST.2) by writing a 1 to the RSTERR bit (LIN0CTRL.2). Starting a new message with the LIN controller selected as master or sending a Wakeup signal with the LIN controller selected as a master or slave is possible only if the ERROR bit (LIN0ST.2) is set to 0.

|                    | Valu             | es | Re | ad                                                 |     | Current SMbus State                             | Typical Response Options                                                                       | Va<br>Wr | lues<br>ite | sto | s<br>ected                     |

|--------------------|------------------|----|----|----------------------------------------------------|-----|-------------------------------------------------|------------------------------------------------------------------------------------------------|----------|-------------|-----|--------------------------------|

| Mode               | Status<br>Vector |    |    | ARBLOST                                            | ACK |                                                 |                                                                                                | STA      | STO         | ACK | Next Status<br>Vector Expected |

|                    | 1110             | (  | 0  | 0                                                  | Х   | A master START was gener-<br>ated.              | Load slave address + R/W into SMB0DAT.                                                         | 0        | 0           | Х   | 1100                           |

|                    | 1100             | (  | 0  | 0                                                  | 0   | A master data or address byte                   | Set STA to restart transfer.                                                                   | 1        | 0           | Х   | 1110                           |

|                    |                  |    |    |                                                    |     | was transmitted; NACK received.                 | Abort transfer.                                                                                | 0        | 1           | Х   |                                |

|                    |                  | (  | 0  | 0                                                  | 1   | was transmitted; ACK                            | Load next data byte into SMB0-<br>DAT.                                                         | 0        | 0           | Х   | 1100                           |

|                    |                  |    |    |                                                    |     | received.                                       | End transfer with STOP.                                                                        | 0        | 1           | Х   | _                              |

| smitter            |                  |    |    | End transfer with STOP and start another transfer. | 1   | 1                                               | Х                                                                                              | —        |             |     |                                |

| rans               |                  |    |    |                                                    |     |                                                 | Send repeated START.                                                                           | 1        | 0           | Х   | 1110                           |

| Master Transmitter |                  |    |    |                                                    |     |                                                 | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT).           | 0        | 0           | Х   | 1000                           |

|                    | 1000             |    | 1  | 0                                                  | Х   | A master data byte was received; ACK requested. | Acknowledge received byte;<br>Read SMB0DAT.                                                    | 0        | 0           | 1   | 1000                           |

|                    |                  |    |    |                                                    |     |                                                 | Send NACK to indicate last byte, and send STOP.                                                | 0        | 1           | 0   | —                              |

|                    |                  |    |    |                                                    |     |                                                 | Send NACK to indicate last byte,<br>and send STOP followed by<br>START.                        | 1        | 1           | 0   | 1110                           |

|                    |                  |    |    |                                                    |     |                                                 | Send ACK followed by repeated START.                                                           | 1        | 0           | 1   | 1110                           |

|                    |                  |    |    |                                                    |     |                                                 | Send NACK to indicate last byte, and send repeated START.                                      | 1        | 0           | 0   | 1110                           |

| eceiver            |                  |    |    |                                                    |     |                                                 | Send ACK and switch to Master<br>Transmitter Mode (write to<br>SMB0DAT before clearing SI).    | 0        | 0           | 1   | 1100                           |

| Master Receiver    |                  |    |    |                                                    |     |                                                 | Send NACK and switch to Mas-<br>ter Transmitter Mode (write to<br>SMB0DAT before clearing SI). | 0        | 0           | 0   | 1100                           |

Table 22.4. SMBus Status Decoding

#### 23.3.3. Multiprocessor Communications

UART0 supports multiprocessor communication between a master processor and one or more slave processors by special use of the extra data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its extra bit is logic 1; in a data byte, the extra bit is always set to logic 0.

Setting the MCE0 bit (SMOD0.7) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the extra bit is logic 1 (RBX0 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned address. If the addresses match, the slave will clear its MCE0 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0 bits set and do not generate interrupts on the reception of the following data byte(s) bits of the following data bytes, thereby ignoring the data. Once the entire message is received, the addressed slave resets its MCE0 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

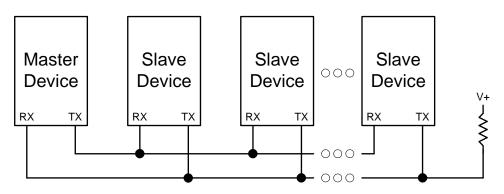

Figure 23.6. UART Multi-Processor Mode Interconnect Diagram

# SFR Definition 24.1. SPI0CFG: SPI0 Configuration

| Bit   | 7      | 6     | 5     | 4     | 3      | 2     | 1    | 0     |

|-------|--------|-------|-------|-------|--------|-------|------|-------|

| Name  | SPIBSY | MSTEN | СКРНА | CKPOL | SLVSEL | NSSIN | SRMT | RXBMT |

| Туре  | R      | R/W   | R/W   | R/W   | R      | R     | R    | R     |

| Reset | 0      | 0     | 0     | 0     | 0      | 1     | 1    | 1     |

## SFR Address = 0xA1; SFR Page = 0x00

| Bit   | Name                                                                                                                                                                                                                  | Function                                                                                                                                                                         |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7     | SPIBSY                                                                                                                                                                                                                | SPI Busy.                                                                                                                                                                        |  |  |  |  |

|       |                                                                                                                                                                                                                       | This bit is set to logic 1 when a SPI transfer is in progress (master or slave mode).                                                                                            |  |  |  |  |

| 6     | MSTEN                                                                                                                                                                                                                 | Master Mode Enable.                                                                                                                                                              |  |  |  |  |

|       |                                                                                                                                                                                                                       | 0: Disable master mode. Operate in slave mode.                                                                                                                                   |  |  |  |  |

|       |                                                                                                                                                                                                                       | 1: Enable master mode. Operate as a master.                                                                                                                                      |  |  |  |  |

| 5     | СКРНА                                                                                                                                                                                                                 | SPI0 Clock Phase.                                                                                                                                                                |  |  |  |  |

|       |                                                                                                                                                                                                                       | 0: Data centered on first edge of SCK period.*                                                                                                                                   |  |  |  |  |

|       |                                                                                                                                                                                                                       | 1: Data centered on second edge of SCK period.*                                                                                                                                  |  |  |  |  |

| 4     | CKPOL                                                                                                                                                                                                                 | SPI0 Clock Polarity.                                                                                                                                                             |  |  |  |  |

|       |                                                                                                                                                                                                                       | 0: SCK line low in idle state.                                                                                                                                                   |  |  |  |  |

|       |                                                                                                                                                                                                                       | 1: SCK line high in idle state.                                                                                                                                                  |  |  |  |  |

| 3     | SLVSEL                                                                                                                                                                                                                | Slave Selected Flag.                                                                                                                                                             |  |  |  |  |

|       |                                                                                                                                                                                                                       | This bit is set to logic 1 whenever the NSS pin is low indicating SPI0 is the selected                                                                                           |  |  |  |  |

|       |                                                                                                                                                                                                                       | slave. It is cleared to logic 0 when NSS is high (slave not selected). This bit does not indicate the instantaneous value at the NSS pin, but rather a de-glitched ver-          |  |  |  |  |

|       |                                                                                                                                                                                                                       | sion of the pin input.                                                                                                                                                           |  |  |  |  |

| 2     | NSSIN                                                                                                                                                                                                                 | NSS Instantaneous Pin Input.                                                                                                                                                     |  |  |  |  |

|       |                                                                                                                                                                                                                       | This bit mimics the instantaneous value that is present on the NSS port pin at the                                                                                               |  |  |  |  |

|       |                                                                                                                                                                                                                       | time that the register is read. This input is not de-glitched.                                                                                                                   |  |  |  |  |

| 1     | SRMT                                                                                                                                                                                                                  | Shift Register Empty (valid in slave mode only).                                                                                                                                 |  |  |  |  |

|       |                                                                                                                                                                                                                       | This bit will be set to logic 1 when all data has been transferred in/out of the shift                                                                                           |  |  |  |  |

|       |                                                                                                                                                                                                                       | register, and there is no new information available to read from the transmit buffer<br>or write to the receive buffer. It returns to logic 0 when a data byte is transferred to |  |  |  |  |

|       |                                                                                                                                                                                                                       | the shift register from the transmit buffer or by a transition on SCK. SRMT = 1 when                                                                                             |  |  |  |  |

|       |                                                                                                                                                                                                                       | in Master Mode.                                                                                                                                                                  |  |  |  |  |

| 0     | RXBMT                                                                                                                                                                                                                 | Receive Buffer Empty (valid in slave mode only).                                                                                                                                 |  |  |  |  |

|       |                                                                                                                                                                                                                       | This bit will be set to logic 1 when the receive buffer has been read and contains no                                                                                            |  |  |  |  |

|       |                                                                                                                                                                                                                       | new information. If there is new information available in the receive buffer that has                                                                                            |  |  |  |  |

|       | · · ·                                                                                                                                                                                                                 | not been read, this bit will return to logic 0. RXBMT = 1 when in Master Mode.                                                                                                   |  |  |  |  |

| Note: | te: In slave mode, data on MOSI is sampled in the center of each data bit. In master mode, data on MISO is sampled one SYSCLK before the end of each data bit, to provide maximum settling time for the slave device. |                                                                                                                                                                                  |  |  |  |  |

|       | See Table 24.1 for timing parameters.                                                                                                                                                                                 |                                                                                                                                                                                  |  |  |  |  |

| L     |                                                                                                                                                                                                                       |                                                                                                                                                                                  |  |  |  |  |

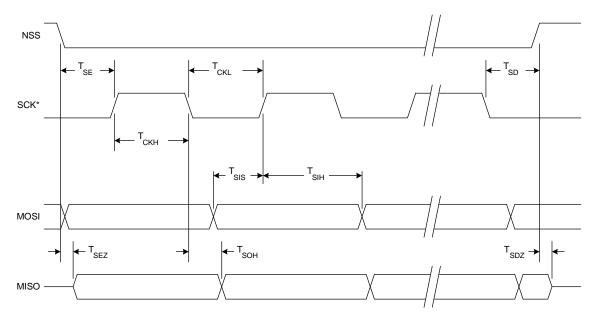

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

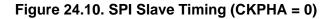

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

# SFR Definition 25.8. TMR2CN: Timer 2 Control

| Bit                                                                                                     | 7                                                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                              | 4                             | 3                                                                   | 2                           | 1                        | 0                       |

|---------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------|---------------------------------------------------------------------|-----------------------------|--------------------------|-------------------------|

| Name                                                                                                    | TF2H                                                 | TF2L                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TF2LEN                         | TF2CEN                        | T2SPLIT                                                             | TR2                         |                          | T2XCLK                  |

| Туре                                                                                                    | R/W                                                  | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W                            | R/W                           | R/W                                                                 | R/W                         | R                        | R/W                     |

| Rese                                                                                                    | <b>t</b> 0                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                              | 0                             | 0                                                                   | 0                           | 0                        | 0                       |

| SFR A                                                                                                   | SFR Address = 0xC8; Bit-Addressable; SFR Page = 0x00 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |                               |                                                                     |                             |                          |                         |

| Bit                                                                                                     | Name                                                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                |                               |                                                                     |                             |                          |                         |

| 7                                                                                                       | TF2H                                                 | Timer 2 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                |                               |                                                                     |                             |                          |                         |

|                                                                                                         |                                                      | mode, this v<br>Timer 2 inte                                                                                                                                                                                                                                                                                                                                                                                                                                                      | will occur wh<br>rrupt is enat | en Timer 2 c<br>bled, setting | high byte over<br>overflows fror<br>this bit cause<br>not automatic | n 0xFFFF to<br>es the CPU t | 0x0000. V<br>o vector to | Vhen the<br>the Timer 2 |

| 6                                                                                                       | TF2L                                                 | Timer 2 Lov                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | w Byte Ove                     | rflow Flag.                   |                                                                     |                             |                          |                         |

|                                                                                                         |                                                      | Set by hardware when the Timer 2 low byte overflows from 0xFF to 0x00. TF2L will be set when the low byte overflows regardless of the Timer 2 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                            |                                |                               |                                                                     |                             |                          |                         |

| 5                                                                                                       | TF2LEN                                               | Timer 2 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |                               |                                                                     |                             |                          |                         |

|                                                                                                         |                                                      | When set to 1, this bit enables Timer 2 Low Byte interrupts. If Timer 2 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 2 overflows.                                                                                                                                                                                                                                                                                                       |                                |                               |                                                                     |                             |                          |                         |

| 4                                                                                                       | 4 TF2CEN Timer 2 Capture Mode Enable.                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |                               |                                                                     |                             |                          |                         |

|                                                                                                         |                                                      | 0: Timer 2 Capture Mode is disabled.<br>1: Timer 2 Capture Mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                       |                                |                               |                                                                     |                             |                          |                         |

| 3 T2SPLIT Timer 2 Split Mode Enable.                                                                    |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |                               |                                                                     |                             |                          |                         |

| When this bit is set, Timer 2 operates a                                                                |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |                               |                                                                     |                             |                          |                         |

| 0: Timer 2 operates in 16-bit auto-reload mode.<br>1: Timer 2 operates as two 8-bit auto-reload timers. |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |                               |                                                                     |                             |                          |                         |

| 2                                                                                                       | TR2                                                  | Timer 2 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                |                               |                                                                     |                             |                          |                         |

|                                                                                                         |                                                      | Timer 2 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables<br>TMR2H only; TMR2L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                       |                                |                               |                                                                     |                             |                          |                         |

| 1                                                                                                       | Unused                                               | Read = 0b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                |                               |                                                                     |                             |                          |                         |

| 0                                                                                                       | 0 T2XCLK Timer 2 External Clock Select.              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |                               |                                                                     |                             |                          |                         |

|                                                                                                         |                                                      | This bit selects the external clock source for Timer 2. If Timer 2 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 2 Clock Select bits (T2MH and T2ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.<br>0: Timer 2 clock is the system clock divided by 12.<br>1: Timer 2 clock is the external clock divided by 8 (synchronized with SYSCLK). |                                |                               |                                                                     |                             |                          |                         |

# SFR Definition 25.13. TMR3CN: Timer 3 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1 | 0      |

|-------|------|------|--------|--------|---------|-----|---|--------|

| Name  | TF3H | TF3L | TF3LEN | TF3CEN | T3SPLIT | TR3 |   | T3XCLK |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R | R/W    |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0 | 0      |

### SFR Address = 0x91;SFR Page = 0x00

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF3H    | <b>Timer 3 High Byte Overflow Flag.</b><br>Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                                            |