#### Silicon Labs - <u>C8051F571-IM Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART      |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 33                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 32x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 40-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 40-QFN (6x6)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f571-im |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 22.3. SMB0DAT: SMBus Data                                | . 228 |

|-------------------------------------------------------------------------|-------|

| SFR Definition 23.1. SCON0: Serial Port 0 Control                       | . 241 |

| SFR Definition 23.2. SMOD0: Serial Port 0 Control                       | . 243 |

| SFR Definition 23.3. SBUF0: Serial (UART0) Port Data Buffer             |       |

| SFR Definition 23.4. SBCON0: UARTO Baud Rate Generator Control          | . 244 |

| SFR Definition 23.6. SBRLL0: UART0 Baud Rate Generator Reload Low Byte  |       |

| SFR Definition 23.5. SBRLH0: UART0 Baud Rate Generator Reload High Byte | . 245 |

| SFR Definition 24.1. SPI0CFG: SPI0 Configuration                        | . 253 |

| SFR Definition 24.2. SPI0CN: SPI0 Control                               | . 254 |

| SFR Definition 24.3. SPI0CKR: SPI0 Clock Rate                           | . 255 |

| SFR Definition 24.4. SPI0DAT: SPI0 Data                                 | . 255 |

| SFR Definition 25.1. CKCON: Clock Control                               | . 260 |

| SFR Definition 25.2. TCON: Timer Control                                | . 265 |

| SFR Definition 25.3. TMOD: Timer Mode                                   | . 266 |

| SFR Definition 25.4. TL0: Timer 0 Low Byte                              |       |

| SFR Definition 25.5. TL1: Timer 1 Low Byte                              |       |

| SFR Definition 25.6. TH0: Timer 0 High Byte                             |       |

| SFR Definition 25.7. TH1: Timer 1 High Byte                             |       |

| SFR Definition 25.8. TMR2CN: Timer 2 Control                            |       |

| SFR Definition 25.9. TMR2RLL: Timer 2 Reload Register Low Byte          |       |

| SFR Definition 25.10. TMR2RLH: Timer 2 Reload Register High Byte        |       |

| SFR Definition 25.11. TMR2L: Timer 2 Low Byte                           |       |

| SFR Definition 25.12. TMR2H Timer 2 High Byte                           |       |

| SFR Definition 25.13. TMR3CN: Timer 3 Control                           |       |

| SFR Definition 25.14. TMR3RLL: Timer 3 Reload Register Low Byte         |       |

| SFR Definition 25.15. TMR3RLH: Timer 3 Reload Register High Byte        |       |

| SFR Definition 25.16. TMR3L: Timer 3 Low Byte                           |       |

| SFR Definition 25.17. TMR3H Timer 3 High Byte                           |       |

| SFR Definition 26.1. PCA0CN: PCA Control                                |       |

| SFR Definition 26.2. PCA0MD: PCA Mode                                   |       |

| SFR Definition 26.3. PCA0PWM: PCA PWM Configuration                     |       |

| SFR Definition 26.4. PCA0CPMn: PCA Capture/Compare Mode                 |       |

| SFR Definition 26.5. PCA0L: PCA Counter/Timer Low Byte                  |       |

| SFR Definition 26.6. PCA0H: PCA Counter/Timer High Byte                 |       |

| SFR Definition 26.7. PCA0CPLn: PCA Capture Module Low Byte              |       |

| SFR Definition 26.8. PCA0CPHn: PCA Capture Module High Byte             | . 299 |

|                                                                         |       |

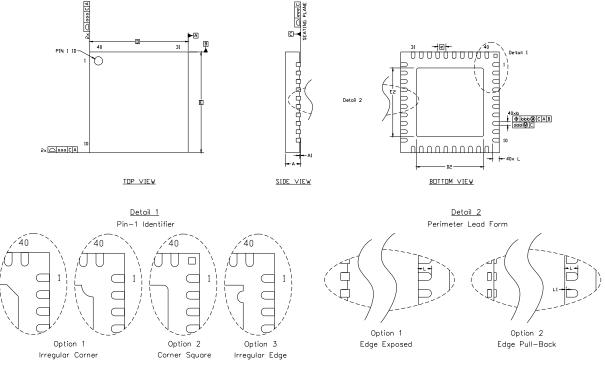

## 4. Package Specifications

#### 4.1. QFN-40 Package Specifications

### Figure 4.1. QFN-40 Package Drawing

| Dimension | Min      | Тур      | Max  | Dimension | Min  | Тур  | Max  |

|-----------|----------|----------|------|-----------|------|------|------|

| A         | 0.80     | 0.85     | 0.90 | E2        | 4.00 | 4.10 | 4.20 |

| A1        | 0.00     |          | 0.05 | L         | 0.35 | 0.40 | 0.45 |

| b         | 0.18     | 0.23     | 0.28 | L1        |      |      | 0.10 |

| D         |          | 6.00 BSC |      | aaa       |      |      | 0.10 |

| D2        | 4.00     | 4.10     | 4.20 | bbb       |      |      | 0.10 |

| е         | 0.50 BSC |          |      | ddd       |      |      | 0.05 |

| E         |          | 6.00 BSC |      | eee       |      |      | 0.08 |

#### Table 4.1. QFN-40 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

**3.** This drawing conforms to JEDEC Solid State Outline MO-220, variation VJJD-5, except for features A, D2, and E2 which are toleranced per supplier designation.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### Table 5.7. Clock Multiplier Electrical Specifications

$V_{DD}$  = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter                            | Conditions | Min | Тур | Max | Units |

|--------------------------------------|------------|-----|-----|-----|-------|

| Input Frequency (Fcm <sub>in</sub> ) |            | 2   | —   | —   | MHz   |

| Output Frequency                     |            |     |     | 50  | MHz   |

| Power Supply Current                 |            | —   | 0.9 | 1.9 | mA    |

#### Table 5.8. Voltage Regulator Electrical Characteristics

$V_{DD}$  = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter                                 | Conditions                                                                | Min         | Тур     | Max   | Units |

|-------------------------------------------|---------------------------------------------------------------------------|-------------|---------|-------|-------|

| Input Voltage Range (V <sub>REGIN</sub> ) |                                                                           | 1.8*        | _       | 5.25  | V     |

| Dropout Voltage (V <sub>DO</sub> )        | Maximum Current = 50 mA                                                   | —           | 10      |       | mV/mA |

| Output Voltage (V <sub>DD</sub> )         | 2.1 V operation (REG0MD = 0)                                              | 2.0         | 2.1     | 2.25  | V     |

|                                           | 2.6 V operation (REG0MD = 1)                                              | 2.5         | 2.6     | 2.75  | v     |

| Bias Current                              |                                                                           |             | 1       | 9     | μA    |

| Dropout Indicator Detection<br>Threshold  | With respect to VDD                                                       | -0.21       | _       | -0.02 | V     |

| Output Voltage Temperature<br>Coefficient |                                                                           | _           | 0.29    | —     | mV/°C |

| VREG Settling Time                        | 50 mA load with $V_{REGIN}$ = 2.4 V and $V_{DD}$ load capacitor of 4.8 µF | _           | 450     | _     | μs    |

| *Note: The minimum input voltage          | e is 1.8 V or $V_{DD}$ + $V_{DO}$ (max load), whi                         | chever is g | greater | •     | •     |

#### SFR Definition 6.11. ADC0LTH: ADC0 Less-Than Data High Byte

| Bit   | 7                | 6                                         | 5        | 4 | 3 | 2 | 1 | 0 |

|-------|------------------|-------------------------------------------|----------|---|---|---|---|---|

| Nam   | ame ADC0LTH[7:0] |                                           |          |   |   |   |   |   |

| Туре  | •                | R/W                                       |          |   |   |   |   |   |

| Rese  | et 0             | 0                                         | 0        | 0 | 0 | 0 | 0 | 0 |

| SFR A | Address = 0xC6   | ; SFR Page                                | e = 0x00 |   |   |   |   |   |

| Bit   | Name             |                                           | Function |   |   |   |   |   |

| 7:0   | ADC0LTH[7:0]     | ADC0 Less-Than Data Word High-Order Bits. |          |   |   |   |   |   |

#### SFR Definition 6.12. ADC0LTL: ADC0 Less-Than Data Low Byte

| Bit                                 | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------------------------|--------------|---|---|---|---|---|---|---|

| Name                                | ADC0LTL[7:0] |   |   |   |   |   |   |   |

| Туре                                | R/W          |   |   |   |   |   |   |   |

| Reset                               | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0xC5; SFR Page = 0x00 |              |   |   |   |   |   |   |   |

| Bit | Name         | Function                                 |

|-----|--------------|------------------------------------------|

| 7:0 | ADC0LTL[7:0] | ADC0 Less-Than Data Word Low-Order Bits. |

#### 6.4.1. Window Detector In Single-Ended Mode

Figure 6.6 example shows two window comparisons for right-justified data with ADC0LTH:ADC0LTL = 0x0200 (512d) and ADC0GTH:ADC0GTL = 0x0100 (256d). The input voltage can range from 0 to V<sub>REF</sub> x (4095/4096) with respect to GND, and is represented by a 12-bit unsigned integer value. The repeat count is set to one. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0100 < ADC0H:ADC0L < 0x0200). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0100 or ADC0H:ADC0L > 0x0200). Figure 6.7 shows an example using left-justified data with the same comparison values.

## SFR Definition 8.6. CPT1MX: Comparator1 MUX Selection

| Bit   | 7             | 6                       | 5                | 4                                                  | 3             | 2             | 1          | 0 |  |

|-------|---------------|-------------------------|------------------|----------------------------------------------------|---------------|---------------|------------|---|--|

| Nam   | е             | CMX1                    | N[3:0]           | 1                                                  |               | CMX1          | P[3:0]     |   |  |

| Туре  | •             | R/                      | W                |                                                    | R/W           |               |            |   |  |

| Rese  | _             | 1                       | 1                | 1                                                  | 0             | 1             | 1          | 1 |  |

| SFR A | Address = 0x9 | F <sup>.</sup> SER Page | $= 0 \times 0 0$ |                                                    |               |               |            |   |  |

| Bit   | Name          |                         |                  |                                                    |               |               |            |   |  |

| 7:4   | CMX1N[3:0]    | Comparato               | r1 Negative      | Input MUX                                          | Selection.    |               |            |   |  |

|       |               | 0000:                   | P0.              | 1                                                  |               |               |            |   |  |

|       |               | 0001:                   | P0.              | 3                                                  |               |               |            |   |  |

|       |               | 0010:                   | P0.              | 5                                                  |               |               |            |   |  |

|       |               | 0011:                   | P0.              | 7                                                  |               |               |            |   |  |

|       |               | 0100:                   | P1.              | 1                                                  |               |               |            |   |  |

|       |               | 0101:                   | P1.              | 3                                                  |               |               |            |   |  |

|       |               | 0110:                   | P1.              | 5                                                  |               |               |            |   |  |

|       |               | 0111:                   | P1.              | 7                                                  |               |               |            |   |  |

|       |               | 1000:                   | P2.              | 1                                                  |               |               |            |   |  |

|       |               | 1001:                   | P2.              | 3 (only avai                                       | lable on 40-p | oin and 32-pi | n devices) |   |  |

|       |               | 1010:                   | P2.              | P2.5 (only available on 40-pin and 32-pin devices) |               |               |            |   |  |

|       |               | 1011:                   | P2.              | 7 (only avai                                       | lable on 40-p | oin and 32-pi | n devices) |   |  |

|       |               | 1100–1111:              | Nor              | ne                                                 |               |               |            |   |  |

| 3:0   | CMX1P[3:0]    | Comparato               | r1 Positive      | Input MUX                                          | Selection.    |               |            |   |  |

|       |               | 0000:                   | P0.              | 0                                                  |               |               |            |   |  |

|       |               | 0001:                   | P0.              | 2                                                  |               |               |            |   |  |

|       |               | 0010:                   | P0.              | 4                                                  |               |               |            |   |  |

|       |               | 0011:                   | P0.              | 6                                                  |               |               |            |   |  |

|       |               | 0100:                   | P1.              | 0                                                  |               |               |            |   |  |

|       |               | 0101:                   | P1.              | 2                                                  |               |               |            |   |  |

|       |               | 0110:                   | P1.              | 4                                                  |               |               |            |   |  |

|       |               | 0111:                   | P1.              | 6                                                  |               |               |            |   |  |

|       |               | 1000:                   | P2.              | 0                                                  |               |               |            |   |  |

|       |               | 1001:                   | P2.              | 2 (only avai                                       | lable on 40-p | pin and 32-pi | n devices) |   |  |

|       |               | 1010:                   | P2.              | 4 (only avai                                       | lable on 40-p | oin and 32-pi | n devices) |   |  |

|       |               | 1011:                   | P2.              | 6 (only avai                                       | lable on 40-p | oin and 32-pi | n devices) |   |  |

|       |               | 1100–1111:              | Nor              | ne                                                 |               |               |            |   |  |

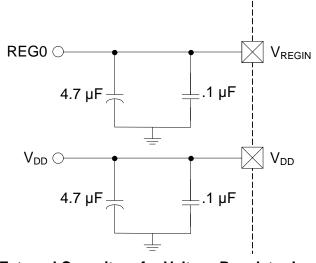

## 9. Voltage Regulator (REG0)

C8051F55x/56x/57x devices include an on-chip low dropout voltage regulator (REG0). The input to REG0 at the  $V_{REGIN}$  pin can be as high as 5.25 V. The output can be selected by software to 2.1 V or 2.6 V. When enabled, the output of REG0 appears on the  $V_{DD}$  pin, powers the microcontroller core, and can be used to power external devices. On reset, REG0 is enabled and can be disabled by software.

The Voltage regulator can generate an interrupt (if enabled by EREG0, EIE2.0) that is triggered whenever the  $V_{REGIN}$  input voltage drops below the dropout threshold voltage. This dropout interrupt has no pending flag and the recommended procedure to use it is as follows:

- 1. Wait enough time to ensure the  $V_{REGIN}$  input voltage is stable

- 2. Enable the dropout interrupt (EREG0, EIE2.0) and select the proper priority (PREG0, EIP2.0)

- 3. If triggered, inside the interrupt disable it (clear EREG0, EIE2.0), execute all procedures necessary to protect your application (put it in a safe mode and leave the interrupt now disabled.

- 4. In the main application, now running in the safe mode, regularly checks the DROPOUT bit (REG0CN.0). Once it is cleared by the regulator hardware the application can enable the interrupt again (EREG0, EIE1.6) and return to the normal mode operation.

The input ( $V_{REGIN}$ ) and output ( $V_{DD}$ ) of the voltage regulator should both be bypassed with a large capacitor (4.7  $\mu$ F + 0.1  $\mu$ F) to ground as shown in Figure 9.1. This capacitor will eliminate power spikes and provide any immediate power required by the microcontroller. The settling time associated with the voltage regulator is shown in Table 5.8 on page 43.

**Note:** The output of the internal voltage regulator is calibrated by the MCU immediately after any reset event. The output of the un-calibrated internal regulator could be below the high threshold setting of the  $V_{DD}$  Monitor. If this is the case *and* the  $V_{DD}$  Monitor is set to the high threshold setting *and* if the MCU receives a non-power on reset (POR), the MCU will remain in reset until a POR occurs (i.e.,  $V_{DD}$  Monitor will keep the device in reset). A POR will force the  $V_{DD}$  Monitor to the low threshold setting which is guaranteed to be below the un-calibrated output of the internal regulator. The device will then exit reset and resume normal operation. It is for this reason Silicon Labs strongly recommends that the  $V_{DD}$  Monitor is always left in the low threshold setting (i.e. default value upon POR).

#### Table 10.1. CIP-51 Instruction Set Summary

| Mnemonic              | Description                              | Bytes | Clock<br>Cycles |

|-----------------------|------------------------------------------|-------|-----------------|

| Arithmetic Operations |                                          | I     |                 |

| ADD A, Rn             | Add register to A                        | 1     | 1               |

| ADD A, direct         | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri            | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data          | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn            | Add register to A with carry             | 1     | 1               |

| ADDC A, direct        | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri           | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data         | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn            | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct        | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri           | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data         | Subtract immediate from A with borrow    | 2     | 2               |

| INC A                 | Increment A                              | 1     | 1               |

| INC Rn                | Increment register                       | 1     | 1               |

| INC direct            | Increment direct byte                    | 2     | 2               |

| INC @Ri               | Increment indirect RAM                   | 1     | 2               |

| DEC A                 | Decrement A                              | 1     | 1               |

| DEC Rn                | Decrement register                       | 1     | 1               |

| DEC direct            | Decrement direct byte                    | 2     | 2               |

| DEC @Ri               | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR              | Increment Data Pointer                   | 1     | 1               |

| MUL AB                | Multiply A and B                         | 1     | 4               |

| DIV AB                | Divide A by B                            | 1     | 8               |

| DA A                  | Decimal adjust A                         | 1     | 1               |

| Logical Operations    |                                          | I     |                 |

| ANL A, Rn             | AND Register to A                        | 1     | 1               |

| ANL A, direct         | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri            | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data          | AND immediate to A                       | 2     | 2               |

| ANL direct, A         | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data     | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn             | OR Register to A                         | 1     | 1               |

| ORL A, direct         | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri            | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data          | OR immediate to A                        | 2     | 2               |

| ORL direct, A         | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data     | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn             | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct         | Exclusive-OR direct byte to A            | 2     | 2               |

| XRL A, @Ri            | Exclusive-OR indirect RAM to A           | 1     | 2               |

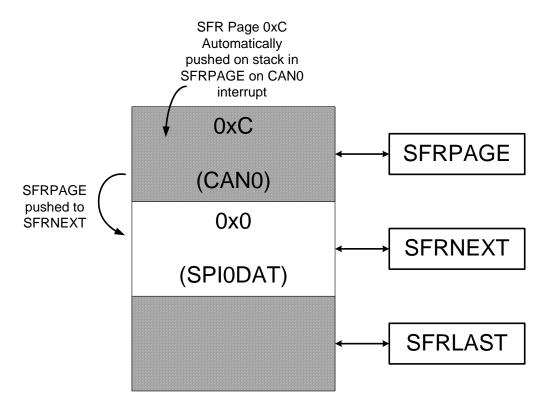

While CIP-51 executes in-line code (writing values to SPI0DAT in this example), the CAN0 Interrupt occurs. The CIP-51 vectors to the CAN0 ISR and pushes the current SFR Page value (SFR Page 0x00) into SFRNEXT in the SFR Page Stack. The SFR page needed to access CAN's SFRs is then automatically placed in the SFRPAGE register (SFR Page 0x0C). SFRPAGE is considered the "top" of the SFR Page Stack. Software can now access the CAN0 SFRs. Software may switch to any SFR Page by writing a new value to the SFRPAGE register at any time during the CAN0 ISR to access SFRs that are not on SFR Page 0x0C. See Figure 12.3.

Figure 12.3. SFR Page Stack After CAN0 Interrupt Occurs

## Table 12.3. Special Function Registers (Continued)

| SERs are listed in alphabetical order  | All undefined SFR locations are reserved |

|----------------------------------------|------------------------------------------|

| SERS are listed in alphabetical order. | All undernied SFR locations are reserved |

| Register | Address | Description                     | Page |

|----------|---------|---------------------------------|------|

| SMB0CF   | 0xC1    | SMBus0 Configuration            | 224  |

| SMB0CN   | 0xC0    | SMBus0 Control                  | 226  |

| SMB0DAT  | 0xC2    | SMBus0 Data                     | 228  |

| SMOD0    | 0xA9    | UART0 Mode                      | 243  |

| SN0      | 0xF9    | Serial Number 0                 | 91   |

| SN1      | 0xFA    | Serial Number 1                 | 91   |

| SN2      | 0xFB    | Serial Number 2                 | 91   |

| SN3      | 0xFC    | Serial Number 3                 | 91   |

| SP       | 0x81    | Stack Pointer                   | 89   |

| SPI0CFG  | 0xA1    | SPI0 Configuration              | 253  |

| SPI0CKR  | 0xA2    | SPI0 Clock Rate Control         | 255  |

| SPIOCN   | 0xF8    | SPI0 Control                    | 254  |

| SPIODAT  | 0xA3    | SPI0 Data                       | 255  |

| TCON     | 0x88    | Timer/Counter Control           | 265  |

| TH0      | 0x8C    | Timer/Counter 0 High            | 268  |

| TH1      | 0x8D    | Timer/Counter 1 High            | 268  |

| TL0      | 0x8A    | Timer/Counter 0 Low             | 267  |

| TL1      | 0x8B    | Timer/Counter 1 Low             | 267  |

| TMOD     | 0x89    | Timer/Counter Mode              | 266  |

| TMR2CN   | 0xC8    | Timer/Counter 2 Control         | 272  |

| TMR2H    | 0xCD    | Timer/Counter 2 High            | 274  |

| TMR2L    | 0xCC    | Timer/Counter 2 Low             | 274  |

| TMR2RLH  | 0xCB    | Timer/Counter 2 Reload High     | 273  |

| TMR2RLL  | 0xCA    | Timer/Counter 2 Reload Low      | 273  |

| TMR3CN   | 0x91    | Timer/Counter 3 Control         | 278  |

| TMR3H    | 0x95    | Timer/Counter 3 High            | 280  |

| TMR3L    | 0x94    | Timer/Counter 3 Low             | 280  |

| TMR3RLH  | 0x93    | Timer/Counter 3 Reload High     | 279  |

| TMR3RLL  | 0x92    | Timer/Counter 3 Reload Low      | 279  |

| VDM0CN   | 0xFF    | V <sub>DD</sub> Monitor Control | 141  |

| XBR0     | 0xE1    | Port I/O Crossbar Control 0     | 176  |

| XBR1     | 0xE2    | Port I/O Crossbar Control 1     | 177  |

| XBR2     | 0xC7    | Port I/O Crossbar Control 2     | 178  |

## SFR Definition 13.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0xA8; Bit-Addressable; SFR Page = All Pages

| Bit | Name  | Function                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <ul> <li>Enable All Interrupts.</li> <li>Globally enables/disables all interrupts. It overrides individual interrupt mask settings.</li> <li>0: Disable all interrupt sources.</li> <li>1: Enable each interrupt according to its individual mask setting.</li> </ul> |

| 6   | ESPI0 | <ul> <li>Enable Serial Peripheral Interface (SPI0) Interrupt.</li> <li>This bit sets the masking of the SPI0 interrupts.</li> <li>0: Disable all SPI0 interrupts.</li> <li>1: Enable interrupt requests generated by SPI0.</li> </ul>                                 |

| 5   | ET2   | <ul> <li>Enable Timer 2 Interrupt.</li> <li>This bit sets the masking of the Timer 2 interrupt.</li> <li>0: Disable Timer 2 interrupt.</li> <li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li> </ul>                                          |

| 4   | ES0   | Enable UART0 Interrupt.<br>This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.<br>1: Enable UART0 interrupt.                                                                                                                             |

| 3   | ET1   | <ul> <li>Enable Timer 1 Interrupt.</li> <li>This bit sets the masking of the Timer 1 interrupt.</li> <li>0: Disable all Timer 1 interrupt.</li> <li>1: Enable interrupt requests generated by the TF1 flag.</li> </ul>                                                |

| 2   | EX1   | <ul> <li>Enable External Interrupt 1.</li> <li>This bit sets the masking of External Interrupt 1.</li> <li>0: Disable external interrupt 1.</li> <li>1: Enable interrupt requests generated by the INT1 input.</li> </ul>                                             |

| 1   | ET0   | <ul> <li>Enable Timer 0 Interrupt.</li> <li>This bit sets the masking of the Timer 0 interrupt.</li> <li>0: Disable all Timer 0 interrupt.</li> <li>1: Enable interrupt requests generated by the TF0 flag.</li> </ul>                                                |

| 0   | EX0   | <ul> <li>Enable External Interrupt 0.</li> <li>This bit sets the masking of External Interrupt 0.</li> <li>0: Disable external interrupt 0.</li> <li>1: Enable interrupt requests generated by the INTO input.</li> </ul>                                             |

### SFR Definition 13.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7     | 6   | 5    | 4    | 3     | 2     | 1      | 0     |

|-------|-------|-----|------|------|-------|-------|--------|-------|

| Name  | ELIN0 | ET3 | ECP1 | ECP0 | EPCA0 | EADC0 | EWADC0 | ESMB0 |

| Туре  | R/W   | R/W | R/W  | R/W  | R/W   | R/W   | R/W    | R/W   |

| Reset | 0     | 0   | 0    | 0    | 0     | 0     | 0      | 0     |

#### SFR Address = 0xE6; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                                          |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ELIN0  | Enable LIN0 Interrupt.<br>This bit sets the masking of the LIN0 interrupt.<br>0: Disable LIN0 interrupts.<br>1: Enable interrupt requests generated by the LIN0INT flag.                                                                                                          |

| 6   | ET3    | <ul> <li>Enable Timer 3 Interrupt.</li> <li>This bit sets the masking of the Timer 3 interrupt.</li> <li>0: Disable Timer 3 interrupts.</li> <li>1: Enable interrupt requests generated by the TF3L or TF3H flags.</li> </ul>                                                     |

| 5   | ECP1   | Enable Comparator1 (CP1) Interrupt.<br>This bit sets the masking of the CP1 interrupt.<br>0: Disable CP1 interrupts.<br>1: Enable interrupt requests generated by the CP1RIF or CP1FIF flags.                                                                                     |

| 4   | ECP0   | <ul> <li>Enable Comparator0 (CP0) Interrupt.</li> <li>This bit sets the masking of the CP0 interrupt.</li> <li>0: Disable CP0 interrupts.</li> <li>1: Enable interrupt requests generated by the CP0RIF or CP0FIF flags.</li> </ul>                                               |

| 3   | EPCA0  | <ul> <li>Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> </ul>                                              |

| 2   | EADC0  | <ul> <li>Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> </ul>          |

| 1   | EWADC0 | <ul> <li>Enable Window Comparison ADC0 Interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ul> |

| 0   | ESMB0  | Enable SMBus (SMB0) Interrupt.<br>This bit sets the masking of the SMB0 interrupt.<br>0: Disable all SMB0 interrupts.<br>1: Enable interrupt requests generated by SMB0.                                                                                                          |

## SFR Definition 13.7. IT01CF: INT0/INT1 Configuration

| Bit   | 7     | 6   | 5          | 4   | 3   | 2          | 1 | 0 |

|-------|-------|-----|------------|-----|-----|------------|---|---|

| Name  | IN1PL |     | IN1SL[2:0] |     |     | IN0SL[2:0] |   |   |

| Туре  | R/W   | R/W |            | R/W | R/W |            |   |   |

| Reset | 0     | 0   | 0          | 0   | 0   | 0          | 0 | 0 |

#### SFR Address = 0xE4; SFR Page = 0x0F

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IN1PL      | INT1 Polarity.<br>0: INT1 input is active low.<br>1: INT1 input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6:4 | IN1SL[2:0] | INT1 Port Pin Selection Bits.<br>These bits select which Port pin is assigned to INT1. Note that this pin assignment is<br>independent of the Crossbar; INT1 will monitor the assigned Port pin without disturb-<br>ing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar<br>will not assign the Port pin to a peripheral if it is configured to skip the selected pin.<br>000: Select P1.0<br>001: Select P1.1<br>010: Select P1.2<br>011: Select P1.3<br>100: Select P1.4<br>101: Select P1.5<br>110: Select P1.6<br>111: Select P1.7 |

| 3   | IN0PL      | INTO Polarity.<br>0: INTO input is active low.<br>1: INTO input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2:0 | IN0SL[2:0] | INTO Port Pin Selection Bits.<br>These bits select which Port pin is assigned to INTO. Note that this pin assignment is<br>independent of the Crossbar; INTO will monitor the assigned Port pin without disturb-<br>ing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar<br>will not assign the Port pin to a peripheral if it is configured to skip the selected pin.<br>000: Select P1.0<br>001: Select P1.1<br>010: Select P1.2<br>011: Select P1.3<br>100: Select P1.4<br>101: Select P1.5<br>110: Select P1.6<br>111: Select P1.7 |

#### 16.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0–), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

#### 16.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "26.4. Watchdog Timer Mode" on page 291; the WDT is enabled and clocked by SYSCLK/12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

#### 16.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address in or above the reserved space.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address in or above the reserved space.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address in or above the reserved space.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "14.3. Security Options" on page 127).

- A Flash read, write, or erase is attempted when the VDD Monitor is not enabled to the high threshold and set as a reset source.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

#### 16.8. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the RST pin is unaffected by this reset.

#### 17.5.3. Split Mode with Bank Select

When EMI0CF[3:2] are set to 10, the XRAM memory map is split into two areas, on-chip space and offchip space.

- Effective addresses below the internal XRAM size boundary will access on-chip XRAM space.

- Effective addresses above the internal XRAM size boundary will access off-chip space.

- 8-bit MOVX operations use the contents of EMI0CN to determine whether the memory access is onchip or off-chip. The upper 8-bits of the Address Bus A[15:8] are determined by EMI0CN, and the lower 8-bits of the Address Bus A[7:0] are determined by R0 or R1. All 16-bits of the Address Bus A[15:0] are driven in "Bank Select" mode.

- 16-bit MOVX operations use the contents of DPTR to determine whether the memory access is on-chip or off-chip, and the full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

#### 17.5.4. External Only

When EMI0CF[3:2] are set to 11, all MOVX operations are directed to off-chip space. On-chip XRAM is not visible to the CPU. This mode is useful for accessing off-chip memory located between 0x0000 and the internal XRAM size boundary.

- 8-bit MOVX operations ignore the contents of EMI0CN. The upper Address bits A[15:8] are not driven (identical behavior to an off-chip access in "Split Mode without Bank Select" described above). This allows the user to manipulate the upper address bits at will by setting the Port state directly. The lower 8-bits of the effective address A[7:0] are determined by the contents of R0 or R1.

- 16-bit MOVX operations use the contents of DPTR to determine the effective address A[15:0]. The full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

#### 17.6. Timing

The timing parameters of the External Memory Interface can be configured to enable connection to devices having different setup and hold time requirements. The Address Setup time, Address Hold time, RD and WR strobe widths, and in multiplexed mode, the width of the ALE pulse are all programmable in units of SYSCLK periods through EMI0TC, shown in SFR Definition 17.3, and EMI0CF[1:0].

The timing for an off-chip MOVX instruction can be calculated by adding 4 SYSCLK cycles to the timing parameters defined by the EMI0TC register. Assuming non-multiplexed operation, the minimum execution time for an off-chip XRAM operation is 5 SYSCLK cycles (1 SYSCLK for RD or WR pulse + 4 SYSCLKs). For multiplexed operations, the Address Latch Enable signal will require a minimum of 2 additional SYSCLK cycles. Therefore, the minimum execution time for an off-chip XRAM operation in multiplexed mode is 7 SYSCLK cycles (2 for /ALE + 1 for RD or WR + 4). The programmable setup and hold times default to the maximum delay settings after a reset. Table 17.2 lists the ac parameters for the External Memory Interface, and Figure 17.3 through Figure 17.5 show the timing diagrams for the different External Memory Interface modes and MOVX operations.

## SFR Definition 18.6. OSCXCN: External Oscillator Control

| Bit   | 7      | 6   | 5           | 4 | 3 | 2         | 1   | 0 |

|-------|--------|-----|-------------|---|---|-----------|-----|---|

| Name  | XTLVLD | ×   | XOSCMD[2:0] |   |   | XFCN[2:0] |     |   |

| Туре  | R      | R/W |             |   | R |           | R/W |   |

| Reset | 0      | 0   | 0           | 0 | 0 | 0         | 0   | 0 |

#### SFR Address = 0x9F; SFR Page = 0x0F

| Bit | Name        |          | -                                                                  | Function                                  |                 |  |  |  |  |  |

|-----|-------------|----------|--------------------------------------------------------------------|-------------------------------------------|-----------------|--|--|--|--|--|

| 7   | XTLVLD      | Crystal  | Crystal Oscillator Valid Flag.                                     |                                           |                 |  |  |  |  |  |

|     |             | •        | (Read only when XOSCMD = 11x.)                                     |                                           |                 |  |  |  |  |  |

|     |             | -        | al Oscillator is unused of                                         |                                           |                 |  |  |  |  |  |

|     |             | -        | al Oscillator is running a                                         |                                           |                 |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] |          | I Oscillator Mode Sele                                             |                                           |                 |  |  |  |  |  |

|     |             |          | ternal Oscillator circuit of                                       |                                           |                 |  |  |  |  |  |

|     |             |          | ternal CMOS Clock Mod<br>ernal CMOS Clock Mod                      |                                           |                 |  |  |  |  |  |

|     |             |          | Coscillator Mode.                                                  | e with divide by 2 stage.                 |                 |  |  |  |  |  |

|     |             |          | pacitor Oscillator Mode.                                           |                                           |                 |  |  |  |  |  |

|     |             | 110: Cry | stal Oscillator Mode.                                              |                                           |                 |  |  |  |  |  |

|     |             | 111: Cry | 111: Crystal Oscillator Mode with divide by 2 stage.               |                                           |                 |  |  |  |  |  |

| 3   | Unused      | Read =   | Read = 0b; Write =0b                                               |                                           |                 |  |  |  |  |  |

| 2:0 | XFCN[2:0]   | Externa  | External Oscillator Frequency Control Bits.                        |                                           |                 |  |  |  |  |  |

|     |             |          | •                                                                  | quency for Crystal or RC                  | mode.           |  |  |  |  |  |

|     |             | Set acc  | ording to the desired K F                                          | actor for C mode.                         |                 |  |  |  |  |  |

|     |             | XFCN     | Crystal Mode                                                       | RC Mode                                   | C Mode          |  |  |  |  |  |

|     |             | 000      | f ≤ 32 kHz                                                         | f ≤ 25 kHz                                | K Factor = 0.87 |  |  |  |  |  |

|     |             | 001      | 32 kHz < f ≤ 84 kHz                                                | 25 kHz < f ≤ 50 kHz                       | K Factor = 2.6  |  |  |  |  |  |

|     |             | 010      | 84 kHz < f ≤ 225 kHz                                               | 50 kHz < f ≤ 100 kHz                      | K Factor = 7.7  |  |  |  |  |  |

|     |             | 011      | 225 kHz < f $\le$ 590 kHz 100 kHz < f $\le$ 200 kHz K Factor = 22  |                                           |                 |  |  |  |  |  |

|     |             | 100      | 590 kHz < f $\leq$ 1.5 MHz 200 kHz < f $\leq$ 400 kHz K Factor = 6 |                                           |                 |  |  |  |  |  |

|     |             | 101      | $1.5 \text{ MHz} < f \le 4 \text{ MHz}$                            | 400 kHz < f ≤ 800 kHz                     | K Factor = 180  |  |  |  |  |  |

|     |             | 110      | $4 \text{ MHz} < f \le 10 \text{ MHz}$                             | 800 kHz < f ≤ 1.6 MHz                     | K Factor = 664  |  |  |  |  |  |

|     |             | 111      | $10 \text{ MHz} < f \le 30 \text{ MHz}$                            | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$ | K Factor = 1590 |  |  |  |  |  |

#### 20.7.2. LIN Indirect Access SFR Registers Definitions

Table 20.4 lists the 15 indirect registers used to configured and communicate with the LIN controller.

| Name     | Address                                                                                                                                                                                                                                                          | Bit7                         | Bit6       | Bit5     | Bit4     | Bit3    | Bit2   | Bit1      | Bit0     |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------|----------|----------|---------|--------|-----------|----------|--|

| LIN0DT1  | 0x00                                                                                                                                                                                                                                                             |                              | DATA1[7:0] |          |          |         |        |           |          |  |

| LIN0DT2  | 0x01                                                                                                                                                                                                                                                             |                              | DATA2[7:0] |          |          |         |        |           |          |  |

| LIN0DT3  | 0x02                                                                                                                                                                                                                                                             |                              |            |          | DATA     | 3[7:0]  |        |           |          |  |

| LIN0DT4  | 0x03                                                                                                                                                                                                                                                             |                              |            |          | DATA     | 4[7:0]  |        |           |          |  |

| LIN0DT5  | 0x04                                                                                                                                                                                                                                                             |                              |            |          | DATAS    | 5[7:0]  |        |           |          |  |

| LIN0DT6  | 0x05                                                                                                                                                                                                                                                             |                              |            |          | DATA     | 67:0]   |        |           |          |  |

| LIN0DT7  | 0x06                                                                                                                                                                                                                                                             |                              |            |          | DATA     | 7[7:0]  |        |           |          |  |

| LIN0DT8  | 0x07                                                                                                                                                                                                                                                             |                              |            |          | DATA     | 3[7:0]  |        |           |          |  |

| LIN0CTRL | 0x08                                                                                                                                                                                                                                                             | STOP(s)                      | SLEEP(s)   | TXRX     | DTACK(s) | RSTINT  | RSTERR | WUPREQ    | STREQ(m) |  |

| LIN0ST   | 0x09                                                                                                                                                                                                                                                             | ACTIVE                       | IDLTOUT    | ABORT(s) | DTREQ(s) | LININT  | ERROR  | WAKEUP    | DONE     |  |

| LIN0ERR  | 0x0A                                                                                                                                                                                                                                                             |                              |            |          | SYNCH(s) | PRTY(s) | TOUT   | СНК       | BITERR   |  |

| LIN0SIZE | 0x0B                                                                                                                                                                                                                                                             | ENHCHK                       |            |          |          |         | LINS   | SIZE[3:0] |          |  |

| LIN0DIV  | 0x0C                                                                                                                                                                                                                                                             |                              |            |          | DIVLS    | B[7:0]  |        |           |          |  |

| LIN0MUL  | 0x0D                                                                                                                                                                                                                                                             | PRESCL[1:0] LINMUL[4:0] DIV9 |            |          |          |         |        | DIV9      |          |  |

| LIN0ID   | 0x0E                                                                                                                                                                                                                                                             |                              |            | ID5      | ID4      | ID3     | ID2    | ID1       | ID0      |  |

| Mast     | *Note: These registers are used in both master and slave mode. The register bits marked with (m) are accessible only in Master mode while the register bits marked with (s) are accessible only in slave mode. All other registers are accessible in both modes. |                              |            |          |          |         |        |           |          |  |

### Table 20.4. LIN Registers\* (Indirectly Addressable)

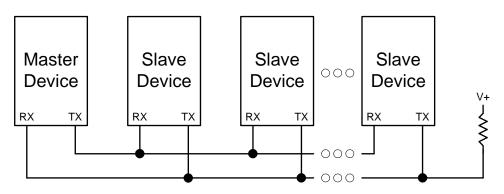

#### 23.3.3. Multiprocessor Communications

UART0 supports multiprocessor communication between a master processor and one or more slave processors by special use of the extra data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its extra bit is logic 1; in a data byte, the extra bit is always set to logic 0.

Setting the MCE0 bit (SMOD0.7) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the extra bit is logic 1 (RBX0 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned address. If the addresses match, the slave will clear its MCE0 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0 bits set and do not generate interrupts on the reception of the following data byte(s) bits of the following data bytes, thereby ignoring the data. Once the entire message is received, the addressed slave resets its MCE0 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 23.6. UART Multi-Processor Mode Interconnect Diagram

| System Clock (Hz)                                                                                                                                                                                                 | PCA0CPL5 | Timeout Interval (ms) |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------|--|--|--|--|--|

| 24,000,000                                                                                                                                                                                                        | 255      | 32.8                  |  |  |  |  |  |

| 24,000,000                                                                                                                                                                                                        | 128      | 16.5                  |  |  |  |  |  |

| 24,000,000                                                                                                                                                                                                        | 32       | 4.2                   |  |  |  |  |  |

| 3,000,000                                                                                                                                                                                                         | 255      | 262.1                 |  |  |  |  |  |

| 3,000,000                                                                                                                                                                                                         | 128      | 132.1                 |  |  |  |  |  |

| 3,000,000                                                                                                                                                                                                         | 32       | 33.8                  |  |  |  |  |  |

| 187,500 <sup>2</sup>                                                                                                                                                                                              | 255      | 4194                  |  |  |  |  |  |

| 187,500 <sup>2</sup>                                                                                                                                                                                              | 128      | 2114                  |  |  |  |  |  |

| 187,500 <sup>2</sup>                                                                                                                                                                                              | 32       | 541                   |  |  |  |  |  |

| <ul> <li>Notes:</li> <li>1. Assumes SYSCLK/12 as the PCA clock source, and a PCA0L value of 0x00 at the update time.</li> <li>2. Internal SYSCLK reset frequency = Internal Oscillator divided by 128.</li> </ul> |          |                       |  |  |  |  |  |

## Table 26.3. Watchdog Timer Timeout Intervals<sup>1</sup>

SILICON LABS

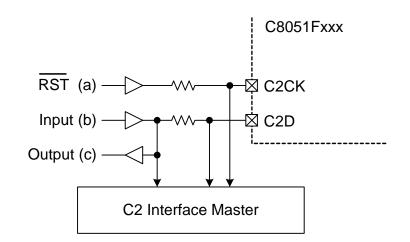

### 27.2. C2 Pin Sharing

The C2 protocol allows the C2 pins to be shared with user functions so that in-system debugging and Flash programming may be performed. This is possible because C2 communication is typically performed when the device is in the halt state, where all on-chip peripherals and user software are stalled. In this halted state, the C2 interface can safely 'borrow' the C2CK (RST) and C2D pins. In most applications, external resistors are required to isolate C2 interface traffic from the user application. A typical isolation configuration is shown in Figure 27.1.

Figure 27.1. Typical C2 Pin Sharing

The configuration in Figure 27.1 assumes the following:

- 1. The user input (b) cannot change state while the target device is halted.

- 2. The  $\overline{\text{RST}}$  pin on the target device is used as an input only.

Additional resistors may be necessary depending on the specific application.

303

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

http://www.silabs.com