# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART       |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 33                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 2.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | A/D 32x12b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                              |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 40-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 40-QFN (6x6)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f575-imr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 25.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)             | 263 |

|-------|---------------------------------------------------------------------|-----|

| 25    | 5.2. Timer 2                                                        | 269 |

|       | 25.2.1. 16-bit Timer with Auto-Reload                               | 269 |

|       | 25.2.2. 8-bit Timers with Auto-Reload                               | 269 |

|       | 25.2.3. External Oscillator Capture Mode                            | 270 |

| 25    | 5.3. Timer 3                                                        |     |

|       | 25.3.1. 16-Bit Timer with Auto-Reload                               |     |

|       | 25.3.2. 8-Bit Timers with Auto-Reload                               | 275 |

|       | 25.3.3. External Oscillator Capture Mode                            |     |

| 26. P | rogrammable Counter Array.                                          |     |

| 26    | 6.1. PCA Counter/Timer                                              | 282 |

| 26    | 6.2. PCA0 Interrupt Sources                                         | 283 |

| 26    | 6.3. Capture/Compare Modules                                        | 283 |

|       | 26.3.1. Edge-triggered Capture Mode                                 | 284 |

|       | 26.3.2. Software Timer (Compare) Mode                               | 285 |

|       | 26.3.3. High-Speed Output Mode                                      | 286 |

|       | 26.3.4. Frequency Output Mode                                       | 287 |

|       | 26.3.5. 8-bit, 9-bit, 10-bit and 11-bit Pulse Width Modulator Modes | 288 |

|       | 26.3.6. 16-Bit Pulse Width Modulator Mode                           |     |

| 26    | 6.4. Watchdog Timer Mode                                            | 291 |

|       | 26.4.1. Watchdog Timer Operation                                    |     |

|       | 26.4.2. Watchdog Timer Usage                                        | 292 |

| 26    | 6.5. Register Descriptions for PCA0                                 | 294 |

| 27. C | 2 Interface                                                         | 300 |

| 27    | 7.1. C2 Interface Registers                                         | 300 |

| 27    | 7.2. C2 Pin Sharing                                                 | 303 |

Figure 1.3. C8051F550-7 (24-pin) Block Diagram

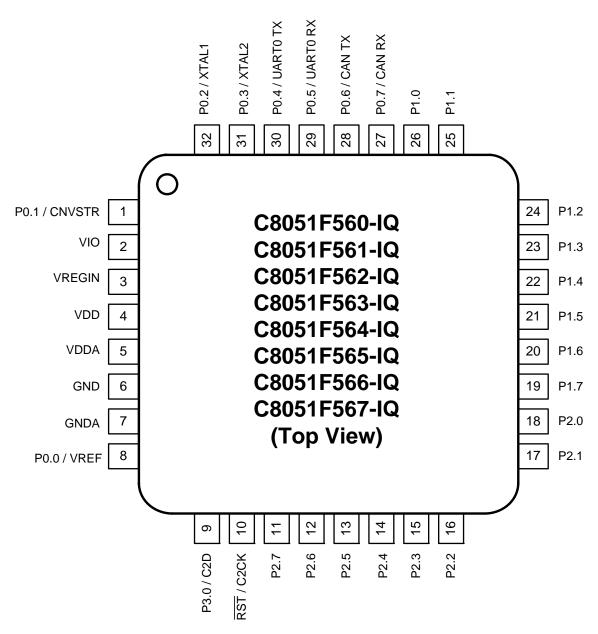

Figure 3.2. QFP-32 Pinout Diagram (Top View)

#### Table 5.3. Port I/O DC Electrical Characteristics

$V_{DD}$  = 1.8 to 2.75 V, –40 to +125 °C unless otherwise specified.

| Parameters          | Conditions                                   | Min                    | Тур                   | Max       | Units |

|---------------------|----------------------------------------------|------------------------|-----------------------|-----------|-------|

| Output High Voltage | I <sub>OH</sub> = –3 mA, Port I/O push-pull  | V <sub>IO</sub> – 0.4  | —                     | _         | V     |

|                     | I <sub>OH</sub> = −10 μA, Port I/O push-pull | V <sub>IO</sub> – 0.02 | —                     | —         |       |

|                     | I <sub>OH</sub> = –10 mA, Port I/O push-pull | —                      | V <sub>IO</sub> – 0.7 | —         |       |

| Output Low Voltage  | V <sub>IO</sub> = 1.8 V:                     |                        |                       |           |       |

|                     | I <sub>OL</sub> = 70 μA                      | —                      | —                     | 50        |       |

|                     | I <sub>OL</sub> = 8.5 mA                     | —                      | —                     | 750       |       |

|                     | V <sub>IO</sub> = 2.7 V:                     |                        |                       |           |       |

|                     | I <sub>OL</sub> = 70 μA                      | —                      | —                     | 45        | mV    |

|                     | I <sub>OL</sub> = 8.5 mA                     | —                      | —                     | 550       |       |

|                     | V <sub>IO</sub> = 5.25 V:                    |                        |                       |           |       |

|                     | I <sub>OL</sub> = 70 μA                      | —                      | —                     | 40        |       |

|                     | I <sub>OL</sub> = 8.5 mA                     |                        | —                     | 400       |       |

| Input High Voltage  | V <sub>REGIN</sub> = 5.25 V                  | 0.7 x VIO              | —                     |           | V     |

| Input Low Voltage   | V <sub>REGIN</sub> = 2.7 V                   | —                      | _                     | 0.3 x VIO | V     |

|                     | Weak Pullup Off                              | —                      | —                     | ±2        |       |

|                     | Weak Pullup On, V <sub>IO</sub> = 2.1 V,     |                        |                       |           |       |

|                     | $V_{IN} = 0 V, V_{DD} = 1.8 V$               |                        | 7                     | 9         |       |

| Input Leakage       | Weak Pullup On, $V_{IO} = 2.6$ V,            |                        |                       | Ū.        | μA    |

| Current             |                                              |                        | 47                    |           | μΛ    |

|                     | $V_{IN} = 0 V, V_{DD} = 2.6 V$               | —                      | 17                    | 22        |       |

|                     | Weak Pullup On, V <sub>IO</sub> = 5.0 V,     |                        |                       |           |       |

|                     | $V_{IN} = 0 V, V_{DD} = 2.6 V$               | —                      | 49                    | 115       |       |

### 6.2. Output Code Formatting

The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code. When the repeat count is set to 1, conversion codes are represented in 12-bit unsigned integer format and the output conversion code is updated after each conversion. Inputs are measured from 0 to  $V_{REF} \times 4095/4096$ . Data can be right-justified or left-justified, depending on the setting of the AD0LJST bit (ADC0CN.2). Unused bits in the ADC0H and ADC0L registers are set to 0. Example codes are shown below for both right-justified and left-justified data.

| Input Voltage    | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|------------------|----------------------------------------------|---------------------------------------------|

| VREF x 4095/4096 | 0x0FFF                                       | 0xFFF0                                      |

| VREF x 2048/4096 | 0x0800                                       | 0x8000                                      |

| VREF x 2047/4096 | 0x07FF                                       | 0x7FF0                                      |

| 0                | 0x0000                                       | 0x0000                                      |

When the ADC0 Repeat Count is greater than 1, the output conversion code represents the accumulated result of the conversions performed and is updated after the last conversion in the series is finished. Sets of 4, 8, or 16 consecutive samples can be accumulated and represented in unsigned integer format. The repeat count can be selected using the AD0RPT bits in the ADC0CF register. The value must be right-justified (AD0LJST = 0), and unused bits in the ADC0H and ADC0L registers are set to 0. The following example shows right-justified codes for repeat counts greater than 1. Notice that accumulating  $2^n$  samples is equivalent to left-shifting by *n* bit positions when all samples returned from the ADC have the same value.

| Input Voltage                | Repeat Count = 4 | Repeat Count = 8 | Repeat Count = 16 |

|------------------------------|------------------|------------------|-------------------|

| V <sub>REF</sub> x 4095/4096 | 0x3FFC           | 0x7FF8           | 0xFFF0            |

| V <sub>REF</sub> x 2048/4096 | 0x2000           | 0x4000           | 0x8000            |

| V <sub>REF</sub> x 2047/4096 | 0x1FFC           | 0x3FF8           | 0x7FF0            |

| 0                            | 0x0000           | 0x0000           | 0x0000            |

#### 6.2.1. Settling Time Requirements

A minimum tracking time is required before an accurate conversion is performed. This tracking time is determined by any series impedance, including the AMUX0 resistance, the ADC0 sampling capacitance, and the accuracy required for the conversion.

Figure 6.5 shows the equivalent ADC0 input circuit. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 6.1. When measuring the Temperature Sensor output, use the settling time specified in Table 5.10. When measuring V<sub>DD</sub> with respect to GND,  $R_{TOTAL}$  reduces to  $R_{MUX}$ . See Table 5.9 for ADC0 minimum settling time requirements as well as the mux impedance and sampling capacitor values.

$$t = ln\left(\frac{2^{n}}{SA}\right) \times R_{TOTAL}C_{SAMPLE}$$

#### **Equation 6.1. ADC0 Settling Time Requirements**

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB). *t* is the required settling time in seconds.  $R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance. *n* is the ADC resolution in bits (10).

## Gain Register Definition 6.1. ADC0GNH: ADC0 Selectable Gain High Byte

| Bit    | 7               | 6                                                                         | 5               | 4            | 3               | 2               | 1       | 0 |  |

|--------|-----------------|---------------------------------------------------------------------------|-----------------|--------------|-----------------|-----------------|---------|---|--|

| Nam    | e               | GAINH[7:0]                                                                |                 |              |                 |                 |         |   |  |

| Тур    | e               | W                                                                         |                 |              |                 |                 |         |   |  |

| Rese   | et 1            | 1                                                                         | 1               | 1            | 1               | 1               | 0       | 0 |  |

| Indire | ct Address = (  | 0x04;                                                                     |                 |              |                 |                 |         |   |  |

| Bit    | Name            | Name Function                                                             |                 |              |                 |                 |         |   |  |

| 7:0    | GAINH[7:0]      | IH[7:0] ADC0 Gain High Byte.                                              |                 |              |                 |                 |         |   |  |

|        |                 | See Section 6.3.1 for details on calculating the value for this register. |                 |              |                 |                 |         |   |  |

| Note:  | This register i | s accessed ind                                                            | lirectly; See S | ection 6.3.2 | for details for | writing this re | gister. |   |  |

#### Gain Register Definition 6.2. ADC0GNL: ADC0 Selectable Gain Low Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2        | 1        | 0        |

|-------|---|------------|---|---|---|----------|----------|----------|

| Name  |   | GAINL[3:0] |   |   |   | Reserved | Reserved | Reserved |

| Туре  |   | W          |   |   |   | W        | W        | W        |

| Reset | 0 | 0          | 0 | 0 | 0 | 0        | 0        | 0        |

Indirect Address = 0x07;

| Bit   | Name             | Function                                                                        |

|-------|------------------|---------------------------------------------------------------------------------|

| 7:4   | GAINL[3:0]       | ADC0 Gain Lower 4 Bits.                                                         |

|       |                  | See Figure 6.3.1 for details for setting this register.                         |

|       |                  | This register is only accessed indirectly through the ADC0H and ADC0L register. |

| 3:0   | Reserved         | Must Write 0000b                                                                |

| Note: | This register is | s accessed indirectly; See Section 6.3.2 for details for writing this register. |

## SFR Definition 8.2. CPT0MD: Comparator0 Mode Selection

| Bit   | 7 | 6 | 5      | 4      | 3 | 2 | 1    | 0      |

|-------|---|---|--------|--------|---|---|------|--------|

| Name  |   |   | CP0RIE | CP0FIE |   |   | CP0M | D[1:0] |

| Туре  | R | R | R/W    | R/W    | R | R | R/W  |        |

| Reset | 0 | 0 | 0      | 0      | 0 | 0 | 1    | 0      |

#### SFR Address = 0x9B; SFR Page = 0x00

| Bit | Name       | Function                                                                   |

|-----|------------|----------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b, Write = Don't Care.                                            |

| 5   | CP0RIE     | Comparator0 Rising-Edge Interrupt Enable.                                  |

|     |            | 0: Comparator0 Rising-edge interrupt disabled.                             |

|     |            | 1: Comparator0 Rising-edge interrupt enabled.                              |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.                                 |

|     |            | 0: Comparator0 Falling-edge interrupt disabled.                            |

|     |            | 1: Comparator0 Falling-edge interrupt enabled.                             |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                            |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select.                                                   |

|     |            | These bits affect the response time and power consumption for Comparator0. |

|     |            | 00: Mode 0 (Fastest Response Time, Highest Power Consumption)              |

|     |            | 01: Mode 1                                                                 |

|     |            | 10: Mode 2                                                                 |

|     |            | 11: Mode 3 (Slowest Response Time, Lowest Power Consumption)               |

## 10. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware (see description in Section 27), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 10.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 50 MIPS Peak Throughput with 50 MHz Clock

- 0 to 50 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

#### 10.1. Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

#### SFR Definition 10.1. DPL: Data Pointer Low Byte

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----------|---|---|---|---|---|---|---|

| Name  | DPL[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W      |   |   |   |   |   |   |   |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0x82; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                    |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------|

| 7:0 | DPL[7:0] | Data Pointer Low.                                                                                                           |

|     |          | The DPL register is the low byte of the 16-bit DPTR. DPTR is used to access indi-<br>rectly addressed Flash memory or XRAM. |

## SFR Definition 10.2. DPH: Data Pointer High Byte

| Bit   | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|----------|---|---|---|---|---|---|

| Name  |   | DPH[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W      |   |   |   |   |   |   |

| Reset | 0 | 0        | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0x83; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                     |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | DPH[7:0] | Data Pointer High.                                                                                                           |

|     |          | The DPH register is the high byte of the 16-bit DPTR. DPTR is used to access indi-<br>rectly addressed Flash memory or XRAM. |

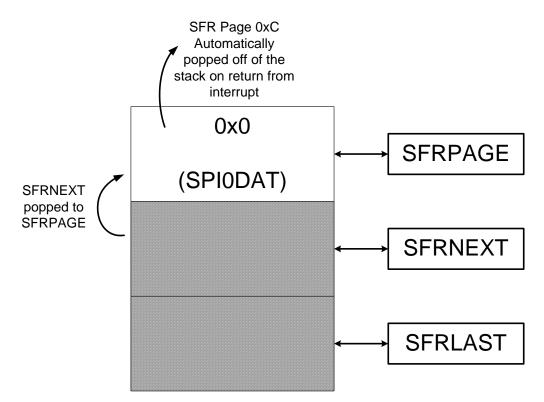

On the execution of the RETI instruction in the CAN0 ISR, the value in SFRPAGE register is overwritten with the contents of SFRNEXT. The CIP-51 may now access the SPI0DAT register as it did prior to the interrupts occurring. See Figure 12.6.

Figure 12.6. SFR Page Stack Upon Return From CAN0 Interrupt

In the example above, all three bytes in the SFR Page Stack are accessible via the SFRPAGE, SFRNEXT, and SFRLAST special function registers. If the stack is altered while servicing an interrupt, it is possible to return to a different SFR Page upon interrupt exit than selected prior to the interrupt call. Direct access to the SFR Page stack can be useful to enable real-time operating systems to control and manage context switching between multiple tasks.

Push operations on the SFR Page Stack only occur on interrupt service, and pop operations only occur on interrupt exit (execution on the RETI instruction). The automatic switching of the SFRPAGE and operation of the SFR Page Stack as described above can be disabled in software by clearing the SFR Automatic Page Enable Bit (SFRPGEN) in the SFR Page Control Register (SFR0CN). See SFR Definition 12.1.

### Table 12.3. Special Function Registers

| SFRs are listed in alphabetica | I order. All undefined SFR locations are reserved |

|--------------------------------|---------------------------------------------------|

|                                |                                                   |

| Register | Address | Description                              | Page |  |  |

|----------|---------|------------------------------------------|------|--|--|

| ACC      | 0xE0    | Accumulator                              | 89   |  |  |

| ADC0CF   | 0xBC    | ADC0 Configuration                       | 58   |  |  |

| ADC0CN   | 0xE8    | ADC0 Control                             | 60   |  |  |

| ADC0GTH  | 0xC4    | ADC0 Greater-Than Compare High           | 62   |  |  |

| ADC0GTL  | 0xC3    | ADC0 Greater-Than Compare Low            | 62   |  |  |

| ADC0H    | 0xBE    | ADC0 High                                | 59   |  |  |

| ADC0L    | 0xBD    | ADC0 Low                                 | 59   |  |  |

| ADC0LTH  | 0xC6    | ADC0 Less-Than Compare Word High         | 63   |  |  |

| ADC0LTL  | 0xC5    | ADC0 Less-Than Compare Word Low          | 63   |  |  |

| ADCOMX   | 0xBB    | ADC0 Mux Configuration                   | 66   |  |  |

| ADC0TK   | 0xBA    | ADC0 Tracking Mode Select                | 61   |  |  |

| В        | 0xF0    | B Register                               | 89   |  |  |

| CCH0CN   | 0xE3    | Cache Control                            | 134  |  |  |

| CKCON    | 0x8E    | Clock Control                            | 260  |  |  |

| CLKMUL   | 0x97    | Clock Multiplier                         | 163  |  |  |

| CLKSEL   | 0x8F    | Clock Select                             | 158  |  |  |

| CPT0CN   | 0x9A    | Comparator0 Control                      | 72   |  |  |

| CPT0MD   | 0x9B    | Comparator0 Mode Selection               | 73   |  |  |

| CPT0MX   | 0x9C    | Comparator0 MUX Selection                | 77   |  |  |

| CPT1CN   | 0x9D    | Comparator1 Control                      | 72   |  |  |

| CPT1MD   | 0x9E    | Comparator1 Mode Selection               | 73   |  |  |

| CPT1MX   | 0x9F    | Comparator1 MUX Selection                | 77   |  |  |

| DPH      | 0x83    | Data Pointer High                        | 88   |  |  |

| DPL      | 0x82    | Data Pointer Low                         | 88   |  |  |

| EIE1     | 0xE6    | Extended Interrupt Enable 1              | 118  |  |  |

| EIE2     | 0xE7    | Extended Interrupt Enable 2              | 118  |  |  |

| EIP1     | 0xF6    | Extended Interrupt Priority 1            | 119  |  |  |

| EIP2     | 0xF7    | Extended Interrupt Priority 2            | 120  |  |  |

| EMI0CF   | 0xB2    | External Memory Interface Configuration  | 148  |  |  |

| EMI0CN   | 0xAA    | External Memory Interface Control        | 147  |  |  |

| EMI0TC   | 0xAA    | External Memory Interface Timing Control | 152  |  |  |

| FLKEY    | 0xB7    | Flash Lock and Key                       |      |  |  |

| FLSCL    | 0xB6    | Flash Scale                              | 133  |  |  |

| IE       | 0xA8    | Interrupt Enable                         | 116  |  |  |

| IP       | 0xB8    | Interrupt Priority                       | 117  |  |  |

### 13.2. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described in this section. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

## SFR Definition 15.1. PCON: Power Control

| Bit   | 7       | 6       | 5 | 4 | 3 | 2 | 1    | 0    |

|-------|---------|---------|---|---|---|---|------|------|

| Name  | GF[5:0] |         |   |   |   |   | STOP | IDLE |

| Туре  |         | R/W R/W |   |   |   |   |      |      |

| Reset | 0       | 0       | 0 | 0 | 0 | 0 | 0    | 0    |

SFR Address = 0x87; SFR Page = All Pages

| Bit | Name    | Function                                                                                                                                                                                                                                                               |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | GF[5:0] | General Purpose Flags 5–0.                                                                                                                                                                                                                                             |

|     |         | These are general purpose flags for use under software control.                                                                                                                                                                                                        |

| 1   | STOP    | <ul><li>Stop Mode Select.</li><li>Setting this bit will place the CIP-51 in Stop mode. This bit will always be read as 0.</li><li>1: CPU goes into Stop mode (internal oscillator stopped).</li></ul>                                                                  |

| 0   | IDLE    | IDLE: Idle Mode Select.<br>Setting this bit will place the CIP-51 in Idle mode. This bit will always be read as 0.<br>1: CPU goes into Idle mode. (Shuts off clock to CPU, but clock to Timers, Interrupts,<br>Serial Ports, and Analog Peripherals are still active.) |

## 17. External Data Memory Interface and On-Chip XRAM

For C8051F55x/56x/57x devices, 2 kB of RAM are included on-chip and mapped into the external data memory space (XRAM). Additionally, an External Memory Interface (EMIF) is available on the C8051F568-9 and 'F570-5 devices, which can be used to access off-chip data memories and memory-mapped devices connected to the GPIO ports. The external memory space may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using the MOVX indirect addressing mode using R0 or R1. If the MOVX instruction is used with an 8-bit address operand (such as @R1), then the high byte of the 16-bit address is provided by the External Memory Interface Control Register (EMIOCN, shown in SFR Definition 17.1).

**Note:** The MOVX instruction can also be used for writing to the Flash memory. See Section "14. Flash Memory" on page 124 for details. The MOVX instruction accesses XRAM by default.

#### 17.1. Accessing XRAM

The XRAM memory space is accessed using the MOVX instruction. The MOVX instruction has two forms, both of which use an indirect addressing method. The first method uses the Data Pointer, DPTR, a 16-bit register which contains the effective address of the XRAM location to be read from or written to. The second method uses R0 or R1 in combination with the EMI0CN register to generate the effective XRAM address. Examples of both of these methods are given below.

#### 17.1.1. 16-Bit MOVX Example

The 16-bit form of the MOVX instruction accesses the memory location pointed to by the contents of the DPTR register. The following series of instructions reads the value of the byte at address 0x1234 into the accumulator A:

MOVDPTR, #1234h; load DPTR with 16-bit address to read (0x1234)MOVXA, @DPTR; load contents of 0x1234 into accumulator A

The above example uses the 16-bit immediate MOV instruction to set the contents of DPTR. Alternately, the DPTR can be accessed through the SFR registers DPH, which contains the upper 8-bits of DPTR, and DPL, which contains the lower 8-bits of DPTR.

#### 17.1.2. 8-Bit MOVX Example

The 8-bit form of the MOVX instruction uses the contents of the EMI0CN SFR to determine the upper 8-bits of the effective address to be accessed and the contents of R0 or R1 to determine the lower 8-bits of the effective address to be accessed. The following series of instructions read the contents of the byte at address 0x1234 into the accumulator A.

| MOV  | EMIOCN, #12h | ; load high byte of address into EMIOCN      |

|------|--------------|----------------------------------------------|

| MOV  | R0, #34h     | ; load low byte of address into R0 (or R1)   |

| MOVX | a, @R0       | ; load contents of 0x1234 into accumulator A |

## SFR Definition 19.2. XBR1: Port I/O Crossbar Register 1

| Bit   | 7   | 6   | 5    | 4           | 3   | 2 | 1      | 0        |

|-------|-----|-----|------|-------------|-----|---|--------|----------|

|       | •   | -   | _    | -           | 0   | - | •      |          |

| Name  | T1E | T0E | ECIE | PCA0ME[2:0] |     |   | SYSCKE | Reserved |

| Туре  | R/W | R/W | R/W  | R/W         | R/W | R | R/W    | R/W      |

| Type  |     |     |      |             |     |   |        | -        |

| Reset | 0   | 0   | 0    | 0           | 0   | 0 | 0      | 0        |

|       |     |     |      |             |     |   |        |          |

#### SFR Address = 0xE2; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | T1E         | <b>T1 Enable.</b><br>0: T1 unavailable at Port pin.<br>1: T1 routed to Port pin.                                                                                                                                                                                                                                                                                                                                                                                    |

| 6   | TOE         | <b>T0 Enable.</b><br>0: T0 unavailable at Port pin.<br>1: T0 routed to Port pin.                                                                                                                                                                                                                                                                                                                                                                                    |

| 5   | ECIE        | PCA0 External Counter Input Enable.<br>0: ECI unavailable at Port pin.<br>1: ECI routed to Port pin.                                                                                                                                                                                                                                                                                                                                                                |

| 4:2 | PCA0ME[2:0] | <ul> <li>PCA Module I/O Enable Bits.</li> <li>000: All PCA I/O unavailable at Port pins.</li> <li>001: CEX0 routed to Port pin.</li> <li>010: CEX0, CEX1 routed to Port pins.</li> <li>011: CEX0, CEX1, CEX2 routed to Port pins.</li> <li>100: CEX0, CEX1, CEX2, CEX3 routed to Port pins.</li> <li>101: CEX0, CEX1, CEX2, CEX3, CEX4 routed to Port pins.</li> <li>110: CEX0, CEX1, CEX2, CEX3, CEX4, CEX5 routed to Port pins.</li> <li>111: RESERVED</li> </ul> |

| 1   | SYSCKE      | /SYSCLK Output Enable.<br>0: /SYSCLK unavailable at Port pin.<br>1: /SYSCLK output routed to Port pin.                                                                                                                                                                                                                                                                                                                                                              |

| 0   | Reserved    | Always Write to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### LIN Register Definition 20.6. LIN0ST: LIN0 Status Register

| Bit   | 7      | 6       | 5     | 4     | 3      | 2     | 1      | 0    |

|-------|--------|---------|-------|-------|--------|-------|--------|------|

| Name  | ACTIVE | IDLTOUT | ABORT | DTREQ | LININT | ERROR | WAKEUP | DONE |

| Туре  | R      | R       | R     | R     | R      | R     | R      | R    |

| Reset | 0      | 0       | 0     | 0     | 0      | 0     | 0      | 0    |

#### Indirect Address = 0x09

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                          |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ACTIVE | LIN Active Indicator Bit.                                                                                                                                                                                                                                                                                         |

|     |        | 0: No transmission activity detected on the LIN bus.                                                                                                                                                                                                                                                              |

|     |        | 1: Transmission activity detected on the LIN bus.                                                                                                                                                                                                                                                                 |

| 6   | IDLT   | Bus Idle Timeout Bit. (slave mode only)                                                                                                                                                                                                                                                                           |

|     |        | 0: The bus has not been idle for four seconds.                                                                                                                                                                                                                                                                    |

|     |        | 1: No bus activity has been detected for four seconds, but the bus is not yet in Sleep mode.                                                                                                                                                                                                                      |

| 5   | ABORT  | Aborted Transmission Bit. (slave mode only)                                                                                                                                                                                                                                                                       |

|     |        | <ul> <li>0: The current transmission has not been interrupted or stopped. This bit is reset to 0 after receiving a SYNCH BREAK that does not interrupt a pending transmission.</li> <li>1: New SYNCH BREAK detected before the end of the last transmission or the STOP bit (LIN0CTRL.7) has been set.</li> </ul> |

| 4   | DTREQ  | Data Request Bit. (slave mode only)                                                                                                                                                                                                                                                                               |

|     |        | 0: Data identifier has not been received.                                                                                                                                                                                                                                                                         |

|     |        | 1: Data identifier has been received.                                                                                                                                                                                                                                                                             |

| 3   | LININT | Interrupt Request Bit.                                                                                                                                                                                                                                                                                            |

|     |        | <ul><li>0: An interrupt is not pending. This bit is cleared by setting RSTINT (LINOCTRL.3)</li><li>1: There is a pending LIN0 interrupt.</li></ul>                                                                                                                                                                |

| 2   | ERROR  | Communication Error Bit.                                                                                                                                                                                                                                                                                          |

|     |        | <ul><li>0: No error has been detected. This bit is cleared by setting RSTERR (LIN0CTRL.2)</li><li>1: An error has been detected.</li></ul>                                                                                                                                                                        |

| 1   | WAKEUP | Wakeup Bit.                                                                                                                                                                                                                                                                                                       |

|     |        | <ul><li>0: A wakeup signal is not being transmitted and has not been received.</li><li>1: A wakeup signal is being transmitted or has been received</li></ul>                                                                                                                                                     |

| 0   | DONE   | Transmission Complete Bit.                                                                                                                                                                                                                                                                                        |

|     |        | 0: A transmission is not in progress or has not been started. This bit is cleared at the                                                                                                                                                                                                                          |

|     |        | start of a transmission.<br>1: The current transmission is complete.                                                                                                                                                                                                                                              |

|     |        |                                                                                                                                                                                                                                                                                                                   |

| Bit   | 7    | 6     | 5     | 4    | 3    | 2    | 1   | 0   |

|-------|------|-------|-------|------|------|------|-----|-----|

| Name  | OVR0 | PERR0 | THRE0 | REN0 | TBX0 | RBX0 | TI0 | RI0 |

| Туре  | R/W  | R/W   | R     | R/W  | R/W  | R/W  | R/W | R/W |

| Reset | 0    | 0     | 1     | 0    | 0    | 0    | 0   | 0   |

### 24.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. Note that the NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 24.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPI0 with the SPIEN bit. Figure 24.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

#### 24.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- 1. The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- 2. The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- 3. The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- 4. The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

#### 25.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

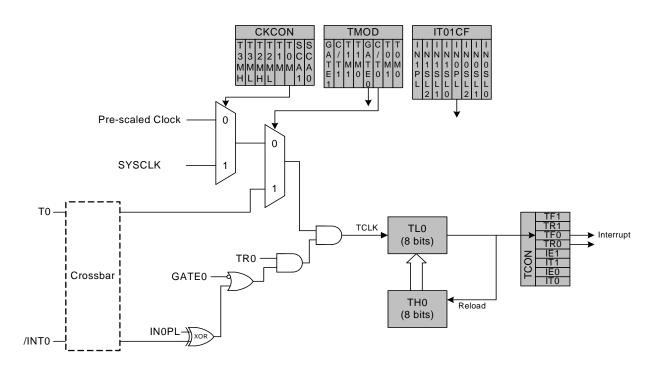

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and/or UART, and/or initiate ADC conversions. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

## SFR Definition 25.14. TMR3RLL: Timer 3 Reload Register Low Byte

| Bit                                 | 7    | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------------------------------------|------|--------------|---|---|---|---|---|---|--|

| Nam                                 | e    | TMR3RLL[7:0] |   |   |   |   |   |   |  |

| Туре                                | )    | R/W          |   |   |   |   |   |   |  |

| Rese                                | et 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |  |

| SFR Address = 0x92; SFR Page = 0x00 |      |              |   |   |   |   |   |   |  |

| Bit                                 | Name | Function     |   |   |   |   |   |   |  |

| ы   | Name         | Function                                                    |  |  |  |

|-----|--------------|-------------------------------------------------------------|--|--|--|

| 7:0 | TMR3RLL[7:0] | Timer 3 Reload Register Low Byte.                           |  |  |  |

|     |              | TMR3RLL holds the low byte of the reload value for Timer 3. |  |  |  |

### SFR Definition 25.15. TMR3RLH: Timer 3 Reload Register High Byte

| Bit   | 7              | 6                                                            | 5                 | 4 | 3 | 2 | 1 | 0 |

|-------|----------------|--------------------------------------------------------------|-------------------|---|---|---|---|---|

| Nam   | e              | TMR3RLH[7:0]                                                 |                   |   |   |   |   |   |

| Туре  | R/W            |                                                              |                   |   |   |   |   |   |

| Rese  | et 0           | 0                                                            | 0                 | 0 | 0 | 0 | 0 | 0 |

| SFR A | Address = 0x93 | 3; SFR Page                                                  | $e = 0 \times 00$ |   |   |   |   |   |

| Bit   | Name           |                                                              | Function          |   |   |   |   |   |

| 7:0   | TMR3RLH[7:0    | MR3RLH[7:0] Timer 3 Reload Register High Byte.               |                   |   |   |   |   |   |

|       |                | TMR3RLH holds the high byte of the reload value for Timer 3. |                   |   |   |   |   |   |