# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 400MHz                                                                 |

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (3)                                                    |

| SATA                            | -                                                                      |

| USB                             | USB 2.0 + PHY (2)                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                     |

| Security Features               | -                                                                      |

| Package / Case                  | 620-BBGA Exposed Pad                                                   |

| Supplier Device Package         | 620-HBGA (29x29)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8343czqagd |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### NOTE

The information in this document is accurate for revision 3.x silicon and later (in other words, for orderable part numbers ending in A or B). For information on revision 1.1 silicon and earlier versions, see the *MPC8343E PowerQUICC II Pro Integrated Host Processor Hardware Specifications*.

See Section 22.1, "Part Numbers Fully Addressed by This Document," for silicon revision level determination.

## 1 Overview

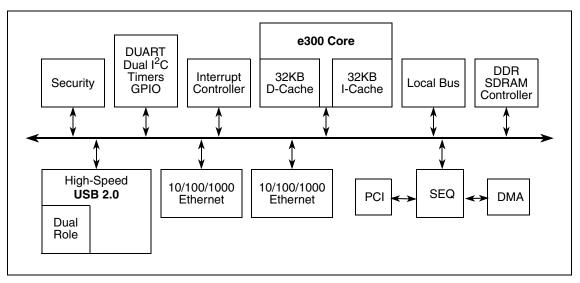

This section provides a high-level overview of the device features. Figure 1 shows the major functional units within the MPC8343EA.

Figure 1. MPC8343EA Block Diagram

Major features of the device are as follows:

- Embedded PowerPC e300 processor core; operates at up to 400 MHz

- High-performance, superscalar processor core

- Floating-point, integer, load/store, system register, and branch processing units

- 32-Kbyte instruction cache, 32-Kbyte data cache

- Lockable portion of L1 cache

- Dynamic power management

- Software-compatible with the other Freescale processor families that implement Power Architecture technology

- Double data rate, DDR1/DDR2 SDRAM memory controller

- Programmable timing supporting DDR1 and DDR2 SDRAM

- 32- bit data interface, up to 266 MHz data rate

Overview

- Address translation units for address mapping between host and peripheral

- Dual address cycle for target

- Internal configuration registers accessible from PCI

- Security engine is optimized to handle all the algorithms associated with IPSec, SSL/TLS, SRTP, IEEE Std. 802.11i<sup>®</sup>, iSCSI, and IKE processing. The security engine contains four crypto-channels, a controller, and a set of crypto execution units (EUs):

- Public key execution unit (PKEU) :

- RSA and Diffie-Hellman algorithms

- Programmable field size up to 2048 bits

- Elliptic curve cryptography

- F2m and F(p) modes

- Programmable field size up to 511 bits

- Data encryption standard (DES) execution unit (DEU)

- DES and 3DES algorithms

- Two key (K1, K2) or three key (K1, K2, K3) for 3DES

- ECB and CBC modes for both DES and 3DES

- Advanced encryption standard unit (AESU)

- Implements the Rijndael symmetric-key cipher

- Key lengths of 128, 192, and 256 bits

- ECB, CBC, CCM, and counter (CTR) modes

- XOR parity generation accelerator for RAID applications

- ARC four execution unit (AFEU)

- Stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- Message digest execution unit (MDEU)

- SHA with 160-, 224-, or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either algorithm

- Random number generator (RNG)

- Four crypto-channels, each supporting multi-command descriptor chains

- Static and/or dynamic assignment of crypto-execution units through an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- Universal serial bus (USB) dual role controller

- USB on-the-go mode with both device and host functionality

- Complies with USB specification Rev. 2.0

- Can operate as a stand-alone USB device

- One upstream facing port

- Six programmable USB endpoints

### Table 8. EC\_GTX\_CLK125 AC Timing Specifications

At recommended operating conditions with  $LV_{DD}$  = 2.5 ± 0.125 mV/ 3.3 V ± 165 mV (continued)

| Parameter                                                           | Symbol | Min      | Typical | Max      | Unit | Notes |

|---------------------------------------------------------------------|--------|----------|---------|----------|------|-------|

| EC_GTX_CLK125 duty cycle<br>GMII, TBI<br>1000Base-T for RGMII, RTBI |        | 45<br>47 | _       | 55<br>53 | %    | 2     |

| EC_GTX_CLK125 jitter                                                |        | —        | _       | ±150     | ps   | 2     |

### Notes:

- 1. Rise and fall times for EC\_GTX\_CLK125 are measured from 0.5 and 2.0 V for  $LV_{DD}$  = 2.5 V and from 0.6 and 2.7 V for  $LV_{DD}$  = 3.3 V.

- 2. EC\_GTX\_CLK125 is used to generate the GTX clock for the eTSEC transmitter with 2% degradation. The EC\_GTX\_CLK125 duty cycle can be loosened from 47%/53% as long as the PHY device can tolerate the duty cycle generated by the eTSEC GTX\_CLK. See Section 8.2.2, "RGMII and RTBI AC Timing Specifications for the duty cycle for 10Base-T and 100Base-T reference clock.

## 5 **RESET Initialization**

This section describes the DC and AC electrical specifications for the reset initialization timing and electrical requirements of the MPC8343EA.

## 5.1 **RESET DC Electrical Characteristics**

Table 9 provides the DC electrical characteristics for the RESET pins of the MPC8343EA.

| Parameter                        | Symbol          | Condition                 | Min  | Мах                    | Unit |

|----------------------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage               | V <sub>IH</sub> | —                         | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage                | V <sub>IL</sub> | —                         | -0.3 | 0.8                    | V    |

| Input current                    | I <sub>IN</sub> | _                         | _    | ±5                     | μA   |

| Output high voltage <sup>2</sup> | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —                      | V    |

| Output low voltage               | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | _    | 0.5                    | V    |

| Output low voltage               | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | —    | 0.4                    | V    |

### Table 9. RESET Pins DC Electrical Characteristics<sup>1</sup>

Notes:

1. This table applies for pins PORESET, HRESET, SRESET, and QUIESCE.

2. HRESET and SRESET are open drain pins, thus V<sub>OH</sub> is not relevant for those pins.

#### DDR and DDR2 SDRAM

### Table 13 provides the DDR2 capacitance when $GV_{DD}(typ) = 1.8$ V.

### Table 13. DDR2 SDRAM Capacitance for GV<sub>DD</sub>(typ) = 1.8 V

| Parameter/Condition                          | Symbol           | Min | Мах | Unit | Notes |

|----------------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> |     | 0.5 | pF   | 1     |

Note:

1. This parameter is sampled.  $GV_{DD}$  = 1.8 V ± 0.090 V, f = 1 MHz, T<sub>A</sub> = 25°C, V<sub>OUT</sub> =  $GV_{DD}/2$ , V<sub>OUT</sub> (peak-to-peak) = 0.2 V.

Table 14 provides the recommended operating conditions for the DDR SDRAM component(s) when  $GV_{DD}(typ) = 2.5 \text{ V}.$

### Table 14. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                             | Symbol            | Min                      | Мах                      | Unit | Notes |

|-------------------------------------------------|-------------------|--------------------------|--------------------------|------|-------|

| I/O supply voltage                              | GV <sub>DD</sub>  | 2.375                    | 2.625                    | V    | 1     |

| I/O reference voltage                           | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$     | $0.51 	imes GV_{DD}$     | V    | 2     |

| I/O termination voltage                         | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04 | V    | 3     |

| Input high voltage                              | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.18 | GV <sub>DD</sub> + 0.3   | V    | _     |

| Input low voltage                               | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.18 | V    | —     |

| Output leakage current                          | I <sub>OZ</sub>   | -9.9                     | -9.9                     | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.95 V) | I <sub>ОН</sub>   | -15.2                    | —                        | mA   | —     |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | I <sub>OL</sub>   | 15.2                     | _                        | mA   | —     |

Notes:

1.  $\text{GV}_{\text{DD}}$  is expected to be within 50 mV of the DRAM  $\text{GV}_{\text{DD}}$  at all times.

2.  $MV_{REF}$  is expected to be equal to 0.5 ×  $GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

Table 15 provides the DDR capacitance when  $GV_{DD}(typ) = 2.5$  V.

### Table 15. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Мах | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | —   | 0.5 | pF   | 1     |

Note:

1. This parameter is sampled.  $GV_{DD} = 2.5 V \pm 0.125 V$ , f = 1 MHz, T<sub>A</sub> = 25°C, V<sub>OUT</sub> =  $GV_{DD}/2$ , V<sub>OUT</sub> (peak-to-peak) = 0.2 V.

#### DDR and DDR2 SDRAM

Table 16 provides the current draw characteristics for  $MV_{REF}$ .

Table 16. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter/Condition                | Symbol             | Min | Max | Unit | Note |

|------------------------------------|--------------------|-----|-----|------|------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> |     | 500 | μA   | 1    |

Note:

1. The voltage regulator for  $\text{MV}_{\text{REF}}$  must supply up to 500  $\mu\text{A}$  current.

## 6.2 DDR and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR and DDR2 SDRAM interface.

### 6.2.1 DDR and DDR2 SDRAM Input AC Timing Specifications

Table 17 provides the input AC timing specifications for the DDR2 SDRAM when  $GV_{DD}(typ) = 1.8 \text{ V}$ .

### Table 17. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

At recommended operating conditions with GV\_{DD} of 1.8  $\pm$  5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.25 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 | _                        | V    | —     |

Table 18 provides the input AC timing specifications for the DDR SDRAM when  $GV_{DD}(typ) = 2.5 V$ .

### Table 18. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

At recommended operating conditions with  $GV_{DD}$  of 2.5  $\pm$  5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | —                        | MV <sub>REF</sub> – 0.31 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | —                        | V    | —     |

Table 19 provides the input AC timing specifications for the DDR SDRAM interface.

### Table 19. DDR and DDR2 SDRAM Input AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of (1.8 or 2.5 V) ± 5%.

| Parameter                             | Symbol              | Min  | Мах | Unit | Notes |

|---------------------------------------|---------------------|------|-----|------|-------|

| Controller Skew for MDQS—MDQ/MECC/MDM | t <sub>CISKEW</sub> |      |     | ps   | 1, 2  |

| 400 MHz                               |                     | -600 | 600 |      | 3     |

| 333 MHz                               |                     | -750 | 750 |      | —     |

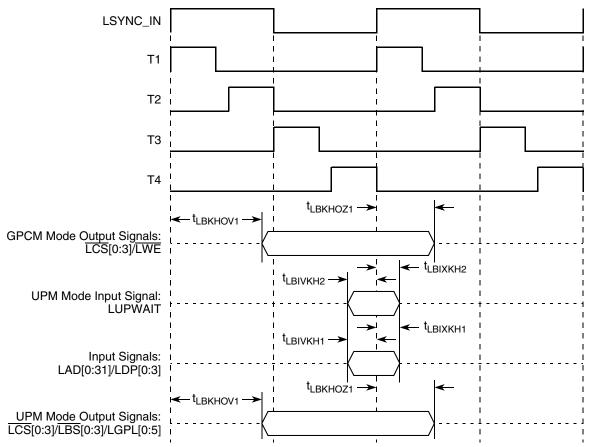

Figure 22. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (DLL Enabled)

## 11 JTAG

This section describes the DC and AC electrical specifications for the IEEE Std. 1149.1 (JTAG) interface of the MPC8343EA.

## **11.1 JTAG DC Electrical Characteristics**

Table 36 provides the DC electrical characteristics for the IEEE Std. 1149.1 (JTAG) interface of the MPC8343EA.

| Table 36. JTAG Interface DC Electrical Character | istics |

|--------------------------------------------------|--------|

|--------------------------------------------------|--------|

| Parameter           | Symbol          | Condition                 | Min                    | Мах                    | Unit |

|---------------------|-----------------|---------------------------|------------------------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> | _                         | OV <sub>DD</sub> - 0.3 | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | _                         | -0.3                   | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | _                         | _                      | ±5                     | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4                    | —                      | V    |

JTAG

Table 36. JTAG Interface DC Electrical Characteristics (continued)

| Parameter          | Symbol          | Condition                | Min | Мах | Unit |

|--------------------|-----------------|--------------------------|-----|-----|------|

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA | _   | 0.5 | V    |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA | _   | 0.4 | V    |

## **11.2 JTAG AC Timing Specifications**

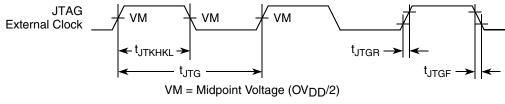

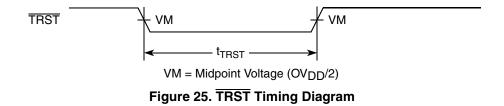

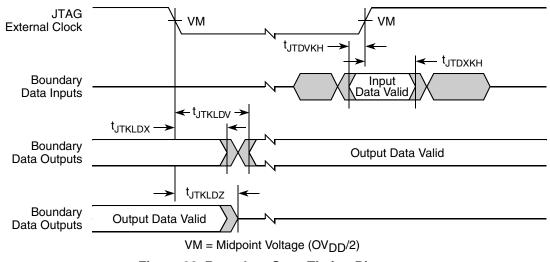

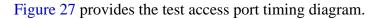

This section describes the AC electrical specifications for the IEEE Std. 1149.1 (JTAG) interface of the MPC8343EA. Table 37 provides the JTAG AC timing specifications as defined in Figure 24 through Figure 27.

### Table 37. JTAG AC Timing Specifications (Independent of CLKIN)<sup>1</sup>

At recommended operating conditions (see Table 2).

| Para                                    | Symbol <sup>2</sup>            | Min                                        | Max      | Unit     | Notes |   |

|-----------------------------------------|--------------------------------|--------------------------------------------|----------|----------|-------|---|

| JTAG external clock frequen             | cy of operation                | f <sub>JTG</sub>                           | 0        | 33.3     | MHz   | — |

| JTAG external clock cycle tir           | ne                             | t <sub>JTG</sub>                           | 30       | _        | ns    | — |

| JTAG external clock pulse w             | idth measured at 1.4 V         | t <sub>JTKHKL</sub>                        | 15       | _        | ns    | — |

| JTAG external clock rise and fall times |                                | t <sub>JTGR</sub> , t <sub>JTGF</sub>      | 0        | 2        | ns    | — |

| TRST assert time                        |                                | t <sub>TRST</sub>                          | 25       | _        | ns    | 3 |

| Input setup times:                      | Boundary-scan data<br>TMS, TDI | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>4   |          | ns    | 4 |

| Input hold times:                       | Boundary-scan data<br>TMS, TDI | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 10<br>10 | -        | ns    | 4 |

| Valid times:                            | Boundary-scan data<br>TDO      | t <sub>jtkldv</sub><br>t <sub>jtklov</sub> | 2<br>2   | 11<br>11 | ns    | 5 |

| Output hold times:                      | Boundary-scan data<br>TDO      | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | 2<br>2   |          | ns    | 5 |

### Table 37. JTAG AC Timing Specifications (Independent of CLKIN)<sup>1</sup> (continued)

At recommended operating conditions (see Table 2).

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min    | Мах     | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|--------|---------|------|-------|

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 2<br>2 | 19<br>9 | ns   | 5, 6  |

Notes:

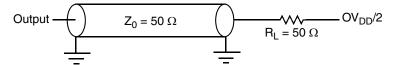

1. All outputs are measured from the midpoint voltage of the falling/rising edge of  $t_{TCLK}$  to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50  $\Omega$  load (see Figure 14). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

2. The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. In general, the clock reference symbol is based on three letters representing the clock of a particular function. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

6. Guaranteed by design and characterization.

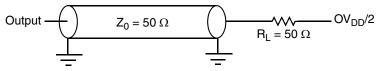

Figure 23 provides the AC test load for TDO and the boundary-scan outputs of the MPC8343EA.

Figure 23. AC Test Load for the JTAG Interface

Figure 24 provides the JTAG clock input timing diagram.

Figure 24. JTAG Clock Input Timing Diagram

Figure 25 provides the  $\overline{\text{TRST}}$  timing diagram.

Figure 26 provides the boundary-scan timing diagram.

Figure 26. Boundary-Scan Timing Diagram

Figure 27. Test Access Port Timing Diagram

## 13 PCI

This section describes the DC and AC electrical specifications for the PCI bus of the MPC8343EA.

## **13.1 PCI DC Electrical Characteristics**

Table 40 provides the DC electrical characteristics for the PCI interface of the MPC8343EA.

| Parameter                 | Symbol          | Test Condition                                       | Min                    | Max                    | Unit |

|---------------------------|-----------------|------------------------------------------------------|------------------------|------------------------|------|

| High-level input voltage  | V <sub>IH</sub> | $V_{OUT} \ge V_{OH}$ (min) or                        | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage   | V <sub>IL</sub> | $V_{OUT} \le V_{OL}$ (max)                           | -0.3                   | 0.8                    | V    |

| Input current             | I <sub>IN</sub> | $V_{IN}^{1} = 0 V \text{ or } V_{IN} = OV_{DD}$      | _                      | ±5                     | μA   |

| High-level output voltage | V <sub>OH</sub> | OV <sub>DD</sub> = min,<br>I <sub>OH</sub> = -100 μA | OV <sub>DD</sub> – 0.2 |                        | V    |

| Low-level output voltage  | V <sub>OL</sub> | OV <sub>DD</sub> = min,<br>I <sub>OL</sub> = 100 μA  | _                      | 0.2                    | V    |

### **Table 40. PCI DC Electrical Characteristics**

Note:

1. The symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1.

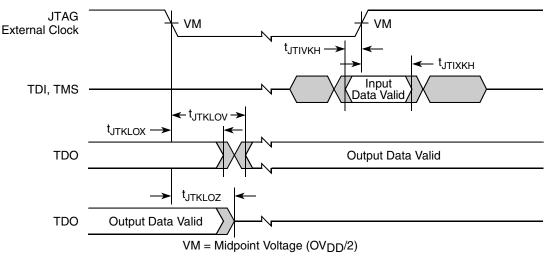

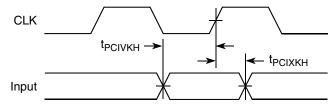

## 13.2 PCI AC Electrical Specifications

This section describes the general AC timing parameters of the PCI bus of the MPC8343EA. Note that the PCI\_CLK or PCI\_SYNC\_IN signal is used as the PCI input clock depending on whether the device is configured as a host or agent device. Table 41 provides the PCI AC timing specifications at 66 MHz.

| Table 41. PCI AC Timing Specifications at 66 MHz <sup>1</sup> |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

| Parameter                      | Symbol <sup>2</sup> | Min | Мах | Unit | Notes |

|--------------------------------|---------------------|-----|-----|------|-------|

| Clock to output valid          | <sup>t</sup> PCKHOV | _   | 6.0 | ns   | 3     |

| Output hold from clock         | t <sub>PCKHOX</sub> | 1   | _   | ns   | 3     |

| Clock to output high impedance | t <sub>PCKHOZ</sub> | -   | 14  | ns   | 3, 4  |

| Input setup to clock           | t <sub>PCIVKH</sub> | 3.0 | _   | ns   | 3, 5  |

Figure 31 shows the PCI input AC timing diagram.

Figure 31. PCI Input AC Timing Diagram

Figure 32 shows the PCI output AC timing diagram.

## 14 Timers

This section describes the DC and AC electrical specifications for the timers.

## 14.1 Timer DC Electrical Characteristics

Table 43 provides the DC electrical characteristics for the MPC8343EA timer pins, including TIN,  $\overline{\text{TOUT}}$ , TGATE, and RTC\_CLK.

| Parameter           | Symbol          | Condition                 | Min  | Мах                    | Unit |

|---------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> | —                         | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                         | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | —                         | —    | ±5                     | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | l <sub>OL</sub> = 3.2 mA  | —    | 0.4                    | V    |

**Table 43. Timer DC Electrical Characteristics**

GPIO

## 14.2 Timer AC Timing Specifications

Table 44 provides the timer input and output AC timing specifications.

Table 44. Timers Input AC Timing Specifications<sup>1</sup>

| Parameter                         | Symbol <sup>2</sup> | Min | Unit |

|-----------------------------------|---------------------|-----|------|

| Timers inputs—minimum pulse width | t <sub>TIWID</sub>  | 20  | ns   |

### Notes:

1. Input specifications are measured from the 50 percent level of the signal to the 50 percent level of the rising edge of CLKIN. Timings are measured at the pin.

2. Timer inputs and outputs are asynchronous to any visible clock. Timer outputs should be synchronized before use by external synchronous logic. Timer inputs are required to be valid for at least t<sub>TIWID</sub> ns to ensure proper operation.

## 15 GPIO

This section describes the DC and AC electrical specifications for the GPIO.

## 15.1 GPIO DC Electrical Characteristics

Table 45 provides the DC electrical characteristics for the MPC8343EA GPIO.

| Table 45. | GPIO | DC | Electrical | Characteristics |

|-----------|------|----|------------|-----------------|

|-----------|------|----|------------|-----------------|

| PArameter           | Symbol          | Condition                 | Min  | Мах                    | Unit |

|---------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> | —                         | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                         | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | —                         | _    | ±5                     | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | _    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | _    | 0.4                    | V    |

## 15.2 GPIO AC Timing Specifications

Table 46 provides the GPIO input and output AC timing specifications.

### Table 46. GPIO Input AC Timing Specifications<sup>1</sup>

| Parameter                       | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

### Notes:

1. Input specifications are measured from the 50 percent level of the signal to the 50 percent level of the rising edge of CLKIN. Timings are measured at the pin.

GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by external synchronous logic. GPIO inputs must be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

SPI

| Table 49. SPI DC Electrical Characteristics (c | continued) |

|------------------------------------------------|------------|

|------------------------------------------------|------------|

| Parameter           | Symbol          | Condition                 | Min | Мах | Unit |

|---------------------|-----------------|---------------------------|-----|-----|------|

| Input current       | I <sub>IN</sub> | _                         | _   | ±5  | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4 | _   | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | _   | 0.5 | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | _   | 0.4 | V    |

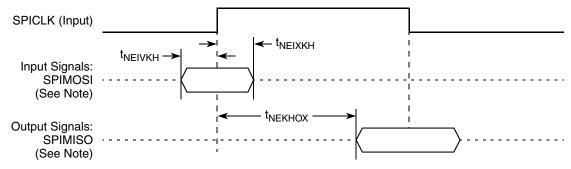

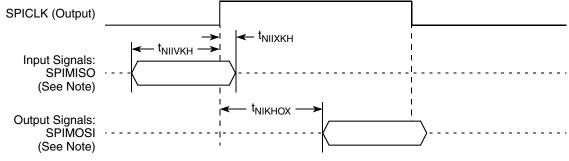

## 17.2 SPI AC Timing Specifications

Table 50 provides the SPI input and output AC timing specifications.

| Table 50. | SPI AC | Timina | Specifications <sup>1</sup> |

|-----------|--------|--------|-----------------------------|

|           |        |        | opeenieanene                |

| Parameter                                               | Symbol <sup>2</sup> | Min | Мах | Unit |

|---------------------------------------------------------|---------------------|-----|-----|------|

| SPI outputs valid—Master mode (internal clock) delay    | t <sub>NIKHOV</sub> | —   | 6   | ns   |

| SPI outputs hold—Master mode (internal clock) delay     | t <sub>NIKHOX</sub> | 0.5 | —   | ns   |

| SPI outputs valid—Slave mode (external clock) delay     | t <sub>NEKHOV</sub> | —   | 8   | ns   |

| SPI outputs hold—Slave mode (external clock) delay      | t <sub>NEKHOX</sub> | 2   | —   | ns   |

| SPI inputs—Master mode (internal clock input setup time | t <sub>NIIVKH</sub> | 4   | —   | ns   |

| SPI inputs—Master mode (internal clock input hold time  | t <sub>NIIXKH</sub> | 0   | _   | ns   |

| SPI inputs—Slave mode (external clock) input setup time | t <sub>NEIVKH</sub> | 4   | —   | ns   |

| SPI inputs—Slave mode (external clock) input hold time  | t <sub>NEIXKH</sub> | 2   | —   | ns   |

### Notes:

1. Output specifications are measured from the 50 percent level of the rising edge of CLKIN to the 50 percent level of the signal. Timings are measured at the pin.

The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>NIKHOX</sub> symbolizes the internal timing (NI) for the time SPICLK clock reference (K) goes to the high state (H) until outputs (O) are invalid (X).

### Figure 33 provides the AC test load for the SPI.

Figure 33. SPI AC Test Load

Figure 34 and Figure 35 represent the AC timings from Table 50. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

Figure 34 shows the SPI timings in slave mode (external clock).

Note: The clock edge is selectable on SPI.

### Figure 34. SPI AC Timing in Slave Mode (External Clock) Diagram

Figure 35 shows the SPI timings in master mode (internal clock).

Note: The clock edge is selectable on SPI.

Figure 35. SPI AC Timing in Master Mode (Internal Clock) Diagram

## **18 Package and Pin Listings**

This section details package parameters, pin assignments, and dimensions. The MPC8343EA is available in a plastic ball grid array (PBGA). See Section 18.1, "Package Parameters for the MPC8343EA PBGA," and Section 18.2, "Mechanical Dimensions for the MPC8343EA PBGA."

### 18.1 Package Parameters for the MPC8343EA PBGA

The package parameters are as provided in the following list. The package type is  $29 \text{ mm} \times 29 \text{ mm}$ , 620 plastic ball grid array (PBGA).

| Package outline         | $29 \text{ mm} \times 29 \text{ mm}$ |

|-------------------------|--------------------------------------|

| Interconnects           | 620                                  |

| Pitch                   | 1.00 mm                              |

| Module height (maximum) | 2.46 mm                              |

Package and Pin Listings

| Signal                      | Package Pin Number                     | Pin Type | Power<br>Supply   | Notes |  |  |  |

|-----------------------------|----------------------------------------|----------|-------------------|-------|--|--|--|

|                             | USB                                    |          |                   |       |  |  |  |

| DR_D0_ENABLEN               | C28                                    | I/O      | OV <sub>DD</sub>  | —     |  |  |  |

| DR_D1_SER_TXD               | F25                                    | I/O      | OV <sub>DD</sub>  | —     |  |  |  |

| DR_D2_VMO_SE0               | B28                                    | I/O      | OV <sub>DD</sub>  | —     |  |  |  |

| DR_D3_SPEED                 | C27                                    | I/O      | OV <sub>DD</sub>  | —     |  |  |  |

| DR_D4_DP                    | D26                                    | I/O      | OV <sub>DD</sub>  | —     |  |  |  |

| DR_D5_DM                    | E25                                    | I/O      | OV <sub>DD</sub>  | —     |  |  |  |

| DR_D6_SER_RCV               | C26                                    | I/O      | OV <sub>DD</sub>  | —     |  |  |  |

| DR_D7_DRVVBUS               | D25                                    | I/O      | OV <sub>DD</sub>  | —     |  |  |  |

| DR_SESS_VLD_NXT             | B26                                    | I        | OV <sub>DD</sub>  | —     |  |  |  |

| DR_XCVR_SEL_DPPULLUP        | E24                                    | I/O      | OV <sub>DD</sub>  | —     |  |  |  |

| DR_STP_SUSPEND              | A27                                    | 0        | OV <sub>DD</sub>  | —     |  |  |  |

| DR_RX_ERROR_PWRFAULT        | C25                                    | I        | OV <sub>DD</sub>  | —     |  |  |  |

| DR_TX_VALID_PCTL0           | A26                                    | 0        | OV <sub>DD</sub>  | —     |  |  |  |

| DR_TX_VALIDH_PCTL1          | B25                                    | 0        | OV <sub>DD</sub>  | —     |  |  |  |

| DR_CLK                      | A25                                    | I        | OV <sub>DD</sub>  | —     |  |  |  |

|                             | Programmable Interrupt Controller      |          |                   |       |  |  |  |

| MCP_OUT                     | E8                                     | 0        | $OV_{DD}$         | 2     |  |  |  |

| IRQ0/MCP_IN/GPIO2[12]       | J28                                    | I/O      | $OV_{DD}$         |       |  |  |  |

| IRQ[1:5]/GPIO2[13:17]       | K25, J25, H26, L24, G27                | I/O      | OV <sub>DD</sub>  |       |  |  |  |

| IRQ[6]/GPIO2[18]/CKSTOP_OUT | G28                                    | I/O      | $OV_{DD}$         |       |  |  |  |

| IRQ[7]/GPIO2[19]/CKSTOP_IN  | J26                                    | I/O      | OV <sub>DD</sub>  | —     |  |  |  |

|                             | Ethernet Management Interface          |          |                   |       |  |  |  |

| EC_MDC                      | Y24                                    | 0        | LV <sub>DD1</sub> |       |  |  |  |

| EC_MDIO                     | Y25                                    | I/O      | LV <sub>DD1</sub> | 11    |  |  |  |

| Gigabit Reference Clock     |                                        |          |                   |       |  |  |  |

| EC_GTX_CLK125               | Y26                                    | I        | LV <sub>DD1</sub> |       |  |  |  |

| Three-S                     | speed Ethernet Controller (Gigabit Eth | ernet 1) |                   |       |  |  |  |

| TSEC1_COL/GPIO2[20]         | M26                                    | I/O      | OV <sub>DD</sub>  | —     |  |  |  |

| TSEC1_CRS/GPIO2[21]         | U25                                    | I/O      | LV <sub>DD1</sub> | —     |  |  |  |

| TSEC1_GTX_CLK               | V24                                    | 0        | LV <sub>DD1</sub> | 3     |  |  |  |

| TSEC1_RX_CLK                | U26                                    | I        | LV <sub>DD1</sub> | —     |  |  |  |

### Table 51. MPC8343EA (PBGA) Pinout Listing (continued)

Package and Pin Listings

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                          | Pin Type                         | Power<br>Supply             | Notes |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------|-------|--|

| OV <sub>DD</sub> | B27, D3, D11, D19, E15, E23, F5, F8,<br>F11, F14, F17, F20, G24, H23, H24, J6<br>J14, J17, J18, K4, L9, L20, L23, L25, M6<br>M9, M20, P5, P20, P23, R6, R9, R24,<br>U23, V4, V6                                                                                                                                                                                                                                             | , Ethernet, and , other standard | OV <sub>DD</sub>            |       |  |

| MVREF1           | AF19                                                                                                                                                                                                                                                                                                                                                                                                                        | I                                | DDR<br>reference<br>voltage | _     |  |

| MVREF2           | AE10                                                                                                                                                                                                                                                                                                                                                                                                                        | I                                | DDR<br>reference<br>voltage | _     |  |

|                  | No Connection                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |                             |       |  |

| NC               | A22, A23, A24, B22, B23, B24, C21,<br>C22, C23, C24, D21, D22, D23, D24,<br>E21, M27, M28, N26, N27, N28, P25,<br>P26, P27, R28, T24, T25, T26, T27, T28<br>U27, U28, Y3, Y4, Y5, AA1, AA2, AA3<br>AA4, AB1, AB2, AB3, AB4, AC1, AC2<br>AC3, AC4, AD1, AD2, AD3, AD5, AD7<br>AD11, AD12, AE4, AE6, AE8, AE9,<br>AE23, AF1, AF5, AF6, AF8, AF24, AG1<br>AG3, AG4, AG7, AG8, AG9, AG10, AH2<br>AH3, AH5, AH8, AH9, V5, V2, V1 | ,<br>,                           | _                           | _     |  |

### Table 51. MPC8343EA (PBGA) Pinout Listing (continued)

### Notes:

1. This pin is an open-drain signal. A weak pull-up resistor (1 kΩ) should be placed on this pin to OV<sub>DD</sub>.

2. This pin is an open-drain signal. A weak pull-up resistor (2-10 kΩ) should be placed on this pin to OV<sub>DD</sub>.

3. During reset, this output is actively driven rather than three-stated.

4. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

5. This pin should have a weak pull-up if the chip is in PCI host mode. Follow the PCI specifications.

6. This pin must be always be tied to GND.

7. This pin must always be pulled up to OV<sub>DD</sub>.

8. Thermal sensitive resistor.

9. It is recommended that MDIC0 be tied to GND using an 18.2  $\Omega$  resistor and MDIC1 be tied to DDR power using an 18.2  $\Omega$  resistor.

10.TSEC1\_TXD[3] is required an external pull-up resistor. For proper functionality of the device, this pin must be pulled up or actively driven high during a hard reset. No external pull-down resistors are allowed to be attached to this net.

11. A weak pull-up resistor (2–10 k $\Omega$ ) should be placed on this pin to LV<sub>DD1</sub>.

12. For systems that boot from local bus (GPCM)-controlled NOR flash, a pull up on LGPL4 is required.

Clocking

|                                        |      |                                                    | Ir    | nput Clock Fr | equency (MHz | ) <sup>2</sup> |

|----------------------------------------|------|----------------------------------------------------|-------|---------------|--------------|----------------|

| CFG_CLKIN_DIV<br>at Reset <sup>1</sup> | SPMF | <i>csb_clk</i> :<br>Input Clock Ratio <sup>2</sup> | 16.67 | 25            | 33.33        | 66.67          |

|                                        |      |                                                    |       | csb_clk Free  | quency (MHz) |                |

| High                                   | 0010 | 2:1                                                |       |               |              | 133            |

| High                                   | 0011 | 3 : 1                                              |       |               | 100          | 200            |

| High                                   | 0100 | 4 : 1                                              |       |               | 133          | 266            |

| High                                   | 0101 | 5 : 1                                              |       |               | 166          | 333            |

| High                                   | 0110 | 6 : 1                                              |       |               | 200          |                |

| High                                   | 0111 | 7:1                                                |       |               | 233          |                |

| High                                   | 1000 | 8 : 1                                              |       |               |              |                |

### Table 55. CSB Frequency Options for Host Mode (continued)

<sup>1</sup> CFG\_CLKIN\_DIV selects the ratio between CLKIN and PCI\_SYNC\_OUT.

<sup>2</sup> CLKIN is the input clock in host mode; PCI\_CLK is the input clock in agent mode.

DDR2 memory may be used at 133 MHz provided that the memory components are specified for operation at this frequency.

### Table 56. CSB Frequency Options for Agent Mode

|                                        | In   |                                                       | put Clock Fre | equency (MHz        | z) <sup>2</sup> |       |

|----------------------------------------|------|-------------------------------------------------------|---------------|---------------------|-----------------|-------|

| CFG_CLKIN_DIV<br>at Reset <sup>1</sup> | SPMF | IF <i>csb_clk</i> :<br>Input Clock Ratio <sup>2</sup> |               | 25                  | 33.33           | 66.67 |

|                                        |      |                                                       |               | <i>csb_clk</i> Freq | uency (MHz)     |       |

| Low                                    | 0010 | 2 : 1                                                 |               |                     |                 | 133   |

| Low                                    | 0011 | 3 : 1                                                 |               |                     | 100             | 200   |

| Low                                    | 0100 | 4 : 1                                                 |               | 100                 | 133             | 266   |

| Low                                    | 0101 | 5 : 1                                                 |               | 125                 | 166             | 333   |

| Low                                    | 0110 | 6 : 1                                                 | 100           | 150                 | 200             |       |

| Low                                    | 0111 | 7:1                                                   | 116           | 175                 | 233             |       |

| Low                                    | 1000 | 8 : 1                                                 | 133           | 200                 | 266             |       |

| Low                                    | 1001 | 9 : 1                                                 | 150           | 225                 | 300             |       |

| Low                                    | 1010 | 10 : 1                                                | 166           | 250                 | 333             |       |

| Low                                    | 1011 | 11 : 1                                                | 183           | 275                 |                 |       |

| Low                                    | 1100 | 12 : 1                                                | 200           | 300                 |                 |       |

| Low                                    | 1101 | 13 : 1                                                | 216           | 325                 |                 |       |

| Low                                    | 1110 | 14 : 1                                                | 233           |                     |                 |       |

| Low                                    | 1111 | 15 : 1                                                | 250           |                     |                 |       |

| Low                                    | 0000 | 16 : 1                                                | 266           |                     |                 |       |

| High                                   | 0010 | 4 : 1                                                 |               | 100                 | 133             | 266   |

|                         | RC   | RCWL 266 MHz Device |                                              | 33:                  | 333 MHz Device        |                                              |                      | 400 MHz Device        |                                              |                      |                       |

|-------------------------|------|---------------------|----------------------------------------------|----------------------|-----------------------|----------------------------------------------|----------------------|-----------------------|----------------------------------------------|----------------------|-----------------------|

| Ref<br>No. <sup>1</sup> | SPMF | CORE<br>PLL         | Input<br>Clock<br>Freq<br>(MHz) <sup>2</sup> | CSB<br>Freq<br>(MHz) | Core<br>Freq<br>(MHz) | Input<br>Clock<br>Freq<br>(MHz) <sup>2</sup> | CSB<br>Freq<br>(MHz) | Core<br>Freq<br>(MHz) | Input<br>Clock<br>Freq<br>(MHz) <sup>2</sup> | CSB<br>Freq<br>(MHz) | Core<br>Freq<br>(MHz) |

| 326                     | 0011 | 0100110             |                                              | _                    |                       | 33                                           | 100                  | 300                   | 33                                           | 100                  | 300                   |

| 623                     | 0110 | 0100011             |                                              | _                    |                       | 33                                           | 200                  | 300                   | 33                                           | 200                  | 300                   |

| 922                     | 1001 | 0100010             |                                              | —                    |                       | 33                                           | 300                  | 300                   | 33                                           | 300                  | 300                   |

| 425                     | 0100 | 0100101             |                                              | _                    |                       | 33                                           | 133                  | 333                   | 33                                           | 133                  | 333                   |

| 524                     | 0101 | 0100100             | _                                            |                      |                       | 33                                           | 166                  | 333                   | 33                                           | 166                  | 333                   |

| A22                     | 1010 | 0100010             | _                                            |                      |                       | 33                                           | 333                  | 333                   | 33                                           | 333                  | 333                   |

| 723                     | 0111 | 0100011             | —                                            |                      |                       |                                              |                      |                       | 33                                           | 233                  | 350                   |

| 604                     | 0110 | 0000100             | —                                            |                      |                       | —                                            |                      |                       | 33                                           | 200                  | 400                   |

| 624                     | 0110 | 0100100             | —                                            |                      |                       | —                                            |                      |                       | 33                                           | 200                  | 400                   |

| 823                     | 1000 | 0100011             |                                              | —                    |                       | —                                            |                      | 33                    | 266                                          | 400                  |                       |

|                         |      |                     |                                              | 66 N                 | MHZ CLKIN             | I/PCI_CLK                                    | Options              |                       |                                              |                      |                       |

| 242                     | 0010 | 1000010             | 66                                           | 133                  | 133                   | 66                                           | 133                  | 133                   | 66                                           | 133                  | 133                   |

| 322                     | 0011 | 0100010             | 66                                           | 200                  | 200                   | 66                                           | 200                  | 200                   | 66                                           | 200                  | 200                   |

| 224                     | 0010 | 0100100             | 66                                           | 133                  | 266                   | 66                                           | 133                  | 266                   | 66                                           | 133                  | 266                   |

| 422                     | 0100 | 0100010             | 66                                           | 266                  | 266                   | 66                                           | 266                  | 266                   | 66                                           | 266                  | 266                   |

| 323                     | 0011 | 0100011             |                                              | —                    |                       | 66                                           | 200                  | 300                   | 66                                           | 200                  | 300                   |

| 223                     | 0010 | 0100101             |                                              | —                    |                       | 66                                           | 133                  | 333                   | 66                                           | 133                  | 333                   |

| 522                     | 0101 | 0100010             | —                                            |                      |                       | 66                                           | 333                  | 333                   | 66                                           | 333                  | 333                   |

| 304                     | 0011 | 0000100             |                                              |                      |                       |                                              | _                    |                       | 66                                           | 200                  | 400                   |

| 324                     | 0011 | 0100100             | _                                            |                      | —                     |                                              | 66                   | 200                   | 400                                          |                      |                       |

| 403                     | 0100 | 0000011             |                                              |                      |                       |                                              |                      |                       | 66                                           | 266                  | 400                   |

| 423                     | 0100 | 0100011             |                                              |                      |                       |                                              | _                    |                       | 66                                           | 266                  | 400                   |

| Table 58. Suggested PLI | Configurations (continued) |

|-------------------------|----------------------------|

|-------------------------|----------------------------|

<sup>1</sup> The PLL configuration reference number is the hexadecimal representation of RCWL, bits 4–15 associated with the SPMF and COREPLL settings given in the table.

<sup>2</sup> The input clock is CLKIN for PCI host mode or PCI\_CLK for PCI agent mode.

NP

Thermal

The junction-to-ambient thermal resistance is an industry-standard value that provides a quick and easy estimation of thermal performance. Generally, the value obtained on a single-layer board is appropriate for a tightly packed printed-circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated. Test cases have demonstrated that errors of a factor of two (in the quantity  $T_J - T_A$ ) are possible.

### 20.2.2 Estimation of Junction Temperature with Junction-to-Board Thermal Resistance

The thermal performance of a device cannot be adequately predicted from the junction-to-ambient thermal resistance. The thermal performance of any component is strongly dependent on the power dissipation of surrounding components. In addition, the ambient temperature varies widely within the application. For many natural convection and especially closed box applications, the board temperature at the perimeter (edge) of the package is approximately the same as the local air temperature near the device. Specifying the local ambient conditions explicitly as the board temperature provides a more precise description of the local ambient conditions that determine the temperature of the device.

At a known board temperature, the junction temperature is estimated using the following equation:

$$T_J = T_A + (R_{\theta JA} \times P_D)$$

where:

$T_I$  = junction temperature (°C)

$T_A$  = ambient temperature for the package (°C)

$R_{\theta IA}$  = junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

When the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made. The application board should be similar to the thermal test condition: the component is soldered to a board with internal planes.

### 20.2.3 Experimental Determination of Junction Temperature

To determine the junction temperature of the device in the application after prototypes are available, use the thermal characterization parameter ( $\Psi_{JT}$ ) to determine the junction temperature and a measure of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

where:

$T_J$  = junction temperature (°C)

$T_T$  = thermocouple temperature on top of package (°C)

$\Psi_{JT}$  = junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per the JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so

#### **Ordering Information**

parts including extended temperatures, refer to the device product summary page on our website listed on the back cover of this document or, contact your local Freescale sales office.

| MPC             | nnnn               | е                                       | t                                      | рр                             | aa                                         | а                     | r                 |

|-----------------|--------------------|-----------------------------------------|----------------------------------------|--------------------------------|--------------------------------------------|-----------------------|-------------------|

| Product<br>Code | Part<br>Identifier | Encryption<br>Acceleration              | Temperature <sup>1</sup><br>Range      | Package <sup>2</sup>           | Processor<br>Frequency <sup>3</sup>        | Platform<br>Frequency | Revision<br>Level |

| MPC             | 8343               | Blank = Not<br>included<br>E = included | Blank = 0 to 105°C<br>C = -40 to 105°C | ZQ = PBGA<br>VR = PB Free PBGA | e300 core<br>speed<br>AD = 266<br>AG = 400 | D = 266               | B = 3.1           |

### Table 62. Part Numbering Nomenclature

Notes:

1. For temperature range = C, processor frequency is limited to 400 with a platform frequency of 266 and up to with a platform frequency of 333

2. See Section 18, "Package and Pin Listings," for more information on available package types.

Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by Part Number Specifications may support other maximum core frequencies.

Table 63 shows the SVR settings by device and package type.

### Table 63. SVR Settings

| Device    | Package | SVR (Rev. 3.0) |

|-----------|---------|----------------|

| MPC8343EA | PBGA    | 8056_0030      |

| MPC8343A  | PBGA    | 8057_0030      |

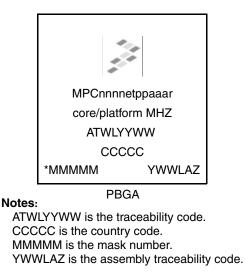

### 22.2 Part Marking

Parts are marked as in the example shown in Figure 40.

### Figure 40. Freescale Part Marking for PBGA Devices