Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 20MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 28                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 256 x 8                                                               |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 12x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08pa32vlc |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Sectio  | on numbe       | er Title                                   | Page |

|---------|----------------|--------------------------------------------|------|

| 13.4 Bl | ock diagram    | 1                                          |      |

| 13.5 Ex | ternal signa   | l description                              |      |

| 13.6 Re | egister defini | ition                                      |      |

| 13      | 6.6.1 MTI      | M Status and Control Register (MTIMx_SC)   |      |

| 13      | 6.2 MTI        | M Clock Configuration Register (MTIMx_CLK) |      |

| 13      | 6.3 MTI        | M Counter Register (MTIMx_CNT)             |      |

| 13      | 6.4 MTI        | M Modulo Register (MTIMx_MOD)              |      |

| 13.7 Fu | inctional des  | scription                                  |      |

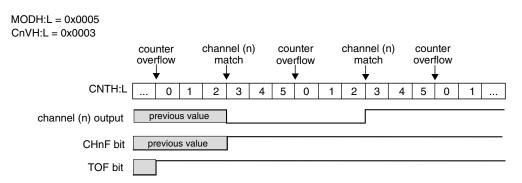

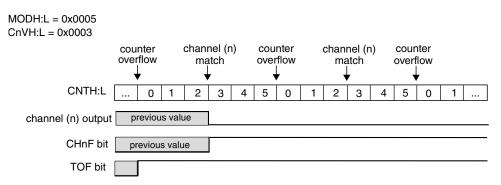

| 13      | 5.7.1 MTI      | M operation example                        |      |

### Chapter 14 Real-time counter (RTC)

| 14.1 | Introduc | tion                                        | .399  |

|------|----------|---------------------------------------------|-------|

| 14.2 | Features |                                             | . 399 |

|      | 14.2.1   | Modes of operation                          | . 399 |

|      |          | 14.2.1.1 Wait mode                          | . 399 |

|      |          | 14.2.1.2 Stop modes                         | .400  |

|      | 14.2.2   | Block diagram                               | . 400 |

| 14.3 | External | signal description                          | 400   |

| 14.4 | Register | definition                                  | .401  |

|      | 14.4.1   | RTC Status and Control Register 1 (RTC_SC1) | . 401 |

|      | 14.4.2   | RTC Status and Control Register 2 (RTC_SC2) | . 402 |

|      | 14.4.3   | RTC Modulo Register: High (RTC_MODH)        | . 403 |

|      | 14.4.4   | RTC Modulo Register: Low (RTC_MODL)         | . 403 |

|      | 14.4.5   | RTC Counter Register: High (RTC_CNTH)       | . 404 |

|      | 14.4.6   | RTC Counter Register: Low (RTC_CNTL)        | . 404 |

| 14.5 | Function | nal description                             | 405   |

|      | 14.5.1   | RTC operation example                       | . 406 |

# Chapter 1 Device Overview

# 1.1 Introduction

These devices are members of the low-cost, high-performance HCS08 family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced HCS08 central processor unit and are available with a variety of modules, memory sizes and types, and package types. The following table summarizes the peripheral availability per package type for the devices available.

| Feature             | MC9S08PA60 | MC9S08PA32 |

|---------------------|------------|------------|

| Flash size (bytes)  | 60,864     | 32,768     |

| EEPROM size (bytes) | 256        | 256        |

| RAM size (bytes)    | 4,096      | 4,096      |

| LQFP-64             | Yes        | Yes        |

| QFP-64              | Yes        | Yes        |

| LQFP-48             | Yes        | Yes        |

| LQFP-44             | Yes        | Yes        |

| LQFP-32             | Yes        | Yes        |

Table 1-1. Memory and package availability

Table 1-2. Feature availability

| Pin number    | 64-pin | 48-pin | 44-pin | 32-pin |

|---------------|--------|--------|--------|--------|

| Bus frequency | 20     | 20     | 20     | 20     |

| (MHz)         | 20     | 20     | 20     | 20     |

| IRQ           |        | Y      | ïes    |        |

| WDOG          | Yes    |        |        |        |

| DBG           | Yes    |        |        |        |

| IPC           | Yes    |        |        |        |

| CRC           | Yes    |        |        |        |

| ICS           | Yes    |        |        |        |

Table continues on the next page...

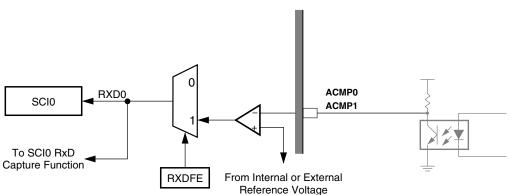

Figure 6-4. IR demodulation diagram

## 6.5.5 RTC capture

RTC overflow may be captured by FTM1 channel 1 by setting SYS\_SOPT2[RTCC] bit. When this bit is set, the RTC overflow is connected to FTM1 channel 1 for capture, the FTM1CH1 pin is released to other shared functions.

## 6.5.6 FTM2 software synchronization

FTM2 contains three synchronization input trigger, one of which is a software trigger by writing 1 to the SYS\_SOPT2[FTMSYNC] bit. Writing 0 to this bit takes no effect. This bit is always read 0.

## 6.5.7 ADC hardware trigger

ADC module may initiate a conversion via a hardware trigger. MTIM0 overflow, RTC, FTM2 match trigger with 8-bit programmable delay, and FTM2 init trigger with 8-bit programmable delay can be enabled as the hardware trigger for the ADC module by setting the SYS\_SOPT2[ADHWT] bits. The following table shows the ADC hardware trigger setting.

| ADHWT | ADC hardware trigger                             |

|-------|--------------------------------------------------|

| 0:0   | RTC overflow                                     |

| 0:1   | MTIM0 overflow                                   |

| 1:0   | FTM2 init trigger with 8-bit programmable delay  |

| 1:1   | FTM2 match trigger with 8-bit programmable delay |

| Table 6-1. | ADC hardware | trigger setting |

|------------|--------------|-----------------|

|------------|--------------|-----------------|

#### **Chapter 7 Parallel input/output**

### **PORT\_PTED** field descriptions (continued)

| Field | Description                                                                                               |

|-------|-----------------------------------------------------------------------------------------------------------|

|       | Reset forces PTED to all 0s, but these 0s are not driven out of the corresponding pins because reset also |

|       | configures all port pins as high-impedance inputs with pullups disabled.                                  |

### 7.7.6 Port F Data Register (PORT\_PTFD)

Address: 0h base + 5h offset = 5h

| Bit           | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------------|---|---|---|----|----|---|---|---|

| Read<br>Write |   |   |   | PT | FD |   |   |   |

| Reset         | 0 | 0 | 0 | 0  | 0  | 0 | 0 | 0 |

### PORT\_PTFD field descriptions

| Field | Description                                                                                                                                                                        |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTFD  | Port F Data Register Bits                                                                                                                                                          |

|       | For port F pins that are configured as inputs, a read returns the logic level on the pin.                                                                                          |

|       | For port F pins that are configured as outputs, a read returns the last value that was written to this register.                                                                   |

|       | For port F pins that are configured as Hi-Z, a read returns uncertainty data.                                                                                                      |

|       | Writes are latched into all bits of this register. For port F pins that are configured as outputs, the logic level is driven out of the corresponding MCU pin.                     |

|       | Reset forces PTFD to all 0s, but these 0s are not driven out of the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

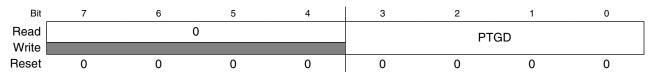

## 7.7.7 Port G Data Register (PORT\_PTGD)

Address: 0h base + 6h offset = 6h

### PORT\_PTGD field descriptions

| Field           | Description                                                                                                                                                                                                                                   |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–4<br>Reserved | This field is reserved.<br>This read-only field is reserved and always has the value 0.                                                                                                                                                       |

| PTGD            | Port G Data Register Bits<br>For port G pins that are configured as inputs, a read returns the logic level on the pin.<br>For port G pins that are configured as outputs, a read returns the last value that was written to this<br>register. |

Table continues on the next page ...

### **Chapter 7 Parallel input/output**

| Field | Description                         |

|-------|-------------------------------------|

| 3–2   | Filter selection for input from PTB |

| FLTB  |                                     |

|       | 00 BUSCLK                           |

|       | 01 FLTDIV1                          |

|       | 10 FLTDIV2                          |

|       | 11 FLTDIV3                          |

| FLTA  | Filter selection for input from PTA |

|       | 00 BUSCLK                           |

|       | 01 FLTDIV1                          |

|       | 10 FLTDIV2                          |

|       | 11 FLTDIV3                          |

### PORT\_IOFLT0 field descriptions (continued)

## 7.7.27 Port Filter Register 1 (PORT\_IOFLT1)

This register sets the filters for input from PTE to PTH.

Address: 0h base + 30EDh offset = 30EDh

| Bit           | 7 | 6   | 5  | 4  | 3    | 2 | 1    | 0 |      |  |

|---------------|---|-----|----|----|------|---|------|---|------|--|

| Read<br>Write | F | LTH | FL | TG | FLTF |   | FLTF |   | FLTE |  |

| Reset         | 0 | 0   | 0  | 0  | 0    | 0 | 0    | 0 |      |  |

### PORT\_IOFLT1 field descriptions

| Field       | Description                         |

|-------------|-------------------------------------|

| 7–6<br>FLTH | Filter selection for input from PTH |

|             | 00 BUSCLK                           |

|             | 01 FLTDIV1                          |

|             | 10 FLTDIV2                          |

|             | 11 FLTDIV3                          |

| 5–4<br>FLTG | Filter selection for input from PTG |

| 1210        | 00 BUSCLK                           |

|             | 01 FLTDIV1                          |

|             | 10 FLTDIV2                          |

|             | 11 FLTDIV3                          |

| 3–2<br>FLTF | Filter selection for input from PTF |

|             | 00 BUSCLK                           |

|             | 01 FLTDIV1                          |

|             | 10 FLTDIV2                          |

|             | 11 FLTDIV3                          |

Table continues on the next page ...

### PORT\_PTCPE field descriptions (continued)

| pins that are configured as outputs or Hi-Z, these bits have no effect.  9 Pullup disabled for port C bit 7.  1 Pullup enabled for port C bit 7.  9 Pull Enable for Port C Bit 6  9 PTCPE6 9 Pullup disabled for port C bit 6. 1 Pullup enabled for port C bit 5. 1 Pullup enabled for port C bit 5. 1 Pullup enabled for port C bit 5. 4 PTCPE4 9 PUI Enable for Port C Bit 4 9 PTCPE4 1 This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect. 0 Pullup disabled for port C bit 5. 4 PTCPE4 9 PTCPE4 9 PUIL Enable for Port C Bit 4 1 Pullup enabled for port C bit 4. 1 Pullup enabled for port C bit 4. 1 Pullup enabled for port C bit 3. 9 PTCPE3 9 PTCPE5 9 PTC                                                                                 | Field  | Description                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       Pullup enabled for port C bit 7.         6       PTCPE6         PTCPE6       Pull Enable for Port C Bit 6         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por<br>pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup enabled for port C bit 6.         5       PTCPE5         7       Pulle nable for Port C Bit 5         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por<br>pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 5.         1       Pullup disabled for port C bit 5.         1       Pullup disabled for port C bit 5.         1       Pullup disabled for port C bit 4.         1       Pullup enabled for port C bit 3.         1       Pullup disabled for port C bit 3.         1       Pullup disabled for port C bit 3.         1       Pullup enabled for port C bit 3.         1       Pullup enabled for port C bit 3.         1       Pullup disabled for port C bit 3.         1       Pullup d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | This control bit determines if the internal pullup device is enabled for the associated PTC pin. For port C pins that are configured as outputs or Hi-Z, these bits have no effect. |

| 1       Pullup enabled for port C bit 7.         6       PTCPE6         PTCPE6       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup enabled for port C bit 6.         5       PTCPE5         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 5.         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup enabled for port C bit 5.         4       PTCPE4         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup enabled for port C bit 4.         1       Pullup disabled for port C bit 4.         1       Pullup enabled for port C bit 3.         2       PTCPE3         This control bit determines if the internal pullup device is enabled for th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        | 0 Pullun disabled for port C bit 7                                                                                                                                                  |

| 6       Pull Enable for Port C Bit 6         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 6.         1       Pullup disabled for port C bit 5         Propes       Pullup disabled for port C bit 5.         1       Pullup disabled for port C bit 5.         0       Pullup disabled for port C bit 5.         1       Pullup disabled for port C bit 5.         4       PTCPE4         4       PTCPE4         7       Pull Enable for Port C Bit 4         7       Pullup disabled for port C bit 4.         1       Pullup disabled for port C Bit 4         7       Pull Enable for Port C Bit 3         7       Pull Enable for Port C Bit 4         7       Pullup disabled for port C bit 4.         1       Pullup disabled for port C Bit 3         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C Bit 3         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |                                                                                                                                                                                     |

| This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por<br>pins that are configured as outputs or Hi-Z, these bits have no effect.<br>Pullup enabled for port C bit 6.<br>Pull Enable for Port C Bit 5<br>PTCPE5<br>PTCPE5<br>PTCPE4<br>Pull Enable for Port C Bit 5.<br>Pull Enable for Port C Bit 4<br>PTCPE4<br>Pullup disabled for port C bit 5.<br>Pull Enable for Port C Bit 4<br>PTCPE4<br>Pullup disabled for port C bit 4.<br>Pullup disabled for port C bit 3.<br>Pullup disabled for port C bit 4.<br>Pullup disabled for port C bit 3.<br>PTCPE3<br>PUE Enable for Port C Bit 3<br>PTCPE3<br>PUE Enable for Port C Bit 3<br>PTCPE3<br>PUE Enable for Port C Bit 2<br>PTCPE4<br>PUE Enable for Port C Bit 2<br>PTCPE5<br>PTCPE2<br>PTCPE2<br>PUE Enable for Port C Bit 2<br>PTCPE3<br>PUE Enable for Port C Bit 2<br>PTCPE4<br>PUE Enable for Port C Bit 2<br>PTCPE5<br>PUE Enable for Port C Bit 1<br>PUE Enable for Port C Bit 1<br>PTCPE1<br>PUE Enable for Port C Bit 1<br>PUE Enable for Port C Bit 1<br>PTCPE5<br>PUE Enable for Port C Bit 1<br>PUE Enable f | -      |                                                                                                                                                                                     |

| 1       Pullup enabled for port C bit 6.         5       PTCPES         7       Pull Enable for Port C Bit 5         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 5.         1       Pullup enabled for port C bit 5.         4       PTCPE4         PTCPE4       Pull Enable for Port C Bit 4         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup enabled for port C bit 4.         1       Pullup enabled for port C bit 3.         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 3.         1       Pullup disabled for port C bit 3.         2       PTCPE2         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 2.         1       Pullup disabled for port C bit 2.         1 </td <td>110.20</td> <td>This control bit determines if the internal pullup device is enabled for the associated PTC pin. For port C pins that are configured as outputs or Hi-Z, these bits have no effect.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 110.20 | This control bit determines if the internal pullup device is enabled for the associated PTC pin. For port C pins that are configured as outputs or Hi-Z, these bits have no effect. |

| 5       PUIL Enable for Port C Bit 5         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For porpins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 5.         4       PTCPE4         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For porpins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 4.         1       Pullup disabled for port C bit 4.         1       Pullup enabled for port C bit 4.         1       Pullup enabled for port C bit 4.         1       Pullup enabled for port C bit 4.         3       PTCPE3         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For porpins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 3.         1       Pullup disabled for port C bit 3.         2       Pulle enable for Port C Bit 2         PTCPE2       Pull Enable for Port C Bit 2.         1       Pullup disabled for port C bit 2.         2       Pulle disabled for port C bit 2.         3       Pull Enable for Port C Bit 1         1       Pullup enabled for port C bit 2.         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | 0 Pullup disabled for port C bit 6.                                                                                                                                                 |

| PTCPE5       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup enabled for port C bit 5.         4       PTCPE4         7       Pull Enable for Port C Bit 4         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 4.         1       Pullup enabled for port C bit 4.         3       PTCPE3         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup enabled for port C bit 3.         1       Pullup enabled for port C bit 3.         2       PTCPE2         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup enabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | 1 Pullup enabled for port C bit 6.                                                                                                                                                  |

| pins that are configured as outputs or Hi-Z, these bits have no effect.<br>0 Pullup disabled for port C bit 5.<br>4 PTCPE4<br>4 PTCPE4<br>4 PTCPE4<br>7 bit control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.<br>0 Pullup disabled for port C bit 4.<br>1 Pullup enabled for port C bit 4.<br>1 Pullup enabled for port C bit 4.<br>1 Pullup enabled for port C bit 4.<br>1 Pullup disabled for port C bit 3.<br>PTCPE3<br>7 bit control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.<br>0 Pullup disabled for port C bit 3.<br>1 Pullup enabled for port C bit 3.<br>2 PTCPE2<br>7 bit control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.<br>0 Pullup disabled for port C bit 3.<br>2 PTCPE2<br>7 bit control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.<br>0 Pullup disabled for port C bit 2.<br>1 Pullup enabled for port C bit 2.<br>1 Pullup disabled for port C bit 2.<br>1 Pullup disabled for port C bit 2.<br>1 Pullup disabled for port C bit 2.<br>1 Pullup enabled for port C bit 2.<br>1 Pullup enabled for port C bit 1.<br>1 Pullup disabled for port C bit 1.<br>1 Pullup disabled for port C bit 1.<br>1 Pullup disabled for port C bit 1.<br>1 Pullup enabled for port C bit 1.<br>1 Pullup disabled for port C bit 1.<br>1 Pullup disabled for port C bit 1.<br>1 Pullup enabled for port C                                       |        | Pull Enable for Port C Bit 5                                                                                                                                                        |

| 1       Pullup enabled for port C bit 5.         4       PTCPE4         1       Pull Enable for Port C Bit 4         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por<br>pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 4.         1       Pullup enabled for port C Bit 3         PTCPE3       Pull Enable for Port C Bit 3         1       Pullup disabled for port C bit 3.         2       Pull Enable for Port C Bit 2         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por<br>pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 2.         1       Pullup disabled for port C bit 2.         1       Pullup disabled for port C bit 2.         1       Pullup enabled for port C bit 1.         1       Pullu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | This control bit determines if the internal pullup device is enabled for the associated PTC pin. For port C pins that are configured as outputs or Hi-Z, these bits have no effect. |

| 4       Pull Enable for Port C Bit 4         PTCPE4       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 4.         1       Pullup enabled for port C bit 4.         3       PTCPE3         7       Pull Enable for Port C Bit 3         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 3.         1       Pullup enabled for port C bit 3.         2       PtCPE2         7       Pull Enable for Port C Bit 2         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 2.         1       Pullup disabled for port C bit 2.         1       Pullup enabled for port C bit 1.         1       Pullup enabled for port C Bit 1         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C Bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | 0 Pullup disabled for port C bit 5.                                                                                                                                                 |

| PTCPE4       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 4.         1       Pullup enabled for port C bit 4.         3       PTCPE3         Pull Enable for Port C Bit 3         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 3.         1       Pullup enabled for port C bit 3.         2       PtCPE2         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 3.         1       Pullup enabled for port C bit 2.         1       Pulle nable for Port C Bit 2         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup enabled for port C bit 2.         1       Pullup enabled for port C bit 1.         1       Pullup disabled for port C bit 1.         1       Pull Enable for Port C Bit 1         This control bit determines if the internal pullup device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        | 1 Pullup enabled for port C bit 5.                                                                                                                                                  |

| pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 4.         1       Pullup enabled for port C bit 4.         PTCPE3       Pull Enable for Port C Bit 3         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 3.         1       Pullup enabled for port C bit 3.         2       PTCPE2         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pull Enable for Port C Bit 1         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 1.         1       Pullup disabled for port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                                                                                                                                                                                     |

| 1       Pullup enabled for port C bit 4.         3       PTCPE3         1       Pull Enable for Port C Bit 3         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For porpins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 3.         1       Pullup enabled for port C bit 3.         2       PTCPE2         2       Ptll Enable for Port C Bit 2         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For porpins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 2.         1       Pullup enabled for port C bit 1.         1       Pullup enabled for port C bit 1.         1       Pullup disabled for port C bit 1.         1       Pullup enabled for port C bit 1.         1       Pullup enabled for port C bit 1.         1       Pullup enabled for port C bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | This control bit determines if the internal pullup device is enabled for the associated PTC pin. For port C pins that are configured as outputs or Hi-Z, these bits have no effect. |

| 1       Pullup enabled for port C bit 4.         3       PTCPE3         1       Pull Enable for Port C Bit 3         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 3.         1       Pullup enabled for port C bit 3.         1       Pullup enabled for port C bit 3.         2       PtCPE2         7       Pull Enable for Port C Bit 2         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pull Enable for Port C Bit 1         7       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pull Enable for Port C Bit 1.         1       Pullup disabled for port C bit 1.         1       Pullup enabled for port C bit 1.         1       Pullup enabled for port C bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | 0 Pullup disabled for port C bit 4.                                                                                                                                                 |

| PTCPE3       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For polypins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 3.         1       Pullup enabled for port C bit 3.         PTCPE2       Pull Enable for Port C Bit 2         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For polypins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 2.         1       Pullup disabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pullup disabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pullup enabled for port C Bit 1         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For polypins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pull Enable for Port C Bit 1         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For polypins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 1.         1       Pullup enabled for port C bit 1.         1       Pullup enabled for port C bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                                                                                                                                                                     |

| pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 3.         1       Pullup enabled for port C bit 3.         2       PtCPE2         Hull Enable for Port C Bit 2         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pullup enabled for Port C Bit 1         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pull Enable for Port C Bit 1         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For points that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 1.         1       Pullup disabled for port C bit 1.         1       Pullup enabled for port C bit 1.      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        | Pull Enable for Port C Bit 3                                                                                                                                                        |

| 1       Pullup enabled for port C bit 3.         2       PTCPE2         PTCPE2       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For polypins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pull Enable for Port C Bit 1         PTCPE1       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For polypins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 1.         1       Pullup disabled for port C bit 1.         1       Pullup disabled for port C bit 1.         0       Pullup disabled for port C bit 1.         0       Pull Enable for Port C Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | This control bit determines if the internal pullup device is enabled for the associated PTC pin. For port C pins that are configured as outputs or Hi-Z, these bits have no effect. |

| 2       Pull Enable for Port C Bit 2         PTCPE2       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For polyins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pull Enable for Port C Bit 1         PTCPE1       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For polyins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 1.         1       Ptlup disabled for port C bit 1.         1       Pullup disabled for port C bit 1.         0       Pullup disabled for port C bit 1.         0       Pullup enabled for port C bit 1.         0       Pull Enable for Port C Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | 0 Pullup disabled for port C bit 3.                                                                                                                                                 |

| PTCPE2       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For polyins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pull Enable for Port C Bit 1         This control bit determines if the internal pullup device is enabled for the associated PTC pin. For polyins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 1.         1       Pullup enabled for Port C Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        | 1 Pullup enabled for port C bit 3.                                                                                                                                                  |

| pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 2.         1       Pullup enabled for port C bit 2.         1       Pull Enable for Port C Bit 1         PTCPE1       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 1.         1       Pullup disabled for port C bit 1.         0       Pullup enabled for Port C Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | Pull Enable for Port C Bit 2                                                                                                                                                        |

| 1       Pullup enabled for port C bit 2.         1       Pull Enable for Port C Bit 1         PTCPE1       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 1.         1       Pullup enabled for port C bit 1.         0       Pull Enable for Port C Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        | This control bit determines if the internal pullup device is enabled for the associated PTC pin. For port C pins that are configured as outputs or Hi-Z, these bits have no effect. |

| 1       Pullup enabled for port C bit 2.         1       Pull Enable for Port C Bit 1         PTCPE1       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For por pins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 1.         1       Pullup enabled for port C bit 1.         0       Pull Enable for Port C Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        | 0 Pullup disabled for port C bit 2.                                                                                                                                                 |

| PTCPE1       This control bit determines if the internal pullup device is enabled for the associated PTC pin. For polyins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 1.         1       Pullup enabled for port C bit 1.         0       Pull Enable for Port C Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |                                                                                                                                                                                     |

| This control bit determines if the internal pullup device is enabled for the associated PTC pin. For polypins that are configured as outputs or Hi-Z, these bits have no effect.         0       Pullup disabled for port C bit 1.         1       Pullup enabled for port C bit 1.         0       Pull Enable for Port C Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | Pull Enable for Port C Bit 1                                                                                                                                                        |

| 1     Pullup enabled for port C bit 1.       0     Pull Enable for Port C Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | This control bit determines if the internal pullup device is enabled for the associated PTC pin. For port C pins that are configured as outputs or Hi-Z, these bits have no effect. |

| 1     Pullup enabled for port C bit 1.       0     Pull Enable for Port C Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | 0 Pullup disabled for port C bit 1.                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                                                                                                                                                                                     |