Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

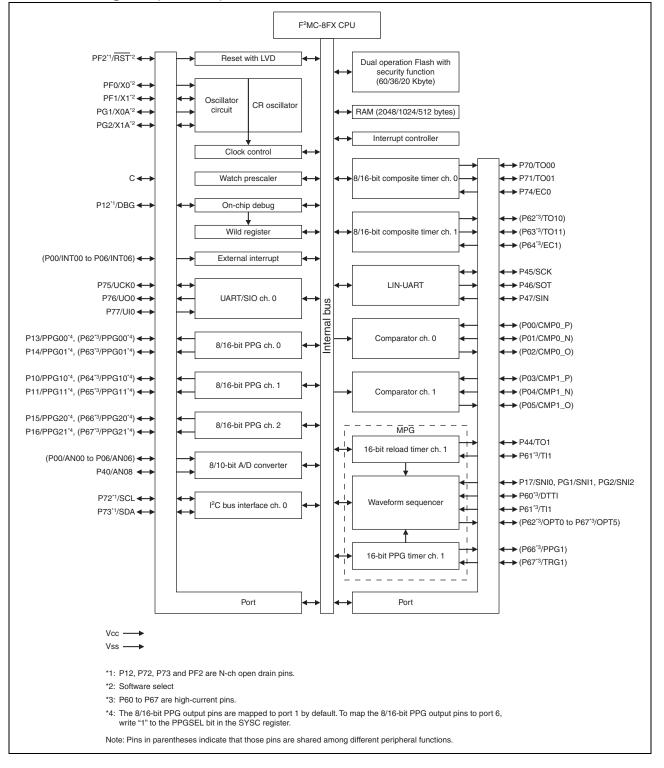

| Core Processor             | F <sup>2</sup> MC-8FX                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 16MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, UART/USART                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 45                                                                              |

| Program Memory Size        | 20KB (20K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 512 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.88V ~ 5.5V                                                                    |

| Data Converters            | A/D 12x8/10b                                                                    |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 52-LQFP                                                                         |

| Supplier Device Package    | 52-LQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f694kpmc1-g-sne2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

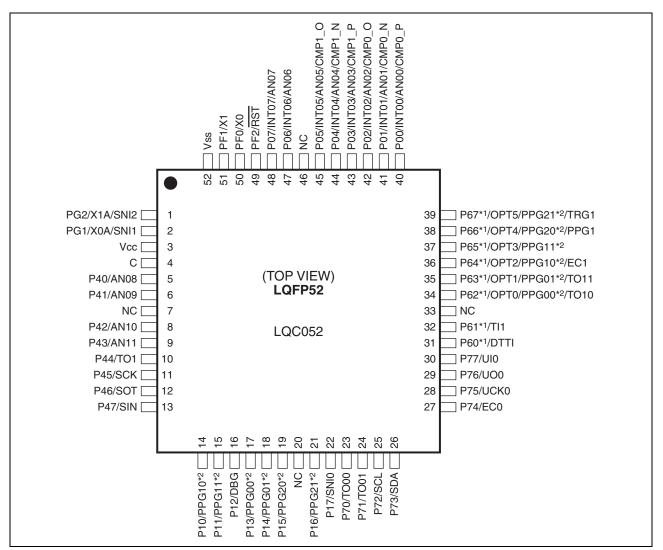

\*1: High-current pin (8 mA/12 mA)

\*2: The 8/16-bit PPG output pins are mapped to port 1 by default. To map the 8/16-bit PPG output pins to port 6, write "1" to the PPGSEL bit in the SYSC register.

| Pin no.              |          |          | I/O               |                                                                                     | I/O type       |              |      |      |  |

|----------------------|----------|----------|-------------------|-------------------------------------------------------------------------------------|----------------|--------------|------|------|--|

| LQFP48*1,<br>QFN48*2 | LQFP52*3 | Pin name | circuit<br>type*4 | Function                                                                            | Input          | Output       | OD*⁵ | PU*6 |  |

| 14                   | 15       | P11      | F                 | General-purpose I/O port                                                            | Hysteresis     | CMOS         |      | 0    |  |

| 17                   | 10       | PPG11    | •                 | 8/16-bit PPG ch. 1 output pin                                                       | Trysteresis    | 01100        |      | Ŭ    |  |

| 15                   | 16       | P12      | G                 | General-purpose I/O port                                                            | Hysteresis     | CMOS         | 0    | _    |  |

| 10                   |          | DBG      | )                 | DBG input pin                                                                       |                | 01100        | Ŭ    |      |  |

| 16                   | 17       | P13      | F                 | General-purpose I/O port                                                            | Hysteresis     | CMOS         |      | 0    |  |

|                      |          | PPG00    |                   | 8/16-bit PPG ch. 0 output pin                                                       |                |              |      |      |  |

| 17                   | 18       | P14      | F                 | General-purpose I/O port                                                            | Hysteresis     | CMOS         |      | 0    |  |

|                      |          | PPG01    |                   | 8/16-bit PPG ch. 0 output pin                                                       | ,              |              |      |      |  |

| 18                   | 19       | P15      | F                 | General-purpose I/O port                                                            | Hysteresis     | CMOS         |      | 0    |  |

|                      |          | PPG20    |                   | 8/16-bit PPG ch. 2 output pin                                                       |                |              |      |      |  |

| _                    | 20       | NC       |                   | It is an internally connected pin.<br>Always leave it unconnected.                  | _              | _            | —    | —    |  |

| 19                   | 21       | P16      | F                 | General-purpose I/O port                                                            | Hysteresis     | CMOS         |      | 0    |  |

| 10                   | 21       | PPG21    |                   | 8/16-bit PPG ch. 2 output pin                                                       | Trysteresis    | omee         |      | Ŭ    |  |

|                      | ļ        | P17      |                   | General-purpose I/O port                                                            |                |              |      |      |  |

| 20                   | 20 22    |          | F                 | Trigger input pin for the position detection function of the MPG waveform sequencer | Hysteresis     | CMOS         | _    | 0    |  |

|                      |          | P70      |                   | General-purpose I/O port                                                            |                |              |      |      |  |

| 21                   | 23       | TO00     | F                 | 8/16-bit composite timer ch. 0<br>output pin                                        | Hysteresis     | CMOS         | -    | 0    |  |

|                      |          | P71      |                   | General-purpose I/O port                                                            |                |              |      |      |  |

| 22                   | 24       | TO01     | F                 | 8/16-bit composite timer ch. 0<br>output pin                                        | Hysteresis     | CMOS         | -    | 0    |  |

|                      |          | P72      |                   | General-purpose I/O port                                                            |                |              |      |      |  |

| 23                   | 25       | SCL      | Н                 | I <sup>2</sup> C bus interface ch. 0 clock I/O<br>pin                               | CMOS           | CMOS         | 0    | —    |  |

|                      |          | P73      |                   | General-purpose I/O port                                                            |                |              |      |      |  |

| 24                   | 26       | SDA      | Н                 | I <sup>2</sup> C bus interface ch. 0 data I/O pin                                   | CMOS           | CMOS         | 0    | _    |  |

|                      |          | P74      |                   | General-purpose I/O port                                                            |                |              |      |      |  |

| 25                   | 27       | EC0      | F                 | 8/16-bit composite timer ch. 0 Hysteresis clock input pin                           |                | CMOS         | -    | 0    |  |

| 26                   | 20       | P75      | F                 | General-purpose I/O port                                                            |                | <u>chios</u> |      |      |  |

| 26                   | 28       | UCK0     | F                 | UART/SIO ch. 0 clock I/O pin                                                        | Hysteresis     | CMOS         |      | 0    |  |

| 07                   |          | P76      | -                 | General-purpose I/O port                                                            | Libert correct | 01/00        | 1    |      |  |

| 27                   | 29       | UO0      | F                 | UART/SIO ch. 0 data output pin                                                      | Hysteresis     | CMOS         |      | 0    |  |

# 11. Block Diagram (LQF044)

| Address                | Register abbreviation | Register name                                                     | R/W | Initial value |

|------------------------|-----------------------|-------------------------------------------------------------------|-----|---------------|

| 0x0055                 | ECCR                  | LIN-UART extended communication control register                  | R/W | 0b00000XX     |

| 0x0056                 | SMC10                 | UART/SIO serial mode control register 1 ch. 0                     | R/W | 0b0000000     |

| 0x0057                 | SMC20                 | UART/SIO serial mode control register 2 ch. 0                     | R/W | 0b00100000    |

| 0x0058                 | SSR0                  | UART/SIO serial status and data register ch. 0                    | R/W | 0b0000001     |

| 0x0059                 | TDR0                  | UART/SIO serial output data register ch. 0                        | R/W | 0b0000000     |

| 0x005A                 | RDR0                  | UART/SIO serial input data register ch. 0                         | R   | 0b0000000     |

| 0x005B<br>to<br>0x005F | _                     | (Disabled)                                                        | _   | _             |

| 0x0060                 | IBCR00                | I <sup>2</sup> C bus control register 0 ch. 0                     | R/W | 0b0000000     |

| 0x0061                 | IBCR10                | I <sup>2</sup> C bus control register 1 ch. 0                     | R/W | 0b0000000     |

| 0x0062                 | IBSR0                 | I <sup>2</sup> C bus status register ch. 0                        | R/W | 0b0000000     |

| 0x0063                 | IDDR0                 | I <sup>2</sup> C data register ch. 0                              | R/W | 0b0000000     |

| 0x0064                 | IAAR0                 | I <sup>2</sup> C address register ch. 0                           | R/W | 0b0000000     |

| 0x0065                 | ICCR0                 | I <sup>2</sup> C clock control register ch. 0                     | R/W | 0b0000000     |

| 0x0066                 | OPCUR                 | 16-bit MPG output control register (upper)                        | R/W | 0b0000000     |

| 0x0067                 | OPCLR                 | 16-bit MPG output control register (lower)                        | R/W | 0b0000000     |

| 0x0068                 | IPCUR                 | 16-bit MPG input control register (upper)                         | R/W | 0b0000000     |

| 0x0069                 | IPCLR                 | 16-bit MPG input control register (lower)                         | R/W | 0b0000000     |

| 0x006A                 | NCCR                  | 16-bit MPG noise cancellation control register                    | R/W | 0b0000000     |

| 0x006B                 | TCSR                  | 16-bit MPG timer control status register                          | R/W | 0b0000000     |

| 0x006C                 | ADC1                  | 8/10-bit A/D converter control register 1                         | R/W | 0b0000000     |

| 0x006D                 | ADC2                  | 8/10-bit A/D converter control register 2                         | R/W | 0b0000000     |

| 0x006E                 | ADDH                  | 8/10-bit A/D converter data register (upper)                      | R/W | 0b0000000     |

| 0x006F                 | ADDL                  | 8/10-bit A/D converter data register (lower)                      | R/W | 0b0000000     |

| 0x0070                 | _                     | (Disabled)                                                        |     | —             |

| 0x0071                 | FSR2                  | Flash memory status register 2                                    | R/W | 0b0000000     |

| 0x0072                 | FSR                   | Flash memory status register                                      | R/W | 0b000X0000    |

| 0x0073                 | SWRE0                 | Flash memory sector write control register 0                      | R/W | 0b0000000     |

| 0x0074                 | FSR3                  | Flash memory status register 3                                    | R   | 0b000XXXXX    |

| 0x0075                 | FSR4                  | Flash memory status register 4                                    | R/W | 0b0000000     |

| 0x0076                 | WREN                  | Wild register address compare enable register                     | R/W | 0b0000000     |

| 0x0077                 | WROR                  | Wild register data test setting register                          | R/W | 0b0000000     |

| 0x0078                 |                       | Mirror of register bank pointer (RP) and direct bank pointer (DP) | _   | _             |

| 0x0079                 | ILR0                  | Interrupt level setting register 0                                | R/W | 0b11111111    |

| 0x007A                 | ILR1                  | Interrupt level setting register 1                                | R/W | 0b11111111    |

| 0x007B                 | ILR2                  | Interrupt level setting register 2                                | R/W | 0b11111111    |

| Address                | Register abbreviation | Register name                                              | R/W | Initial value |

|------------------------|-----------------------|------------------------------------------------------------|-----|---------------|

| 0x007C                 | ILR3                  | Interrupt level setting register 3                         | R/W | 0b11111111    |

| 0x007D                 | ILR4                  | Interrupt level setting register 4                         | R/W | 0b11111111    |

| 0x007E                 | ILR5                  | Interrupt level setting register 5                         | R/W | 0b11111111    |

| 0x007F                 | —                     | (Disabled)                                                 | —   | —             |

| 0x0F80                 | WRARH0                | Wild register address setting register (upper) ch. 0       | R/W | 0b0000000     |

| 0x0F81                 | WRARL0                | Wild register address setting register (lower) ch. 0       | R/W | 0b0000000     |

| 0x0F82                 | WRDR0                 | Wild register data setting register ch. 0                  | R/W | 0b0000000     |

| 0x0F83                 | WRARH1                | Wild register address setting register (upper) ch. 1       | R/W | 0b0000000     |

| 0x0F84                 | WRARL1                | Wild register address setting register (lower) ch. 1       | R/W | 0b0000000     |

| 0x0F85                 | WRDR1                 | Wild register data setting register ch. 1                  | R/W | 0b0000000     |

| 0x0F86                 | WRARH2                | Wild register address setting register (upper) ch. 2       | R/W | 0b0000000     |

| 0x0F87                 | WRARL2                | Wild register address setting register (lower) ch. 2       | R/W | 0b0000000     |

| 0x0F88                 | WRDR2                 | Wild register data setting register ch. 2                  | R/W | 0b0000000     |

| 0x0F89<br>to<br>0x0F91 | _                     | (Disabled)                                                 | _   | _             |

| 0x0F92                 | T01CR0                | 8/16-bit composite timer 01 status control register 0      | R/W | 0b0000000     |

| 0x0F93                 | T00CR0                | 8/16-bit composite timer 00 status control register 0      | R/W | 0b0000000     |

| 0x0F94                 | T01DR                 | 8/16-bit composite timer 01 data register                  | R/W | 0b0000000     |

| 0x0F95                 | T00DR                 | 8/16-bit composite timer 00 data register                  | R/W | 0b0000000     |

| 0x0F96                 | TMCR0                 | 8/16-bit composite timer 00/01 timer mode control register | R/W | 0b00000000    |

| 0x0F97                 | T11CR0                | 8/16-bit composite timer 11 status control register 0      | R/W | 0b0000000     |

| 0x0F98                 | T10CR0                | 8/16-bit composite timer 10 status control register 0      | R/W | 0b0000000     |

| 0x0F99                 | T11DR                 | 8/16-bit composite timer 11 data register                  | R/W | 0b0000000     |

| 0x0F9A                 | T10DR                 | 8/16-bit composite timer 10 data register                  | R/W | 0b0000000     |

| 0x0F9B                 | TMCR1                 | 8/16-bit composite timer 10/11 timer mode control register | R/W | 0600000000    |

| 0x0F9C                 | PPS01                 | 8/16-bit PPG01 cycle setting buffer register               | R/W | 0b11111111    |

| 0x0F9D                 | PPS00                 | 8/16-bit PPG00 cycle setting buffer register               | R/W | 0b11111111    |

| 0x0F9E                 | PDS01                 | 8/16-bit PPG01 duty setting buffer register                | R/W | 0b11111111    |

| 0x0F9F                 | PDS00                 | 8/16-bit PPG00 duty setting buffer register                | R/W | 0b11111111    |

| 0x0FA0                 | PPS11                 | 8/16-bit PPG11 cycle setting buffer register               | R/W | 0b11111111    |

| 0x0FA1                 | PPS10                 | 8/16-bit PPG10 cycle setting buffer register               | R/W | 0b11111111    |

| 0x0FA2                 | PDS11                 | 8/16-bit PPG11 duty setting buffer register                | R/W | 0b11111111    |

| 0x0FA3                 | PDS10                 | 8/16-bit PPG10 duty setting buffer register                | R/W | 0b11111111    |

| 0x0FA4                 | PPGS                  | 8/16-bit PPG start register                                | R/W | 0b00000000    |

| 0x0FA5                 | REVC                  | 8/16-bit PPG output inversion register                     | R/W | 0b00000000    |

| Address                | Register abbreviation                                  | Register name                                                           | R/W                                   | Initial value |

|------------------------|--------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------|---------------|

| 0x0FA6                 | PPS21                                                  | 8/16-bit PPG21 cycle setting buffer register                            | R/W                                   | 0b11111111    |

| 0x0FA7                 | PPS20                                                  | 8/16-bit PPG20 cycle setting buffer register                            | R/W                                   | 0b11111111    |

| 0x0FA8                 | TMRH1 16-bit reload timer timer register (upper) ch. 1 |                                                                         |                                       | 0b00000000    |

| UXUFAO                 | TMRLRH1                                                | 16-bit reload timer reload register (upper) ch. 1                       | d timer reload register (upper) ch. 1 |               |

|                        | TMRL1                                                  | 16-bit reload timer timer register (lower) ch. 1                        | R/W                                   | 060000000     |

| 0x0FA9                 | TMRLRL1                                                | 16-bit reload timer reload register (lower) ch. 1                       | - K/VV                                | 0b00000000    |

| 0x0FAA                 | PDS21                                                  | 8/16-bit PPG21 duty setting buffer register                             | R/W                                   | 0b11111111    |

| 0x0FAB                 | PDS20                                                  | 8/16-bit PPG20 duty setting buffer register                             | R/W                                   | 0b11111111    |

| 0x0FAC<br>to<br>0x0FAF | _                                                      | (Disabled)                                                              | _                                     | —             |

| 0x0FB0                 | PDCRH1                                                 | 16-bit PPG downcounter register (upper) ch. 1                           | R                                     | 0b0000000     |

| 0x0FB1                 | PDCRL1                                                 | 16-bit PPG downcounter register (lower) ch. 1                           | R                                     | 0b00000000    |

| 0x0FB2                 | PCSRH1                                                 | 16-bit PPG cycle setting buffer register (upper) ch. 1                  | R/W                                   | 0b11111111    |

| 0x0FB3                 | PCSRL1                                                 | 16-bit PPG cycle setting buffer register (lower) ch. 1                  | R/W                                   | 0b11111111    |

| 0x0FB4                 | PDUTH1                                                 | 16-bit PPG duty setting buffer register (upper) ch. 1                   | R/W                                   | 0b11111111    |

| 0x0FB5                 | PDUTL1                                                 | 16-bit PPG duty setting buffer register (lower) ch. 1                   | R/W                                   | 0b11111111    |

| 0x0FB6<br>to<br>0x0FBB | _                                                      | (Disabled)                                                              |                                       | —             |

| 0x0FBC                 | BGR1                                                   | LIN-UART baud rate generator register 1                                 | R/W                                   | 0b0000000     |

| 0x0FBD                 | BGR0                                                   | LIN-UART baud rate generator register 0                                 | R/W                                   | 0b0000000     |

| 0x0FBE                 | PSSR0                                                  | UART/SIO dedicated baud rate generator prescaler select register ch. 0  | R/W                                   | 060000000     |

| 0x0FBF                 | BRSR0                                                  | UART/SIO dedicated baud rate generator baud rate setting register ch. 0 | R/W                                   | 0b00000000    |

| 0x0FC0,<br>0x0FC1      | _                                                      | (Disabled)                                                              |                                       | —             |

| 0x0FC2                 | AIDRH                                                  | A/D input disable register (upper)                                      | R/W                                   | 0b0000000     |

| 0x0FC3                 | AIDRL                                                  | A/D input disable register (lower)                                      | R/W                                   | 0b0000000     |

| 0x0FC4                 | OPDBRH0                                                | 16-bit MPG output data buffer register (upper) ch. 0                    | R/W                                   | 0b0000000     |

| 0x0FC5                 | OPDBRL0                                                | 16-bit MPG output data buffer register (lower) ch. 0                    | R/W                                   | 0b0000000     |

| 0x0FC6                 | OPDBRH1                                                | 16-bit MPG output data buffer register (upper) ch. 1                    | R/W                                   | 0b0000000     |

| 0x0FC7                 | OPDBRL1                                                | 16-bit MPG output data buffer register (lower) ch. 1                    | R/W                                   | 0b0000000     |

| 0x0FC8                 | OPDBRH2                                                | 16-bit MPG output data buffer register (upper) ch. 2                    | R/W                                   | 0b0000000     |

| 0x0FC9                 | OPDBRL2                                                | 16-bit MPG output data buffer register (lower) ch. 2                    | R/W                                   | 0b0000000     |

| 0x0FCA                 | OPDBRH3                                                | 16-bit MPG output data buffer register (upper) ch. 3                    | R/W                                   | 0b0000000     |

| 0x0FCB                 | OPDBRL3                                                | 16-bit MPG output data buffer register (lower) ch. 3                    | R/W                                   | 0b0000000     |

| 0x0FCC                 | OPDBRH4                                                | 16-bit MPG output data buffer register (upper) ch. 4                    | R/W                                   | 0b0000000     |

| Address                | Register abbreviation | Register name | R/W | Initial value |

|------------------------|-----------------------|---------------|-----|---------------|

| 0x0FF0<br>to<br>0x0FFF | _                     | (Disabled)    | _   | _             |

• R/W access symbols

R/W : Readable/Writable

R : Read only

Initial value symbols

0 : The initial value of this bit is "0".

1 : The initial value of this bit is "1".

X : The initial value of this bit is undefined.

Note: Do not write to an address that is "(Disabled)". If a "(Disabled)" address is read, an indeterminate value is returned.

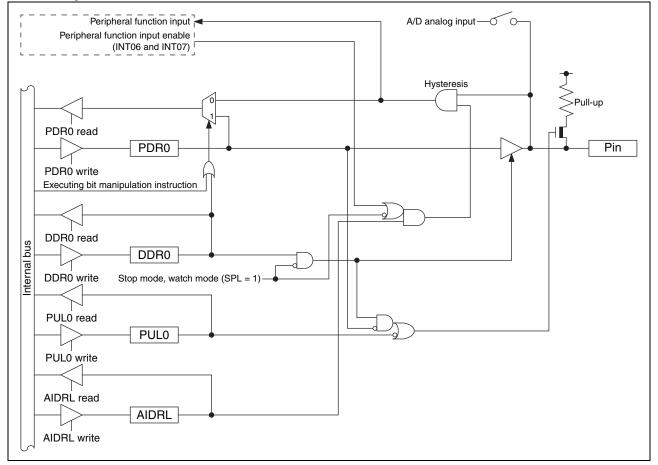

• P06/INT06/AN06 pin

This pin has the following peripheral functions:

- External interrupt input pin (INT06)

- 8/10-bit A/D converter analog input pin (AN06)

- P07/INT07/AN07 pin

- This pin has the following peripheral functions:

- External interrupt input pin (INT07)

- 8/10-bit A/D converter analog input pin (AN07)

- Block diagram of P06/INT06/AN06 and P07/INT07/AN07

## 17.2.3 Port 1 registers

Port 1 register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                               |  |  |  |  |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|-------------------------------------|--|--|--|--|--|--|

| PDR1                  | 0    | Pin state is "L" level. | PDR1 value is "0".                          | As output port, outputs "L" level.  |  |  |  |  |  |  |

|                       |      | Pin state is "H" level. | PDR1 value is "1".                          | As output port, outputs "H" level.* |  |  |  |  |  |  |

| DDR1                  | 0    |                         | Port input enabled                          |                                     |  |  |  |  |  |  |

| DDRI                  | 1    |                         | Port output enabled                         |                                     |  |  |  |  |  |  |

| PUL1                  | 0    |                         | Pull-up disabled                            |                                     |  |  |  |  |  |  |

| FULI                  | 1    |                         | Pull-up enabled                             |                                     |  |  |  |  |  |  |

\*: If the pin is an N-ch open drain pin, the pin state becomes Hi-Z.

• Correspondence between registers and pins for port 1

|          |      | Correspondence between related register bits and pins |      |      |      |       |      |      |  |  |  |  |

|----------|------|-------------------------------------------------------|------|------|------|-------|------|------|--|--|--|--|

| Pin name | P17  | P16                                                   | P15  | P14  | P13  | P12   | P11  | P10  |  |  |  |  |

| PDR1     |      |                                                       |      |      |      |       |      |      |  |  |  |  |

| DDR1     | bit7 | bit6                                                  | bit5 | bit4 | bit3 | bit2* | bit1 | bit0 |  |  |  |  |

| PUL1     |      |                                                       |      |      |      |       |      |      |  |  |  |  |

\*: Though P12 has no pull-up function, bit2 in the PUL1 register can still be accessed. The operation of P12 is not affected by the setting of bit2 in the PUL1 register.

#### 17.2.4 Port 1 operations

- Operation as an output port

- A pin becomes an output port if the bit in the DDR1 register corresponding to that pin is set to "1".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- When a pin is used as an output port, it outputs the value of the PDR1 register to external pins.

- If data is written to the PDR1 register, the value is stored in the output latch and is output to the pin set as an output port as it is.

- Reading the PDR1 register returns the PDR1 register value.

- Operation as an input port

- A pin becomes an input port if the bit in the DDR1 register corresponding to that pin is set to "0".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- If data is written to the PDR1 register, the value is stored in the output latch but is not output to the pin set as an input port.

- Reading the PDR1 register returns the pin value. However, if the read-modify-write (RMW) type of instruction is used to read the PDR1 register, the PDR1 register value is returned.

- Operation as a peripheral function output pin

- A pin becomes a peripheral function output pin if the peripheral output function is enabled by setting the output enable bit of a peripheral function corresponding to that pin.

- The pin value can be read from the PDR1 register even if the peripheral function output is enabled. Therefore, the

output value of a peripheral function can be read by the read operation on the PDR1 register. However, if the readmodify-write (RMW) type of instruction is used to read the PDR1 register, the PDR1 register value is returned.

- Operation as a peripheral function input pin

- To set a pin as an input port, set the bit in the DDR1 register corresponding to the input pin of a peripheral function to "0".

- Reading the PDR1 register returns the pin value, regardless of whether the peripheral function uses that pin as its input pin. However, if the read-modify-write (RMW) type of instruction is used to read the PDR1 register, the PDR1 register value is returned.

#### • Operation at reset If the CPU is reset, all bits in the DDR1 register are initialized to "0" and port input is enabled.

- Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDR1 register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

## • Operation of the pull-up register

Setting the bit in the PUL1 register to "1" makes the pull-up resistor be internally connected to the pin. When the pin output is "L" level, the pull-up resistor is disconnected regardless of the value of the PUL1 register.

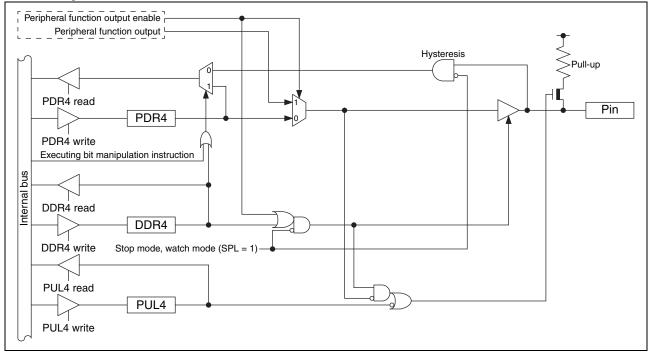

# 17.3 Port 4

Port 4 is a general-purpose I/O port. This section focuses on its functions as a general-purpose I/O port. For details of peripheral functions, refer to their respective chapters in "New 8FX MB95690K Series Hardware Manual".

### 17.3.1 Port 4 configuration

- Port 4 is made up of the following elements.

- General-purpose I/O pins/peripheral function I/O pins

- Port 4 data register (PDR4)

- Port 4 direction register (DDR4)

- Port 4 pull-up register (PUL4)

- A/D input disable register (upper) (AIDRH)

#### 17.3.2 Block diagrams of port 4

- P40/AN08 pin

- This pin has the following peripheral function:

- 8/10-bit A/D converter analog input pin (AN08)

- P41/AN09 pin

- This pin has the following peripheral function:

- 8/10-bit A/D converter analog input pin (AN09)

- P42/AN10 pin

- This pin has the following peripheral function:

- 8/10-bit A/D converter analog input pin (AN10)

- P43/AN11 pin

- This pin has the following peripheral function:

- 8/10-bit A/D converter analog input pin (AN11)

- P44/TO1 pin

- This pin has the following peripheral function:

- 16-bit reload timer ch. 1 output pin (TO1)

- P46/SOT pin

- This pin has the following peripheral function:

- LIN-UART data output pin (SOT)

- Block diagram of P44/TO1 and P46/SOT

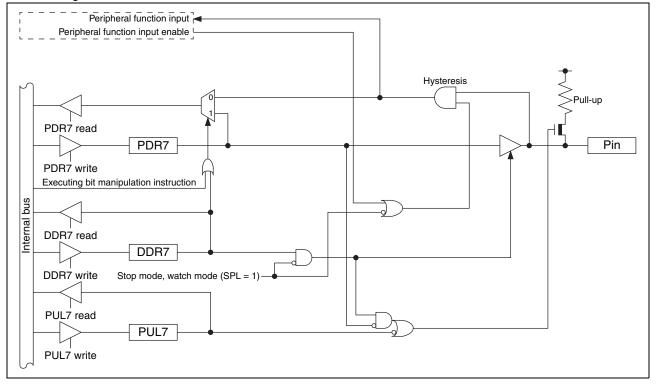

#### Block diagram of P74/EC0

#### 17.6.4 Port F operations

- Operation as an output port

- A pin becomes an output port if the bit in the DDRF register corresponding to that pin is set to "1".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- When a pin is used as an output port, it outputs the value of the PDRF register to external pins.

- If data is written to the PDRF register, the value is stored in the output latch and is output to the pin set as an output port as it is.

- Reading the PDRF register returns the PDRF register value.

- · Operation as an input port

- A pin becomes an input port if the bit in the DDRF register corresponding to that pin is set to "0".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- If data is written to the PDRF register, the value is stored in the output latch but is not output to the pin set as an input port.

- Reading the PDRF register returns the pin value. However, if the read-modify-write (RMW) type of instruction is used to read the PDRF register, the PDRF register value is returned.

- · Operation at reset

If the CPU is reset, all bits in the DDRF register are initialized to "0" and port input is enabled.

- Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDRF register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

# **18. Interrupt Source Table**

|                                      | Interrupt         |        | r table<br>ress |          | pt level<br>register | Priority order of<br>interrupt sources             |  |  |

|--------------------------------------|-------------------|--------|-----------------|----------|----------------------|----------------------------------------------------|--|--|

| Interrupt source                     | request<br>number | Upper  | Lower           | Register | Bit                  | of the same level<br>(occurring<br>simultaneously) |  |  |

| External interrupt ch. 0             | IRQ00             | 0xFFFA | 0xFFFB          | ILR0     | L00 [1:0]            | High                                               |  |  |

| External interrupt ch. 4             | IIII              |        | UNITE           |          | 200[1.0]             |                                                    |  |  |

| External interrupt ch. 1             | IRQ01             | 0xFFF8 | 0xFFF9          | ILR0     | L01 [1:0]            |                                                    |  |  |

| External interrupt ch. 5             |                   | 0,1110 | 0/1113          |          | 201[1.0]             |                                                    |  |  |

| External interrupt ch. 2             | IRQ02             | 0xFFF6 | 0xFFF7          | ILR0     | L02 [1:0]            |                                                    |  |  |

| External interrupt ch. 6             | 11/02/02          |        |                 | ILINU    | L02 [1.0]            |                                                    |  |  |

| External interrupt ch. 3             | IRQ03             | 0xFFF4 | 0xFFF5          | ILR0     | L03 [1:0]            |                                                    |  |  |

| External interrupt ch. 7             |                   | 086664 | UXEFES          | ILKU     | LU3 [1.0]            |                                                    |  |  |

| UART/SIO ch. 0                       | IRQ04             | 0xFFF2 | 0xFFF3          | ILR1     | L04 [1:0]            |                                                    |  |  |

| MPG (DTTI)                           |                   | UXFFFZ | UXFFF3          |          | L04 [1.0]            |                                                    |  |  |

| 8/16-bit composite timer ch. 0       | IRQ05             | 0xFFF0 | 0xFFF1          | ILR1     | 1 05 [1:0]           |                                                    |  |  |

| (lower)                              | IRQUS             | UXFFFU | UXFFFI          | ILRI     | L05 [1:0]            |                                                    |  |  |

| 8/16-bit composite timer ch. 0       | IRQ06             |        | 0xFFEF          |          | 1.00 [4.0]           |                                                    |  |  |

| (upper)                              | IRQUO             | 0xFFEE | UXFFEF          | ILR1     | L06 [1:0]            |                                                    |  |  |

| LIN-UART (reception)                 | IRQ07             | 0xFFEC | 0xFFED          | ILR1     | L07 [1:0]            |                                                    |  |  |

| LIN-UART (transmission)              | IRQ08             | 0xFFEA | 0xFFEB          | ILR2     | L08 [1:0]            |                                                    |  |  |

| 8/16-bit PPG ch. 1 (lower)           | IRQ09             | 0xFFE8 | 0xFFE9          | ILR2     | L09 [1:0]            |                                                    |  |  |

| 8/16-bit PPG ch. 1 (upper)           | IRQ10             | 0xFFE6 | 0xFFE7          | ILR2     | L10 [1:0]            |                                                    |  |  |

| 8/16-bit PPG ch. 2 (upper)           | IRQ11             | 0xFFE4 | 0xFFE5          | ILR2     | L11 [1:0]            |                                                    |  |  |

| 8/16-bit PPG ch. 0 (upper)           | IRQ12             | 0xFFE2 | 0xFFE3          | ILR3     | L12 [1:0]            |                                                    |  |  |

| 8/16-bit PPG ch. 0 (lower)           | IRQ13             | 0xFFE0 | 0xFFE1          | ILR3     | L13 [1:0]            |                                                    |  |  |

| 8/16-bit composite timer ch. 1       |                   |        |                 |          |                      |                                                    |  |  |

| (upper)                              | IRQ14             | 0xFFDE | 0xFFDF          | ILR3     | L14 [1:0]            |                                                    |  |  |

| 8/16-bit PPG ch. 2 (lower)           | IRQ15             | 0xFFDC | 0xFFDD          | ILR3     | L15 [1:0]            |                                                    |  |  |

| 16-bit reload timer ch. 1            |                   |        | -               |          |                      |                                                    |  |  |

| MPG (write timing/compare clear)     | IRQ16             | 0xFFDA | 0xFFDB          | ILR4     | L16 [1:0]            |                                                    |  |  |

| I <sup>2</sup> C bus interface ch. 0 |                   | -      | -               |          |                      |                                                    |  |  |

| 16-bit PPG timer ch. 1               |                   |        |                 |          |                      |                                                    |  |  |

| MPG (position detection/compare      | IRQ17             | 0xFFD8 | 0xFFD9          | ILR4     | L17 [1:0]            |                                                    |  |  |

| interrupt)                           |                   |        |                 |          |                      |                                                    |  |  |

| 8/10-bit A/D converter               | IRQ18             | 0xFFD6 | 0xFFD7          | ILR4     | L18 [1:0]            |                                                    |  |  |

| Time-base timer                      | IRQ19             | 0xFFD4 | 0xFFD5          | ILR4     | L19 [1:0]            |                                                    |  |  |

| Watch prescaler                      |                   |        |                 |          |                      |                                                    |  |  |

| Comparator ch. 0                     | IRQ20             | 0xFFD2 | 0xFFD3          | ILR5     | L20 [1:0]            |                                                    |  |  |

| Comparator ch. 1                     | IRQ21             | 0xFFD0 | 0xFFD1          | ILR5     | L21 [1:0]            |                                                    |  |  |

| 8/16-bit composite timer ch. 1       |                   |        |                 |          |                      |                                                    |  |  |

| (lower)                              | IRQ22             | 0xFFCE | 0xFFCF          | ILR5     | L22 [1:0]            |                                                    |  |  |

| Flash memory                         | IRQ23             | 0xFFCC | 0xFFCD          | ILR5     | L23 [1:0]            | Low                                                |  |  |

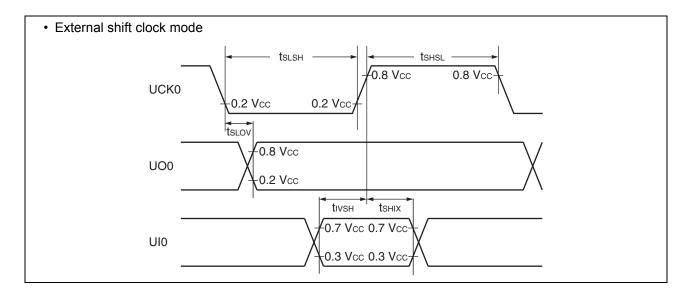

## 20.4 AC Characteristics

## 20.4.1 Clock Timing

(Vcc = 2.88 V to 5.5 V, Vss = 0.0 V, T<sub>A</sub> = -40 °C to +85 °C)

| David t            | 0       | <b>D</b> ' | 0         |       |        |       | Demerica |                                                                                                                                                                                                                                                                            |                                                                                                                                                       |

|--------------------|---------|------------|-----------|-------|--------|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter          | Symbol  | Pin name   | Condition | Min   | Тур    | Max   | Unit     | Remarks                                                                                                                                                                                                                                                                    |                                                                                                                                                       |

|                    | Fсн     | X0, X1     | _         | 1     | —      | 16.25 | MHz      | When the main oscillation<br>circuit is used                                                                                                                                                                                                                               |                                                                                                                                                       |

|                    | ГСН     | X0         | X1: open  | 1     |        | 12    | MHz      | When the main external clock                                                                                                                                                                                                                                               |                                                                                                                                                       |

|                    |         | X0, X1     | *         | 1     | _      | 32.5  | MHz      | is used                                                                                                                                                                                                                                                                    |                                                                                                                                                       |

|                    |         |            |           | 3.92  | 4      | 4.08  | MHz      | • 0 °C $\leq$ TA $\leq$ +70 °C                                                                                                                                                                                                                                             |                                                                                                                                                       |

|                    | Ескн    | _          | _         | 3.8   | 4      | 4.2   | MHz      | Operating conditions<br>• The main CR clock is used.<br>• $-40 \ ^{\circ}C \le T_A < 0 \ ^{\circ}C,$<br>$+70 \ ^{\circ}C < T_A \le +85 \ ^{\circ}C$                                                                                                                        |                                                                                                                                                       |

|                    |         |            |           | 7.84  | 8      | 8.16  | MHz      | <ul> <li>0 °C ≤ T<sub>A</sub> ≤ +70 °C</li> </ul>                                                                                                                                                                                                                          |                                                                                                                                                       |

|                    |         |            |           | 7.6   | 8      | 8.4   | MHz      | $\begin{array}{l} \text{Operating conditions}\\ \bullet \ \text{PLL multiplication rate: 2}\\ \bullet \ - 40 \ ^{\circ}\text{C} \leq \text{T}_{\text{A}} < 0 \ ^{\circ}\text{C},\\ + 70 \ ^{\circ}\text{C} < \text{T}_{\text{A}} \leq + 85 \ ^{\circ}\text{C} \end{array}$ |                                                                                                                                                       |

|                    | -       | RPLL —     |           |       | 9.8    | 10    | 10.2     | MHz                                                                                                                                                                                                                                                                        | Operating conditions<br>• PLL multiplication rate: 2.5<br>• $0 \ ^{\circ}C \le T_A \le +70 \ ^{\circ}C$                                               |

| Clock<br>frequency |         |            |           |       | 9.5    | 10    | 10.5     | MHz                                                                                                                                                                                                                                                                        | Operating conditions<br>• PLL multiplication rate: 2.5<br>• $-40 \ ^{\circ}C \le T_A < 0 \ ^{\circ}C,$<br>$+70 \ ^{\circ}C < T_A \le +85 \ ^{\circ}C$ |

|                    | FMCRPLL |            |           | 11.76 | 12     | 12.24 | MHz      | • 0 °C ≤ T <sub>A</sub> ≤ +70 °C                                                                                                                                                                                                                                           |                                                                                                                                                       |

|                    |         |            |           | 11.4  | 12     | 12.6  | MHz      | Operating conditions<br>• PLL multiplication rate: 3<br>• $-40 \ ^{\circ}C \le T_A < 0 \ ^{\circ}C,$<br>$+70 \ ^{\circ}C < T_A \le +85 \ ^{\circ}C$                                                                                                                        |                                                                                                                                                       |

|                    |         |            |           | 15.68 | 16     | 16.32 | MHz      | • 0 °C ≤ T <sub>A</sub> ≤ +70 °C                                                                                                                                                                                                                                           |                                                                                                                                                       |

|                    |         |            |           | 15.2  | 16     | 16.8  | MHz      | Operating conditions<br>• PLL multiplication rate: 4<br>• $-40 \ ^{\circ}C \le T_A < 0 \ ^{\circ}C,$<br>$+70 \ ^{\circ}C < T_A \le +85 \ ^{\circ}C$                                                                                                                        |                                                                                                                                                       |

|                    | FcL     | X0A V1A    |           | _     | 32.768 | _     | kHz      | When the sub-oscillation<br>circuit is used                                                                                                                                                                                                                                |                                                                                                                                                       |

|                    | FCL     | X0A, X1A   |           | _     | 32.768 | _     | kHz      | When the sub-external clock is used                                                                                                                                                                                                                                        |                                                                                                                                                       |

|                    | FCRL    |            |           | 50    | 100    | 150   | kHz      | When the sub-CR clock is<br>used                                                                                                                                                                                                                                           |                                                                                                                                                       |

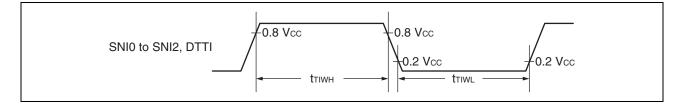

20.4.10 MPG Input Timing

(Vcc = 5.0 V±10%, Vss = 0.0 V, T<sub>A</sub> = -40 °C to +85 °C)

| Parameter         | Svmbol          | Pin name              | Condition | Va      | ue  | Unit | Remarks  |

|-------------------|-----------------|-----------------------|-----------|---------|-----|------|----------|

|                   | Symbol          | Finname               | Condition | Min     | Max |      | itema K3 |

| Input pulse width | tтıwн,<br>t⊤ıw∟ | SNI0 to SNI2,<br>DTTI | _         | 4 tmclk | _   | ns   |          |

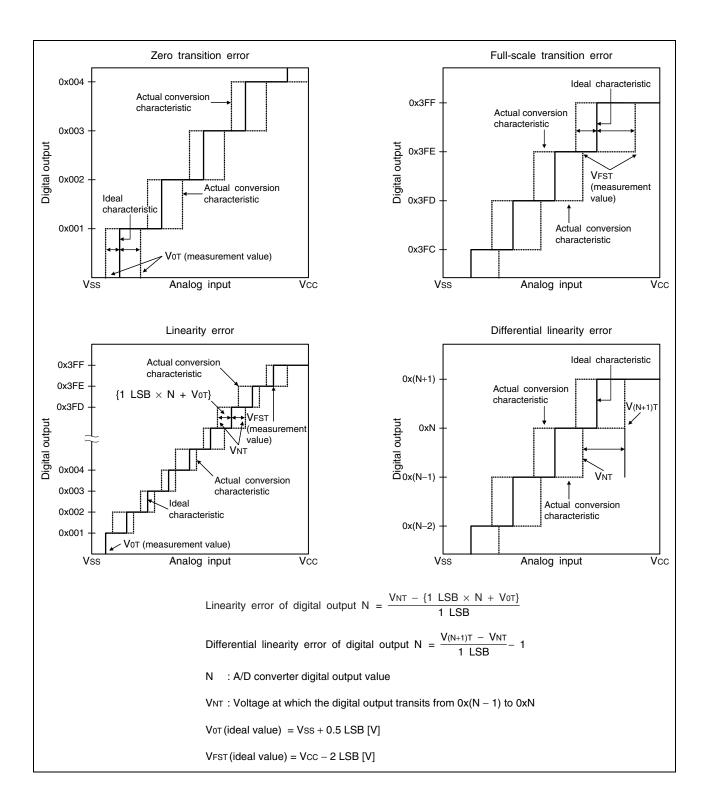

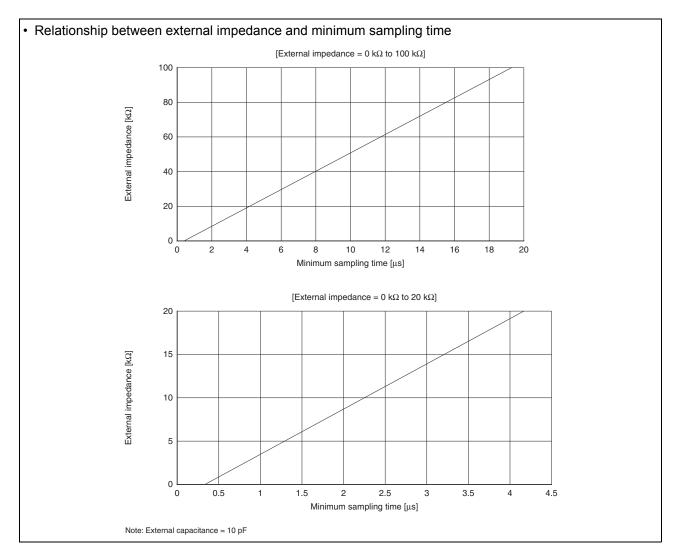

## • A/D conversion error

As |Vcc - Vss| decreases, the A/D conversion error increases proportionately.